183 3

362

|

00 tr |

0 |

1 |

q8^H |

0 |

1 1 1 |

Xł OD |

0 |

1 |

|

00 |

0 |

0 |

00 |

0 |

LU) |

00 |

0 |

0 |

|

01 |

0 |

0 |

01 |

0 |

1 |

00 |

D |

0 |

|

11 |

0 |

CD |

11 |

1 |

0 |

00 |

0 |

0 |

|

10 |

0 |

0 |

10 |

0 |

1) |

00 |

D |

0 |

W1 w2

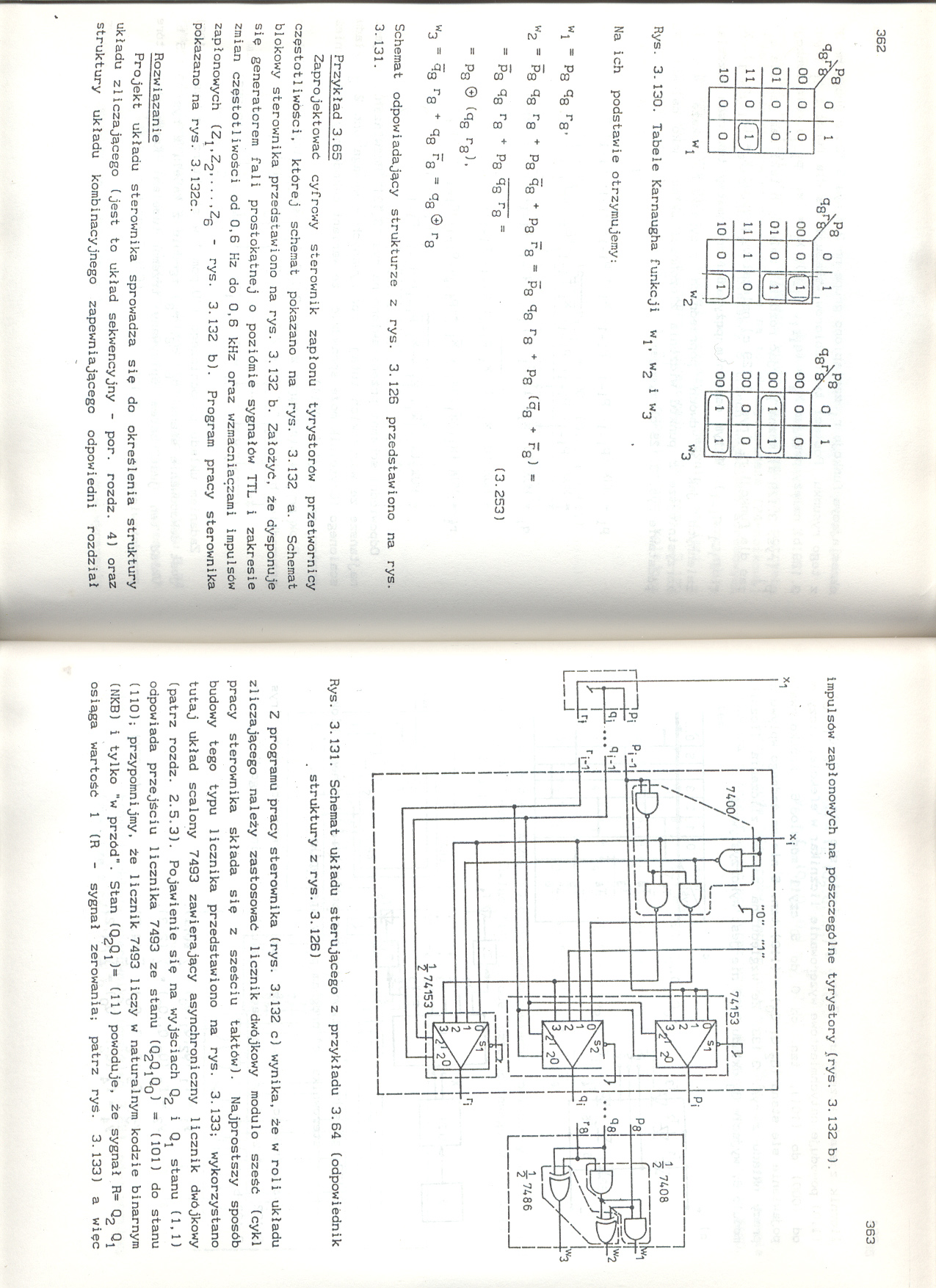

Rys. 3.130. Tabele Karnaugha funkcji Wj, i w^ Na ich podstav;ie otrzymujemy:

W1 = P8 q8 r8’

W2 = P8 q8 r8 + P8 q8 * p8 F8 = P8 q8 r8 + p8 (q8 + F8J =

PS q8 r8 + p8 qS r8 = (3.253)

= Pa © (q8 r8).

W3 = qS r8 + q8 F8 = q8 9 r8

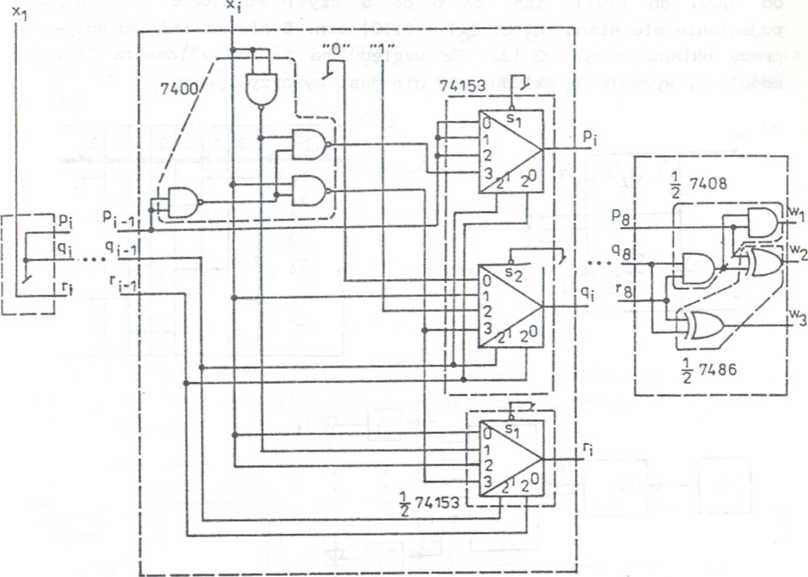

Schemat odpowiadający strukturze z rys. 3.12S przedstawiono na rys. 3. 131.

Przykład 3.65

Zaprojektować cyfrowy sterownik zapłonu tyrystorów przetwornicy częstotliwości, której schemat pokazano na rys. 3.132 a. Schemat blokowy sterownika przedstawiono na rys. 3.132 b. Założyć, że dysponuje się generatorem fali prostokątnej o poziómie sygnałów TTL i zakresie zmian częstotliwości od 0,6 Hz do 0,6 kHz oraz wzmacniaczami impulsów zapłonowych (Zj.Zg....,Zg - rys. 3.132 b). Program pracy sterownika pokazano na rys. 3.132c.

Rozwiązanie

Projekt układu sterownika sprowadza się do określenia struktury układu zliczającego (jest to układ sekwencyjny - por. rozdz. 4) oraz struktury układu kombinacyjnego zapewniającego odpowiedni rozdział impulsów zapłonowych na poszczególne tyrystory .(rys. 3.132 b).

Rys. 3.131. Schemat układu sterującego z przykładu 3.64 (odpowiednik struktury z rys. 3.126)

Z programu pracy sterownika (rys. 3.132 c) wynika, że w roli układu zliczającego należy zastosować licznik dwójkowy moduło sześć (cykl

pracy sterownika składa się z sześciu taktów). Najprostszy sposób

budowy tego typu licznika przedstawiono na rys. 3.133; wykorzystano

tutaj układ scalony 7493 zawierający asynchroniczny licznik dwójkowy (patrz rozdz. 2.5.3). Pojawienie się na wyjściach Qg i stanu (1.1) odpowiada przejściu licznika 7493 ze stanu (OgOjOg) = (101) do stanu (110); przypomnijmy, że licznik 7493 liczy w naturalnym kodzie binarnym (NKB) i tylko “w przód". Stan (Q2Qj)= (11) powoduje, że sygnał R= Qj osiąga wartość 1 (R - sygnał zerowania; patrz ryś. 3.133) a więc

Wyszukiwarka

Podobne podstrony:

Zdj 25252525EAcie087 i Ko/por^ilzcinc Ministra lnfra.Mn.Mi.iy, ov 00 tr u ,prawi,

I! im A n fiS fi ! i 51*11fi§ l«I IM;je114a f a i tfI sili V >OOOyO*iNON ^ *0 00 Tr- mi *“ i * 4r

29244 skanowanie0003 (183) (*> --, S>.8-C0 9,00 Ś (i c7€rttAJiErT^m]rr$

Zdj 25252525EAcie087 i Ko/por^ilzcinc Ministra lnfra.Mn.Mi.iy, ov 00 tr u ,prawi,

13 10 Agnieszka 6 624,00 zł 4 627,00 zł 7 362,00 zł 18 613,00 zł Artur 2 671,00 zł 9 053,00 zł 9 84

DSC00433 1 A.y 099*0 ^/MV ##<M /dMPWflrt# * -+-f*+* *+• 0* **♦ t • I 00 0, tr* it V V*.

Inne Budżet (plan) Faktyczny wydatek _ Domowe 300,00 362,00 -62,00 Prezenty &

Zdjęcie014 1 *o ft* i 004* nm f0 tr ca * * •o m M »*j •1 « IJt » 00 4 /• «

i i ul. Rynek 1, 26-610 Radom Telefon: (0-48) 362-11-50, 340-51-00

więcej podobnych podstron