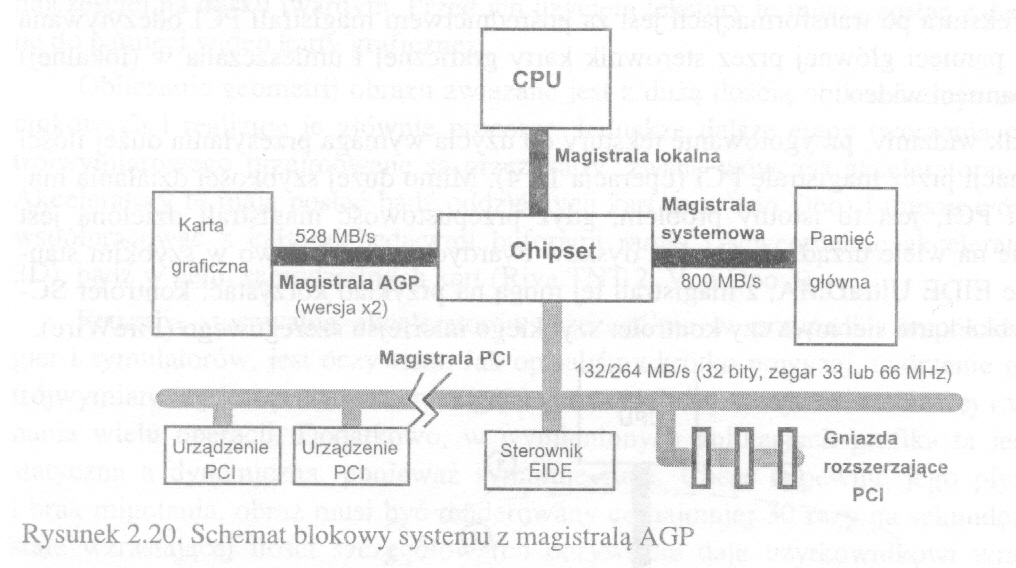

rys 2 20

Magistrala lokalna

|

Magistrala | ||||

|

Karta |

528 MB/s |

Chipset |

systemowa |

Pamięć |

|

graficzna |

■■■■■i | |||

|

Magistrala AGP |

800 MB/s |

główna | ||

|

(wersja x2) |

Wyszukiwarka

Podobne podstrony:

rys 2 19 CPU PCI© Wideo RAM Karta graficzna Magistrala

rys 2 28 CPU Gniazda rozszerzające PCI HDD Rysunek 2.28. Przebieg teksturowania dla magistrali PCI

9.4. Magistrale lokalne m rracę z kartą graficzną pobierającą nawet ponad 200 W. Złącze AGP Pro umoż

66607 p1030157 CPU - magistrale systemowe Rejestry ALU Jednostka h sterująca Magistrale Sterowania D

73002 p1020828 VESA Video Local Bus CPU Magistrala 486 PAO Cache Sloty VL (2 lub

rys 2 18 Interfejs magistrali 32-bitowej Generator sygnałów synchronizujących SYNCHRO H SYNCHRO

> Podstawy działania sieci komputerowych <17> Rysunek 20. Topologia magistrali w

Image064 I I ©Z-O . Jz Rys. 3.20. Schematy logiczne układów realizujących wieloargumentową funkcję A

Image099 W przypadku dołączenia do tej bramki ekspanderów (rys. 4.20) układ realizuje funkcję: F = A

więcej podobnych podstron