Zdjęcia 0032

U ■

• A * I • I • • •

A-

-w t

&

* * ' * w

r v» ; <

•• v» I

I gi ?

*

I

* •

f

\ ••*•• f • • • • ••• •

sŁ

%

JL C-1

?/!

< *

Li

lt * • • H • •

% • M • <

WTK • \v

* I pŁ *

-1

# i

pasma

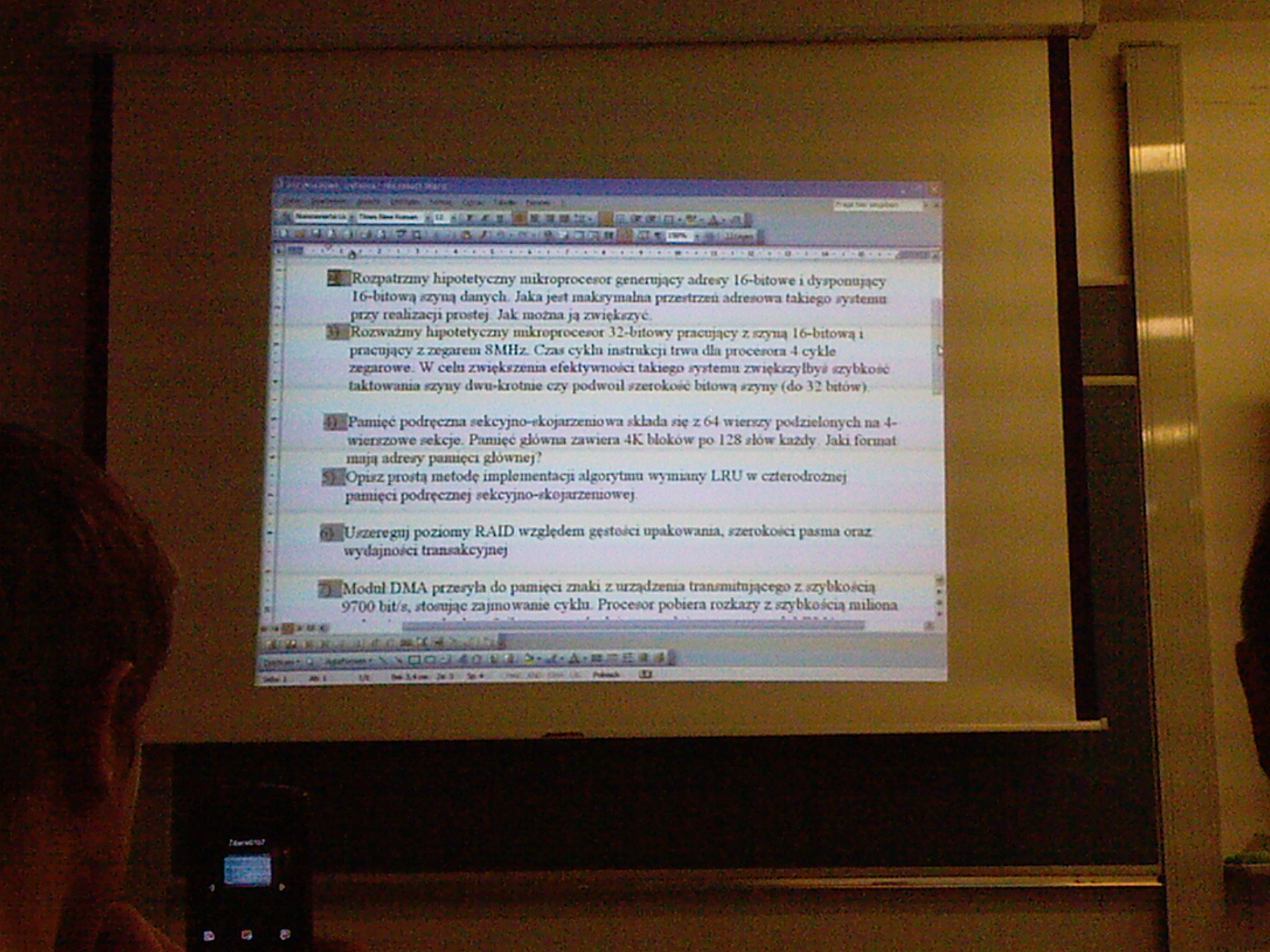

ozpatrzzny hipotetyczny uukiopiocesor generujący adresy 16-Utowc i dysponujący l6~bitowa szyna tLuiych Jaka je»t maksymalna pnastiran adresowa takiego systemu przy trabzacji prostej Jak mottu ;a zwiększyć URorwaziny hipoteł>cmy nńkroproceeot 4 2-bitowy pracujący r. szyna I6bit»iq» pracujący z zegarem SMH/ < Va« cyUn in>tiukcji trwa «lli procesora 4 cykle zegarowe W celu zwięlcezraa efektywności takiego systemu zwiększyłby* *zy bkosc taktowaniu «z>uy dwu-kiotiue cz>’ podwoił */ctoko»c bitów* szynę (do 42 hitowi

4WfPanucc |Kxlręczr-i sckcyjno-ekojarmuowa składa nę z 64 wicirzy po» lziclonych na 4-wicrrzowc sekcje Plunięć główna rauicta tk blokow po 128 slow kardy Jaki ionrot maj* adresy panueci głównej ’

poetą metodę implementacji algotytmu wymiany LRU w czlctodrozncj pamięci podxe«»ej sekcyjno-skojarzriuowc)

[U/zrrcguj poziomy RAID względem gęstości upakowania, wydajności transakcy jnej

ifodal DMA pizesyb do pantteci znaki z uizadzrtua transmitującego z szy bkością 9700 bit s. stosując zajmowaiue cyklu Procesor pobiera tozkazy z szy bkością nuliona

b u «

%Ą h»M«

•w*

f % A * ' *

1

f •

•!

i>fkł f* rl ■. • *

rrfĆEA; • V

• •

l • •

• • •

t *

M

l •

•«•

!• 4 *

Wyszukiwarka

Podobne podstrony:

Zdjęcie0121 J « »* M<ŁU ( v« oi /at)m r/>JI>iH «g

Zdjęcie0141 —-X...... U .*, ^f >„ H 1 * /■« /?/ 3 ■v ~ł>,v-a e-e- v c> <apV V V ^ —1-?*

12327 IMGC48 v» w • • ;#J

13504 Zdjęcie0252 (2) CZ.v» . ,JL. i <qJL£jlc&>* ćHH <✓. p»-ł3&W*

Zdjęcie0018 •tntfttttf* »v» * MMM* MM - MM WuwMtMmww { a 0 i .« mr*» juk” • j

56190 Zdjęcie0580 (10) V—±h*)t4 -*<*4mĘ £ taPfWi tJlUk. U im,

Zdjęcie0563 :» sympiili v« /n;i In. kr//imimi:i t.>• iiwihiiikiitt

Zdjęcie 24 v~>_ X m? . u( Cv^ o. pp Y* «u_l ła.^ a V - Mtci vlm >órr jnek%t

więcej podobnych podstron