img035 (56)

EUWiP / MECHATRONIKA

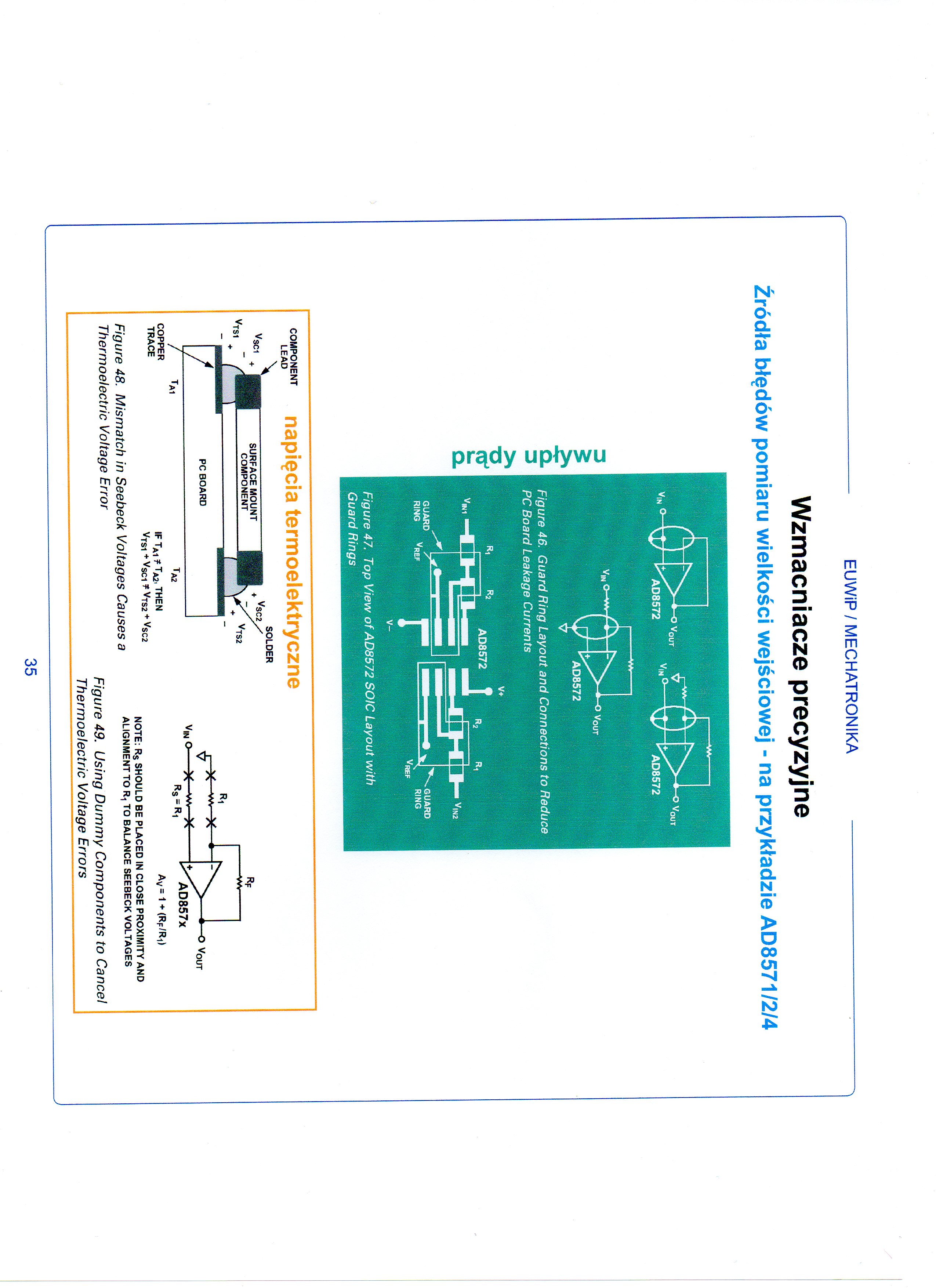

Wzmacniacze precyzyjne

Źródła błędów pomiaru wielkości wejściowej - na przykładzie AD8571/2/4

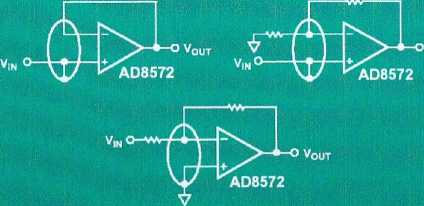

Figurę 46. Guard Ring Layout and Connections to Reduce PC Board Leakage Currents

Figurę 47. Top View of AD8572 SOIC Layout with Guard Rings

CTeadENT

COPPER

TRACĘ

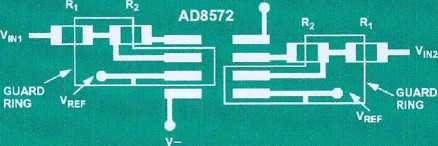

IF TA111*2, THEN Vts1 + VSC1 ¥ VTS2 + VSC2

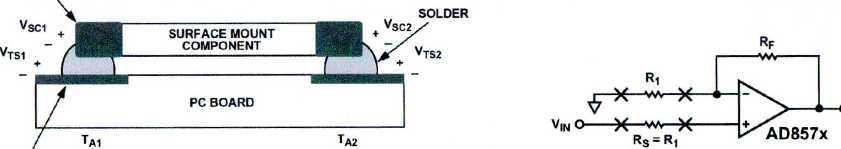

Av=1 + (Rf'Ri)

NOTĘ: Rs SHOULD BE PLACED IN CLOSE PROXIMITY AND ALIGNMENT TO R, TO BALANCE SEEBECK VOLTAGES

Figurę 48. Mismatch in Seebeck Voltages Causes a Thermoelectric Voltage Error

Figurę 49. Using Dummy Components to Cancel Thermoelectric Voltage Errors

35

Wyszukiwarka

Podobne podstrony:

img032 (56) EUWiP/MECHATRONIKAWzmacniacze precyzyjne Struktura wewnętrzna wzmacniaczyb) Wzmacniacze

img029 (56) EUWiP / MECHATRONIKAWzmacniacze o różnicowym wejściu i wyjściuZastosowania(c.d.) Sterowa

img033 (53) EUWiP / MECHATRONIKAWzmacniacze precyzyjne Dokumentacja katalogowa - na przykładzie AD85

img037 (49) EUWiP / MECHATRONIKAWzmacniacze precyzyjneAD8571/2/4 - przykład zastosowania Wzmacniacz

img038 (50) EUWiP / MECHATRONIKAWzmacniacze precyzyjneZestawienie porównawcze parametrów (wg ADI)

W2. Analiza błędów pomiarów wielkości fizycznych Wszystkie wykonywane pomiary obarczone są błędem

img036 (53) EUWiP / MECHATRONIKAWzmacniacze precyzyjneAD8571/2/4 - praca z obciążeniem o charakterze

img031 (56) - EUWiP / MECHATRONIKAWzmacniacze o różnicowym wejściu i wyjściuZestawienie parametrów w

img034 (58) EUWiP / MECHATRONIKAWzmacniacze precyzyjne AD8571/2/4 - podstawowe

więcej podobnych podstron