Image131 (2)

■ Projekty AVT

W urządzeniach elektronicznych mających na celu sterowanie różnymi elementami mechanicznymi często stosuje się silniki krokowe. Dzięki ich budowie możliwe jest obrócenie wału o praktycznie dowolny kąt w dowolnym kierunku. Niestety wymaga to odpowiedniego sterowania cewkami silnika, co komplikuje układ elektroniczny obsługujący silnik.

Prezentowany układ stanowi rozwiązanie tego problemu. Nie jest on samodzielnym sterownikiem, a jedynie układem zamieniającym wejściowe impulsy zegarowe na odpowiednie sekwencje sterujące cewkami silnika. Urządzenie służy do sterowania silnikiem krokowym czterocewkowym, w którym wszystkie cewki mająjeden przewód wspólny. Silniki takie są często spotykane w starych stacjach dyskietek 5,25 cala, gdzie sterują ruchomą głowicą. Sterowanie odbywa się w trybie unipolarnym. Możliwy jest wybór kierunków' obrotów oraz wyłączenie zasilania silnika. Układ przyda się wszędzie tam, gdzie konieczne okazuje się użycie silnika krokowego, a z jakichś powodów nie można zrealizować w tym samym urządzeniu odpowiedniego sterownika. Jest tani, niewielki, a jednocześnie prosty w użytkowaniu.

Opis układu

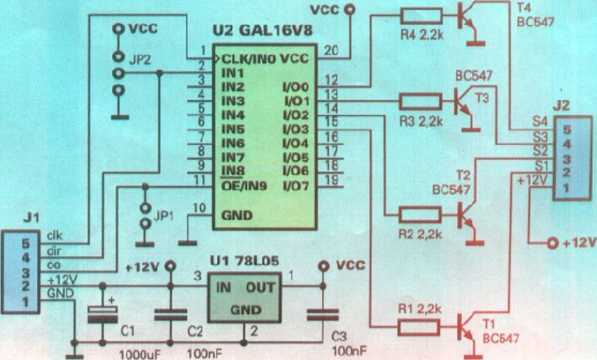

Schemat ideowy sterownika pokazany jest na rysunku I. Sterownik został zrealizowany za pomocą układu programowalnego typu GALI6V8. Jest to tani układ z rodziny SPLD (Simple Programmable Logic Devices) mogący zastąpić garść klasycznych układów TTL. Zachowanie układu nie jest bowiem zdefiniowane na stałe, lecz jest programowane przez użytkownika. Układ taki składa się z bloków złożonych z programowalnej matrycy wejściowej bramek AND, zespołu bramek OR su-mujących składniki iloczynowe (tzw. termy) generowane przez matrycę AND oraz programowalnego przerzutnika typu D. W zależności od typu układu, takich bloków, zwanych makrokomórkami. jest od kilku do kilkudziesięciu. W użytym układzie jest ich 8. Ustawienia makrokomórek przechowywane są w pamięci EEPROM, co umożliwia wielokrotne programowanie i kasowanie układu. Więcej informacji na temat układów programowalnych można znaleźć w cyklu artykułów pt. .,Układy programowalne” w Elektronice Praktycznej od nr 2<2004. Zastosowanie układu SPLD umożliwia łatwe wykonanie licznika ze specyficznymi stanami wyjściowymi w jednym układzie scalonym. Do opisu zachowania wewnętrznych bloków układów programowalnych służą specjalne języki opisu sprzętu zwane HDL (Hardware Description Langua-ge). Prezentowany projekt został zrealizowany w języku CUPL za pomocą kompilatora Win-CUPL udostępnianego bezpłatnie, po zarejestrowaniu się, przez firmę Atmel. Opis projektu w języku CUPL

przedstawiony jest na listingu I. Opis ten składa się z kilku charakterystycznych części. Na początku znajduje się nagłówek zawierający informacje opisujące projekt. W ostatniej linijce nagłówka jest definicja typu użytego układu. Poniżej znajdują się deklaracje wejść i wyjść używanych w projekcie. Pin nr 1 to wejście sygnału zegarowego, pin 2 odpowiada za kierunek zliczania licznika Q0-Q3, któremu odpowiadają piny 12-15, pin 11 steruje przełączaniem wyjść w stan wysokiej impedancji. Następnie zdefiniowane jest pole licznika 4-bitowego oraz stany, które ten licznik przyjmuje. Ostatnim elementem w pokazanym opisie jest definicja przejść pomiędzy kolejnymi stanami licznika w zależności od poziomu linii dir. Stany S0-S7 odpowiadają kolejnym fazom ruchu wirnika, natomiast stan Sx to stan początkowy po włączeniu zasilania, kiedy

Rys. 1 Schemat ideowy

18 Wrzesień 2005 Elektronika dla Wszystkich

Wyszukiwarka

Podobne podstrony:

32981 Image131 (2) ■ Projekty AVT W urządzeniach elektronicznych mających na celu sterowanie różny

- od 1 do 4: 1-4pkt. Czy projekt przewiduje zastosowanie działań mających na celu

ORIOŃSKItflSl* st’WOLONTARIAT MISYJNY to projekt mający na celu pomoc placówkom misyjnym w Afryce Ty

MINISZKOŁA POD ŻAGLAMI to nowy projekt Stowarzyszenia Edukacja pod Żaglami mający na celu: ■

Image127 Projekty AVT prosta otóż częstotliwość wyjściowa generatora VCO (Voltage Controlled Oscilla

Dlaczego Uniwersytet Bergen ? • Ambitny i innowacyjny projekt mający na celu

Image11 (39) li ^STOPNIE OCHRONY OSŁON URZĄDZEŃ ELEKTROENERGETYCZNYCH WYTRZYMAŁOŚĆ NA UDERZENIA OSŁO

urządzenia przyspieszające pracę, stworzono nowy system coachingowo -mentoringowy, mający na celu sz

Cykl spotkań mających na celu kultywowanie tradycji, nabycie umiejętności właściwego zachowania się

więcej podobnych podstron