Image129

■

DldT LED LA5642

|

1 i * t>A1A2f * h | |

|

c l_ |

UJ |

Sterują one prostym wzmacniaczem z tran zystorem T3 (darlingtona), z którego napięcie wyjściowe jest podawane przez filtr dolno-przepustowy (R16, C8, R17) na diodę pojemnościową Dl w obwodzie rezonansowym generatora VCO.

W układzie Ul stan pętli jest na bieżąco kontrolowany i określany na wyprowadzeniu UL, gdzie podczas zamknięcia pętli (synchronizacji) występuje stan wysoki, a podczas otwarcia stan niski. Wykorzystano to do wykonania prostego wskaźnika stanu pętli (wprowadzenie UL połączono przez rezystor RIO do kropki segmentu h drugiej cyfry wyświetlacza), który w końcowym etapie budowy układu znacznie ułatwi strojenie.

Zmiany kanałów w układzie dokonuje się dwoma przyciskami GÓRA i DÓŁ, które są bezpośrednio podłączone do układu Ul. Krótkie przyciśnięcie któregokolwiek z nich powoduje zmianę kanału o jeden kanał dalej w wybranym kierunku, dłuższe przyciśnięcie prowadzi do automatycznej zmiany kanałów.

Elementy R12 i C7 odpowiadają za poprawny start (tzw. resct) układu podczas włączenia zasilania.

Montaż i uruchomienie

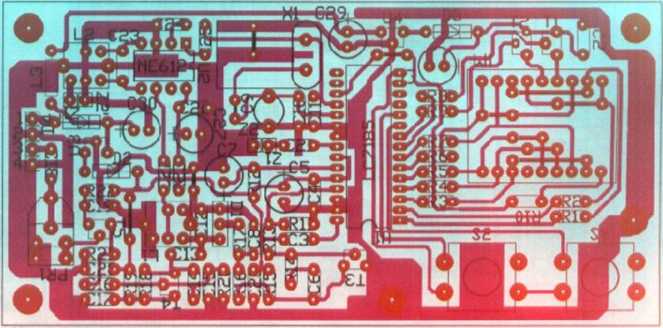

Schemat montażowy syntezy PLL przedstawia rysunek 5 Podczas projektowania płytki starano się ograniczyć jej gabaryty do niezbędnego minimum, stąd rezystory na niej są typu miniaturowego (0,IW). Nie jest to warunkiem poprawnego działania układu i można z powodzeniem montować rezystory większe (0.125 W, 0,25W) - w pozycji pionowej. Montaż należy wykonać zgodnie z obowiązującymi regułami sztuki elektronicznej, tzn. rozpocząć od najniższych elementów (zworek), a zakończyć na najwyższych. Zwrócić przy tym należy szczególną uwagę na wyprowadzenia filtrów LI i L2. Chodzi o to, czy cieniutkie końce uzwojeń dochodzące do nich nie są pourywane. Unikniemy w ten sposób dużych kłopotów przy uruchamianiu układu. Tranzystora T3 nie montujemy, ponieważ utrudniałby on początkowy cykl sirojenia układu. Ponadto na płytce należy wykonać jedną zworkę krótkim przewodem ekranowanym biegnącym pomiędzy filtrem L2 a kondensatorem C21. Wyświetlacz W1 należy zamontować tak wysoko, jak to tylko możliwe, tzn. na ile pozwolą nam jego wyprowadzenia. Uzyskamy w ten sposób lepszą jego widoczność po zamontowaniu modułu płytki w obudowie.

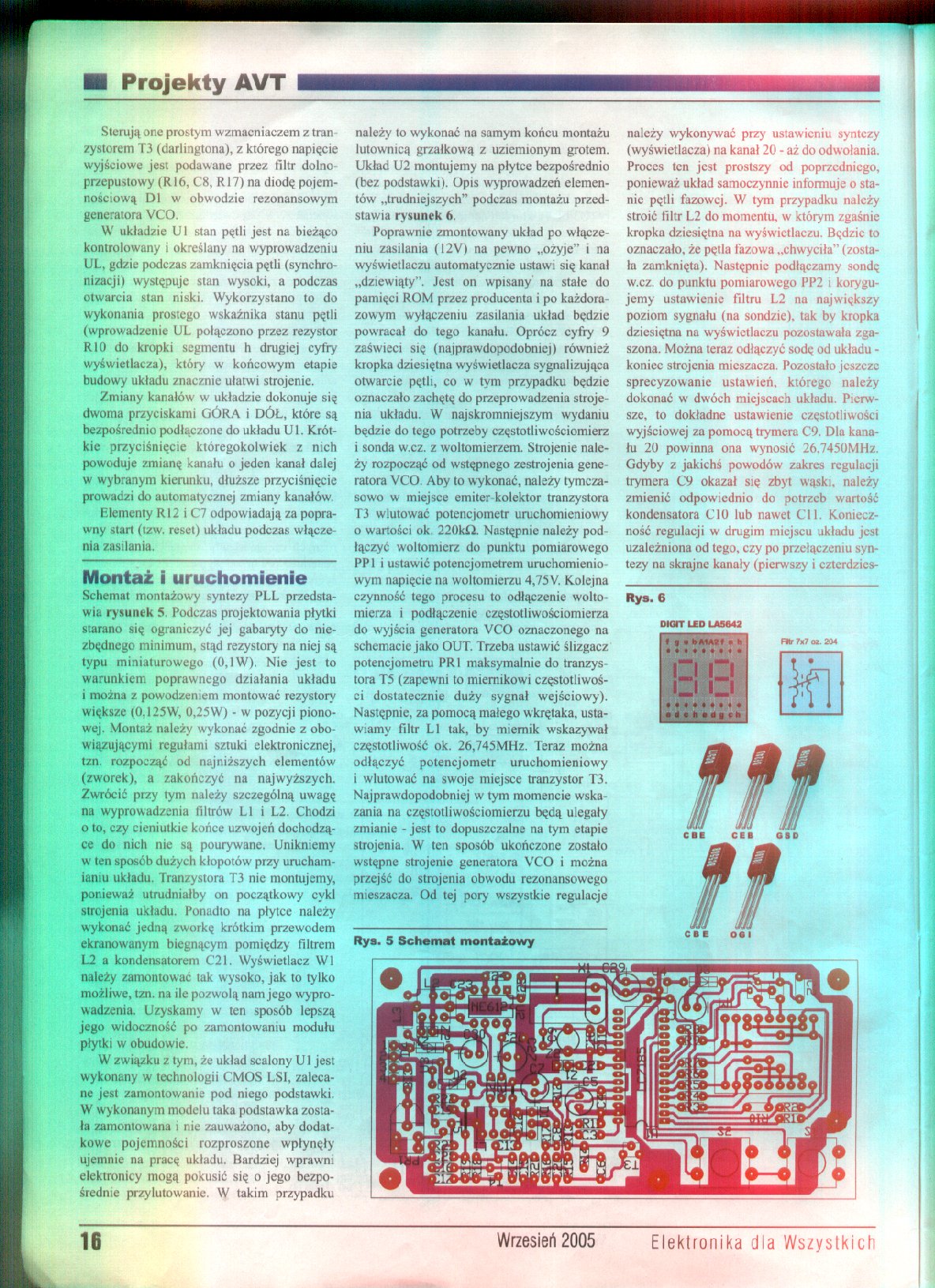

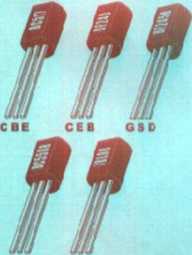

W związku z tym, że układ scalony U1 jest wykonany w technologii CMOS LSI, zalecane jest zamontowanie pod niego podstawki. W wykonanym modelu taka podstawka została zamontowana i nie zauważono, aby dodatkowe pojemności rozproszone wpłynęły ujemnie na pracę układu. Bardziej wprawmi elektronicy mogą pokusić się o jego bezpośrednie przy lutowanie. W takim przypadku należy to wykonać na samym końcu montażu lutownicą grzałkową z uziemionym grotem. Układ U2 montujemy na płytce bezpośrednio (bez podstawki). Opis wyprowadzeń elementów „trudniejszych” podczas montażu przedstawia ry sunek 6

Poprawnie zmontowany układ po włączeniu zasilania (12V) na pewno „ożyje” i na wyświetlaczu automatycznie ustawi się kanał „dziewiąty”. Jest on wpisany na stałe do pamięci ROM przez producenta i po każdorazowym wyłączeniu zasilania układ będzie powracał do tego kanału. Oprócz cyfry 9 zaświeci się (najprawdopodobniej) również kropka dziesiętna wyświetlacza sygnalizująca otwarcie pętli, co w tym przypadku będzie oznaczało zachętę do przeprowadzenia strojenia układu. W najskromniejszym wydaniu będzie do tego potrzeby częstotliwościomierz i sonda w.cz. z woltomierzem. StTojeme należy rozpocząć od wstępnego zestrojenia gene ratora VCO. Aby to wykonać, należy tymczasowo w miejsce emiter kolektor tranzystora T3 wlutować potencjometr uruchomieniowy

0 wartości ok 220k£2. Następnie należy podłączyć woltomierz do punktu pomiarowego PP1 i ustawić potencjometrem uruchomieniowym napięcie na woltomierzu 4,75 V. Kolejna czynność tego procesu to odłączenie woltomierza i podłączenie częstotliwościomierza do wyjścia generatora VCO oznaczonego na schemacie jako OUT. Trzeba ustawić ślizgacz potencjometru PR1 maksymalnie do tranzys tora T5 (zapewni to miernikowi częstotliwości dostatecznie duży sygnał wejściowy). Następnie, za pomocą małego wkrętaka, ustawiamy filtr LI tak, by miernik wskazywał częstotliwość ok. 26,745MHz. Teraz można odłączyć potencjometr uruchomieniowy

1 wlutować na swoje miejsce tranzystor T3. Najprawdopodobniej w tym momencie wska zania na częstotliwościomierzu będą ulegały zmianie - jest to dopuszczalne na tym etapie strojenia. W ten sposób ukończone zostało wstępne strojenie generatora VCO i można przejść do strojenia obwodu rezonansowego mieszacza. Od tej pory wszystkie regulacje należy wykonywać przy ustawieniu syntezy (wyświetlacza) na kanał 20 - aż do odwołania. Proces ten jest prostszy od poprzedniego, ponieważ układ samoczynnie informuje o stanic pętli fazowej. W tym przypadku należy stroić filtr L2 do momentu, w którym zgaśnie kropka dziesiętna na wyświetlaczu. Będzie to oznaczało, że pętla fazowa „chwyciła” (została zamknięta). Następnie podłączamy sondę w.cz do punktu pomiarowego PP2 i korygujemy ustawienie filtru L2 na największy poziom sygnału (na sondzie), tak by kropka dziesiętna na wyświetlaczu pozostawała zgaszona. Można teraz odłączyć sodę od układu -koniec strojenia mieszacza. Pozostało jeszcze sprecyzowanie ustawień, którego należy dokonać w dwóch miejscach układu. Pierwsze, to dokładne ustawienie częstotliwości wyjściowej za pomocą trymera C9. Dla kanału 20 powinna ona wynosić 26.7450MHz. Gdyby z jakichś powodów zakres regulacji trymera C9 okazał się zbyt wąski, należy zmienić odpowiednio do potrzeb wartość kondensatora CIO lub nawet CII. Konieczność regulacji w drugim miejscu układu jest uzależniona od tego, czy po przełączeniu syntezy na skrajne kanały (pierwszy i cztcrdzics-

Rys. 6

Rys. 5 Schemat montażowy

CBE OGI

16 Wrzesień 2005 Elektronika dla Wszystkich

Wyszukiwarka

Podobne podstrony:

Image11 (25) ■ Projekty AVT „liter” (LED). Obsługę wspomnianego programu testowego przybliża ry sune

Image164 Projektowanie bloków pamięci Układy pamięci można w prosty sposób łączyć w bloki pamięci o

18290 Image140 (3) Projektowanie £=ŁiHi Ja ustawiłem je dla kaprysu w taki sposób, jak pokazuje rysu

20338 Image189 (2) ■ Projekty AVT r" BootLock12 f BootLock11 f BootLockQ2 BootLockOI I Lcck2 P

WSTĘPSPIS TREŚCI L Wstęp_ Większa swoboda projektowa dzięki diodom LED.............. System

więcej podobnych podstron