wykl02c

Wykład 3

Pamięć systemu komputerowego

Złożone zagadnienia pamięci komputerowych można opanować łatwiej, jeśli podzieli się systemy pamięciowe według ich podstawowych własności.

U

ii

i procesor

wewnętrzna (giówna)

S zewnętrzna (pomocnicza)

rozmiar słowa iiczba słów

słowo

biok

U

n

I

t

sekwencyjny

bezpośredni

swobodny

skojarzeniowy

półprzewodnikowa

magnetyczna

uiotna/nieuiotna

wymazywalna/niewymazy walna

Program wykładu

• Właściwości pamięci w systemach komputerowych

- Położenie i pojemność pamięci

- Jednostka transferu pamięci

- Dostęp do pamięci

• Miara wydajności

• Hierarchia pamięci - przesłanki

• Pamięci półprzewodnikowe

- Typy pamięci półprzewodnikowych

- Mikroukłady pamięci

- Organizacja modułu pamięci

• Korekcja błędów

- Kody korekcyjne

- Kod Hamminga

- Konstruowanie kodu

- Długość słowa o korekcja

- KodySEC-DEC

Położenie i pojemność pamięci

W każdym systemie komputerowym istnieją pamięci zarówno wewnętrzne, iak i zewnętrzne w stosunku do komputera.

jest często identyfikowana z . Są

jednak inne formy pamięci wewnętrznej. Przykładowo procesor wymaga własnej pamięci iokainej w postaci . Ponadto, jednostka

sterująca procesora może również potrzebować wiasnej pamięci wewnętrznej.

składa się z ,

takich jak pamięa dyskowe i taśmowe, które są dostępne dia procesora poprzez sterowniki wejścia-wyjścia.

^ Oczywistą własnością pamięci jest jej . W przypadku pamięci

wewnętrznej jest ona zwykie wyrażana w bajtach (i bajt = 8 bitów) iub w słowach. Powszechnymi długościami słów są: 8, 16 i 32 bity. Pojemność pamięci zewnętrznej jest zwykie wyrażana w bajtach.

Parametrem związanym z pojemnością jest (ang. transfer

unit). W przypadku pamiąci wewnętrznej jednostka transferu jest

doprowadzonych do modułu pamięci i wychodzących z niego. Jest ona często równa długości słowa.

t Słowo. „Naturaina" jednostka organizacji pamięci. Zwykle rozmiar słowa jest równy iiczbie bitów wykorzystywanych do reprezentowania iiczby łub długości rozkazu.

•J £ Jednostka adresowaina. W wieiu systemach jednostką adresowalną jest . Jednak niektóre systemy umożliwiają adresowanie na poziomie bajtów. W każdym przypadku zaieżność między długością adresu A a iiczbą adresowalnych jednostek N jest następująca:

2* = N.

•Jt Jednostka transferu. W przypadku pamięci głównej jest to liczba bitów jednocześnie odczytywanych z pamięci lub do niej zapisywanych.

. W przypadku pamięci zewnętrznej dane są często przekazywane w jednostkach o wiele większych niż słowo, określanych jako bloki.

Dostęp do pamięci - cz.ll

Dostęp sekwencyjny. Pamięć jest zorganizowana za pomocą jednostek danych zwanych rekordami.

. Do oddzieiania rekordów i do pomocy przy odczycie są wykorzystywane przechowywane informacje adresowe. Odczyt i zapis są wykonywane za pomocą tego samego mechanizmu, przy czym proces ten musi się przenosić z pozycji bieżącej do pozycji pożądanej, przepuszczając i odrzucając każdy rekord pośredni. W rezultacie czas dostępu do różnych rekordów może się bardzo różnić, (np. pamięci taśmowe)

Dostęp cykliczny bezpośredni. Podobnie jak w przypadku dostępu sekwencyjnego, proces odczytu i zapisu w pamięciach o dostępie bezpośrednim jest reaiizowany za pomocą tego samego mechanizmu. Jednak poszczególne bioki lub rekordy mają unikatowy adres oparty na iokacji fizycznej. Dostęp jest reaiizowany przez bezpośredni dostęp do najbliższego otoczenia, po którym następuje sekwencyjne poszukiwanie, liczenie lub oczekiwanie w celu osiągnięcia iokacji finainej. Jak poprzednio czas dostępu jest zmienny, (np. pamięci dyskowe)

Dostęp do pamięci - cz.lll

Dostęp swobodny. Każda adresowaina lokacja w pamięci ma unikatowy, fizycznie wbudowany mechanizm adresowania.

dostępu i jest stały. Dzięki temu dowoina lokacja może być wybierana swobodnie i jest adresowana i dostępna bezpośrednio, (np. pamięć główna)

Dostęp skojarzeniowy. Jest to rodzaj dostępu swobodnego, który umożiiwia porównywanie i specyficzne badanie zgodności wybranych bitów wewnątrz słowa, przy czym jest to czynione

. Tak więc słowo jest wyprowadzane raczej części swojej niż na podstawie adresu.

Podobnie jak w przypadku zwykłych pamięci o dostępie swobodnym, każda iokacja ma własny mechanizm adresowania, a czas dostępu jest stały i niezaieżny od poprzednich operacji dostępu, (np. pamięć podręczna)

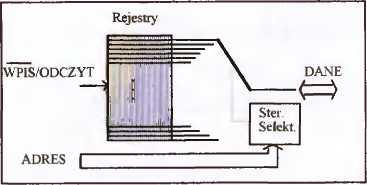

Pamięć o dostępie swobodnym (RAM)

Miara wydajności - cz.l

Istnieją trzy podstawowe parametry będące miara wydajności:

Czas dostępu.

1

I

W przypadku jest to czas

odczytu lub zapisu, to znaczy czas od chwiii doprowadzenia adresu do chwiii zmagazynowania lub udostępnienia danych.

W przypadku czas dostępu jest

czasem potrzebnym na odczytu-zapisu

w pożądanym miejscu.

_ izn> iaLIh _

X X

W’ \_/ .

l

Po odczycie

|

7 | ||

|

i ^1 | ||

|

Wskaźnik stosu | ||

|

-_J1_ |

Przygotowanie Wpis Odczyt

do wpisu

Pamięć o dostępie stosowym (STACK)

Miara wydajności - cz.ll

nęci. Pojęcie to było pierwotnie stosowane do pamięci o dostępie swobodnym. Czas cyklu składa się z czasu dostępu oraz z dodatkowego czasu, który musi upłynąć, zanim będzie mógi nastąpić kolejny dostęp. Ten dodatkowy czas może być potrzebny dia zaniku sygnałów przejściowych iub do regeneracji danych, jeśii odczyt jest niszczący.

____ cykhi

x y

RH

DANE

L2J>* pizetiz> inai

Szybkość przesyłania (transferu!. Jest to szybkość, z jaką dane mogą być wprowadzane do jednostki pamięci iub z niej wyprowadzane.

t W przypadku pamięci o dostępie swobodnym jest ona równa:

ii W przypadku pamięci o dostępie nieswobodnym zachodzi następująca zaieiność:

TA +

N_

R

Tn - średni czas odczytu iub zapisu W bitów,

Ta -średni czas dostępu,

N- iiczba bitów,

R - szybkość transferu w bitach na sekundę [bit/s].

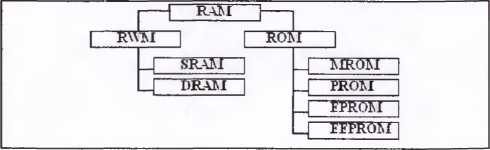

Pamięci półprzewodnikowe

PÓŁPRZEWODNIKOWE PAMIĘCI 0 DOSTĘPIE SWOBODNYM

Hierarchia pamięci - przesłanki

t Ograniczenia przy projektowaniu pamięci komputera mogą być podsumowane za pomocą trzech pytań: Ile? Jak szybko? Za ile?

Istnieją wzajemne zależności między podstawowymi parametrami pamięci, to znaczy między kosztem, pojemnością i czasem dostępu.

i I większa pojemność - mniejszy koszt na bit,

< > większa pojemność - większy czas dostępu.

< > mniejszy czas dostępu - większy koszt na bit,

0,25-1 ns, 1-4kB, duża moc

lwi**- 10-50ns. 256MB-4GB, mała

Dyikow* pamięć podręczna N.

Pamięć dyskowa

1-1 Oms, 20-120GB

>1TB

Pamięć taśmowa

Dysk optyczny

|

Rodzaj pamięci |

Kategoria |

Wymazywanie |

Sposób zapisu |

Ulotność |

|

Pamięć czytaj-pisz (RWM) |

odczyt-zapis |

elektryczne, na poziomie bajta |

elektryczny |

ulotna |

|

Pamięć stała (ROM) Programował na pamięć stała (PROM) |

tylko odczyt |

niemożliwe |

maski | |

|

Wymazywania PROM (EPROM) |

światłem UV. na poziomie mikroukładu |

nleulolne | ||

|

Pamięć błyskawiczna |

głównie odczyt |

Elektryczne na poziomie bloku |

elektryczny | |

|

Elektrycznie wymazywalna PROM (EEPROM) |

elektryczne, na poziomie bajta |

j

REI ADRES wmun

pamiętanie pojemności Cs -005pF

- powolna llfl ta ładunku

- konieczność odśwież ima

co I 8 nas -1 etapy adresowania adicsłwin.1 iRAK) adi es kolumny (CA8)

«- odczytywane wszystkie kolumny » odczyt mszczący

• 2 etapy

ZipiS k

• : etapy

|

LS,., |

LS, |

n |

|

4, |

4r ' |

W- _u~ |

|

LBi. |

4... ■ aa |

4- u« |

czag cyŁhi

DC

/W

_My

Dr

czdtLdM^pii cza* przetizyinai

odczyt z pamięci

, czas cyklu

-ęsD-

czng iwtaiaiiia ! cza* przetrzymania

zapis do pamięci

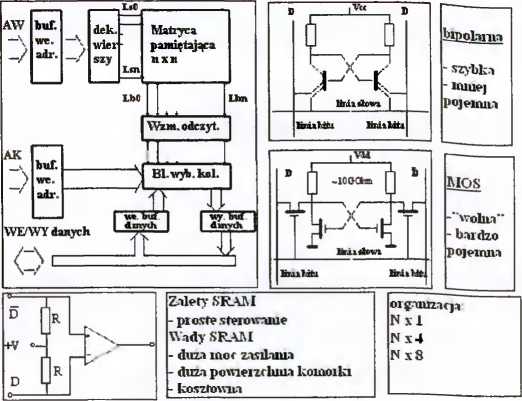

Organizacja i obsługa statycznej pamięci RAM

odczyt - jeden cyki pamięci: stabilny adres & transfer danych zapis - jeden cyki pamięci: stabiiny adres & transfer danych

Pamięć dynamiczna

• Odświeżanie pamięci DRAM

• Odświeżanie sygnałem RAS

Podawanie kolejnych adresów wierszy i w odpowiednim momencie stanu niskieeo RAS. CAS pozostaje w stanie wysokim (wyjście pamięci w stanie wysokiej imped.).

• Odświeżanie ukryte (wewn. licznik odświeżania pamięci)

Po operacji odczytu RAS ponownie zmienia stan na niski. CAS pozostaje w stanie niskim (jak dla odczytu). Odświeżany jest wiersz wskazywany przez wewn. licznik.

• Odświeżanie w trybie CAS przed RAS (wewn. licznik odświeżania pamięci) Cykl odświeżania rozpoczyna się, gdy CAS osiągnie stan niski odpowiednio wcześniej przed RAS i utrzyma ten stan odpowiednio długo. Zewnętrzny adres jest ignorowany, adres odświeżanego wiersza określa wewn. licznik. Wyjście pamięci jest w stanie wysokiej impedancji.

• Odświeżanie automaty czne (wewn. układ odświeżania)

Pamięci takie mają wyprowadzenie REF. Po każdym podaniu stanu niskieeo na REF - odświeżanie kolejnego wiersza.

Architektury pamięci

DRAM

RAS

CAS

ADR

DATA

RAS

-CAS

ADR

DATA

RAS

CAS

ADR

UATA

RAS

CAS

ADR

DATA

- Fast Page Modę, dostęp do kolejnych 4-ech komórek (tryb półbajtowy) - adr wiersza bez zmiany, zmiany adresów kolumn.

- Extended Data Out Memory, utrzymanie danej po zaniku adresu = możliwość adresowania kolejnej lokacji przed zakończeniem poprzedniego transferu

- Burst Extended Data Out Memory - zwłaszcza transfery blokowe, adres wiersza i kolumny tylko na początku bloku

Architektury pamięci

(synchronous DRAM) - synchronizacja wejścia i wyjścia, zwykle 4-banki pamięci, 25% szybsza od EDO, zwykle burst-mode; adresy na początku bloku, pozostałe -> domniemane (możliwość opuszczania elementów - DQM)

P (double-data ratę SDRAM), SDRAM II - szybsza wersja SDRAM umożliwiająca odczyt danych na obu zboczach CLK

® (Rambus™ DRAM) - zwiększona przepustowość wewnętrzna

(Syndink DRAM) - 16 banków pamięci, nowy interface i logika sterująca

i 5DRAM

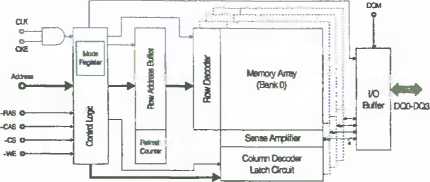

TMS 664414 (64 Mb)

• Multipieksowane ilnle adresów wierszy i kolumn.

• Oddzielne linie do adresowania banków (zwykle dołączane jako A12A13)

Architektury pamięci

kturo Jj DRAM

afCAŁUdwi-

■» to

II

I

|

Rozkaz |

-ca |

-RAS |

~CAS - |

CAS | |

|

Minie Register Sol |

0 |

0 |

0 0 |

V | |

|

Bunk Preehargi: |

0 |

0 |

1 0 |

HAS | |

|

‘At | |||||

|

Row Addrcs1 Łntry |

0 |

0 |

1 1 |

CS | |

|

Coluirm Adtirew fcniry Hejil |

0 |

1 |

0 1 |

Kil BSO (A13.A12) |

Hut l < a

*

CUCAS rrc-'-a

Architektura SDRAM

•Programowanie układu •Aktywacja/deaktywacja banków (wymagana przed podaniem nowego adresu wiersza)

|

Rozkaz |

-CS |

-RAS |

~CAS -WE |

BS1 BSO (A13j (A12J |

AU |

A10 |

A9 - AO |

|

Modę Register Scl |

0 |

» |

0 0 |

0 0 |

0 |

0 |

Register Scl Dulu w-O-0-13-12-1 l-a-bł-b2-bl |

|

Bank Prcchurjje |

0 |

0 |

1 0 |

Numer banku 00-BO 01 BI 10 b; 11 83 |

Bez znacz. |

0 |

bez zn uczeniu |

|

Row Adtlrc*! Entry |

0 |

0 |

t 1 |

Numer banku (M) BO 01: BI 10. B2 11 B3 |

Ml |

Mn |

r^-r8-i7-r6-r5-z4-r3- r2-?l-K) |

|

Colunw Addrets Enlry Kead |

0 |

1 |

0 1 |

Numer bunku 00: BO Ol BI ID- B2 UB3 |

Bez znacz |

0 |

c9-c8-c7-Ł6-c5-ł:4- c3-c2-el-c0 |

r

Architektury pamięci

Architektura DDRAM

-clk 1 ( i !; ) 1 > ( ? ; 7 f ; ‘ j | ; i 1

CLK f r ‘ • i i !■ ł i J ! > ‘ I "

CM W ADR

IXfo

DO

CL 2

l i i 1

I

•Operacje na narastającym i opadającym zboczu zegara •2 sygnały zegarowe

•Dwukierunkowy sygnał DOS (przy czytaniu sterowanie z modułu pamięci, faza CLK; przy wpisie sterowanie z zewnątrz, faza ~CLK

• Odrębny standard magistrali -kanał

• 2 kanały po 16 bitów

• Łańcuchowe połączenie modułów (zwory)

,r.vur. om !>f\ txwi< ion

'.•Wiln Ił » •’

0 '

inwvMii«

Ł

11 CK

tł

• ł*M -

• Struktura wewnętrzna pamięci - 32 banki x 128 bitów (taktowanie wew. 100 MHz -> 1.6GBps)

• Na styku z magistralą - multipleksery dopasowują do szerokości 16bitów (400 MHz x 16b -» 1.6GBps)

Organizacja modułu pamięci

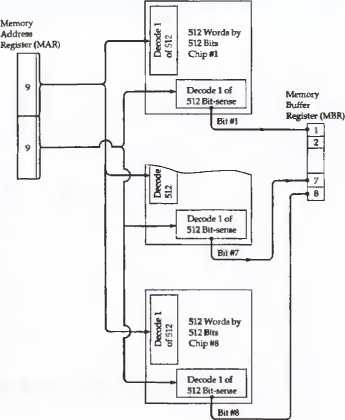

Jeśii mikroukład RAM zawiera tyiko i bit na słowo, potrzeba przynajmniej iiczby mikroukładów równej iiczbie bitów w słowie. Na rysunku jest pokazane przykładowo, jak może być zorganizowany moduł pamięci zawierający 256 K siów 8-bitowych. W przypadku 256 K stów wymagany jest adres 18-bitowy; jest on dostarczany do modułu z pewnego źródia zewnętrznego (np. z linii adresowych magistraii, do której moduł jest dołączony). Adres jest doprowadzany do 8 mikroukładów 256 K x i, z których każdy umożliwia wejście/ wyjście i bitu.

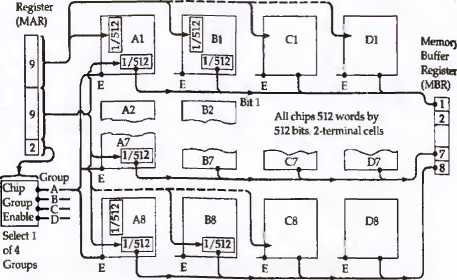

Organizacja modułu 1M

Na rysunku jest pokazana możliwa organizacja pamięci składającej się z I M siów 8-bitowych. W tym przypadku występują 4 kolumny mikroukładów; każda kolumna zawiera 256 K słów uporządkowanych w sposób pokazany na poprzedniej foiii. W przypadku i M siów wymaganych jest 20 iinii adresowych. Osiemnaście najmniej znaczących bitów doprowadza się do wszystkich 32

modułów. Dwa najbardziej znaczące bity są doprowadzone do moduiu iogicznego wyboru grupy, który wysyia sygnai Uaktywnienia mikroukładu do jednej z 4 kolumn moduiów.

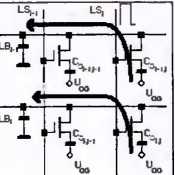

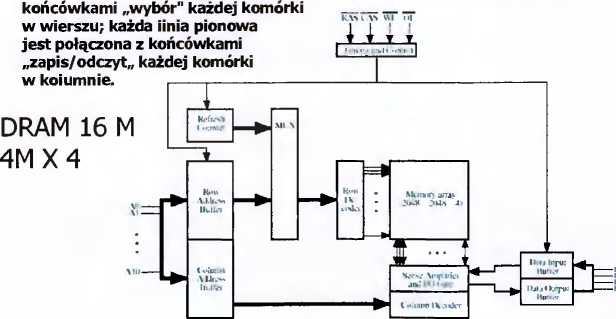

Jednocześnie mogą być odczytywane iub zapisywane 4 bity. Logicznie rzecz biorąc, zespół pamięci jest zorganizowany w postaci 4 kwadratowych układów 2048 na 2048 elementów. Możiiwe są różne organizacje fizyczne. W każdym przypadku eiementy zespołu są połączone zarówno przez linie poziome (wiersze), jak i pionowe (koiumny). Każda iinia pozioma jest połączona z

Memory

Address

Bit 8

Pamięć stata

|

A\V ~\ |

flek. \>1ei szy |

Ln |

Matryca piunlętnjłjcn U XII |

|

AK |

LWI |

-1-1_; | |

|

\ V |

BI. wyli. kol. -n- | ||

\VY danych

MROM- maska PROM - pi o&i amow.mle I raz _(przepalanie)_

ZX*7.

|

LB, |

“ml | |

|

Tc |

Vcc |

Pmnifć MROM lub PROM

EPRt)M - kasowanie ptoin.

ultrafioletowym Flasli EPROM kasowanie elektryczne (szybkie) EEPROM - zapis bez kasowania

, dekoder może , a następnie ewentualnie

niektóre kombinacje błędów.

Proces ten ma charakter stochastyczny -

Pe dowolnie bliskie 1, gdy odpowiednio duży nadmiar.

Korekcja błędów

W systemach pamięci półprzewodnikowych występują błędy. Można je podzieiić na błędy stałe i przypadkowe.

O Błąd stały jest permanentnym defektem fizycznym powodującym, że uszkodzona komórka iub komórki pamięciowe nie są w stanie niezawodnie przechowywać danych, iecz pozostają w stanie 0 iub i, aibo błędnie przeskakują między 0 a 1.

8łąd przypadkowy jest iosowym i nieniszczącym zjawiskiem, które zmienia zawartość jednej iub wielu komórek pamięciowych, bez uszkadzania samej pamięci.

Zarówno błędy stałe, jak i przypadkowe są oczywiście niepożądane i większość współczesnych systemów pamięci głównych zawiera układy iogiczne wykrywające i korygujące błędy.

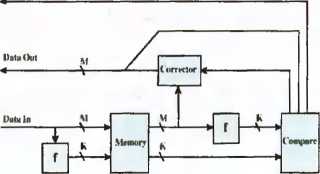

Kody korekcyjne

Krnir NątnJ

Gdy dane mają być wczytane do pamięci, przeprowadza się na tych danych obiiczenia, okreśiane jako funkcja/, w ceiu utworzenia kodu do korekty błędów. Zarówno kod, jak i dane są przechowywane. W rezuitacie, jeśli ma być zapisane danych, a , to aktuaina

Gdy uprzednio zmagazynowane słowo jest odczytywane, kod jest wykorzystywany do wykrywania i ewentuainej korekty błędów. Generowany jest nowy zestaw K bitów kodowych z M bitów danych, po czym porównuje się go z pobranymi bitami kodowymi. Porównanie prowadzi do jednego z trzech wyników:

• Nie wykryto żadnych błędów. Pobrane bity danych są wysyłane.

4 Wykryto błąd, którego korekta jest możiiwa. Bity danych i bity korekty błędu są doprowadzane do układu korektora, który tworzy poprawiony zestaw M bitów przeznaczony do wysłania.

4 Wykryto błąd niemożiiwy do

poprawienia. Stan ten jest zgłaszany.

i

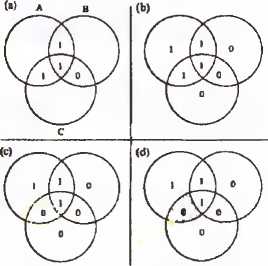

• W przypadku trzech krzyżujących się okręgów mamy do czynienia z siedmioma przedziałami.

I

(a).

< I Pozostałe przedziały są wypełniane tzw. bitami parzystości.

ił Jeśii teraz błąd spowoduje zmianę jednego z bitów danych (c), jest on łatwy do wykrycia.

A i C, aie nie w B.

M=4

# Tyiko jeden z 7 przedziałów znajduje się w A i C, aie nie w B. Błąd może więc być poprawiony przez zmianę tego bitu (d).

Kod korekcyjny dla 8 bitów - cz.ll

j (-Słowo zawierające . Zazwyczaj

generuje się syndrom 4-bitowy o następujących własnościach:

^ Jeśii syndrom zawiera

t

I

Jeśii syndrom zawiera

. Wówczas korekta jest niepotrzebna.

Jeśii syndrom zawiera inwersji tego bitu.

Korekta poiega na

H W celu uzyskania takich własności bity danych i

I

bity kontroine są aranżowane w postaci słowa 12-bitowego w sposób pokazany obok. Pozycje bitowe są ponumerowane od 1 do 12.

|

12 |

1 |

1 |

0 |

0 |

M8 | |

|

II |

I |

0 |

1 |

I |

M7 | |

|

10 |

1 |

0 |

I |

0 |

M6 | |

|

9 |

1 |

0 |

0 |

I |

M5 | |

|

R |

1 |

o |

0 |

o |

08 | |

|

7 |

0 |

1 |

1 |

1 |

M4 | |

|

6 |

0 |

1 |

1 |

0 |

M3 | |

|

5 |

0 |

1 |

0 |

1 |

M2 | |

|

4 |

0 |

I |

0 |

0 |

C4 | |

|

3 |

0 |

0 |

1 |

1 |

Ml | |

|

2 |

0 |

0 |

1 |

0 |

C2 | |

|

1 |

0 |

0 |

0 |

1 |

Cl |

Kod korekcyjny dla 8 bitów - cz.l

Należy opracować kod, który może posłużyć do wykrycia i skorygowania 1-bitowego błędu w słowach 8-bitowych

11 Wymagana długość kodu wynika z przedstawionego wcześniej rysunku działania kodu korekcyjnego. Układy iogiczne porównujące otrzymują na wejściu dwie wartości K bitowe. Porównanie bit po bicie jest przeprowadzane przy użyciu bramki LUB wyłączne (exc!usive-or = EXOR) o 2 wejściach. Wynik jest okreśiany jako słowo- . Tak więc, każdy

41 Słowo- ma więc K bitów i zakres wartości 2K (pomiędzy 0

a 2K - 1).

zaś 2K - 1 wartości służy do wskazania błędu i jego iokaiizaęji bitowej. Ponieważ błąd może wystąpić w każdym z M bitów danych i K bitów kontroinych,

2K -1 >M + K

Równanie to określa iiczbę bitów wymaganą do skorygowania błędu 1-bitowego w słowie zawierającym M bitów danych.

Konstruowanie kodu - cz.lll

1 l»

jk Bity kontroine są obliczane następująco (symboi ® oznacza operację LUB ^ wykluczające (EXOR)):

Cl = Ml ® M2 ® M4 ® M5 ® M7

0 o <

1 ■

1 o

C2 = Ml ® M3 ® M4 ® M6 ® M7 C4 = M2 ® M3 ® M4 ® M8

C8 = M5 ® M6 ® M7 ® M8

Każdy bit kontrolny działa na każdej pozycji bitu danych, której numer zawiera 1 w odpowiedniej pozycji kolumny. Tak więc pozycje bitowe danych ; pozycje bitowe

; pozycje bitowe , a pozycje bitowe

. Inaczej mówiąc, pozycja bitowa n jest sprawdzana przez

bity C, takie, że

Z/=,?

TNa przykład pozycja 7 jest sprawdzana przez bity znajdujące się na pozycjach 4, 2 i 1; zachodzi więc 4 + 2 + 1=7.

Kody SEC-DEC

Błąd!!!

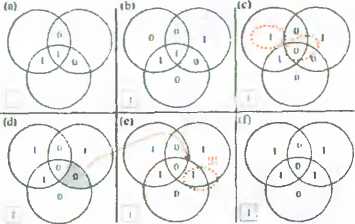

Opisany na wcześniejszych foliach kod jest znany jako kod poprawiania pojedynczego błędu (ang. singte-error-correcting -). Najczęściej jednak pamięć półprzewodnikowa jest wyposażana w kod poprawiania pojedynczego i wykrywania podwójnego błędu ( ). W

przytoczonej tabeli, takie kody wymagają jednego dodatkowego bit w porównaniu z kodami SEC.

Na rysunku jest pokazane, jak działa taki kod, znów dia przypadku 4-bitowego słowa danych. Przedstawiona sekwencja ujawnia, że jeśli występują dwa błędy (c), procedura kontroina jest błędna i pogarsza probiem, tworząc trzeci błąd (e). W celu pokonania tej trudności, dodany jest ósmy bit, taki że całkowita liczba jedynek na wykresie jest parzysta. Dodatkowy bit parzystości umożliwia wychwycenie błędu (f)-

|

Liczba bitów danych |

Poprawianie pojedynczego błędu |

Poprawianie pojedynczego błędu, | ||

|

Bity kontrolne |

% wzrostu |

Bity kontrolne |

% wzrostu | |

|

8 |

4 |

50 |

5 |

62,5 |

|

16 |

5 |

31,25 |

6 |

37,5 |

|

32 |

6 |

1B,75 |

7 |

21,B75 |

|

64 |

7 |

10,94 |

B |

12,5 |

|

128 |

8 |

6,25 |

9 |

7,03 |

|

256 |

9 |

3,52 |

10 |

3,91 |

Czytanie z SDRAM

Wyszukiwarka

Podobne podstrony:

wykl02c Wykład 3Pamięć systemu komputerowego Bp Właściwości pamięci w SK Złożone zagadnienia

wykl02 Wykład 3Pamięć systemu komputerowego Właściwości pamięci w SK Złożone zagadnienia pamięci

Wykład 7Bezpieczeństwo systemów komputerowych Integralność i uwierzytelnianie danych - główne

SWB - Systemy wbudowane - wprowadzenie - wykład 9a®zElementy składowe systemu komputerowego Pamię

44371 so egz 3 10. (1 pkt.) W systemie komputerowym czas dostępu do pamięci główne

W8 Architektura systemów komputerowych: Pamięci ROM i RAM- podział, budowa i zasada

Architektura Systemów Komputerowych • ••• •Bezpośredni dostęp do pamięci •Realizacja

16 Laboratorium Administrowania Systemami Komputerowymi - DNS.pdf Zadanie nr 2 - Serwer nazw z pamię

WSTiE rggigOrganizacja systemu komputerowego » Centralnym elementem jest pamięć operacyjna •

p1020931 (2) Urządzenia we-wy System komputerowy Pamięć Sterowniki

P0410090001 II Tematyka wykładu II. Historia rozwoju systemów komputerowych 2 Miizyry von Neumanna 3

p1020995 Organizacja systemów komputerowych Listy rozkazów: właściwości i funkcje Wykład: 4X11.2008

13819 p1030012 Organizacja systemów komputerowychArchitektury i rodzaje procesorów Jak usprawniać pr

więcej podobnych podstron