3818438038

Katedra Inżynierii Komputerowej

ly laboratoryjnej

Laboratorium Elektrotechniki i Elektroniki Sprawozdanie z ćwiczenia

Inwerter scalony CMOS

sprawozdania

zajęć

Poniedziałek 8

Rok/semestr/g

Rok 2!, S grft-

1. Wprowadzenie

Ćwiczenie ma na celu zapoznanie się z działaniem inwertera scalonego CMOS oraz zmierzenie jego najważniejszych parametrów.

1.1.Wiadomości teoretyczne

Bramka logiczna

Bramka logiczna - element konstrukcyjny maszyn i mechanizmów (dzi ś zazwyczaj: układ scalony, choć podobne funkcje można zrealizować równie ż za pomocą innych rozwiązań technicznych, np. hydrauliki czy pneumatyki), realizujący fizycznie pewną prostą funkcję logiczną, której argumenty (zmienne logiczne) oraz sama fun keja mogą przybierać jedną

z dwóch warto ści, np. 0 lub 1 (zob. algebra Boole'a).

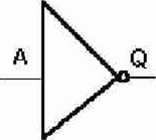

Inwerter (bramka NOT)

Jest to układ cyfrowy, bramka logiczna wykonuj ąca logiczną negaq ę [~j.

Inwerter

Inwerter CMOS

Podstawową struktura każdego układu

|

Ti | |

|

1 |

0 |

|

0 |

1 |

CMOS jest para

komplementarna,

która jednoczę śnie stanowi układ realizujący negację sygnału wej ściowego, czyli jest funktorem NOT. Bardziej złożone bramki (NAND, NOT) są kombinacją

Wyszukiwarka

Podobne podstrony:

Katedra Inżynierii Komputerowej o 9 y laboratoiyjnej Laboratorium Elektrotechniki i Elektroniki

KATEDRA INŻYNIERII KOMPUTEROWEJ I ELEKTRYCZNEJKIERUNKI PRAC ROZWOJOWO-BADAWCZYCH KATEDRY TEL: 81 538

Katedra Inżynierii Komputerowej Politechnika CzęstochowskaTrasowanie i protokół OSPF Laboratorium

Katedra Inżynierii Komputerowej Laboratorium z Informatyki - semestr IICel i zakres zajęć: Głównym c

Katedra Inżynierii KomputerowejLaboratorium Prototypowania Obwodów Drukowanych W skład laboratorium

POLITECHNIKA GDAŃSKA KATEDRA INŻYNIERII MATERIAŁOWEJ WYTWARZANIE POWŁOK METODĄ ELEKTROLITYCZNĄ I

IV. Wydział Inżynierii Produkcji i Logistyki 1. Katedra Inżynierii i Bezpieczeństwa Pracy Laboratori

Politechnika Koszalińska WEil Katedra Inżynierii Komputerowej [KIK)Tematy projektów aplikacjibazodan

Elektronika - laboratorium Katedra Architektury Komputerów i Telekomunikacji Zakład Systemów i

SCHODOWA SCHODOWA Lokalizacja laboratoriów komputerowych Instytutu Informatyki w Gmachy Elektroniki

KLATKA KLATKA Lokalizacja laboratoriów komputerowych Instytutu Informatyki w Gmachy Elektroniki - we

więcej podobnych podstron