diod pó³przewodnikowych spolaryzowanych

w kierunku przewodzenia, mo¿na uzyskaæ

urz¹dzenia charakteryzuj¹ce siê bardzo

ma³¹ wartoci¹ wspó³czynnika temperaturo-

wego. Z rys. 2 wynika, ¿e je¿eli bezwzglêd-

ne wartoci zmian napiêcia na diodzie spo-

laryzowanej w kierunku przewodzenia i dio-

dzie Zenera o dodatnim wspó³czynniku tem-

peraturowym s¹ takie same przy zmianie

temperatury od 25 do 100

o

C, wówczas na-

piêcie na zaciskach przedstawionego zesta-

wu bêdzie takie samo, zarówno dla tem-

peratury 25, jak i 100

o

C, poniewa¿ jego

spadek na diodzie pó³przewodnikowej spo-

laryzowanej w kierunku przewodzenia zosta-

nie ca³kowicie skompensowany wzrostem

napiêcia na zaciskach diody Zenera. Je¿e-

li dodatkowo, szybkoæ zmian napiêcia na

diodzie spolaryzowanej w kierunku prze-

wodzenia jest taka sama, jak szybkoæ

zmian napiêcia na diodzie Zenera, wów-

czas napiêcie na zaciskach zestawu pozo-

stanie sta³e w ca³ym zakresie temeperatu-

ry od 25 do 100

o

C. Niestety, w praktyce

okazuje siê, ¿e termiczne zale¿noci na-

piêæ na diodzie pó³przewodnikowej spolary-

zowanej w kierunku przewodzenia i diodzie

Zenera spolaryzowanej w kierunku zaporo-

wym, wykazuj¹ znaczn¹ nieliniowoæ.

W zwi¹zku z powy¿szym dok³adne dopaso-

wanie charakterystyk termicznych obu urz¹-

dzeñ nie jest mo¿liwe i zawsze ród³o napiê-

cia referencyjnego bêdzie wykazywa³o choæ-

by minimaln¹ zale¿noæ napiêcia wyjciowe-

go od temperatury.

Na rys. 3 zamieszczono schemat zestawu,

stanowi¹cego szeregowe po³¹czenie diody

Zenera z dwiema diodami pó³przewodniko-

wymi spolaryzowanymi w kierunku przewo-

dzenia. Zwykle diody referencyjne s¹ urz¹-

dzeniami dostarczaj¹cymi stabilnych napiêæ

o niewielkich wartociach, w których stosowa-

ne s¹ diody Zenera o napiêciach przebicia la-

winowego od 6 do 8 V. W takim wypadku,

w celu kompensacji termicznej napiêcia wyj-

ciowego wystarczy u¿ycie jednej b¹d

dwóch diod pó³przewodnikowych spolary-

zowanych w kierunku przewodzenia.

n

Miros³aw Gajer

Opracowano na podstawie:

TVS/Zener _ Device Data, materia³y firmy Motorola

DEL150/D, REV 1, 1997

+

_

Diody pó³przewodnikowe

ze z³¹czem PN

Dioda Zenera

Rys. 3. Przyk³ad zestawu stanowi¹cego po³¹czenie

diody Zenera z dwiema diodami

pó³przewodnikowymi spolaryzowanymi

w kierunku przewodzenia

PROCESORY SYGNA£OWE

DLATELEKOMUNIKACJI

(2)

Przegl¹d architektury

uk³adu `C64x

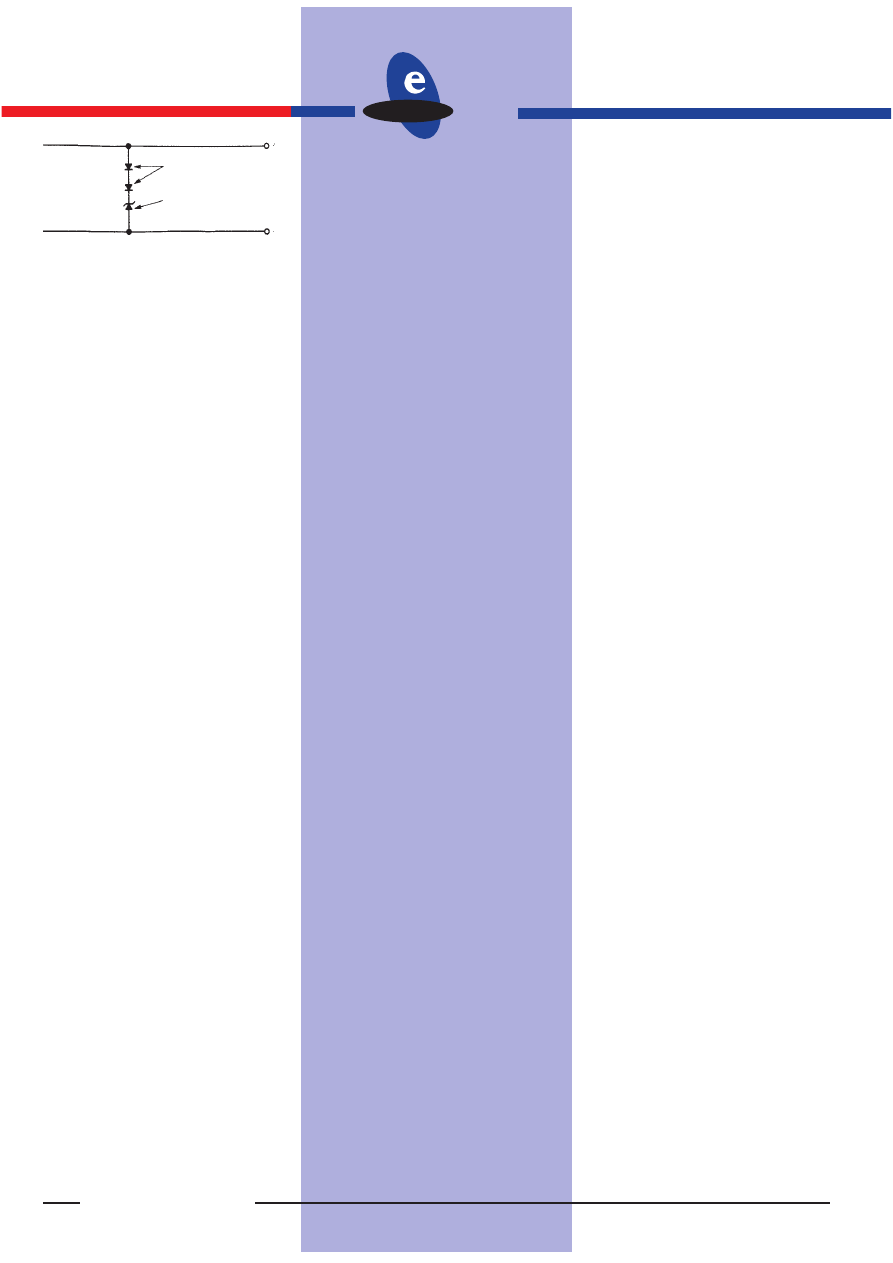

Na jednostkê centraln¹ procesorów serii

`C6000 sk³adaj¹ siê nastêpuj¹ce elementy:

q

dwa pliki rejestrów ogólnego przeznacze-

nia (A i B)

q

osiem jednostek funkcjonalnych (L1, L2,

S 1, S2, M 1, M2, D1 i D2)

q

dwie magistrale s³u¿¹ce do odczytu

danych z pamiêci (LD1 i LD2)

q

dwie magistrale s³u¿¹ce do zapisu

danych do pamiêci (STl i ST2)

q

dwie magistrale adresowe i danych (DA 1

i DA2)

q

dwie magistrale s³u¿¹ce do odczytu plików

rejestrowych, nale¿¹cych do s¹siedniego to-

ru przetwarzania danych (data cross paths)

(1X i 2X).

Architektura jednostki centralnej procesora

`C64x zosta³a przedstawiona na rys. 2. W to-

rach przetwarzania danych procesora `C6000

istniej¹ dwa pliki rejestrów ogólnego prze-

znaczenia (A i B). W przypadku plików reje-

strów procesorów `C62x/`C67x ka¿dy z plików

zawiera po 16 rejestrów 32-bitowych. Rejestry

ogólnego przeznaczenia mog¹ zostaæ wy-

korzystane do przechowywania danych,

wskaników do danych lub flag s³u¿¹cych

do sterowania przebiegiem wykonywaniem

programu. W przypadku procesora `C64x zo-

sta³a podwojona liczba rejestrów ogólnego

przeznaczenia. Rejestry A0, Al, A2, B0, B 1

i B2 mog¹ zostaæ wykorzystane jako rejestry

flagowe. Ponadto rejestry A4-A7 i rejestry

B4-B7 mog¹ zostaæ wykorzystane do adreso-

wania cyklicznego.

W przypadku procesorów `C62x/C67x

w rejestrach mog¹ byæ przechowywane da-

ne sta³oprzecinkowe o rozmiarach od 16 bi-

tów do 40 bitów oraz 64-bitowe dane zmien-

noprzecinkowe. Dane o rozmiarach wiêk-

szych ni¿ 32 bity s¹ przechowywane w pa-

rach rejestrów, przy czym 32 najmniej znacz¹-

ce bity (LSB) s¹ przechowywane w rejestrach

o numerach parzystych, natomiast pozosta-

³e 8 b¹d 32 najbardziej znacz¹ce bity (MSB)

s¹ przechowywane w rejestrach o nume-

rach nieparzystych.

Z kolei w rejestrach procesora `C64x mog¹

byæ przechowywane wszystkie wy¿ej wymie-

nione typy danych i dodatkowo 8-bitowe da-

ne upakowane oraz 64-bitowe dane sta³o-

przecinkowe. Dane upakowane obejmuj¹

cztery wartoci 8-bitowe b¹d dwie wartoci

16-bitowe zapisane w pojedynczym rejestrze

32-bitowym lub cztery wartoci 16-bitowe

umieszczone w 64-bitowej parze rejestrów.

Osiem jednostek funkcjonalnych procesorów

`C6000 mo¿e zostaæ podzielonych na dwie

grupy, po cztery jednostki w ka¿dym z torów.

Jednostki funkcjonalne w pierwszym torze

przetwarzania danych s¹ prawie identyczne

z jednostkami toru drugiego.

Kod obiektowy dla procesora `C64x jest kom-

patybilny z kodem procesora `C62x. Procesor

`C64x poza mo¿liwoci¹ wykonywania wszy-

stkich instrukcji procesora `C62x ma wiele

8- i 16-bitowych rozszerzeñ zbioru instrukcji.

Dla przyk³adu instrukcja MPYU4 wykonuje

cztery mno¿enia 8-bitowe w jednym cyklu

zegarowym w jednostce M. Z kolei instrukcja

ADD4 wykonuje cztery dodawania liczb 8-bi-

towych jako jedna instrukcjê w jednostce L.

Ka¿da z jednostek funkcjonalnych dokonuje

bezporednich zapisów i odczytów z reje-

strów zawartych w pliku rejestrowym. Jed-

nostki funkcjonalne L1, S1, D1 i M1 dokonu-

j¹ zapisów i odczytów pliku rejestrowego A.

Z kolei jednostki L2, S2, D2 i M2 operuj¹ na

pliku rejestrowym B.

Wiêkszoæ magistral jednostki centralnej

umo¿liwia przesy³anie operandów 32-bito-

wych, a dodatkowo niektóre z nich umo¿liwia-

j¹ transmisjê danych 40- i 64-bitowych. Ka¿-

da z jednostek funkcjonalnych ma swój 32-bi-

towy port umo¿liwiaj¹cy zapis danej do pliku

rejestrowego. Ka¿da z jednostek funkcjonal-

nych ma dwa 32-bitowe porty umo¿liwiaj¹ce

odczyt operandów ród³owych scr1 i scr2.

Cztery jednostki L1, L2, S1 i S2 maj¹ dodat-

kowe 8-bitowe porty umo¿liwiaj¹ce zapis i od-

czyt danych 40-bitowych. Poniewa¿ ka¿da

z jednostek funkcjonalnych ma swój 32-bito-

wy port s³u¿¹cy do zapisu wyników do pliku

rejestrowego, wszystkie osiem jednostek mo-

¿e pracowaæ równolegle, dostarczaj¹c w jed-

nym cyklu zegarowym omiu ró¿nych wyni-

ków. Poniewa¿ uk³ad mno¿¹cy mo¿e dostar-

czaæ 64-bitowe wyniki wykonanych operacji,

zosta³ wyposa¿ony w 32-bitowy port zapisu

pliku rejestrowego.

Pliki rejestrowe s¹ tak¿e po³¹czone z jedno-

stkami funkcjonalnymi le¿¹cymi w s¹siednim

torze przetwarzania danych. Celowi temu

s³u¿¹ magistrale 1X i 2X. Pierwsza umo¿liwia

jednostkom funkcjonalnym z toru A odczyt

32-bitowego argumentu z pliku rejestrowego

toru B. Podobnie magistrala 2X umo¿liwia

jednostce funkcjonalnej z toru B odczyt reje-

stru w torze A.

W przypadku procesora `C64x wszystkie

osiem jednostek funkcjonalnych ma dostêp do

rejestrów w s¹siednim torze przetwarzania da-

nych. Wejcia scr2 jednostek M l, M2, S l, S2,

D I i D2 mog¹ byæ dodatkowo wybierane po-

Radioelektronik Audio-HiFi-Video 3/2002

28

miêdzy plikami rejestrów nale¿¹cych do w³a-

snego b¹d s¹siedniego toru przetwarzania

danych. W przypadku jednostek L1 i L2 mo¿-

liwoæ wyboru istnieje zarówno w przypadku

argumentu ród³owego src 1 jak i src2.

W przypadku wczeniejszych wersji

procesorów `C62x1`C67x tylko szeæ jedno-

stek funkcjonalnych mia³o zdolnoæ siêgania

do s¹siedniego pliku rejestrów.

Multipleksowane magistrale adresowe i da-

nych oznaczone DA1 i DA2 maj¹ po³¹czenia

z jednostkami D w obu torach przetwarzania

danych. W zwi¹zku z tym instrukcje zapisu

b¹d odczytu danych z pamiêci zewnêtrznej

mog¹ wykorzystywaæ do zaadresowania ko-

mórki pamiêci zawartoci rejestrów z jedne-

go toru danych, a wynik umieciæ w rejestrze

nale¿¹cym do s¹siedniego toru danych. Istnie-

j¹ cztery 32-bitowe cie¿ki zapisu danych

z zewnêtrznej pamiêci do plików rejestro-

wych. Dla toru Amagistrala LD1a s³u¿y do od-

czytu 32 MSB danych z pamiêci, natomiast 32

LSB s¹ przesy³ane magistral¹ LD1b. W torze

A magistrala ST1a s³u¿y do zapisu 32 LSB,

a ST1b do zapisu 32 MSB.

Unikatowe cechy procesora `C64x

Procesor `C64x ma najwiêksz¹ moc oblicze-

niow¹ sporód wszystkich wykorzystywa-

nych w dziedzinie cyfrowego przetwarzania

sygna³ów. Taktowany z czêstotliwoci¹ 1,1

GHz jest w stanie wykonaæ prawie 9 miliardów

instrukcji w ci¹gu jednej sekundy.

Rozszerzenia architektury VelociTL2 i wiêk-

sza czêstotliwoæ taktowania podnios³y wydaj-

noæ obliczeniow¹ w stosunku do architektu-

ry VelociTl procesorów `C62x1`C67x 8-krot-

nie w zastosowaniach telekomunikacyjnych

i 15-krotnie w dziedzinie przetwarzania i ana-

lizy obrazów.

Do unikatowych cech procesora `c64xzalicza siê:

q

wzbogacenie plików rejestrowych,

q

rozszerzenie torów przetwarzania danych,

q

przetwarzanie danych upakowanych,

q

dodatkowe jednostki funkcjonalne,

q

zwiêkszon¹ ortogonalnoæ.

Wzbogacenie plików rejestrowych

q

Podwojenie rozmiarów plików rejestro-

wych. Procesor `C62x mia³ 32 rejestry ogól-

nego przeznaczenia, natomiast procesor

`C64x ma ju¿ 64 rejestry.

q

Procesor `C62x wykorzystuje rejestry A1,

A2, B0, B1 i B2 do wykonywania operacji

warunkowych (condition registers); procesor

`C64x mo¿e wykorzystaæ w tym celu dodat-

kowo rejestr A0.

q

Procesor `C62x mo¿e przetwarzaæ dane

32- i 40-bitowe oraz 16-bitowe dane upakowa-

ne, a `C64x mo¿e dodatkowo przetwarzaæ

upakowane dane 8-bitowe i 64-bitowe,

Rozszerzenie torów przetwarzania danych

q

Ka¿da z jednostek D mo¿e dokonywaæ od-

czytu b¹d zapisu danych 64-bitowych w jed-

nym cyklu instrukcji, wczeniejsza wersja by-

³a pozbawiona tej mo¿liwoci.

q

Jednostka D mo¿e pozyskaæ operand

z s¹siedniego toru przetwarzania danych.

W przypadku procesora `C62x jedynie jedno-

stki L, M i S mia³y tak¹ mo¿liwoæ.

q

W przypadku procesora `C64x dostêpy

do danych z s¹siedniego toru przetwarzania

s¹ umieszczane w potoku (pipelining), rozwi¹-

r

TELEKOMU

NIKCJA

S1 S2 D DL SL

L1

SL DL S1 S2

S1

DL D S1 S2

M1

D S1 S2

D1

S2 S1 D

D2

S2 S1 DL D

M2

S2 S1 D DLSL

S2

SL DLD S2 S1

S2

Rejestry A0-A31

Rejestry B0-B31

Rys. 2. Architektura jednostki

centralnej procesora `C64x

L1

L2

L1P

16 KB

L1D

16 KB

Procesor

TMS320C64xx

128 KB

odwzorowanej

pamiêci RAM

96 KB

odwzorowanej

pamiêci RAM

jednodro¿na

pamiêæ cache

32 KB

dwudro¿na

pamiêæ cache

64 KB

trzydro¿na

pamiêæ cache

96 KB

czterodro¿na

pamiêæ cache

128 KB

64 KB

odwzorowanej

pamiêci RAM

32 KB

odwzorowanej

pamiêci RAM

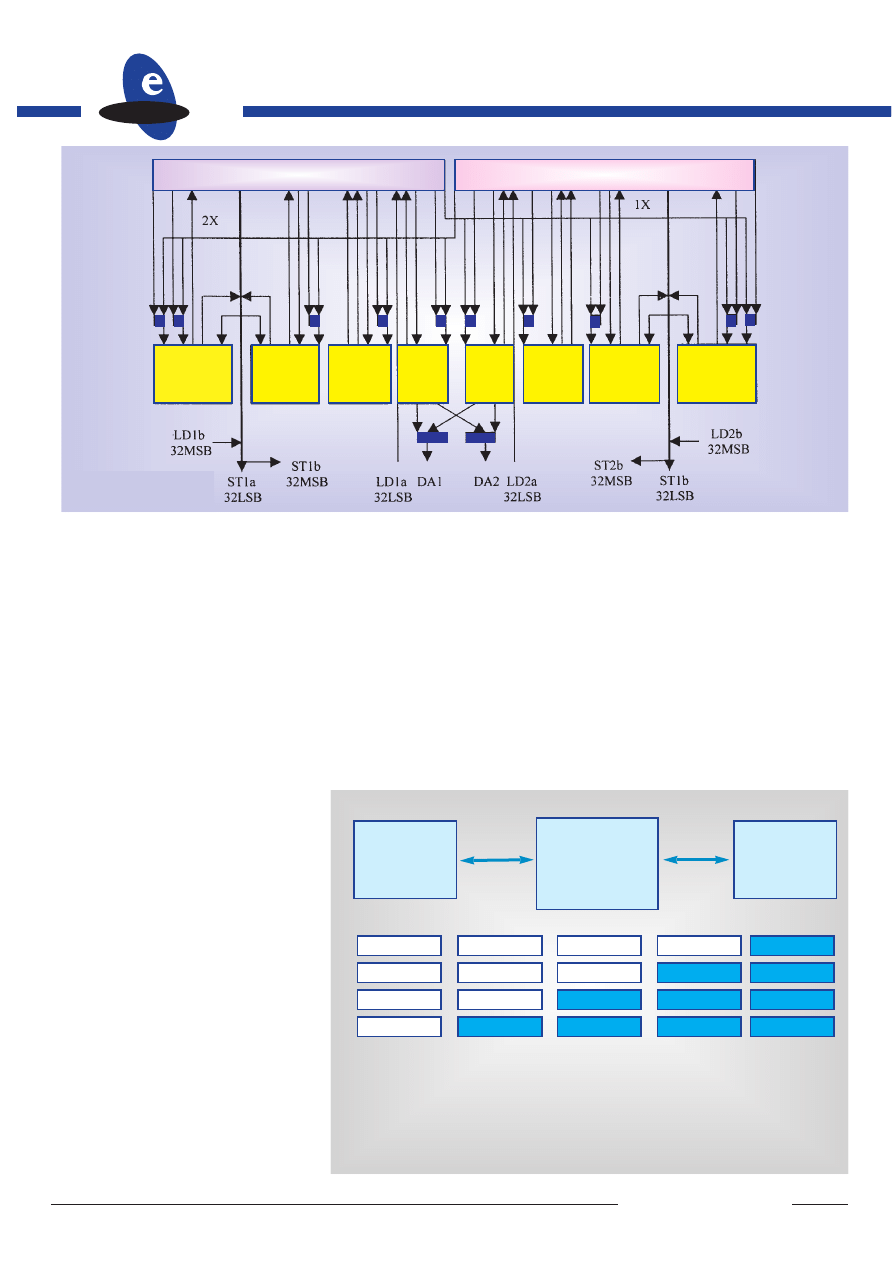

Rys. 3. Organizacja pamiêci podrêcznych procesora serii TMS320C64xx

Radioelektronik Audio-HiFi-Video 3/2002

29

zanie takie umo¿liwia dostêp do tej samej danej wielu jednostkom funkcjo-

nalnym; w przypadku procesora `C62x tylko jedna jednostka funkcjonalna

mog³a uzyskaæ taki dostêp.

Przetwarzanie danych upakowanych

q

Zosta³y dodane instrukcje, które operuj¹ bezporednio na danych upako-

wanych, co istotnie wp³ywa na szybkoæ realizacji programu. Procesor

`C64x zawiera bogaty zestaw instrukcji operuj¹cych na danych 8- i 16-bitowych.

q

Procesor `C64x wyposa¿ono w rozszerzony zestaw instrukcji upakowy-

wania i rozpakowywania danych, co znacznie u³atwia manipulacjê typami

danych upakowanych.

Dodatkowe jednostki funkcjonalne.

q

Ka¿da z jednostek M jest w stanie wykonaæ dwie operacje mno¿enia

danych 16-bitowych b¹d cztery operacje mno¿enia danych 8-bitowych.

q

Jednostka D mo¿e odczytywaæ argumenty 32- i 64-bitowe umieszczo-

ne pod dowolnym adresem, adresy nie musz¹ byæ wyrównane (non-aligned)

do granic s³ów (words) b¹d s³ów podwójnych (double words). Takiej mo¿-

liwoci by³ pozbawiony uk³ad `C62x.

q

Jednostka M zosta³a wyposa¿ona w mo¿liwoæ realizacji operacji prze-

suniêæ dwukierunkowych o zmienn¹ liczbê bitów (bi-directional variable shi-

fts). Cecha ta znajduje bezporednie zastosowanie podczas realizacji al-

gorytmów kompresji sygna³u mowy.

q

Jednostka L ma mo¿liwoæ wykonywania operacji odejmowania da-

nych 8-bitowych i jednoczesnego wyznaczania bezwzglêdnej wartoci wy-

niku. Ta w³aciwoæ znajduje zastosowanie podczas realizacji algorytmów

estymacji ruchu.

q

Do zbioru instrukcji wykonywanych przez jednostkê M dodano instruk-

cje SHFL,DEAL oraz GMPY4, które znajduj¹ powszechne zastosowanie

w kodowaniu z korekcja b³êdów (error-correcting codes).

q

Urz¹dzenia sprzêtowe s³u¿¹ce do zliczania bitów i ich rotacji, w które wy-

posa¿ono jednostkê M, umo¿liwiaj¹ realizacjê algorytmów operuj¹cych na

poziomie poszczególnych bitów, takich jak operacje morfologiczne binarnych

obrazów, pomiary cech obiektów oraz kodowanie obrazów.

Zwiêkszona ortogonalnoæ

q

Zarówno jednostka D jak i jednostki S i L s¹ w stanie wykonywaæ instruk-

cje operacji logicznych na danych 32-bitowych.

q

Jednostka D umo¿liwia bezporednia realizacjê operacji zapisu i odczy-

tu danych 64-bitowych; `C62x nie mia³ takiej mo¿liwoci, a `C67x umo¿li-

wia³ jedynie bezporedni odczyt danych 64-bitowych.

q

Jednostki L i D mog¹ zostaæ u¿yte do generacji 5-bitowych sta³ych, a do-

datkowo jednostka S mo¿e zostaæ wykorzystana do generacji sta³ych 16-

bitowych.

q

Procesor `C62x umo¿liwia do czterech odczytów danego rejestru w da-

nym cyklu zegarowym, `C64x nie ma takich ograniczeñ.

q

Procesor `C62x umo¿liwia³ w jednym cyklu zegarowym odczyt i zapis jed-

nego s³owa 32-bitowego, natomiast `C64x mo¿e zapisywaæ b¹d odczyty-

waæ dwa takie s³owa.

Dwupoziomowa architektura pamiêci podrêcznej _ cache

Jednostka centralna CPU ma bezporednie po³¹czenie z pamiêciami

podrêcznymi programu L1P oraz danych L1D, z których ka¿da ma pojem-

noæ 16 kB. Pamiêci te pracuj¹ z pe³n¹ szybkoci¹ taktowania procesora. Z ko-

lei pamiêæ drugiego poziomu L2, która jest pamiêci¹ podrêczn¹, przeznaczo-

n¹ do przechowywania zarówno danych jak i programu, umo¿liwia znacz-

n¹ elastycznoæ w jej u¿ytkowaniu. Przyk³adowo na rys. 3 przedstawiono przy-

k³adow¹ pamiêæ podrêczn¹ L2 o pojemnoci 128 kB (rozmiary tej pamiêci

mog¹ siê ró¿niæ w zale¿noci od typu procesora rodziny TMS320C64xx). Czte-

rodro¿na pamiêæ L2 mo¿e zostaæ skonfigurowana jako pamiêæ podrêczna

b¹d jako pamiêæ RAM, odwzorowuj¹ca wybrany obszar pamiêci danych lub

programu (mapped RAM). Zmieniaj¹c sposób, w jaki pamiêæ ta zostaje

odwzorowana, u¿ytkownik ma mo¿liwoæ umieszczenia w niej krytycznych

sekcji kodu programu, takich jak procedury obs³ugi przerwañ, lub najczêciej

wywo³ywane funkcje. W pamiêci tej mo¿na umieciæ ponadto krytyczne

sekcje danych, takie jak np. stos programowy oraz czêsto u¿ywane wspó³-

czynniki.

n

Miros³aw Gajer

Opracowano na podstawie: Digital Signal Processing Solutions _ TMS320C64x Technical Ove-

rview, materia³y katalogowe firmy Texas Instruments, September 2000

Radioelektronik Audio-HiFi-Video 3/2002

Wyszukiwarka

Podobne podstrony:

2002 03 27 Dec nr 81 MON przejęcie przez DAS tradycji Toruńskiej BA

2002 03 26

2002 03 egzamin

2002 03 06

2002 08 27 1530

pierwsze kolo 2002-03, Kolokwium 13.12, Kolokwium 13

1929 03 27 Rozp RM przekazanie funkcji PP innym organom prawo cywilneid 18474

2002 03 45

2002 03 kolokwium 1id 21673

1999 03 27 praid 18591 Nieznany

2002 03 09

03 27 POLMONITI

2002 10 27

2002 03 40

więcej podobnych podstron