PARAMETRY KOMPUTERÓW

- moc

obliczeniowa

•

MIPS

•

MFLOPS

- szybkość transmisji danych do/z różnych urządzeń

- niezawodność

•

MTBF

- koszt

- ....

Szybkość mikroprocesorów

W przypadku mikroprocesorów dodawanie nowych układów oraz zwiększanie

szybkości wynikające ze zmniejszenia odległości między nimi poprawiało

wydajność 4-krotnie w ciągu każdych 3 lat (prawo Moore’a).

Aby wykorzystać potencjalne możliwości mikroprocesora, należy zapewnić jego

„zasilanie” ciągłym strumieniem zadań (rozkazów). Dlatego projektanci

procesorów wykorzystują coraz bardziej wymyślne rozwiązania jak:

!"

przewidywanie rozgałęzienia (ang. branch prediction),

!"

analiza przepływu danych,

!"

spekulatywne wykonywanie rozkazów.

Równowaga wydajności

Podczas gdy moc procesorów rosła z zawrotną szybkością, rozwój innych

krytycznych zespołów komputera był zbyt wolny. Powstała potrzeba znalezienia

r ó w n o w a g i w y d a j n o ś c i :

dostosowanie organizacji i architektury w celu skompensowania niezgodności

między możliwościami różnych zespołów komputera.

P r o b l e m k r y t y c z n y : interfejs między procesorem a pamięcią główną.

Przykładowe sposoby rozwiązania tego problemu:

!"

zwiększanie liczby bitów, które są jednocześnie wprowadzane

(projektowanie „szerokich” układów DRAM),

!"

stosowanie bardziej efektywnych interfejsów pamięci DRAM

przez umieszczanie układów buforowanych w strukturach

DRAM,

!"

redukowanie częstości odwołań do pamięci głównej przez

wprowadzanie efektywnych struktur pamięci podręcznych

(ang. cache) między procesorem a pamięcią główną.

GENERACJE KOMPUTERÓW

- komputery pierwszej generacji

technologia lamp elektronowych

- komputery drugiej generacji (lata 50-te)

technologia tranzystorów

- komputery trzeciej generacji (połowa lat 60-tych)

układy scalone SSI (ang. small scale integration),

układy scalone MSI (ang. medium scale integration)

- komputery czwartej generacji (połowa lat 70-tych)

układy LSI (ang. large scale integration), era

minikomputerów

- komputery piątej generacji (połowa lat 80-tych)

układy VLSI, wiele kierunków w rozwoju komputerów,

architektury potokowe, RISC, systemy wieloprocesorowe

HISTORIA

1627 Wilhelm Schickald - stworzył pierwsze dwa urządzenia do

sumowania kilkucyfrowych liczb;

1642 B. Pascal - opracował jeden z pierwszych szeregowych

sumatorów/subtraktorów (urządzeń dodających

i odejmujących);

1694 C. W. Leibnitz - buduje pierwszy arytmometr

czterodziałaniowy ( wcześniej, w 1671 zbudował sumator

równoległy );

1833 Ch. Babbage - realizuje projekt maszyny analitycznej,

którą można uznać za pierwowzór późniejszych

komputerów;

1920 - zbudowano arytmometr elektryczny;

1937-1944 - pod kierunkiem H. Aikena zbudowano

przekaźnikowy, całkowicie zautomatyzowany Mark

I

(komputer generacji 0);

1945 J. von Neuman - określa zasadę obowiązującą we

wszystkich powstających później komputerach (poza

ENIAC’em): program maszynowy realizujący działania

zlecone przez programistę zapisany jest w pamięci

komputera;

1946 J. W. Manchly i J. P. Eckert - budują ENIAC (Electronic

Numerical Integrator and Computer - generacja 1): zawierał

18000 lamp i 1500 przekaźników, ważył 30 ton, pobierał

150kW mocy; czas wykonywania operacji: dodawanie w 0.2

ms, mnożenie w 2.8 ms dla liczb dziesiętnych;

1950 - powstaje EDVAC (Electronic Delay Storage Automatic

Computer) z pamięcią na rtęciowych liniach opóźniających;

1968 - po raz pierwszy użyto myszki jako urządzenia

wskazującego;

1970 - pierwsze komputery, które można zaliczyć do 4-tej

generacji, m. in. PDP11 (układy LSI i VLSI);

wyprodukowanie, przez Intel, pierwszej kości dynamicznej

pamięci RAM;

1971 - Intel sprzedaje pierwszy układ procesora (CPU),

4-bitowy, 108 kHz o oznaczeniu 4004, technologia 10

µ

;

1972 - Intel wprowadza procesor 8008, technologia 10

µ

, częstot.

108KHz, który może obsługiwać 16 KB pamięci RAM, czyli

mniej więcej 1/1000 zasobów potrzebnych dla Windows 98;

1974 - Intel buduje kolejny procesor, 8-bitowy 8080, technologia

6

µ

, częstot. 2MHz, zdolny obsłużyć 64KB RAM;

1977 - Intel wprowadza procesor 8086, technologia 3

µ

, częstot.

5MHz;

1981 - sprzedany zostaje IBM PC z systemem operacyjnym

Microsoftu i kompilatorem BASIC’a, firma Osborn

Computers tworzy pierwszy przenośny komputer osobisty

bazujący na IBM PC. Ma on 64KB RAM i waży 10kg;

1983 - Intel wprowadza procesor 80286, technologia 1,5

µ

,

częstot. 8MHz;

1985 - Microsoft wprowadza Windows 1.0, Intel wprowadza

procesor 80386DX, technologia 1

µ

, częstot. 16MHz;

1987 - Microsoft sprzedaje 2 miliony egzemplarzy Windows

2.0;

1989 - Intel wprowadza procesor 80486DX, technologia 1

µ

,

częstot. 25MHz, 1,2 mln tranzystorów;

1990 - Microsoft wypuszcza Windows 3.0;

1991 - Microsoft wypuszcza Windows 3.1;

1992 - Intel wprowadza procesor 80486DX2, technologia 1

µ

,

częstot. 50MHz, 1,2 mln tranzystorów;

1993 - pojawia się wczesna wersja alfa produktu Microsoftu

o nazwie Chicago - Win 95, Intel wprowadza procesor

PENTIUM, technologia 0,8

µ

, częstot. 60MHz, 3,1 mln

tranzystorów;

1995 - Microsoft wprowadza Windows 95 oraz Windows NT

3,51, Intel wprowadza procesor PENTIUM Pro,

technologia 0,6

µ

, częstot. 150 - 200MHz, 5,5 mln

tranzystorów;

1996 - wchodzi Windows NT 4.0;

1997 - Intel wprowadza procesor PENTIUM MMX,

technologia 0,35

µ

, częst. 150 - 200MHz, 4,5 mln

tranzystorów, w maju wprowadza PENTIUM II,

technologia 0,35

µ

, częstot. 150 - 200MHz, 4,5 mln

tranzystorów ;

1998 - Microsoft wprowadza Windows 98, Intel wprowadza

procesor

CELERON, który jest odpowiednikiem

PENTIUM II bez pamięci Cache L2;

1999 – Pentium III, częstotliwość taktowania 450-700 MHz,

technologia 0,25 lub 0,18

µ

;

1999-2000 AMD K7 Athlon, częstotliwość taktowania 1GHz;

2000 – Intel Itanium, 64-bitowa architektura, min. częstotliwość

800 MHz, VLIW, 1 MB cache L2, 2-4 MB cache L3;

2001 – Intel ELBRUS 2000, AMD SLEDGEHAMMER

2002 –

2003 – minimalna częstotliwość 3 GHz, technologia 0,08

µ

;

?

Architektura von Neumanna

1.

Wspólna pamięć do przechowywania zarówno rozkazów

jak i danych.

2.

Pamięć jednowymiarowa, złożona z kolejno

ponumerowanych komórek o jednakowej wielkości.

3.

Brak jawnego rozróżniania rozkazów i danych.

4.

Brak jawnej specyfikacji typów danych.

5.

Praca sekwencyjna - przed rozpoczęciem wykonywania

kolejnego rozkazu musi zostać zakończone wykonywanie

rozkazu chronologicznie poprzedniego. Każdy rozkaz

określa jednoznacznie adres następnego.

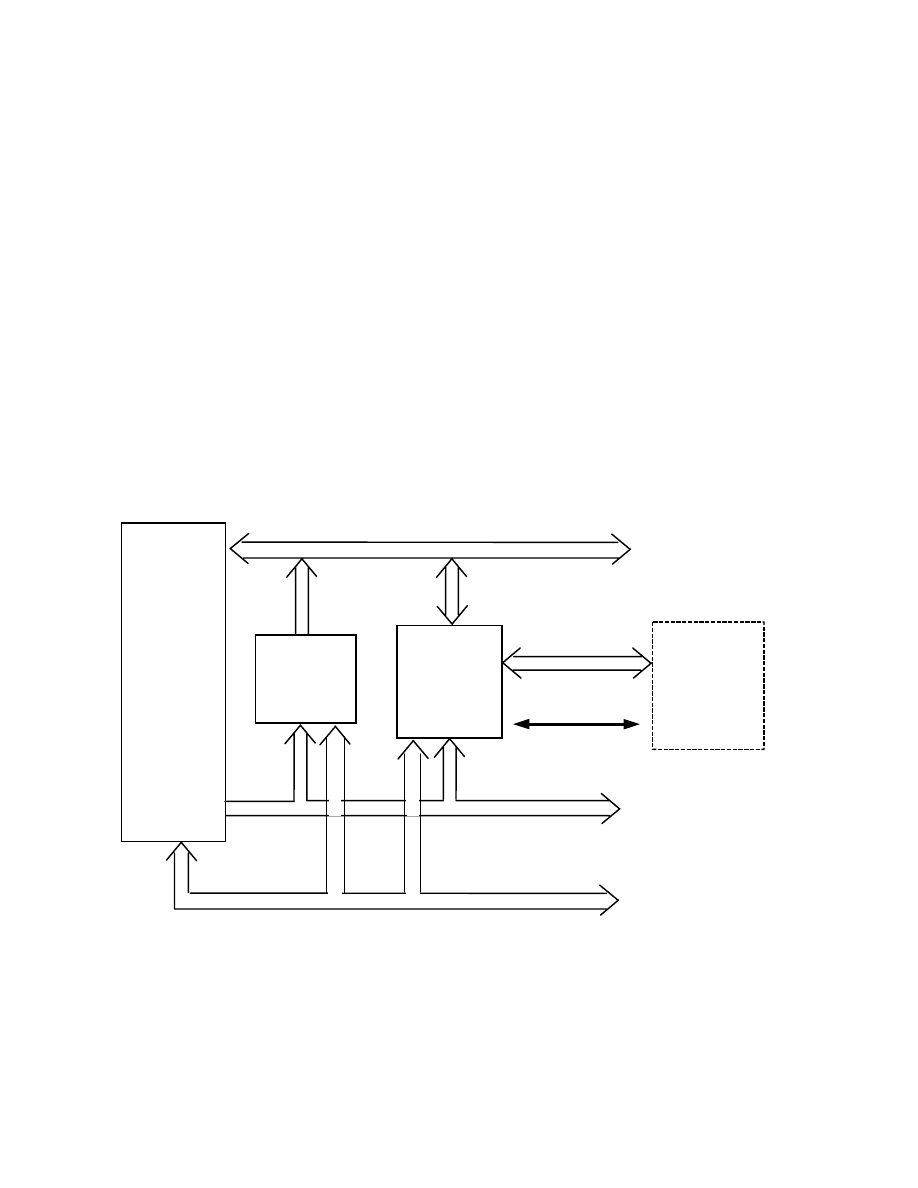

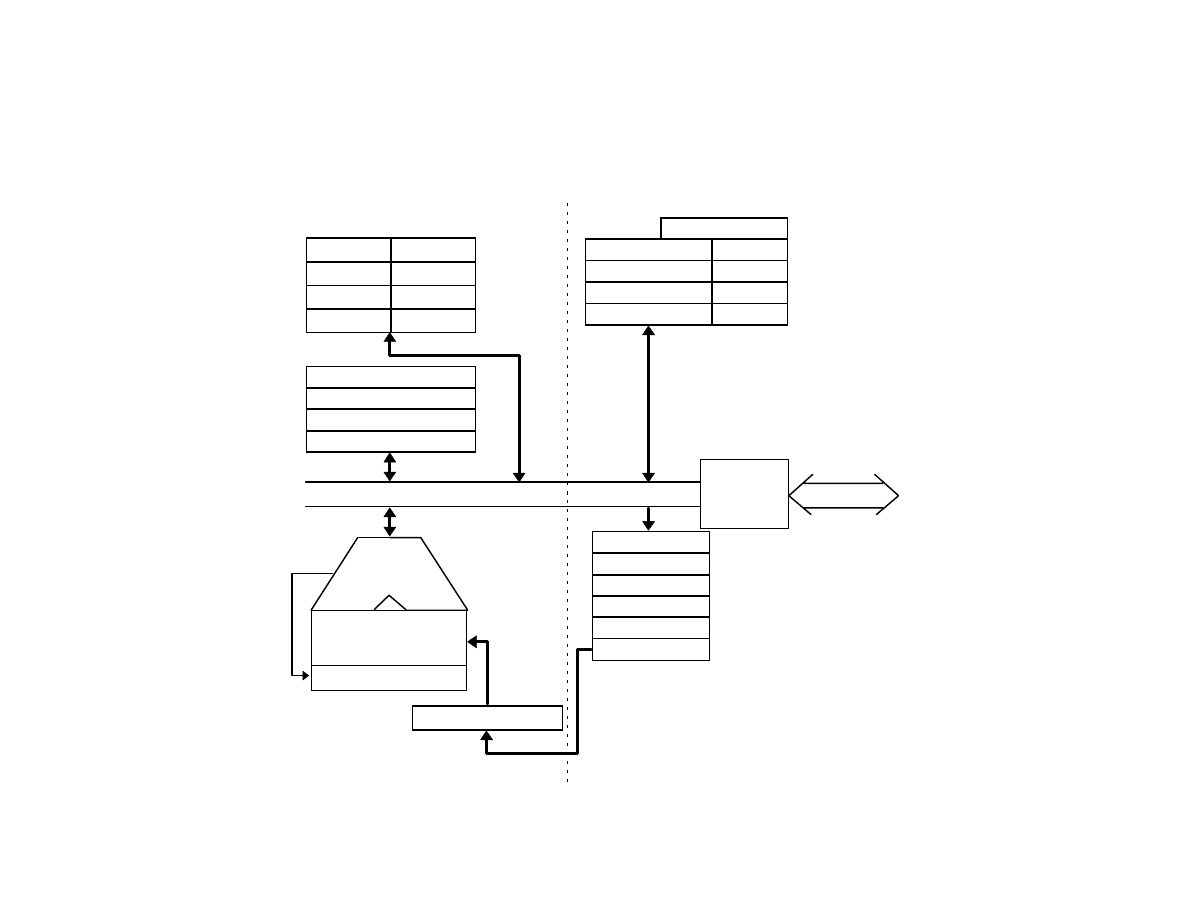

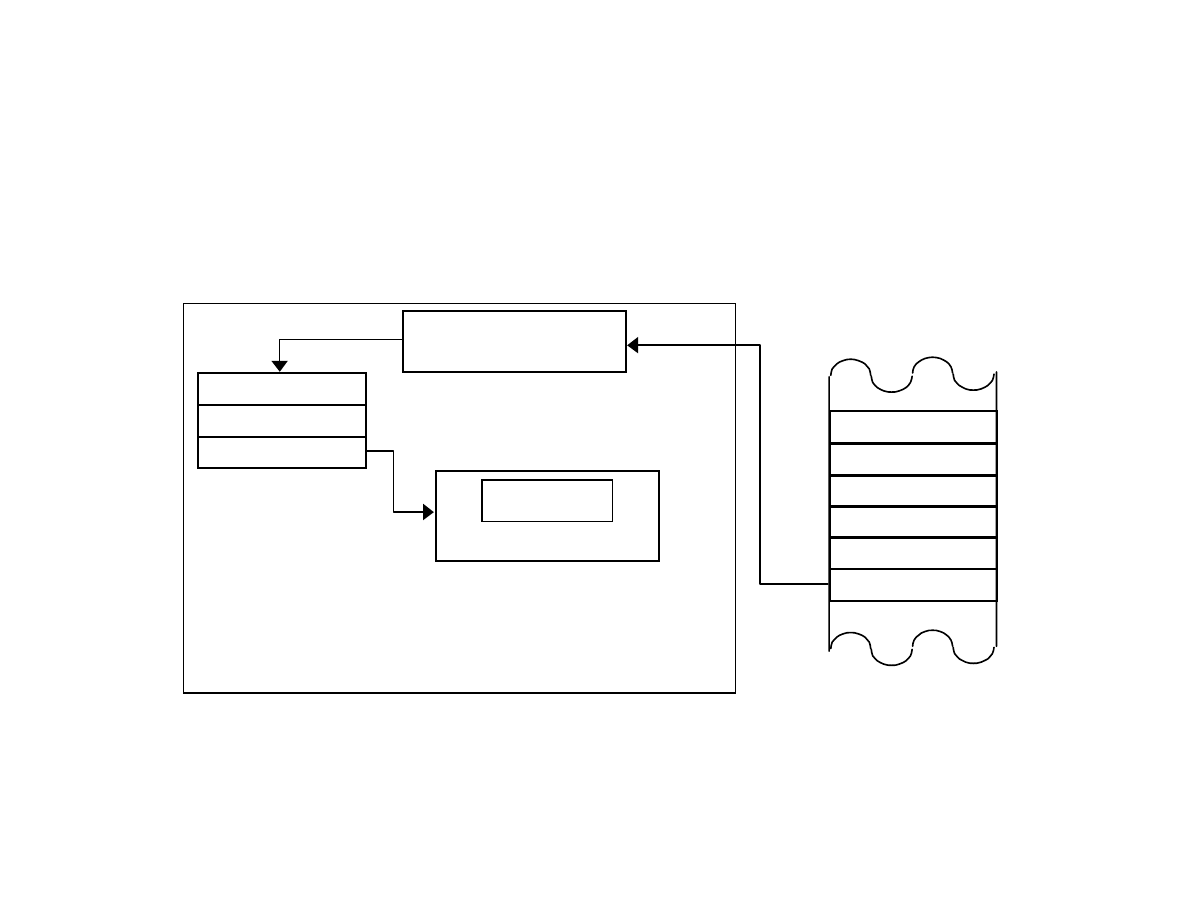

Procesor

Pamięć

operacyjna

(PAO)

Urządzenia

wej/wyj

Progra-

mowane

układy

wej/wyj

Szyna adresowa

Szyna danych

Szyna sterowania

Szyna wej/wyj

Sterowanie

Schemat blokowy komputera

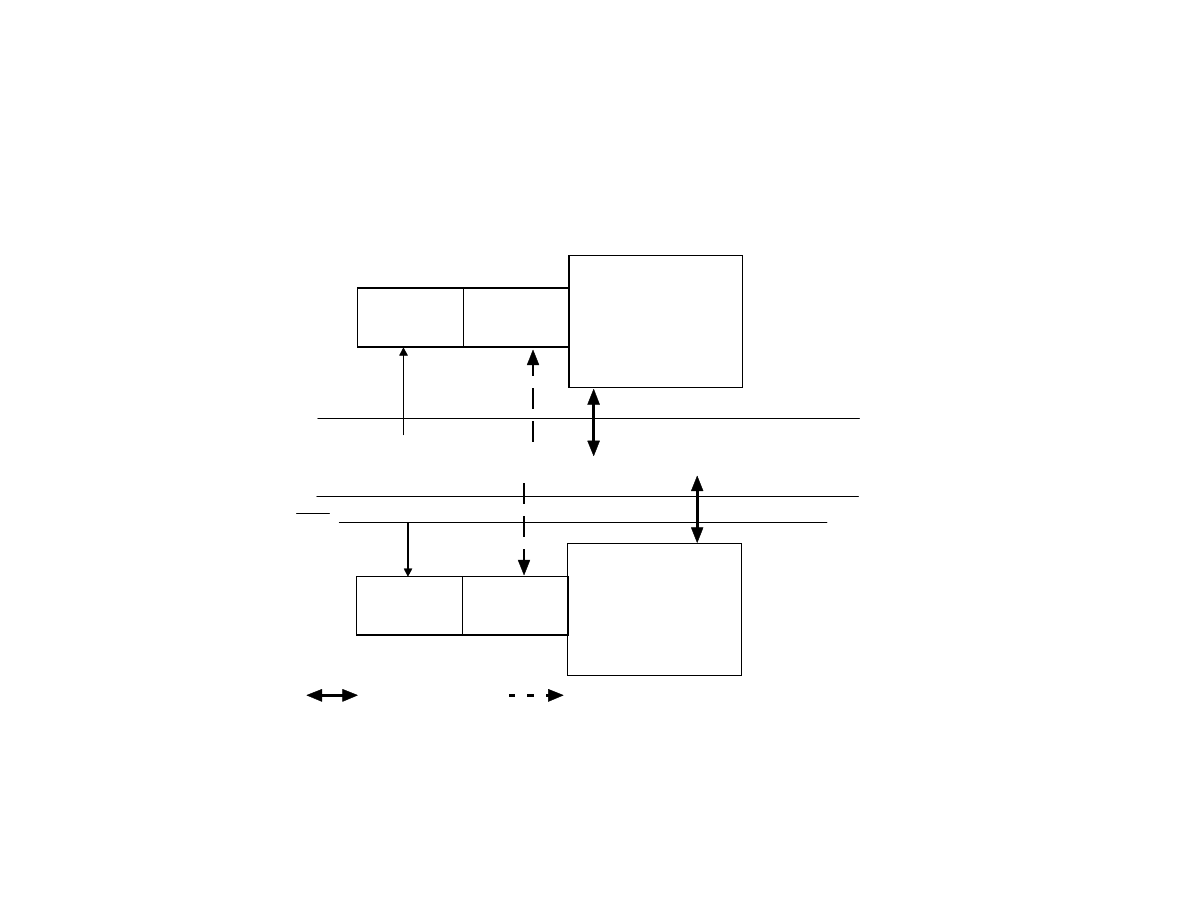

Sekwencje czynności w czasie wykonywania instrukcji

Faza pobrania

rozkazu

Dekodowanie

rozkazu

Cykl maszynowy

Cykl maszynowy

Faza pobrania

argumentu (ów)

Faza wykonania

rozkazu

Cykl instrukcyjny

Przerwania i cykl rozkazowy

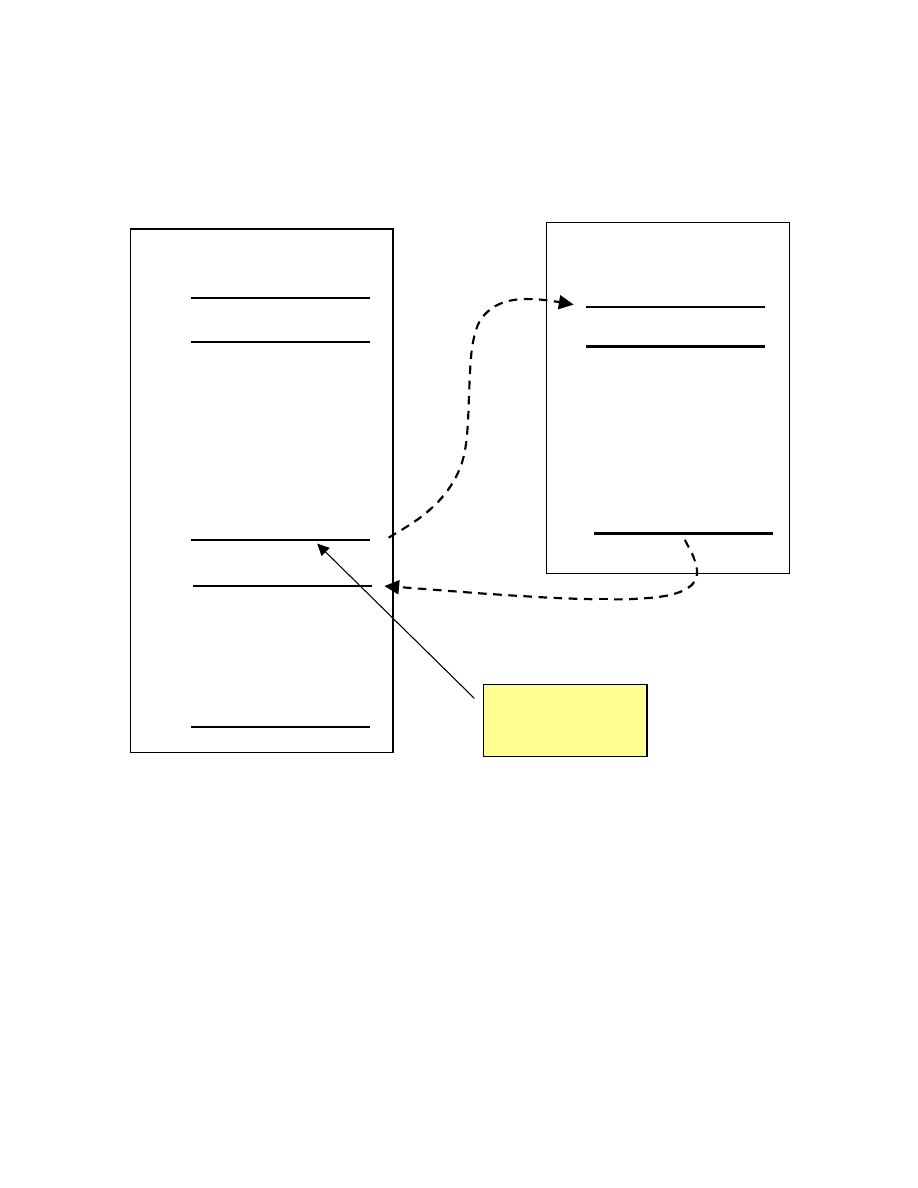

Przekazywanie sterowania za pomocą przerwań

Program użytkownika

1

2

#

#

#

#

#

#

i

i+1

#

#

#

#

M

Program obsługi

przerwania

#

#

#

Tutaj następuje

przerwanie

Cykl rozkazu z przerwaniami

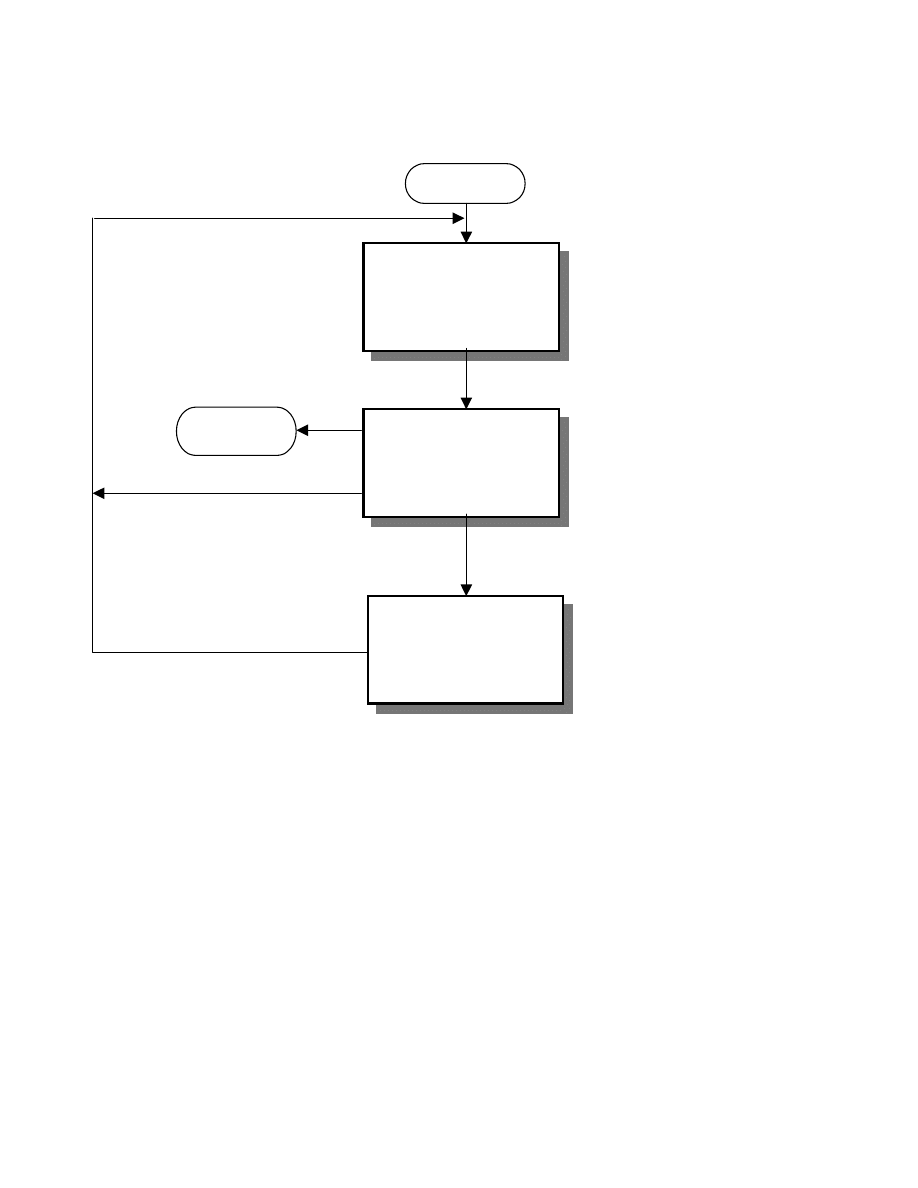

Start

Pobierz

następny

rozkaz

Wykonaj

rozkaz

Sprawdź, czy nie

ma przerwania;

przetwórz

przerwanie

Stop

Przerwania dozwolone

Przerwania zablokowane

Przerwania wielokrotne

W przypadku obsługi wielu urządzeń możliwe jest, że

przerwanie wywołane przez jedno z urządzeń nastąpi w czasie,

w którym jest przetwarzane przerwanie spowodowane przez

inne urządzenie.

Sposoby postępowania z przerwaniami wielokrotnymi:

!"

blokowanie przerwań – procesor będzie ignorował sygnał

żądania przerwania w czasie obsługi danego przerwania;

!"

określenie priorytetów przerwań – przerwanie o wyższym

priorytecie powoduje przerwanie programu obsługi

przerwania o niższym priorytecie.

Klasyfikacja komputerów

W modelu von Neumana zakłada się, że komputer wykonuje

program, umieszczony w jego pamięci i operujący na danych,

które także znajdują się w pamięci.

Zwiększenie efektywności (szybkości) działania komputerów

można osiągnąć:

- poprzez zastosowanie nowych technologii,

- zastosowanie nowych rozwiązań w architekturze komputerów.

Zwiększenie szybkości pracy komputera można uzyskać poprzez

wprowadzenie zwielokrotnienia zarówno ciągu danych, jak

i instrukcji.

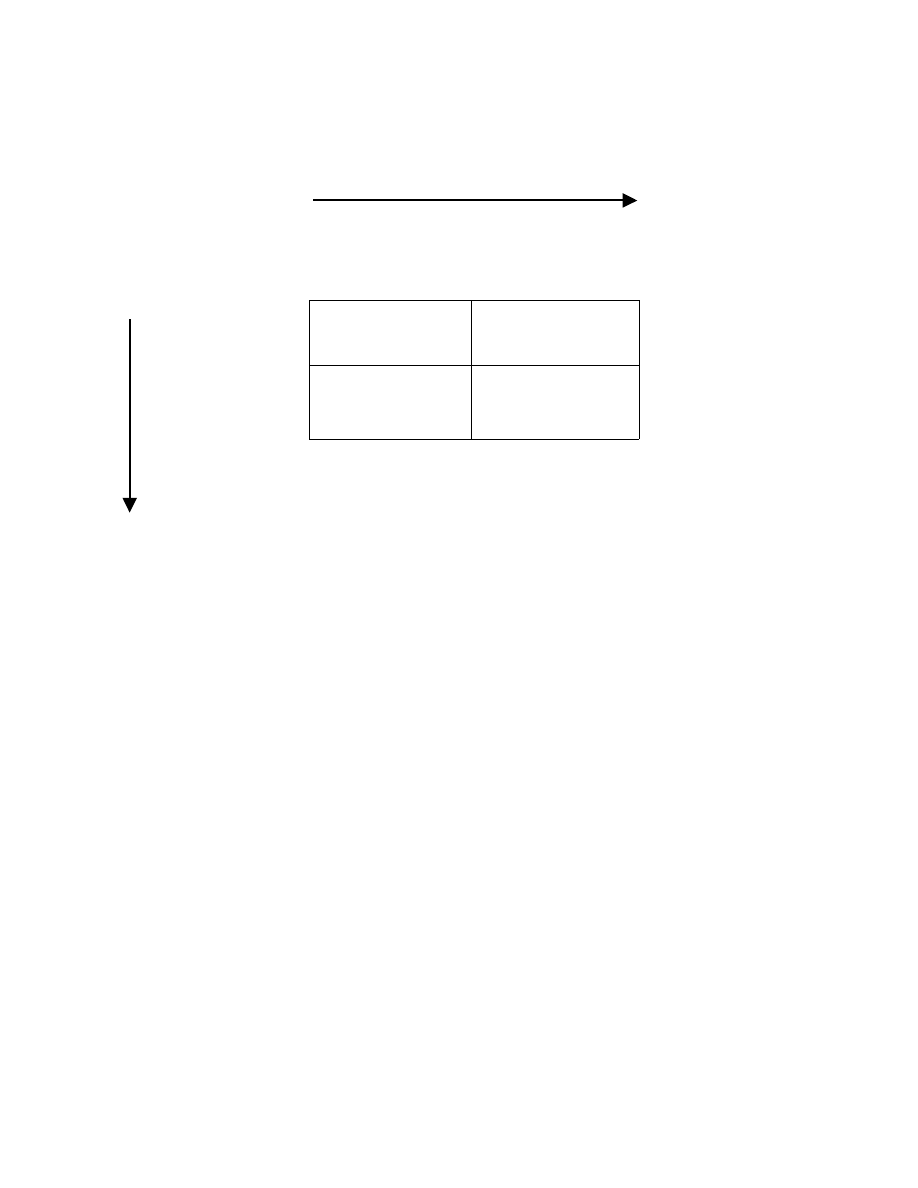

Klasyfikacja Flynna [1966]

SISD

SIMD

MISD

MIMD

Pojedynczy

ciąg danych

Wielokrotny

ciąg danych

Pojedynczy ciąg

instrukcji

Wielokrotny

ciąg instrukcji

Klasyfikacja Treleavena i Lima [1984]

Opiera się na pojęciu bloku obliczeniowego.

Blokiem obliczeniowym nazywa się wykonywaną operację wraz z jej

argumentami i wynikami. Wykonywany program można przedstawić

jako ciąg bloków obliczeniowych, których kolejność i momenty

rozpoczęcia ich wykonywania są sterowane przez tzw. mechanizm

sterujący.

Wyróżnia się 4 rodzaje mechanizmów sterujących:

1) samosterujące (ang. control driven),

2) sterowane argumentami (ang. data driven),

3) sterowane żądaniami (ang. demand driven),

4) sterowane wzorcem (ang. pattern driven).

Mechanizmy wymiany danych:

1) mechanizm wspólnych danych (ang. shared data),

2) mechanizm przesłań komunikatów (ang. message passing).

WSPÓLNE

DANE

PRZESYŁANIE

KOMUNIKATÓW

SAMOSTERUJĄCY

COSH

COME

STEROWANE DANYMI

DASH

DAME

STEROWANE ŻĄDANIAMI

DESH

DEME

STEROWANE WZORCEM

PASH

PAME

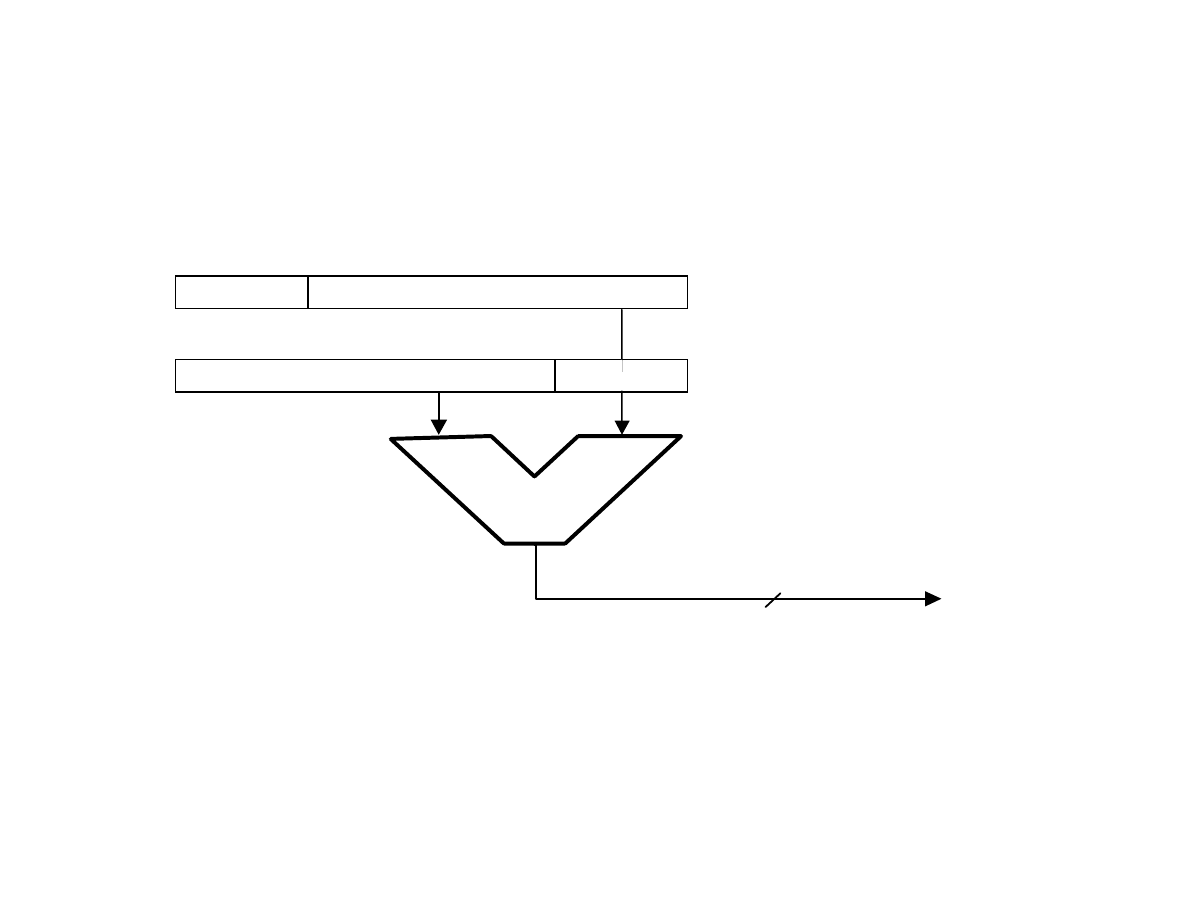

Mechanizm translacji adresów

∑

Przemieszczenie

0 0 0 0

Segment

0 0 0 0

Adres efektywny

Adres bazowy segmentu

0

0

15

15

Adres fizyczny

20 bitowy

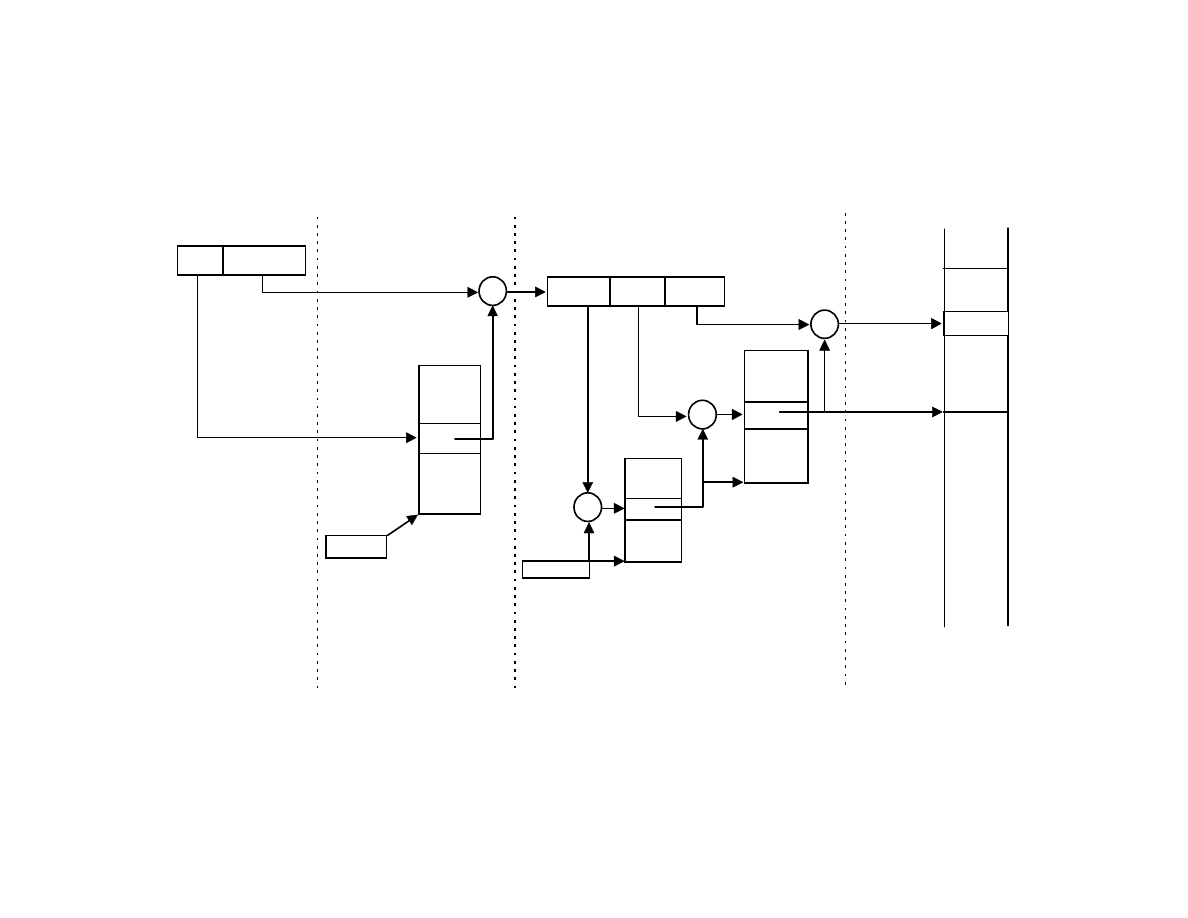

Mechanizm translacji adresów

Adres logiczny

Baza

tablicy

segmen-

tów

Tablica

deskrypto-

rów

Katalog

tablic

stron

Tablica

stron

Adres liniowy

Baza

katalogu

stron

+

+

+

+

Adres

fizyczny

Strona

Pamięć fizyczna

Blok stronnicowania

Blok segmentacji

Program

Segmentacja w procesorach Intel

Deskryptory są umieszczane w pamięci kolejno tworząc tzw. tablice deskryptorów. Wykonywany

program ma dostęp do dwóch tablic deskryptorów: globalnej tablicy deskryptorów GDT i lokalnej

tablicy deskryptorów LDT, których wielkość wynosi 64KB. Numer deskryptora w jednej z tablic

GDT lub LDT jest wybierany na podstawie 13 bitów selektora (bity 3...15). Zatem każda z tablic

może zawierać do 8192 deskryptorów.

Rozmiar logicznej przestrzeni adresowej określa się jako maksymalną wielkość widzianą przez

pojedyncze zadanie. Ponieważ zadanie ma dostęp do obu tablic, dlatego też może w sumie korzystać

z 16384 segmentów, 16K. O wielkości logicznej przestrzeni adresowej decydują liczba segmentów

i ich długość. Dlatego też w mikroprocesorze 80286, gdzie maksymalna długość segmentu wynosiła

64KB logiczna pamięć zwana też pamięcią wirtualną ma pojemność 16K * 64K = 2

14

* 2

16

= 2

30

bajtów = 1GB.

Analogicznie w 80386 (i486), gdzie maksymalna długość segmentu jest równa 4GB

(przemieszczenie 32-bity), jest ona równa: 16K * 4GB = 2

14

* 2

32

= 2

46

bajtów = 64TB. Tak więc,

pamięć widziana przez zadanie jest znacznie większa od pamięci, którą może zaadresować procesor.

Jednak istnieje możliwość wykorzystania całej pamięci zadania dzięki odpowiednim mechanizmom

wbudowanym w procesor, które umożliwiają implementację pamięci wirtualnej.

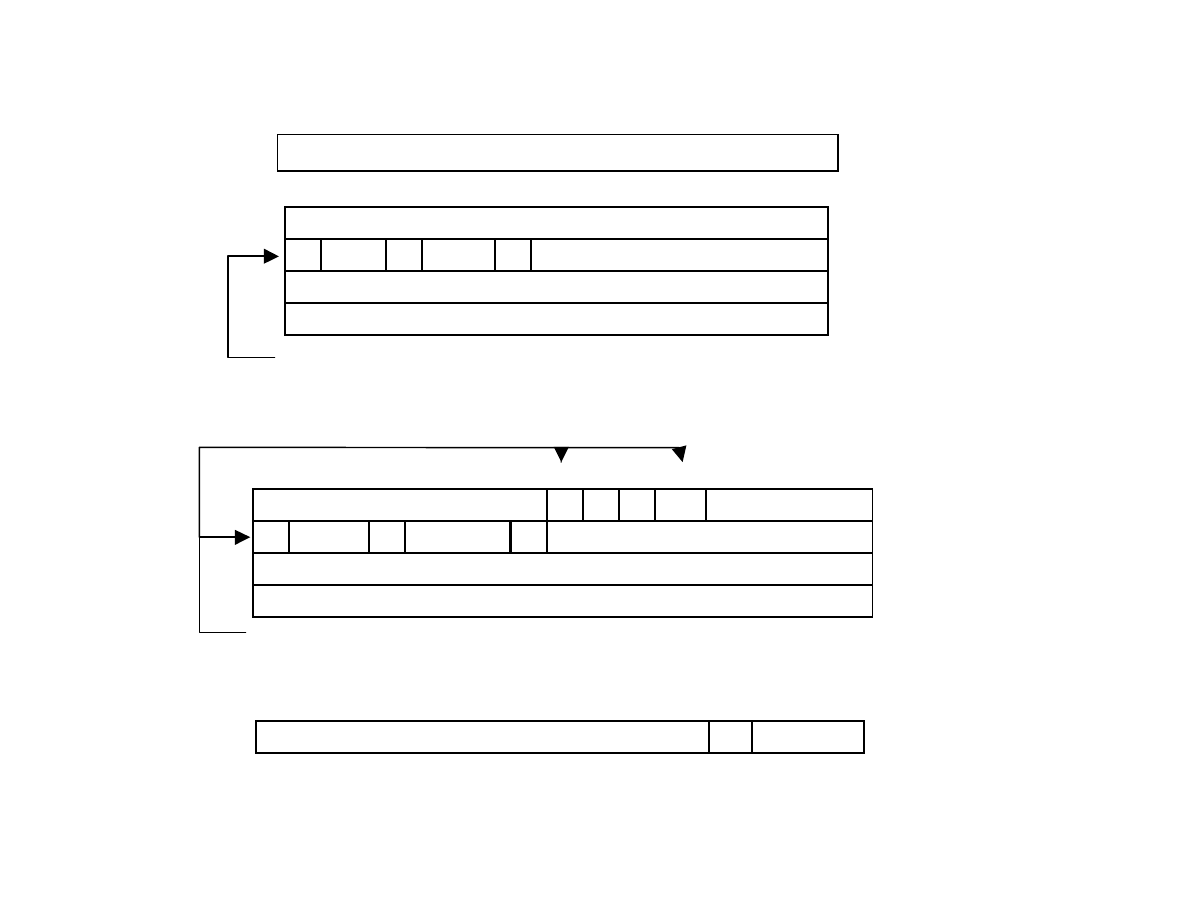

15 0

+6

+4

+2

0

15

0

+6

+4

+2

0

Adres bazowy segmentu 31..24

Adres bazowy segmentu 23..16

A

t y p

DPL

S

A

Adres bazowy segmentu 15 ... 0

Wielkość segmentu 15 ... 0

Bajt atrybutów

G

D

0

AVL

Wielokość 16..19

7 4

Numer deskryptora

TI

RPL

0

1

2

15

3

(zarezerwowane)

Adres bazowy segmentu 23..16

A

t y p

DPL

S

A

Adres bazowy segmentu 15 ... 0

Wielkość segmentu 15 ... 0

Bajt atrybutów

Format deksryptora segmentu pamięci dla 80286

Format deksryptora segmentu pamięci dla 80386 i nowszych

Format selektora

Opis deskryptorów - 80286:

P - segment obecny; określa czy dany segment (strona) znajdują się

w pamięci operacyjnej komputera - P = 1, jeżeli P=0 wówczas generowany jest wyjątek

w wyniku czego przygotowywana jest odpowiednia ilość miejsca w pamięci i brakujący segment

(strona) wprowadzana jest do pamięci operacyjnej.

DPL - poziom ochrony opisywanego segmentu. Pole to zawiera podstawową informację

o segmencie, wykorzystywaną przez mechanizm ochrony mikroprocesora.

S - rodzaj deskryptora. Deskryptory mogą opisywać segmenty pamięci - danych lub kodu - S = 1,

oraz specjalne systemowe struktury danych - segmenty systemowe i bramki zadań - S = 0.

typ - określa prawa dostępu do danego segmentu:

0 - segment danych tylko odczyt;

1 - segment danych - odczyt i zapis;

2 - segment danych rozszerzany w dół tylko odczyt;

3 - segment danych rozszerzany w dół - odczyt i zapis;

4 - segment kodu tylko wykonywanie;

5 - segment kodu - wykonywanie i odczyt;

6 - zgodny segment kodu tylko wykonywanie;

7 - zgodny segment kodu - wykonywanie i odczyt;

Segment zgodny różni się od zwykłego segmentu kodu tym, że po przekazaniu sterowania do

procedury zawartej w tym segmencie nie następuje zmiana poziomu ochrony (na wartość

określoną w deskryptorze segmentu). Procedura wykonuje się na poziomie ochrony procesu

wywołującego.

A - segment użyty. Bit ten jest ustawiany przez procesor przy ładowaniu selektora do rejestru

segmentu lub deskryptora do rejestru deskryptora.

Opis deskryptorów - 80386 oraz i486:

G - ziarnistość. Umożliwia opis segmentu do 4GB przy użyciu jedynie 20-bitowego pola wielkość.

Jednostką długości segmentu może być jeden bajt - G = 0 - można wówczas zdefiniować segment

o długości do 1MB, albo wielkość może być zdefiniowana w jednostkach alokacji 4KB, co daje

możliwość zdefiniowania segmentu o rozmiarze do 4GB.

D - długość słowa. Dla D = 1 oznacza stosowanie 32-bitowego przemieszczenia w adresie

argumentu oraz 32-bitowych argumentów. Dla D = 0 16-bitowe przemieszczenie i 16-bitowe

argumenty.

AVL - pole nie jest interpretowane przez mikroprocesory, może być użyte przez oprogramowanie.

Opis bitów selektora:

TI - określa rodzaj tablicy deskryptorów do, której chce się odwołać program. TI = 0 odwołanie

dotyczy tablicy globalne, TI = 1 oznacza, że odwołanie dotyczy tablicy lokalnej.

RPL - poziom ochrony zadania żądającego dostępu. Służy do osłabienia bieżącego poziomu

ochrony.

Przykład:

Jeżeli zadanie o poziomie ochrony 3 próbuje przez wywołanie funkcji systemowej o poziomie

ochrony 0 uzyskać dostęp do danych na poziomie 2, to nie uzyska takiego dostępu, gdyż wartość

RPL selektora wywołującego będzie równa 3.

Stronicowanie w procesorach Intel

Polega na podziale całej przestrzeni adresowej na bloki o długość 4KB, które są

rozmieszczone sekwencyjne począwszy od adresu 0. W przestrzeni adresowej

mikroprocesora znajdują się więc 2

32

/ 2

12

= 2

20

stron = 1M stron. Położenie strony jest

jednoznacznie określane za pomocą jej 20-bitowego numeru.

W 32-bitowym adresie liniowym można wyróżnić 12 mniej znaczących bitów

określających położenie wewnątrz strony, oraz 20-bitowy numer strony wskazujący jej

położenie w przestrzeni adresowej. Jeżeli założymy wykorzystanie tablicy translacji,

w której każdy element składałby się z 4-bitów jej rozmiar musiałby wynosić 4 * 2

20

=

4Mb. Ze względu na tak duży rozmiar ewentualnej tablicy translacji w mikroprocesorze

80386 zastosowano dwupoziomowe stronicowanie, wprowadzając dwie tablicę: tablicę

stron wskazującą na położenie strony w przestrzeni adresowej oraz tablice wyższego

poziomu zwane katalogami stron, którego to elementy wskazują na właściwą tablicę

stron. Elementy obydwu tych tablic mają identyczny format.

Adres logiczny

Baza

tablicy

segmen-

tów

Tablica

deskrypto-

rów

Katalog

tablic

stron

Tablica

stron

Adres liniowy

Baza

katalogu

stron

+

+

+

+

Adres

fizyczny

Strona

Pamięć fizyczna

Blok stronnicowania

Blok segmentacji

Program

Architektura mikroprocesora 8086

AH

BL

BH

AL

CH

DL

DH

CL

SP

DI

SI

BP

CS

ES

SS

DS

0000

0000

0000

0000

PC

0

7

8

15

AX

BX

CX

DX

0

15

0

15

Magistrala wewnętrzna

Bufor

magistrali

zewnętrznej

6

3

4

5

2

1

Kolejka rozkazów

ALU

Jednostka sterująca

Rejestr znaczników

Rejestr rozkazów

Jednostka sterująca

BIU

Jednostka wykonawcza

EU

0

15

Organizacja pamięci w systemie z mikroprocesorem 8086

Układ wyboru

banku pamięci

A0

Dekoder

adresów

A1...A19

1

Bank pamięci

zawierający mniej

znaczące bajty

D0...D7

Układ wyboru

banku pamięci

Dekoder

adresów

A1...A19

2

D0...D7

Bank pamięci

zawierający bardziej

znaczące bajty

Multipleksowana

szyna adresów i

danych

AD8...AD15

AD0...AD7

BHE

A1...A19

A1...A19

A0

Szyna danych

Szyna adresowa

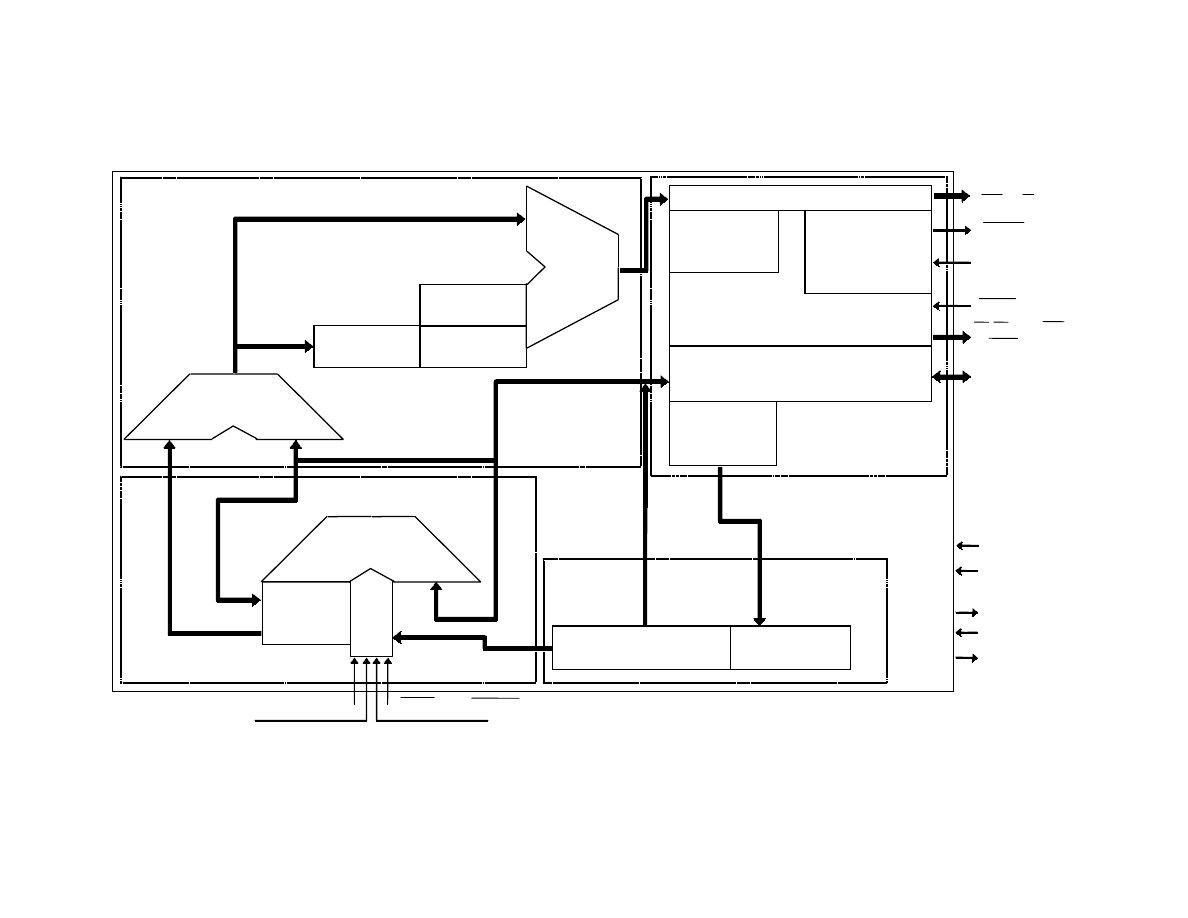

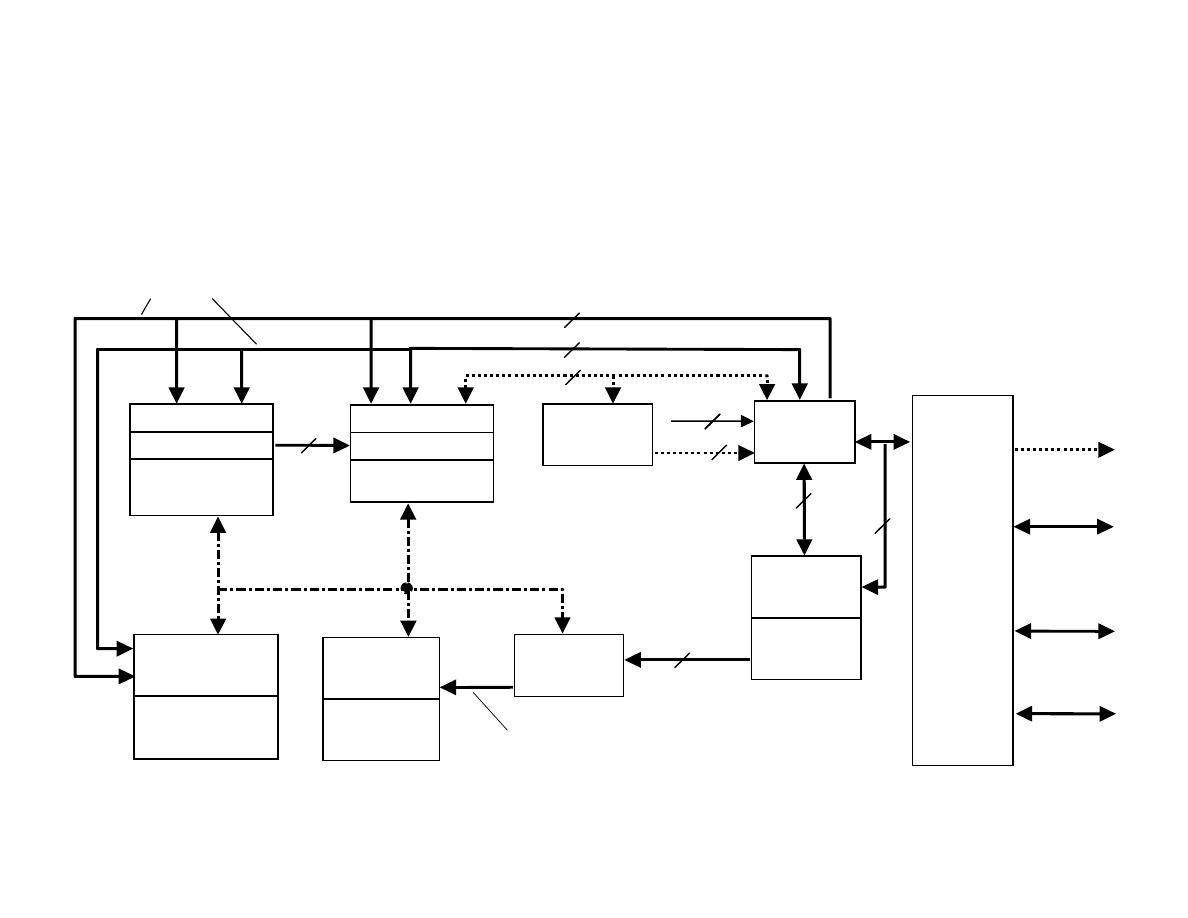

Schemat blokowy mikroprocesora 80286.

Ste-

rowa-

nie

Sterowanie magistrali

S1, S0, COD/ INTA

LOCK, HLDA

Sumator

przemieszczenia

Sumator

adresów

fizycznych

Bazy

segmentów

Rozmiary

segmentów

Kontrola

ograniczeń

Blok

generacji

adresów

ALU

Blok

rejestrów

roboczych

Blok przetwarzania

Kolejka zdekodowanych

rozkazów

Dekoder

rozkazów

Blok

dekodera

Zatrzaskujące bufory adresów

Układ

wprowadzania

rozkazów

Interfejs

z układami

rozszerzającymi

(koprocesorami)

Bufory danych

6-bajtowa

kolejka

rozkazów

A23....A0

BHE,M / IO

PEACK

PEREQ

READY, HOLD

D15...D0

RESET

CLK

GND

U

CC

CAP

BUSY

ERROR

INTR

NMI

Blok

interfejsu

Schemat funkcjonalny mikroprocesora 80386.

Dane

ALU

Zestaw

rejestrów

Rejestr

przesuwający

Blok

segmentacji

Tablica

deksry-

ptorów

Blok

interfejsu

Sterowanie

Adresy

Blok

wprowadzania

Kolejka

rozkazów

Dekoder

rozkazów

Kolejka

Sterowanie

Blok

kontroli

dostępu

Blok prze-

twarzania

danych

Blok programu

Blok

stronicowania

TLB

Mechanizm wyprzedzającego wprowadzania kodów rozkazów.

Mikroprocesor

Rozkaz n+2

Rozkaz n

Rozkaz n+1

Blok wyprzedzającego

wprowadzania

Rozkaz n-1

Dekoder rozkazów

Rozkaz n-2

Rozkaz n

Rozkaz n-1

Rozkaz n+1

Rozkaz n+3

Rozkaz n+2

Pamięć programu

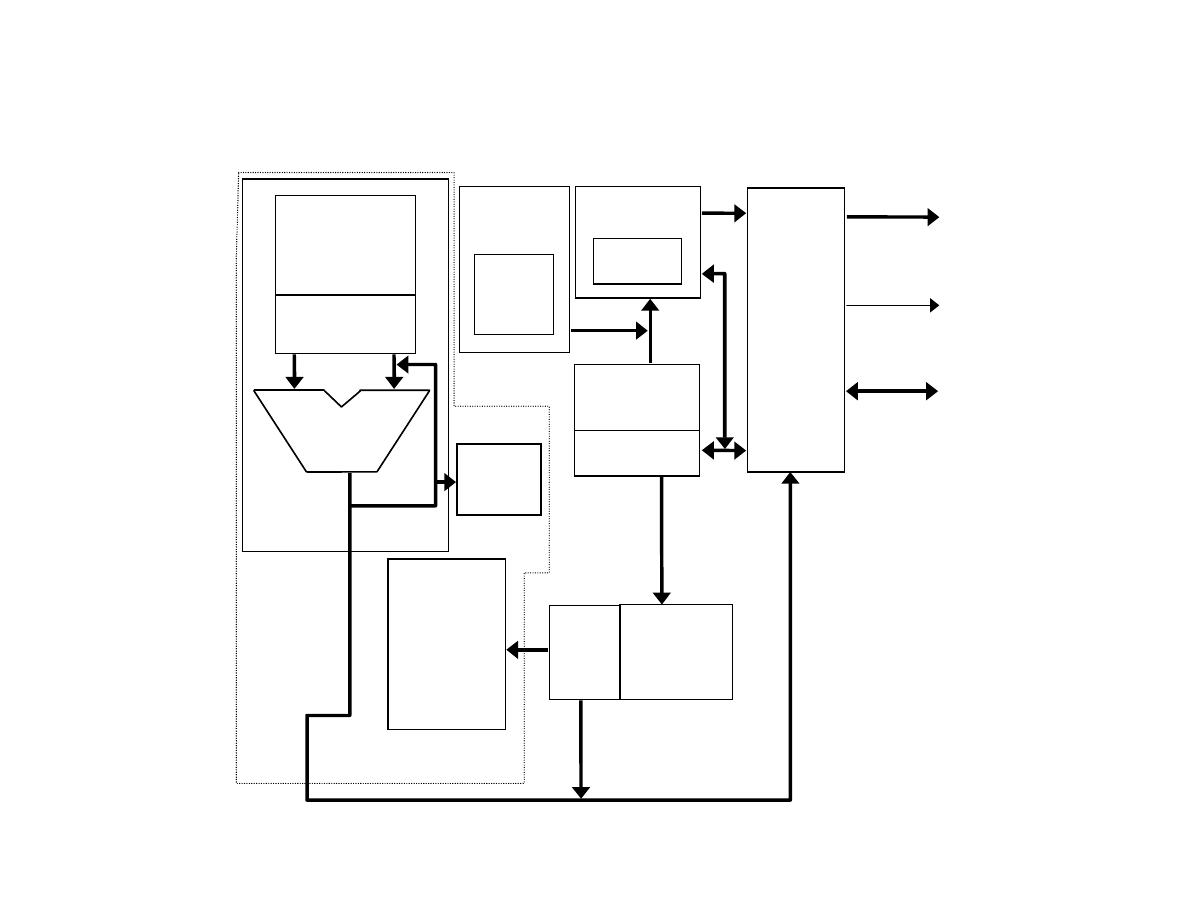

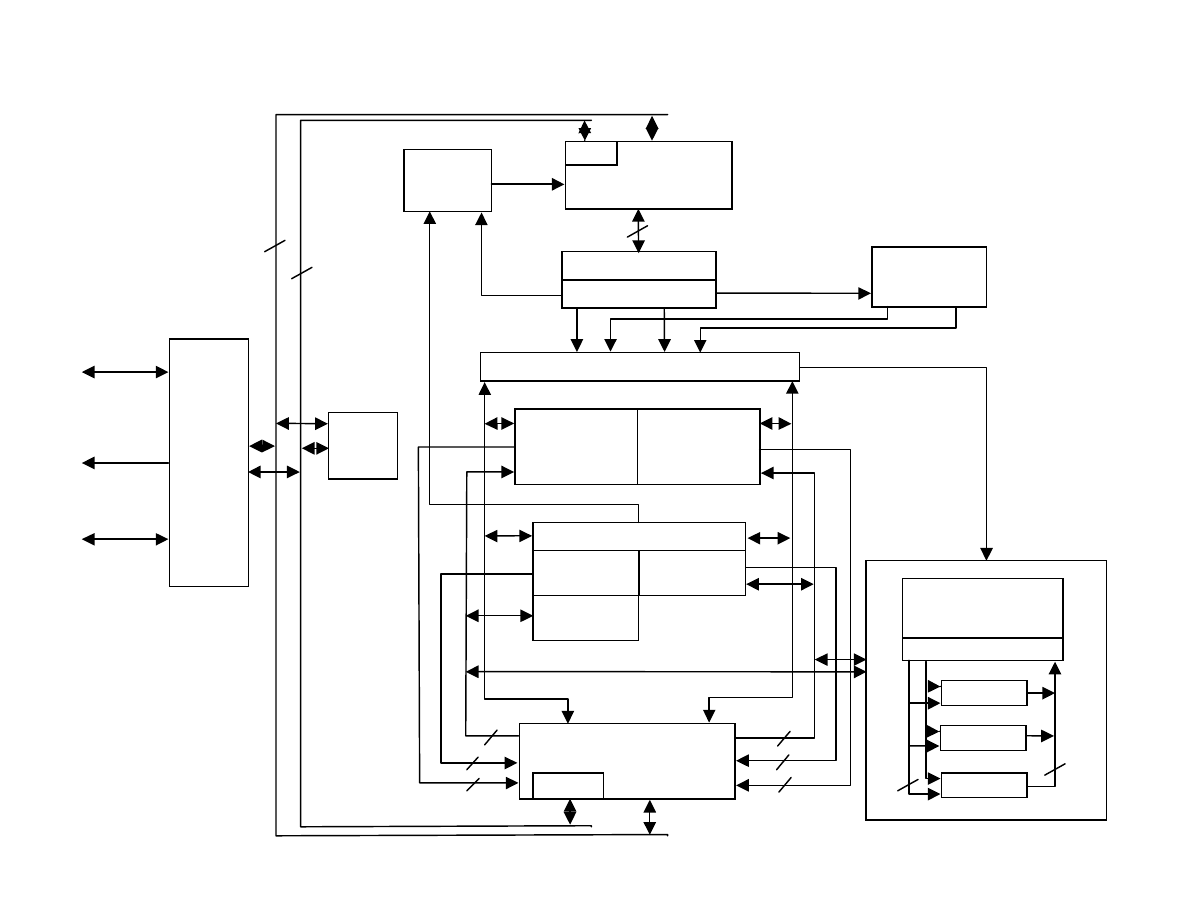

Schemat blokowy mikroprocesora 80486.

Układ przesuwania

Blok rejestrów

ALU

Blok segmentacji

Deskryptory

Długości segmentów

i prawa dostępu

Blok

stronnicowania

Blok pamięci

Cache

Kolejka

rozkazów

Blok

wprowadzania

Dekoder

instrukcji

Jednostka

zmiennopozycyjna

Blok rejestrów

zmiennopozycyjnych

Blok

interfejsu

szyny

Sterowanie

Pamięć

mikroprogramó

w

20

32

32

32

2

128

Adres fizyczny

Szyna adresu liniowego

32

24

Zdekodowane

instrukcje

Strumień

instrukcji

PCD, PWT

32

Adres A2..A31

Dane D0..D31

Sterowanie

JTAG

mikroinstrukcje

Szyna danych

Szyna danych

64-bitowa wewnętrzna szyna danych

Kolejka rozkazów

Dekoder instrukcji

Jednostka sterująca

Blok rejestrów

Bufor

kierunku

skoków

TLB

Cache programu

8 KB

Cache danych

8 KB

TLB

Układ generacji

adresów

(potok U)

Układ generacji

adresów

(potok V)

ALU

(potok U)

ALU

(potok V)

Rejestr

przesuwny

Blok

stroni-

cowania

256

Wskaźnik

instrukcji

Pamięć

mikroinstrukcji

ROM

Blok

interfejsu

64-bitowa

szyna

danych

32-bitowa

szyna

adresowa

Sterowanie

Jednostka zmienno-

przecinkowa

Blok rejestrów

Dodawanie

Dzielenie

Mnożenie

80

80

64-bitowa

szyna

danych

32-bitowa

szyna

adresowa

32

32

32

32

32

32

Schemat blokowy

mikroprocesora Pentium

Organizacja rejestrów procesora PENTIUM

Rodzaje rejestrów:

!"

Ogólnego przeznaczenia (robocze). Występuje 8 32-bitowych rejestrów ogólnego

przeznaczenia;

!"

Segmentowe. Sześć 16-bitowych rejestrów segmentowych zawiera selektory segmentu

służące jako indeksy w tablicach segmentów.

!"

Znaczniki stanu. Rejestr EFLAGS zawiera kody warunkowe i różne bity trybu.

!"

Wskaźnik rozkazu. Zawiera adres bieżącego rozkazu.

!"

Rejestry do współpracy z jednostką zmiennopozycyjną: numeryczne – 8 rejestrów

80-bitowych, dostępnych jako stos; rejestr sterowania – 16-bitowy rejestr sterowania;

rejestr stanu; słowo wyróżników.

Rejestry sterowania

Pentium wykorzystuje cztery 32-bitowe rejestry sterowania CR0, CR2, CR3, CR4.

Rejestr CR0 zawiera znaczniki stanu sterowania systemowego, które sterują trybami lub

wskazują stany odnoszące się raczej do procesora niż do wykonywanego programu.

Znaczniki te są następujące:

Zezwolenie ochrony (PE). Włącza lub blokuje tryb chroniony.

Monitorowanie koprocesora (MP).

Emulacja (EM). Ustawiany, gdy procesor nie ma jednostki zmiennopozycyjnej.

Błąd numeryczny (NE). Umożliwia standardowy mechanizm zgłaszania błędów

zmiennopozycyjnych na zewnętrznych liniach danych.

Ochrona zapisu (WP). Gdy ten bit jest zerem, strony tylko do odczytu na poziomie

uprzywilejowania użytkownika mogą być zapisane przez program nadzorczy (SO).

Brak zapisu jednoczesnego (NW). Wybiera tryb pracy pamięci podręcznej danych. Gdy

bit ten jest ustawiony, operacje zapisu jednoczesnego pamięci podręcznej są

zablokowane.

Blokowanie pamięci podręcznej (CD). Włącza lub blokuje mechanizm zapełniania

wewnętrznej pamięci podręcznej.

Rejestr CR2 służy do przechowania 32-bitowego adresu liniowego ostatniej strony, która

spowodowała błąd strony.

Rejestr CR3 (20 bardziej znaczących bitów) – adres podstawowego katalogu stron.

W rejestrze CR4 jest zdefiniowanych 6 dodatkowych bitów kontrolnych.

Wyszukiwarka

Podobne podstrony:

nauka obsługi komputera w systemie microsoft word 4ICUUD75A253KS776P7IQDUIR4ZRHIMXQX2RK4Q

Microsoft Word W14 Szeregi Fouriera

New Microsoft Word Document (2)

Nowy Dokument programu Microsoft Word (5)

Nowy Dokument programu Microsoft Word

Nowy Dokument programu Microsoft Word

Microsoft Word zrodla infor I czesc pprawiona 2 do wydr

Nowy Dokument programu Microsoft Word

Nowy Dokument programu Microsoft Word (2) (1)

Nowy Dokument programu Microsoft Word (5)

Nowy Dokument programu Microsoft Word (11)

nowy dokument programu microsoft word RLKN2HZYOAUUDMOC2OMN5RCBSSHEHKGU4RH67MY

Nowy Dokument programu Microsoft Word

Nowy Dokument programu Microsoft Word (58)

Nowy Dokument programu Microsoft Word (27)

więcej podobnych podstron