Instytut Automatyki

Ćwiczenie 7

Liczniki liczące w przód, dzielniki częstotliwości

1.

Zakres ćwiczenia

1.1

Zrealizować w układzie programowalnym GAL16V8:

- układ liczący działający jak licznik 7490

- układ liczący MOD-X , x wskazane przez prowadzącego

- układ dzielnika częstotliwości przez liczbę wskazaną

przez prowadzącego

WYMAGANIA : Znajomość materiałów laboratoryjnych : Synteza układów

cyfrowych z wykorzystaniem układów programowalnych. Znajomość budowy

układów licznikowych. Znajomość działania przerzutników.

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

Ćwiczenie 8

Synteza układów synchronicznych

1. Zakres ćwiczenia

1.1

Dokonać syntezy i zbadać następujące układy:

a) licznik MOD 9 pracujący w kodzie binarnym naturalnym

(obciętym do 9-ciu kombinacji)

b) licznik MOD 6 pracujący w kodzie binarnym naturalnym

c) licznik MOD 8 pracujący w kodzie Grey'a

d) licznik pracujący w kodzie EXEES-3

e) układ sterowania silnikiem krokowym generujący

przebiegi 3-fazowe prostokątne

f) układ sterowania silnikiem krokowym generujący

przebiegi 3-fazowe prostokątne z tak zwanymi

półkrokami

W projektowanych układach wykorzystać przerzutniki JK.

WYMAGANIA : Znajomość budowy układów synchronicznych i umiejętność

syntezy ich przy pomocy metody pogrubionych zer i jedynek.

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

Ćwiczenie 9

Sumatory i komparatory

1. Zakres ćwiczenia

1.1

Przy użyciu układu programowalnego ispGal22V10

zrealizować układ działający jak układ 7483 i sprawdzić jego

działanie przy sumowaniu :

- przy sumowaniu liczb bez znaku

- przy sumowaniu liczb ze znakiem w kodzie D2

Zrealizować układ logiczny wykrywający nadmiar (OVERFLOW).

1.2

Przy użyciu układu programowalnego ispGal22V10

zrealizować układ działający jak układ komparatora 7485

WYMAGANIA : Znajomość materiałów laboratoryjnych : Synteza układów

cyfrowych z wykorzystaniem układów programowalnych. Znajomość budowy

sumatorów i komparatorów oraz kodów reprezentujących liczby ze znakiem.

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

Ćwiczenie 10

Synteza dekoderów adresowych dla systemów

mikroprocesorowych

1. Zakres ćwiczenia

1.1

Zaprojektować w układzie programowalnym 16V8 układ

dekodera adresowego o magistrali 8-bitowej (A7....A0) do

którego wchodzą dodatkowo sygnały sterujące magistralą /WR

oraz /RD. Układ powinien sterować sygnałami wyboru dla:

- trzech urządzeń wejściowych (tylko odczyt)

- trzech urządzeń wyjściowych (tylko zapis)

- jednego urządzenia wejściowo-wyjściowego (zapis i odczyt)

- pamięci RAM o pojemności 16 bajtów

Adresy poszczególnych elementów podaje prowadzący.

WYMAGANIA : Znajomość materiałów laboratoryjnych : Synteza układów

cyfrowych z wykorzystaniem układów programowalnych. Znajomość idei

magistrali adresowej w układach mikroprocesororwych.

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

Ćwiczenie 11

Projektowanie układów sekwencyjnych

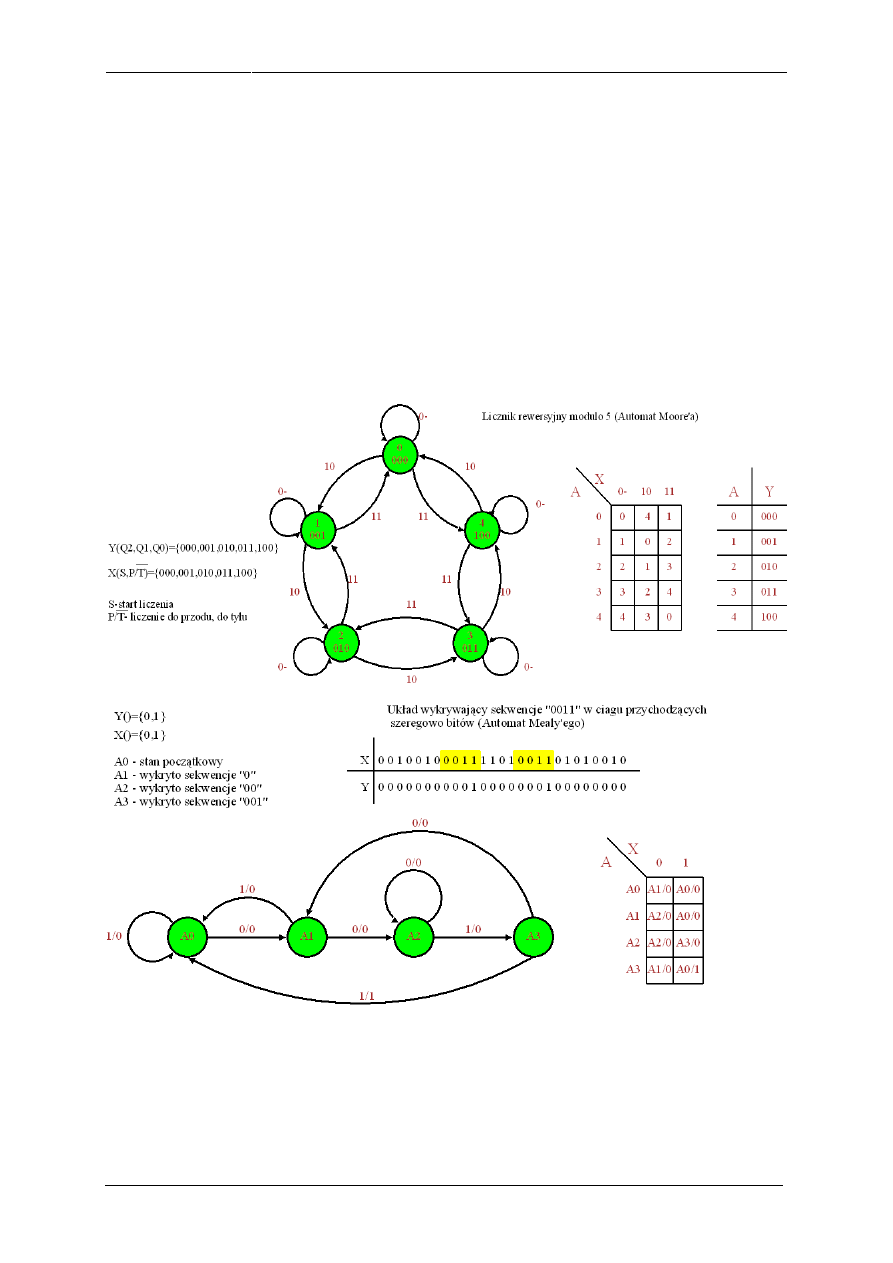

1. Teoria Automatów

1.1

Zasada działania.

Aby zapewnić współpracę różnych członów urządzeń

cyfrowych niezbędne jest generowanie odpowiednich sekwencji

sygnałów sterujących. Rolę generatora sekwencji sygnałów

sterujących może pełnić synchroniczny automat Moore’a lub

automat Mealy'ego (rys.1).

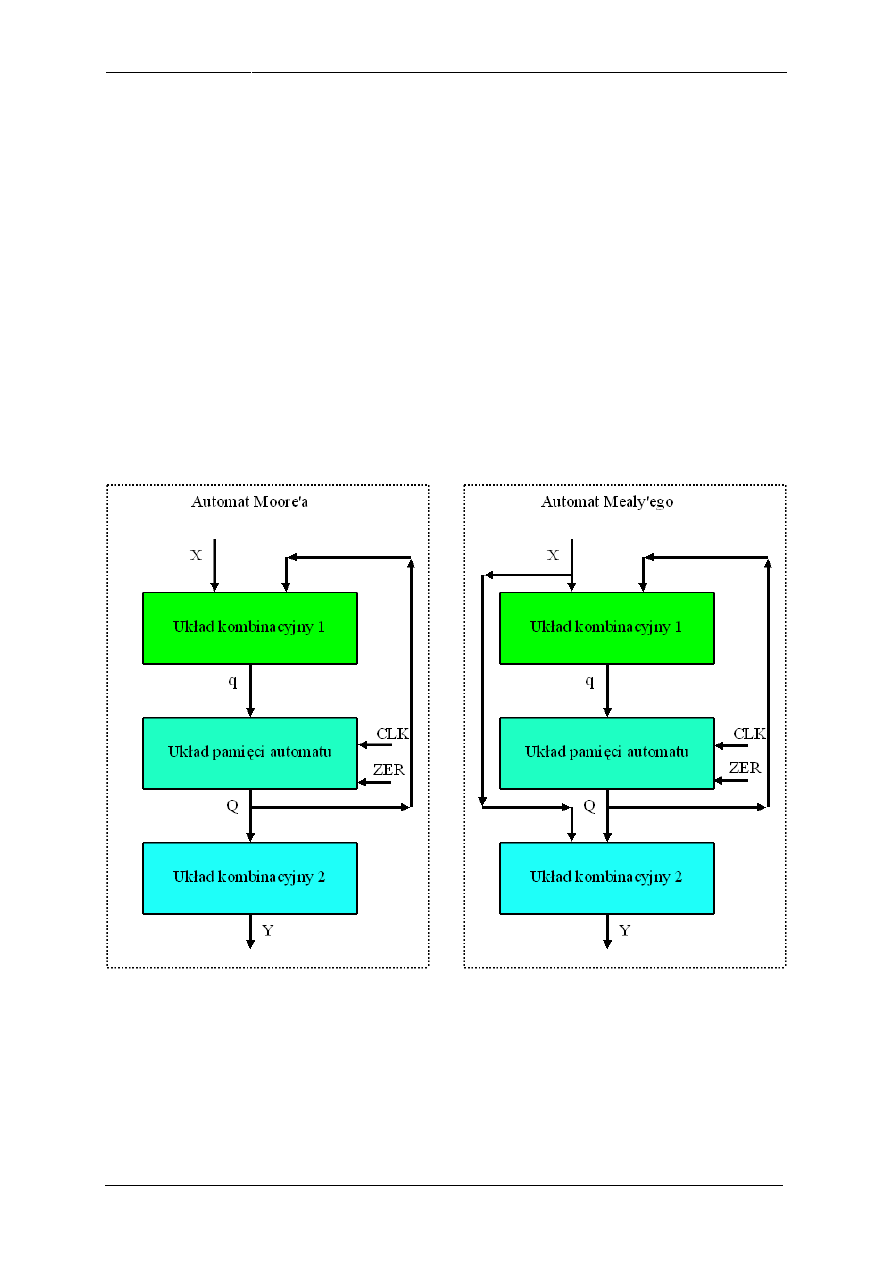

Rys.1 Synchroniczne automaty Moore’a i Mealy'ego - schematy

ideowe

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

UK1,UK2 – układy kombinacyjne

UP – układ pamięciowy

q – sygnały wzbudzeń układu pamięciowego

Q – stan wewnętrzny automatu

X – sygnały warunków

Y – wyjściowe sygnały sterujące.

Układ pamięciowy (UP) może być złożony z zespołu

przerzutników, których sygnały wyjściowe określają stan

wewnętrzny Q automatu. Sygnały wzbudzeń q tych przerzutników są

wytwarzane w układzie kombinacyjnym UK1 na podstawie sygnałów

warunków X i sygnałów sprzężeń zwrotnych Q. Układ kombinacyjny

UK2 służy do wytwarzania wyjściowych sygnałów sterujących Y

zależnych od stanu wewnętrznego Q (automat Moore'a) lub od stanu

wewnętrznego Q i sygnałów warunków X (automat Mealy'ego).

Zmiany stanu automatu zachodzą pod wpływem impulsów

zegarowych CLK, zaś ustawienie go w stanie początkowym odbywa

się przez doprowadzenie impulsu zerującego ZER.

Projektowanie struktury takiego automatu odbywa się przy

wykorzystaniu metod syntezy automatów synchronicznych i polega

na zbudowaniu tablicy przejść, jej uproszczeniu, zakodowaniu i

wyznaczeniu funkcji wzbudzeń przerzutników i funkcji wyjść

układu.

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

1.2

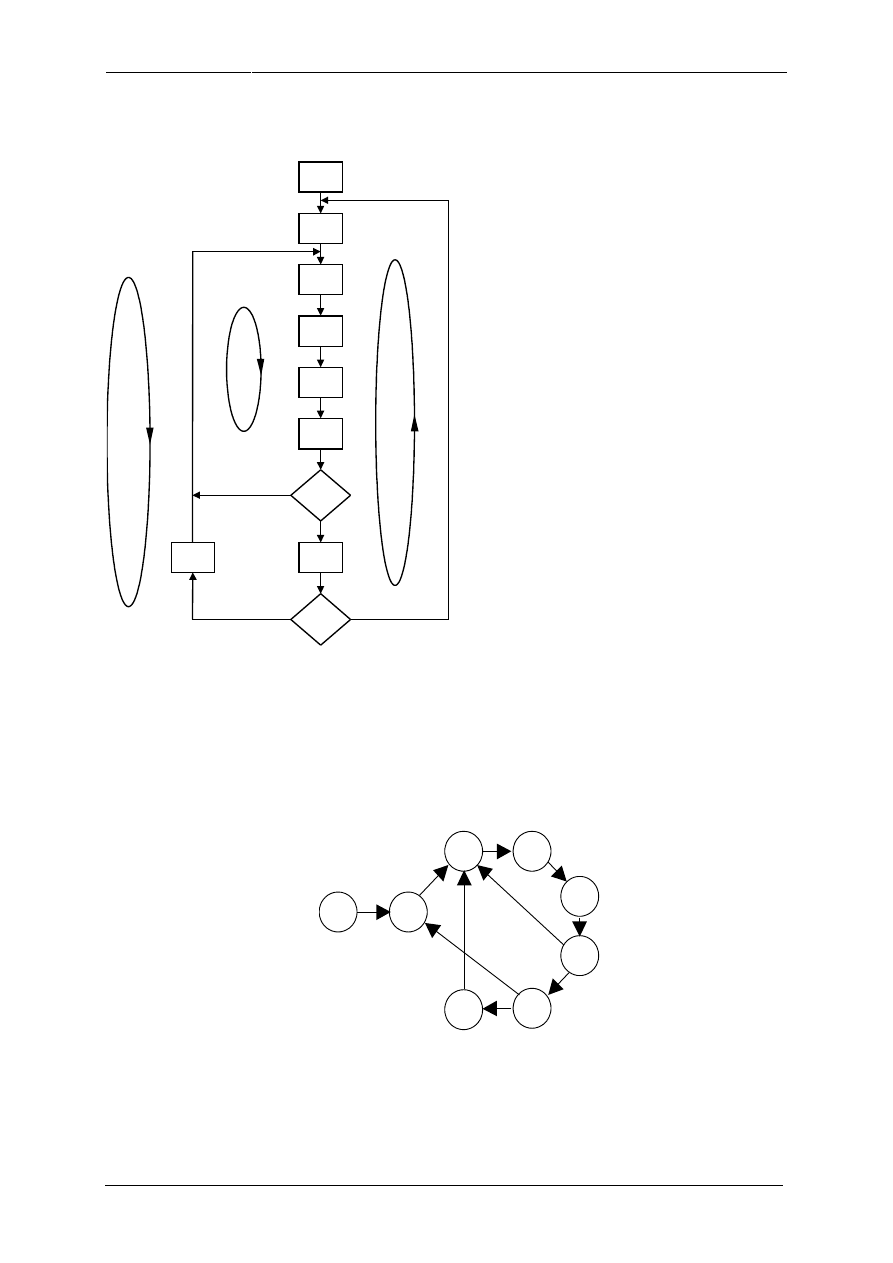

Przykładowe rozwiązanie układu sekwentera (automa Moore'a)

Rozpatrzony zostanie

układ generujący sekwencję

impulsów

zgodnie

z

programem

działania

przedstawionym na rys. 2.

0,1,...,7–stany wewnetrzne

automatu

I0,I1,...I5–sygnały wyjściowe

S1,S2 – sygnały określające

warunki rozgałęzień przy

tworzeniu pętli

A,B,C – pętle programu

Rys.2. Program działania przykładowego sekwentera

Programowi działania z rys.2 odpowiada graf przedstawiony na

rys.3a oraz tablica przejść przedstawiona na rys 3b.

0

1

2

3

4

5

6

7

S1=0

S1=1

S2=0

S2=1

Laboratorium Układów Logicznych i Cyfrowych

I0

I1

I3

I2

I3

I4

I5

I2

S1

S2

0

1

2

3

4

5

6

7

„0”

„1”

„0”

„1”

B

C

A

Instytut Automatyki

Stan aktualny

Q

t

Warunki S1,S2

Sygnały

wyjściowe

00 10 11 01

0

1

1

1

1

I0

1

2

2

2

2

I1

2

3

3

3

3

I3

3

4

4

4

4

I4

4

5

5

5

5

I5

5

2

6

6

2

I2

6

7

7

1

1

I3

7

2

2

2

2

I2

Rys.3. Graf oraz tablica przejść programu działania sekwentera

impulsów z rys. 2.

Zakładając, że układ pamięciowy tego automatu będzie złożony

z przerzutników typu D, a układ kombinacyjny UK1 z

multiplekserów, można na podstawie tablicy przejść sekwentera

(tabela 3b) wyznaczyć tablice przejść przerzutników układu

pamięciowego (rys. 4).

Stan

aktualny

Warunki S1,S2

Q

3

t

Q

2

t

Q

1

t

00 10 11 01

00 10 11 01

00 10 11 01

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

1

0

0

0

0

1

1

1

1

0

0

0

0

0

1

0

0

0

0

0

1

1

1

1

1

1

1

1

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

0

1

0

1

1

0

1

1

1

1

0

0

0

0

1

1

0

1

1

0

0

1

1

0

0

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

Q

3

t + 1

Q

2

t + 1

Q

1

t + 1

Rys. 4. Tablice przejść przerzutników układu pamięciowego UP

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

Tablicom przejść z rysunku 4 odpowiadają następujące funkcje

wzbudzeń przerzutników:

( )

( )

( )

2

1

2

6

5

4

,

3

6

7

,

5

,

2

,

1

6

,

4

,

2

,

0

1

3

3

1

2

2

1

1

1

s

s

t

s

t

t

Q

D

Q

D

Q

D

∑

∑

∑

∑

∑

∑

+

+

=

=

+

=

=

=

=

+

+

+

przy czym symbol

( )

∑

z

x

oznacza, że wyrażenie to przyjmuje

wartość logiczną 1 wtedy, gdy

3

2

1

Q

Q

Q

wyraża liczbę x i jednocześnie

z=1.

Związki (1) wyznaczają strukturę układu UK1, który może

zostać zrealizowany przy użyciu trzech multiplekserów MX1, MX2,

MX3 typu 8/1 o adresie 3 bitowym.

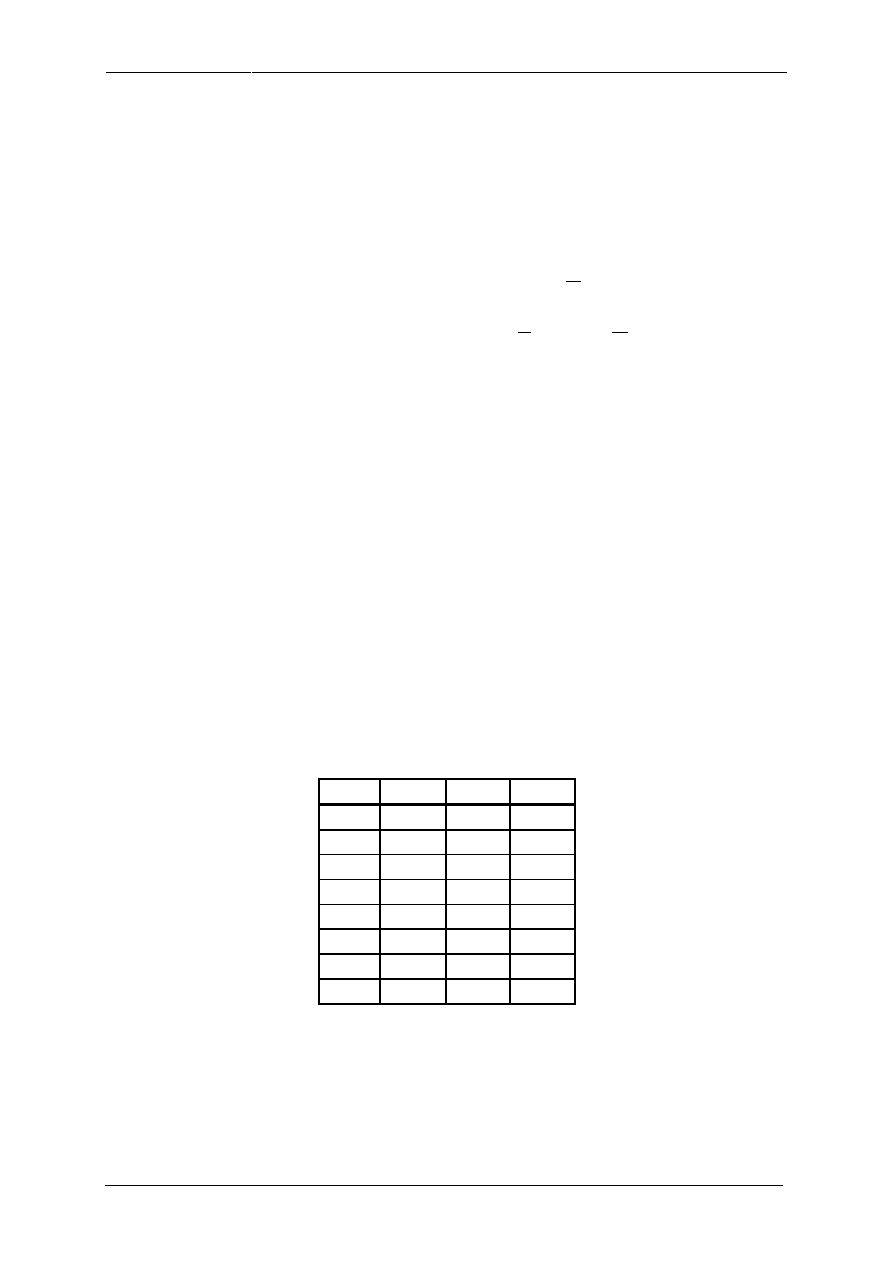

Sygnały wyjściowe y1, y2, y3 zależą tylko od stanów

wewnętrznych Q układu zgodnie z poniższą tabelą (rys. 5)

Q

t

y3

y2

y1

0

0

0

0

1

0

0

1

2

0

1

1

3

1

0

0

4

1

0

1

5

0

1

0

6

0

1

1

7

0

1

0

Rys.5. Tablica zależności sygnałów y1, y2, y3 od stanów

wewnętrznych Q.

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

Z tablicy powyższej wynikają następujące zależności od

sygnałów wewnętrznych automatu Q, które posłużą do realizacji

układu:

∑

∑

∑

=

=

=

6

,

4

,

2

,

1

7

,

6

,

5

,

2

4

,

3

1

2

1

y

y

y

(2)

1.3

Inne przykłady automatów.

1.4

W układzie programowalnym Gal 16V8 zaprojektować automat

Moore'a lub Mealy'ego o działaniu wskazanym przez

prowadzcego

Laboratorium Układów Logicznych i Cyfrowych

Instytut Automatyki

Ćwiczenie 12

Synteza liczników złożonych w układach programowalnych

1. Zakres ćwiczenia.

Zaprojektować licznik opisany przez prowadzącego w układzie

opisanym poniżej na podstawie przykładu. Układ wykorzystuje

strukturę CPLD firmy Lattice MACH 4A5

WYMAGANIA : Znajomość materiałów laboratoryjnych : Synteza układów

cyfrowych z wykorzystaniem układów programowalnych. Znajomość budowy

układów licznikowych

Laboratorium Cyfrowych Układów Automatyki

Instytut Automatyki

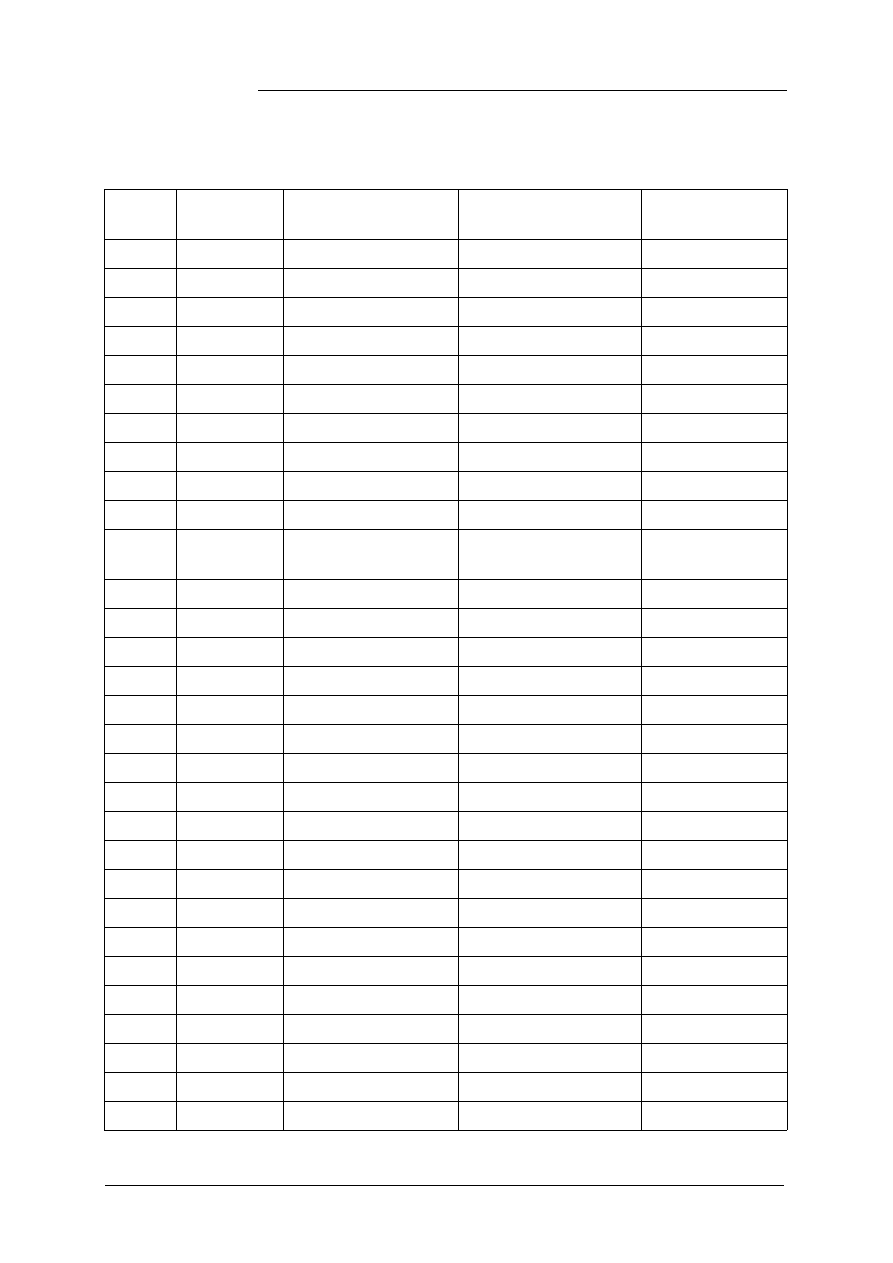

Opis wyprowadzeń układu MACH M4A5- 64/32 dla płytki

edukacyjnej firmy Vantis

Nr pinu

Definicja

pinu

Opis we/wy

Opis led

Uwagi

1

GND

2

I/O 0

wyjście

Led -a cyfra1

3

I/O 1

wyjście

Led -b cyfra1

4

I/O 2

wyjście

Led -c cyfra1

5

I/O 3

wyjście

Led -d cyfra1

6

I/O 4

wyjście

Led -e cyfra1

7

I/O 5

wyjście

Led -f cyfra1

8

I/O 6

wyjście

Led -g cyfra1

9

I/O 7

Wejście SW1

Led dp -cyfra1

Tylko jako wejście

10

TDI

Sygnał JTAG

11

CLK 0/ I 0 Wejście zegarowe

Wybór f

jumperem

12

GND

13

TCK

Sygnał JTAG

14

I/O 8

wyjście

Led -a cyfra2

15

I/O 9

wyjście

Led -b cyfra2

16

I/O 10

wyjście

Led -c cyfra2

17

I/O 11

wyjście

Led -d cyfra2

18

I/O 12

wyjście

Led -e cyfra2

19

I/O 13

wyjście

Led -f cyfra2

20

I/O 14

wyjście

Led -g cyfra2

21

I/O 15

Wejście SW2

Led dp -cyfra2

Tylko jako wejście

22

VCC

23

GND

24

I/O 16

wyjście

Led -a cyfra3

25

I/O 17

wyjście

Led -b cyfra3

26

I/O 18

wyjście

Led -c cyfra3

27

I/O 19

wyjście

Led -d cyfra3

28

I/O 20

wyjście

Led -e cyfra3

29

I/O 21

wyjście

Led -f cyfra3

30

I/O 22

wyjście

Led -g cyfra3

Laboratorium Cyfrowych Układów Automatyki

Instytut Automatyki

31

I/O 23

Wejście SW3

Led dp -cyfra3

Tylko jako wejście

32

TMS

Sygnał JTAG

33

CLK 1/I 1

Wejście zegarowe

f=4Hz

34

GND

35

TDO

Sygnał JTAG

36

I/O 24

wyjście

Led -a cyfra3

37

I/O 25

wyjście

Led -b cyfra3

38

I/O 26

wyjście

Led -c cyfra3

39

I/O 27

wyjście

Led -d cyfra3

40

I/O 28

wyjście

Led -e cyfra3

41

I/O 29

wyjście

Led -f cyfra3

42

I/O 30

wyjście

Led -g cyfra3

43

I/O 31

wyjście

Led -dp cyfra3

44

VCC

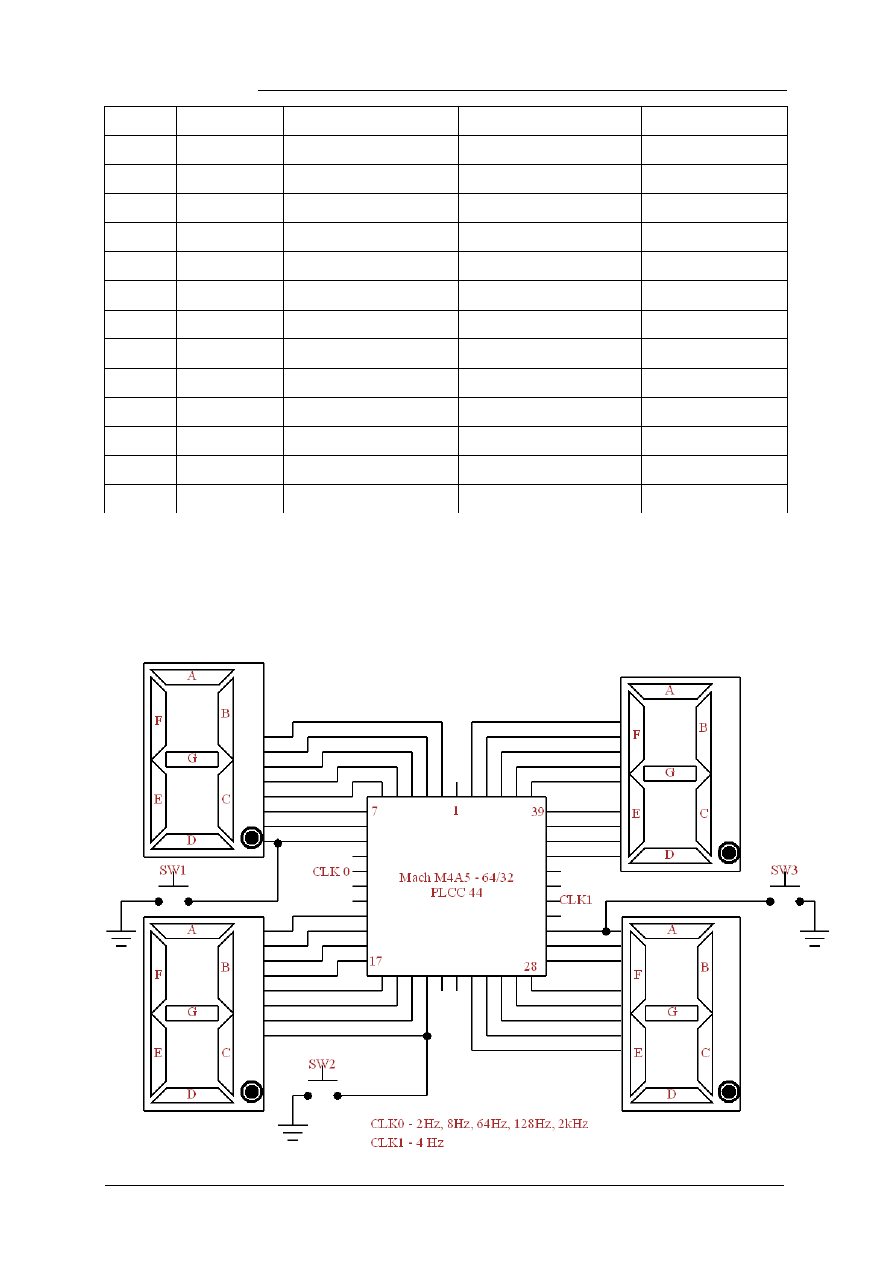

Schemat płytki edukacyjnej firmy Vantis

Laboratorium Cyfrowych Układów Automatyki

Instytut Automatyki

Przykład projektu dla w/w układu w języku ABEL

MODULE

licznik

TITLE

'licznik jedna cyfra'

declarations

"wejscia

sw1,sw2

pin 9,21 ;"przyciski

clk0

pin 11; "zegar

"wyjscia

cyf1_g,cyf1_f,cyf1_e,cyf1_d,cyf1_c,cyf1_b,cyf1_a pin 8,7,6,5,4,3,2 istype 'com';

"segmenty cyfry1

dp pin 43 istype 'com'; "migająca kropka

"zmienne pomocnicze

a3,a2,a1,a0 node istype 'reg'; "zmienne pomocnicze typu register cyfra liczaca 1

p1 node istype 'com'; "zmienne pomocnicze typu kombinacyjnego przeniesienia

clk_pom node istype 'reg'; "dzielnik zegar przez 2

" definicje wektorów

wysw1=[cyf1_g,cyf1_f,cyf1_e,cyf1_d,cyf1_c,cyf1_b,cyf1_a]; "wektor segmentów cyfra1

cyfra1=[a3,a2,a1,a0]; "wektor cyfra liczaca 1

on,off = 0,1; " definicja stanów swiecenia diod

equations

clk_pom := !clk_pom.fb; " dzielenie częstotliwości przez 2

clk_pom.clk=clk0;

when (cyfra1.fb==9) then p1=1 "przeniesienie dla cyfry 1

else p1=0;

when !sw2 then cyfra1:=cyfra1.fb "sterowanie liczeniem cyfra1

else when p1 then cyfra1:=0

else cyfra1:= cyfra1.fb+1;

cyfra1.clk=clk_pom; "definicje zegara dla wektora cyfry

cyfra1.ar=!sw1; " reset asynchroniczny

dp=clk_pom;" kropka miga jak dzielnik przez 2

Laboratorium Cyfrowych Układów Automatyki

Instytut Automatyki

"dekoder z kody binarnego na 7 segmentowy

truth_table (cyfra1 -> wysw1)

0 -> [ off, on, on, on, on, on, on];

1 -> [ off,off,off,off, on, on,off];

2 -> [ on,off, on, on,off, on, on];

3 -> [ on,off,off, on, on, on, on];

4 -> [ on, on,off,off, on, on,off];

5 -> [ on, on,off, on, on,off, on];

6 -> [ on, on, on, on, on,off, on];

7 -> [ off,off,off,off,on, on, on];

8 -> [ on, on, on, on, on, on, on];

9 -> [ on, on,off, on, on, on, on];

10 -> [ on, on, on,off, on, on, on];

11 -> [ on, on, on, on, on,off,off];

12 -> [ off, on, on, on,off,off, on];

13 -> [ on,off, on, on, on, on,off];

14 -> [ on, on, on, on,off,off, on];

15 -> [ on, on, on,off,off,off, on];

END

Laboratorium Cyfrowych Układów Automatyki

Wyszukiwarka

Podobne podstrony:

Cwiczenie 12 id 99084 Nieznany

Fizjologia Cwiczenia 12 id 1743 Nieznany

Biochemia Cwiczenia 12 id 86309 Nieznany (2)

Biologia Cwiczenia 12 id 87710 Nieznany (2)

Cwiczenie 12 id 99108 Nieznany

Cwiczenie 12 id 99084 Nieznany

Fizjologia Cwiczenia 11 id 1743 Nieznany

Biologia Cwiczenia 11 id 87709 Nieznany (2)

cwiczenie 14 id 125164 Nieznany

lab1 12 id 258878 Nieznany

8 Cwiczenia rozne id 46861 Nieznany

cwiczenia wzrost id 155915 Nieznany

II CSK 330 12 1 id 209820 Nieznany

cwiczenie III id 101092 Nieznany

Cwiczenie 5B id 99609 Nieznany

Cwiczenie nr 8 id 99953 Nieznany

cwiczenie 05 id 125057 Nieznany

F Cwiczenia, cz 3 id 167023 Nieznany

cwiczenie 52 id 41325 Nieznany

więcej podobnych podstron