Podstawy Techniki Cyfrowej i

Mikroprocesorowej

1

1

Technika Cyfrowa 2 – Wykład 1

dr in

ż

. Sławomir Sambor

slawomir.sambor@pwr.wroc.pl

ITA, budynek C-5 pokój 708,

Tel. 0 71 320 30 78

http://zstux.ita.pwr.wroc.pl/slawek/

Materiały dostępne na stronie:

http://zstux.ita.pwr.wroc.pl/moodle/

Nazwa użytkownika:

numer indeksu

Hasło:

numer indeksu

Hasło do zapisania się na przedmiot:

TC2

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

2

Literatura

W. Majewski, T. Łuba, K. Jasi

ń

ski, B.

Zbierzchowski: Programowalne moduły

logiczne w syntezie układów cyfrowych, WKŁ

1992

T. Łuba, M.A. Markowski, B. Zbierzchowski:

Komputerowe projektowanie układów cyfrowych

w strukturach PLD, WKŁ 1993

Pasierbi

ń

ski J., Zbysi

ń

ski P.: Układy

programowalne w praktyce. WKiŁ

Zbysi

ń

ski P., Pasierbi

ń

ski J.: Układy

programowalne – pierwsze kroki

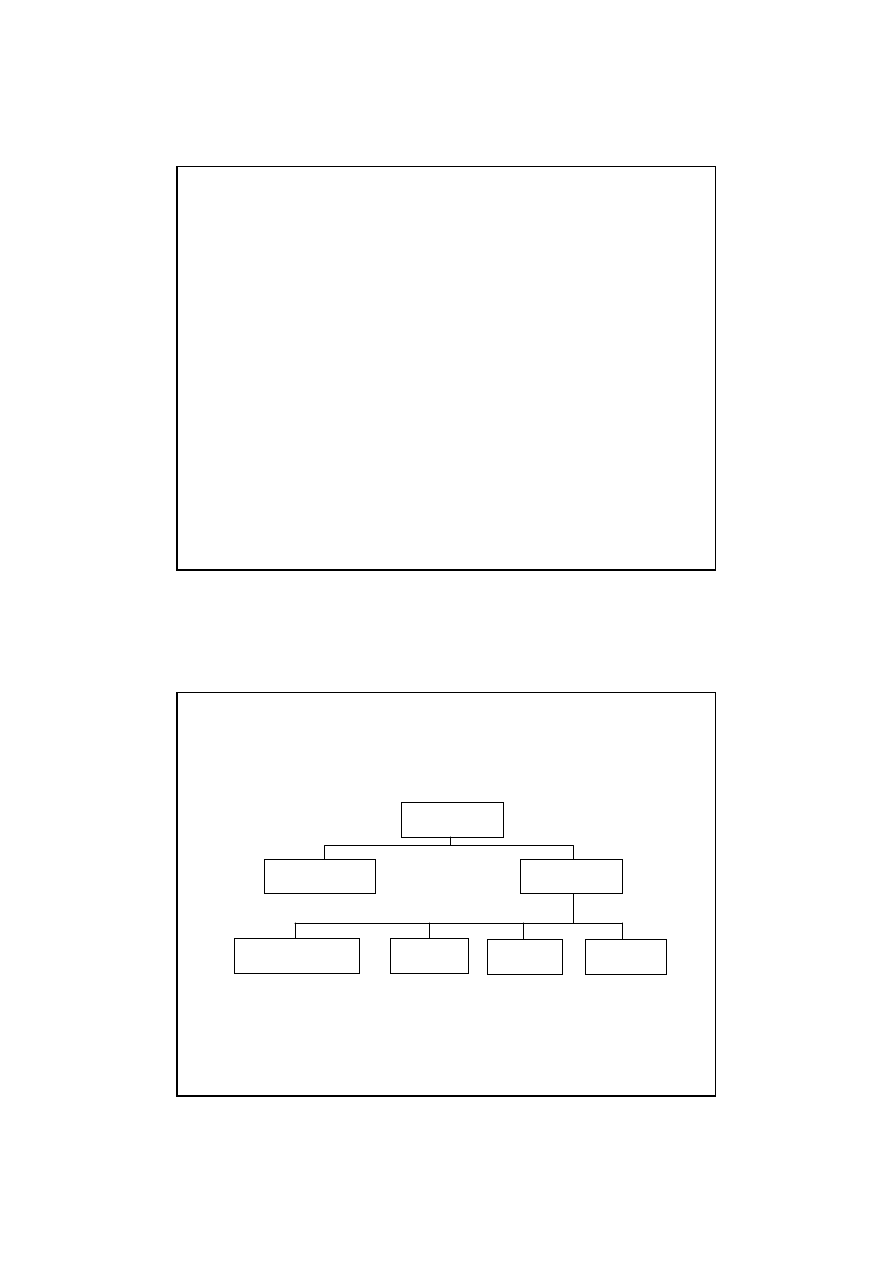

Klasyfikacja układów cyfrowych

Układy

cyfrowe

Układy

standardowe

ASIC

Układy programowalne

PLD

Gate

Arrays

Standard

Cell

Full

Custom

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

3

Cyfrowe układy scalone

Dwa podstawowe kryteria klasyfikacji:

• ilość bramek w układzie (złożoność układu, tzw. stopień integracji),

• technologia wykonania.

Stopień integracji -liczba bramek logicznych w układzie

• SSI (Small Scale Integration)

< 10

4 x NAND

4 x OR...

- proste układy rodziny TTL

• MSI (Medium Scale Inetgration)

10 – 100

przerzutniki (np. SN7474: 2 x D = 2 x 6 NAND)

rejestry, liczniki

proste układy arytmetyczne...

- bardziej złożone układy rodziny TTL

• LSI (Large Scale Inetgration)

100 - 10.000

proste mikroprocesory (liczba tranzystorów):

-4004 (1971) 2550

-8008 (1972) 2500

-8080 (1974) 5000

układy WE /WY, zegary, kalkulatory...

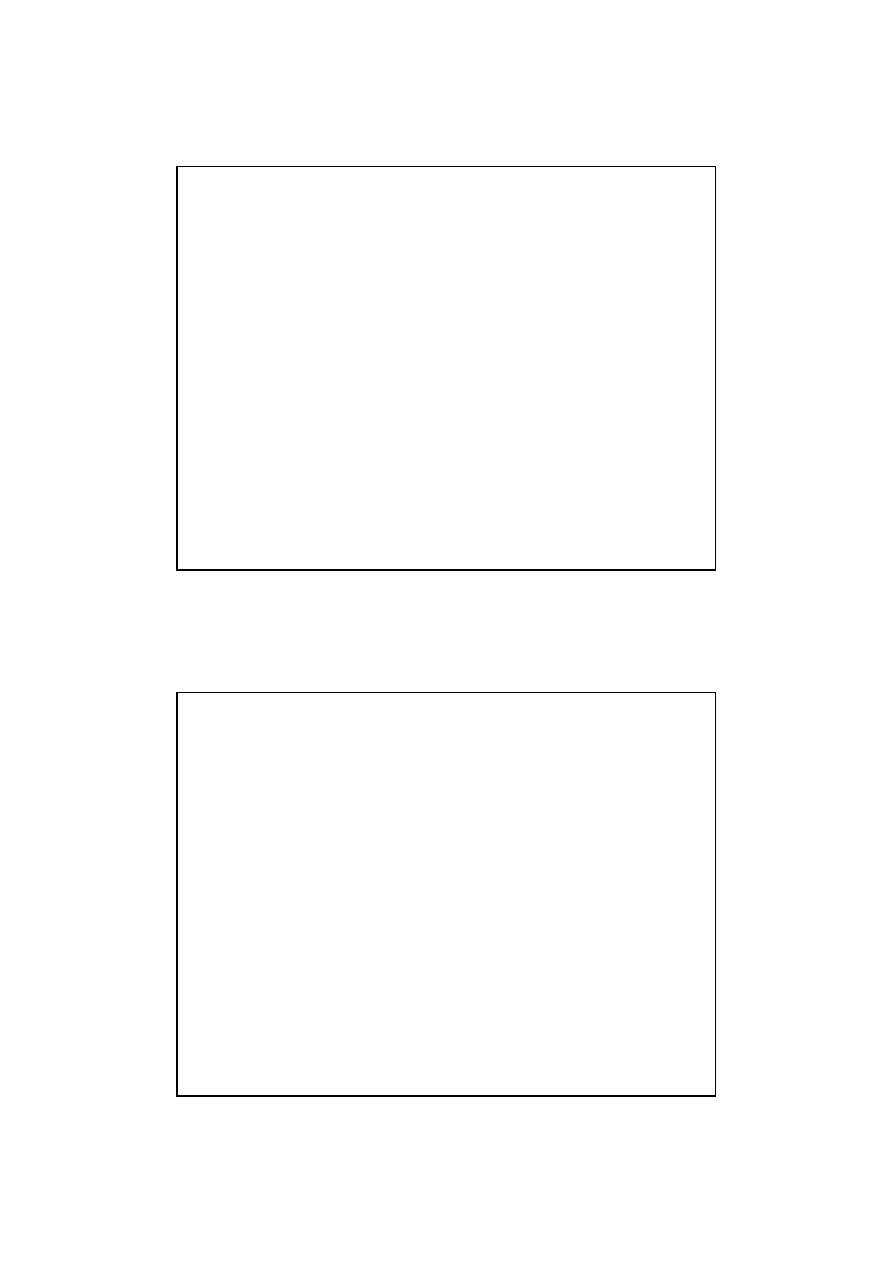

• VLSI (Very Large Scale Inetgration)

> 10.000

mikroprocesory (liczba tranzystorów):

-8086

(1978)

29 000

-i386Dx

(1985)

275 000

-i486Dx

(1989)

1 200 000

-Pentium

(1993)

3 100 000

-Pentium II

(1997)

7 500 000

-Pentium III

(1999)

24 000 000

-Pentium IV

(2000)

42 000 000

-Core 2 Duo

(2006) 291 000 000

-Core 2 Quad

(2007) 582 000 000

UWAGI:

• Klasyfikacja utworzona na początku lat 80.

• Obecnie miarą złożoności mikroprocesorów jest raczej liczba tranzystorów

niż bramek (pamięci podręczne cache...).

• Gordon Moore (współzałożyciel firmy Intel w 1968 r), 1965:

liczba tranzystorów w układzie scalonym rośnie wraz z czasem w tempie wykładniczym

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

4

http://www.intel.com/technology/mooreslaw/

Technologie

• Tranzystory bipolarne

- rodzina TTL (Transistor-Transistor Logic): 1965, Texas Instruments, układy SN74

- rodzina ECL (Emiter Coupled Logic): 1962, Motorola; większy pobór mocy, najszybsze

• Tranzystory unipolarne MOS: mniejszy pobór mocy,

mniejsze rozmiary (nawet 10x) ⇒ lepsze scalanie

- pMOS: chronologicznie pierwsze

- nMOS: szybsze (większa ruchliwość nośników n);

technologia HMOS: down, sizing, zmniejszanie długości kanału tranzystora zwiększa

także szybkość; największy stopień scalenia

- Complementary MOS, CMOS: oba typy tranzystorów MOS, najmniejszy pobór mocy

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

5

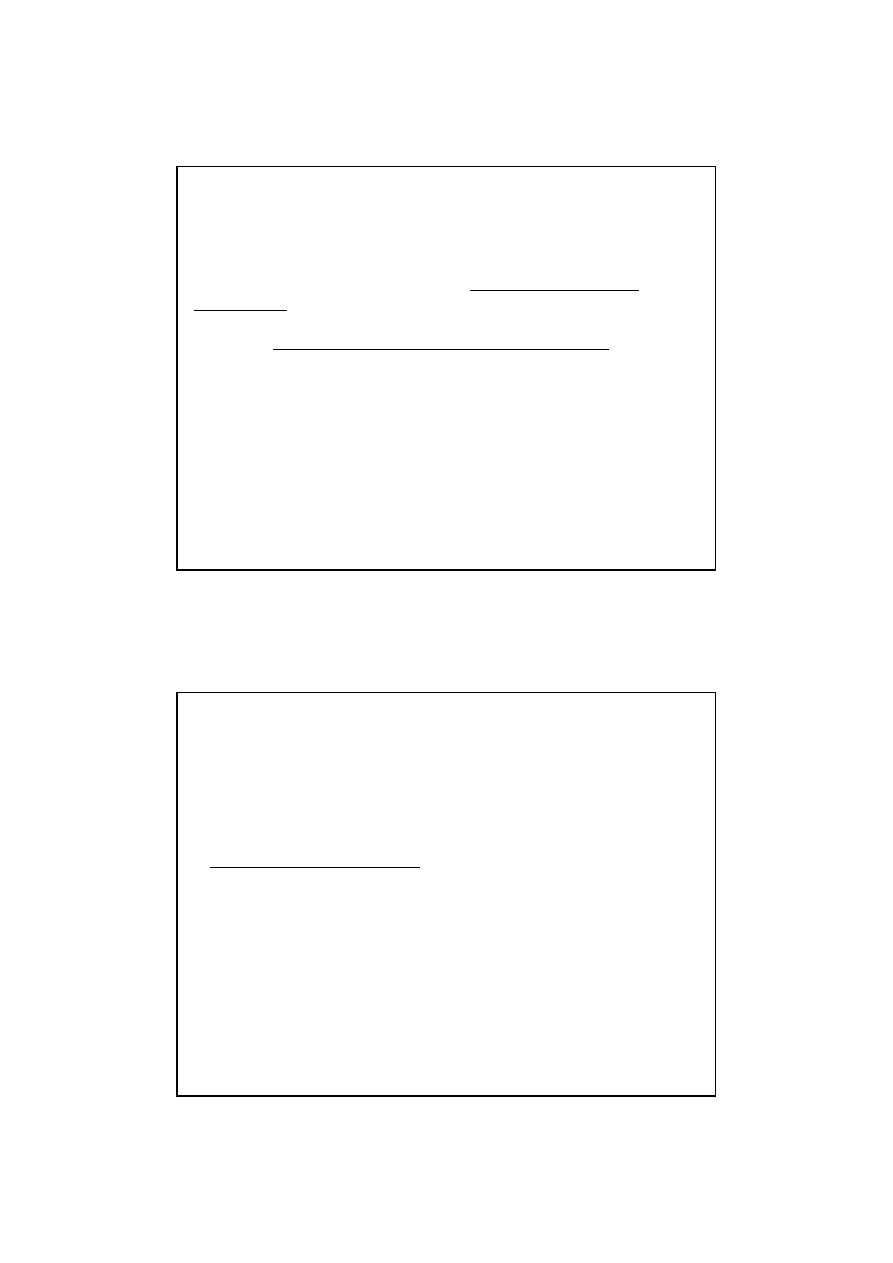

Technologia TTL

Układy scalone bipolarne

Nadal popularne w prostych układach

Oznaczenia serii (przykład: SN 74LS00N)

SN – symbol producenta (SN)

74 – technika TTL „cywilna” temp. robocza 0-70

0

C (54 – „wojskowa”,

temp -55 - +125

0

C)

LS – odmiana technologii (S, ALS, F, AS)

00 – kod układu 2 lub 3 cyfry (tutaj 4xNAND)

N - rodzaj obudowy (tutaj dwurzędowa plastik)

Nowoczesne zamienniki CMOS (np. HCT)

Podstawowe parametry układów

Maksymalna szybkość pracy – czas propagacji

Moc strat

Odporność na zakłócenia

Obciążalność – ile mogę podłączyć wejść do pojedynczego

wyjścia

Parametry typowe

Parametry graniczne

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

6

Moc strat

Zależna od:

technologii budowy układu

częstotliwości (pośrednio)

ilości przełączeń na sek.

obciążenia

konstrukcji całego układu elektronicznego

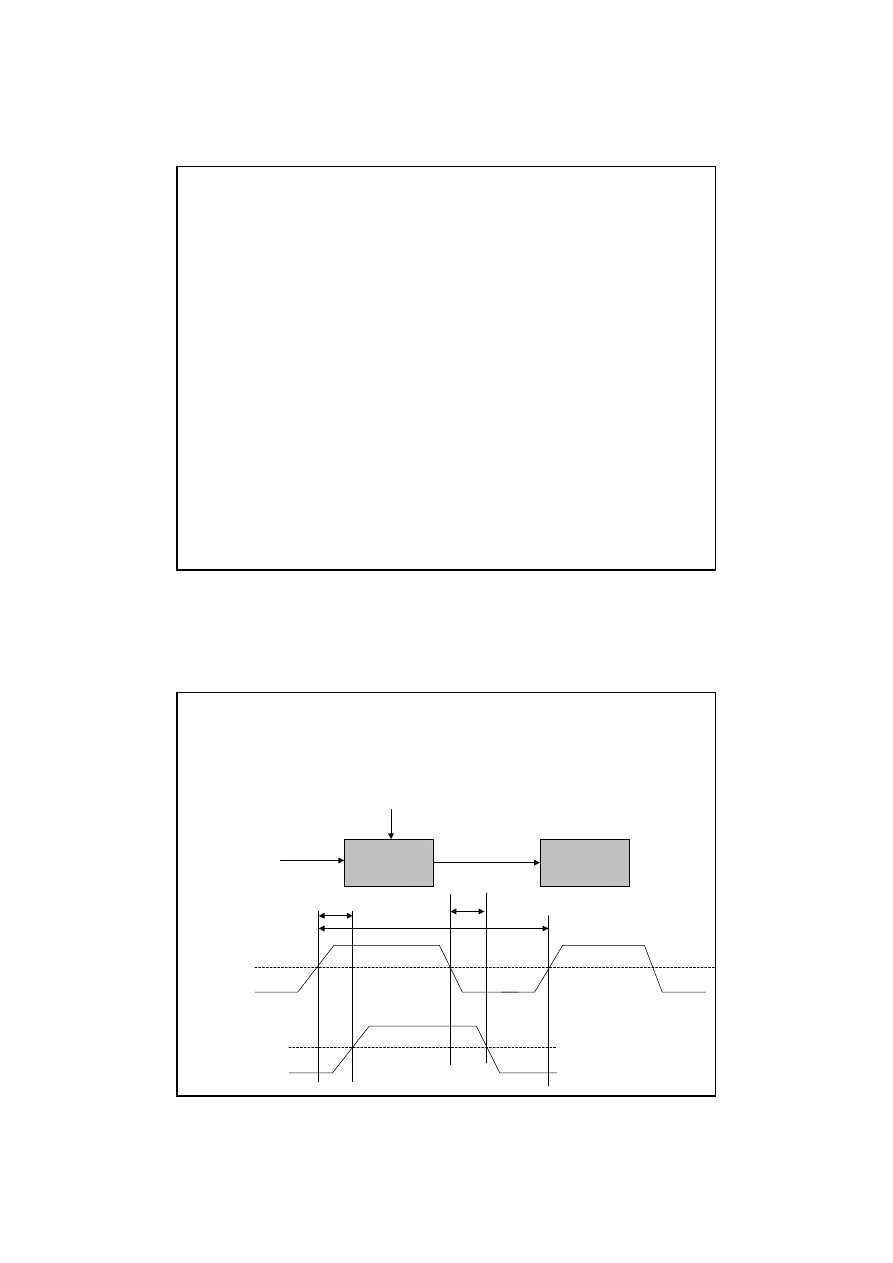

Czas propagacji t

p

Układ cyfrowy

Obci

ąż

enie

(inny układ)

wej

ś

cie

wyj

ś

cie

zasilanie

U

i

U

o

t

pHL

t

pLH

U

i

U

o

T=1/f

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

7

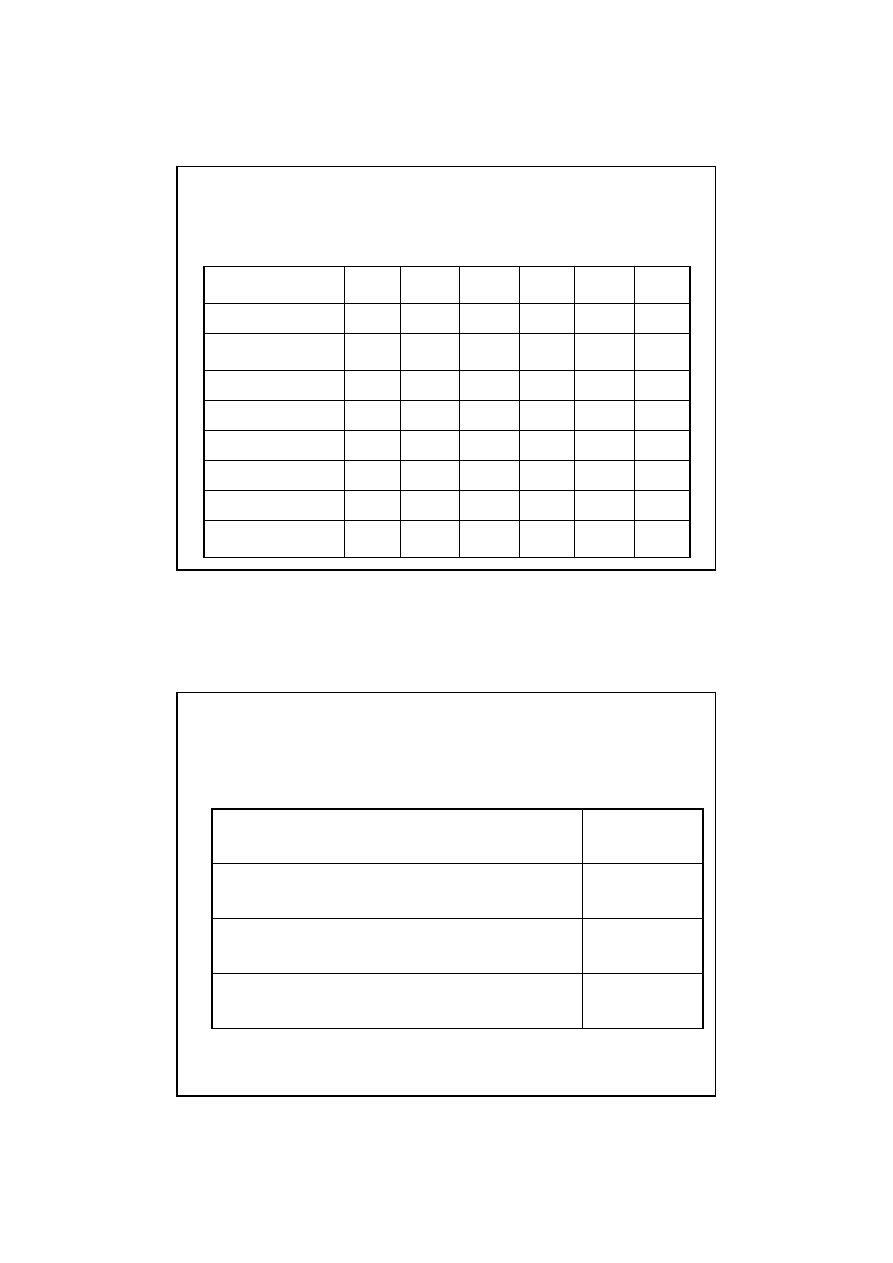

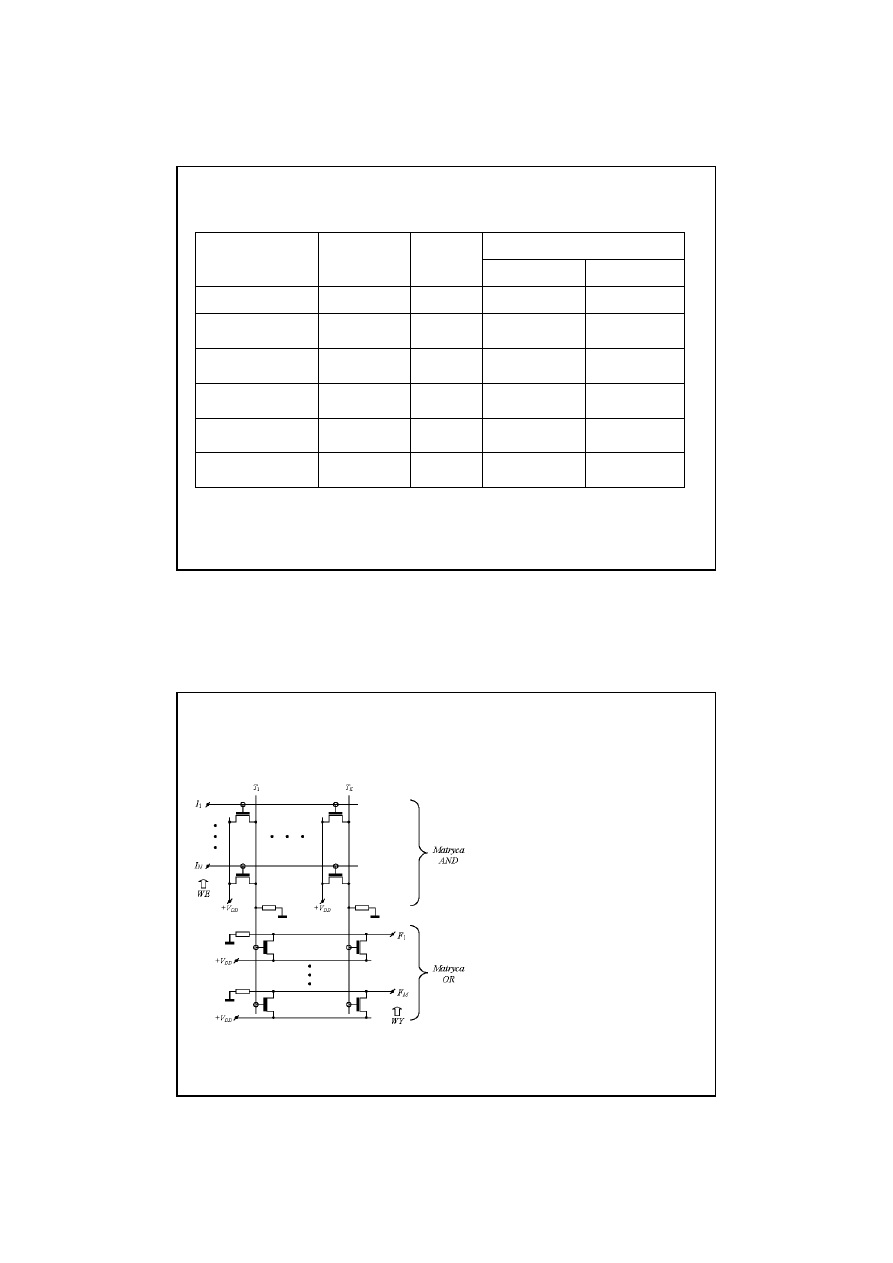

Parametry układów rodziny TTL

13,6

5

19,2

18

57

100

Wsp dobroci (im mniej tym

lepiej) P

O

*t

p

48

40

33

20

10

10

Obci

ąż

alno

ść

N

max

0,5

0,2

0,6

0,4

2

1,6

Pr

ą

d wej I

ILmax

[mA]

20

8

20

8

20

16

Pr

ą

d wyj I

LOHmax

[mA]

2

0,4

1

0,4

1

0,4

Pr

ą

d wyj I

OHmax

[mA]

200

50

150

33

125

25

Max. Cz

ę

st. Rob [MHz]

8

1

5,5

2

19

10

Moc strat na bramk

ę

P

O

[mW]

1,7

5

3,5

9

3

10

Czas propagacji t

p

[ns]

AS

ALS

F

LS

S

TTL

Parametry stanów H i L

0,8 [V]

Maks napi

ę

cie wej w stanie L

0,4 [V]

Maks napi

ę

cie. wyj w stanie L

2,0 [V]

Minimalne nap. wej w stanie H

2,4 [V]

Minimalne nap wyj w stanie H.

Margines zakłóce

ń

0,4V (2,4-2,0) oraz (0,8-0,4)

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

8

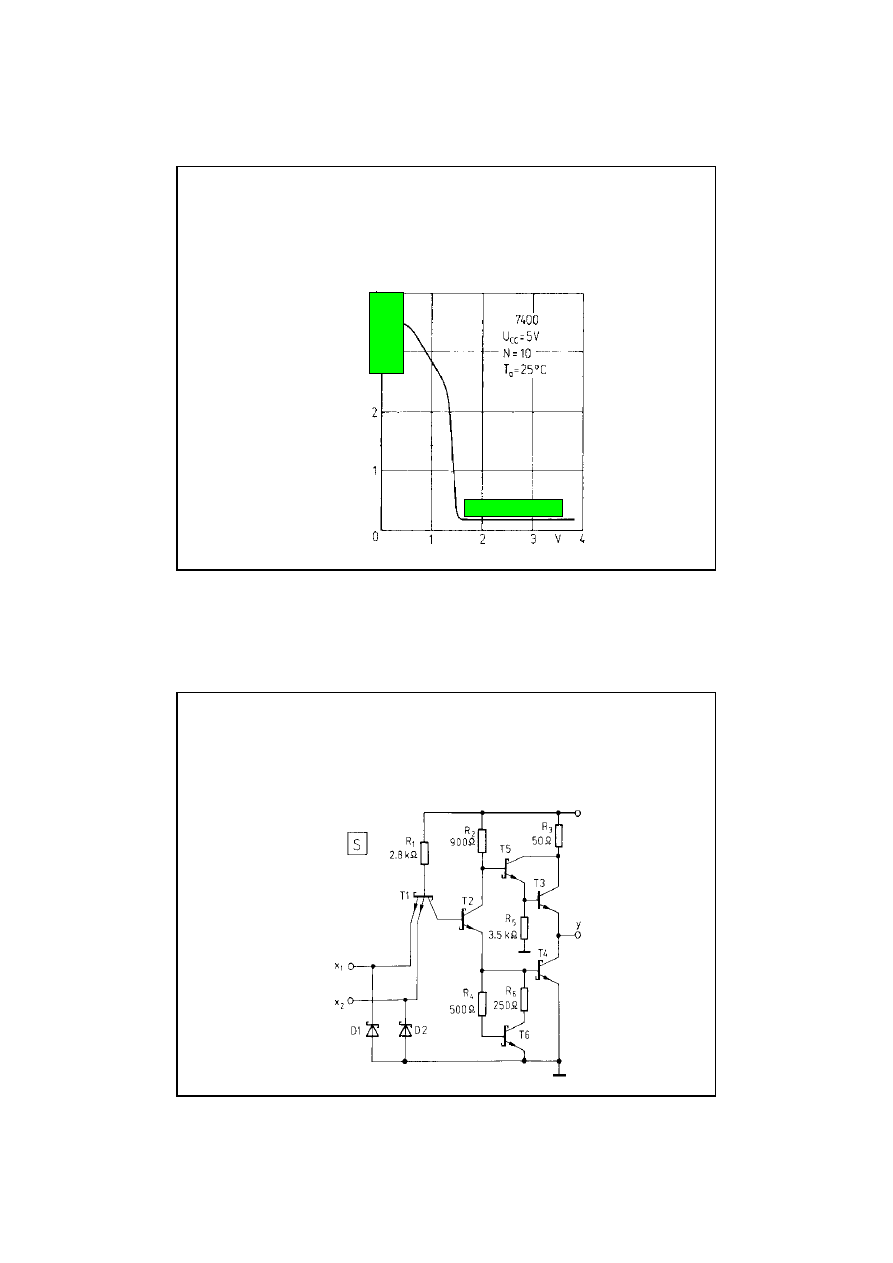

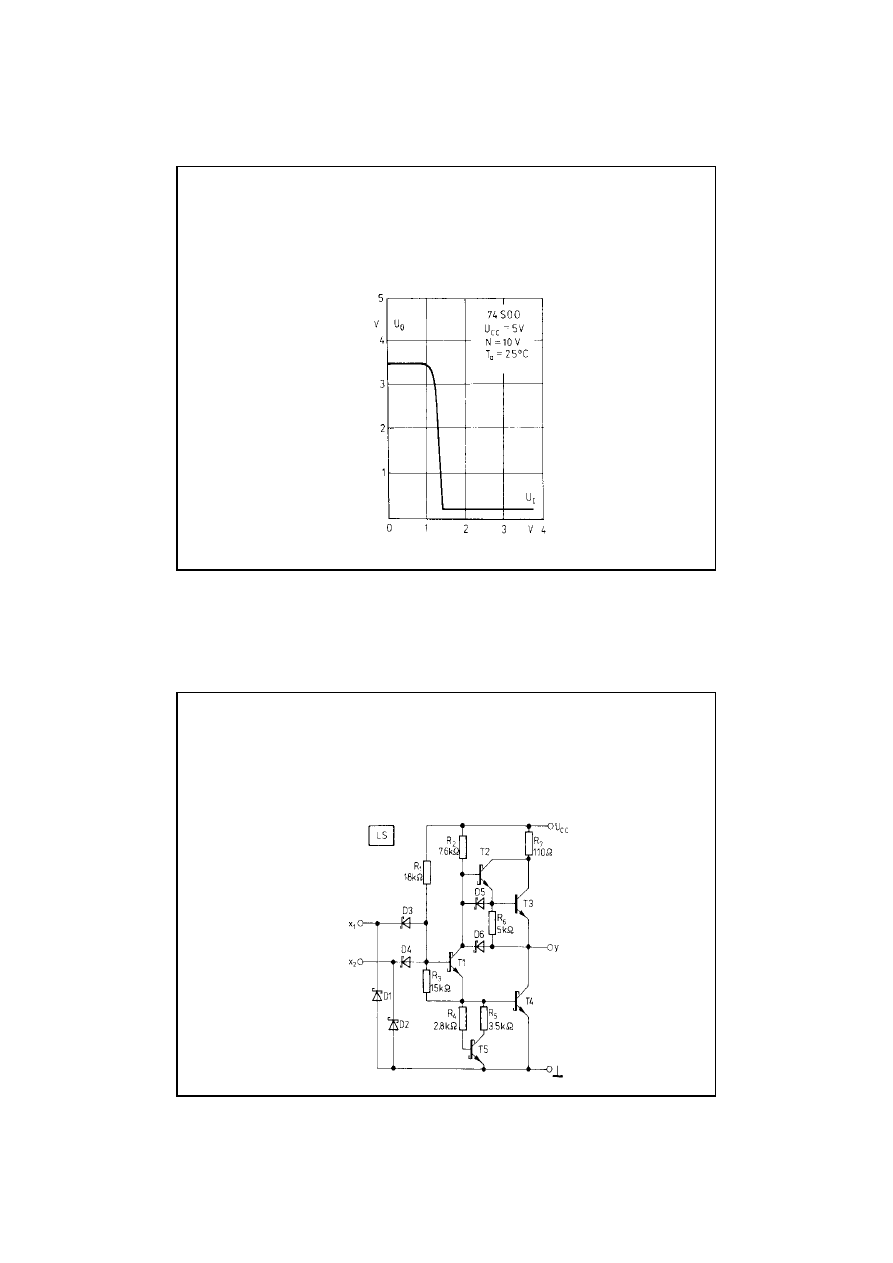

Charakterystyka napięciowa przejściowa i zakres

pracy

Podstawowa bramka TTL-S

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

9

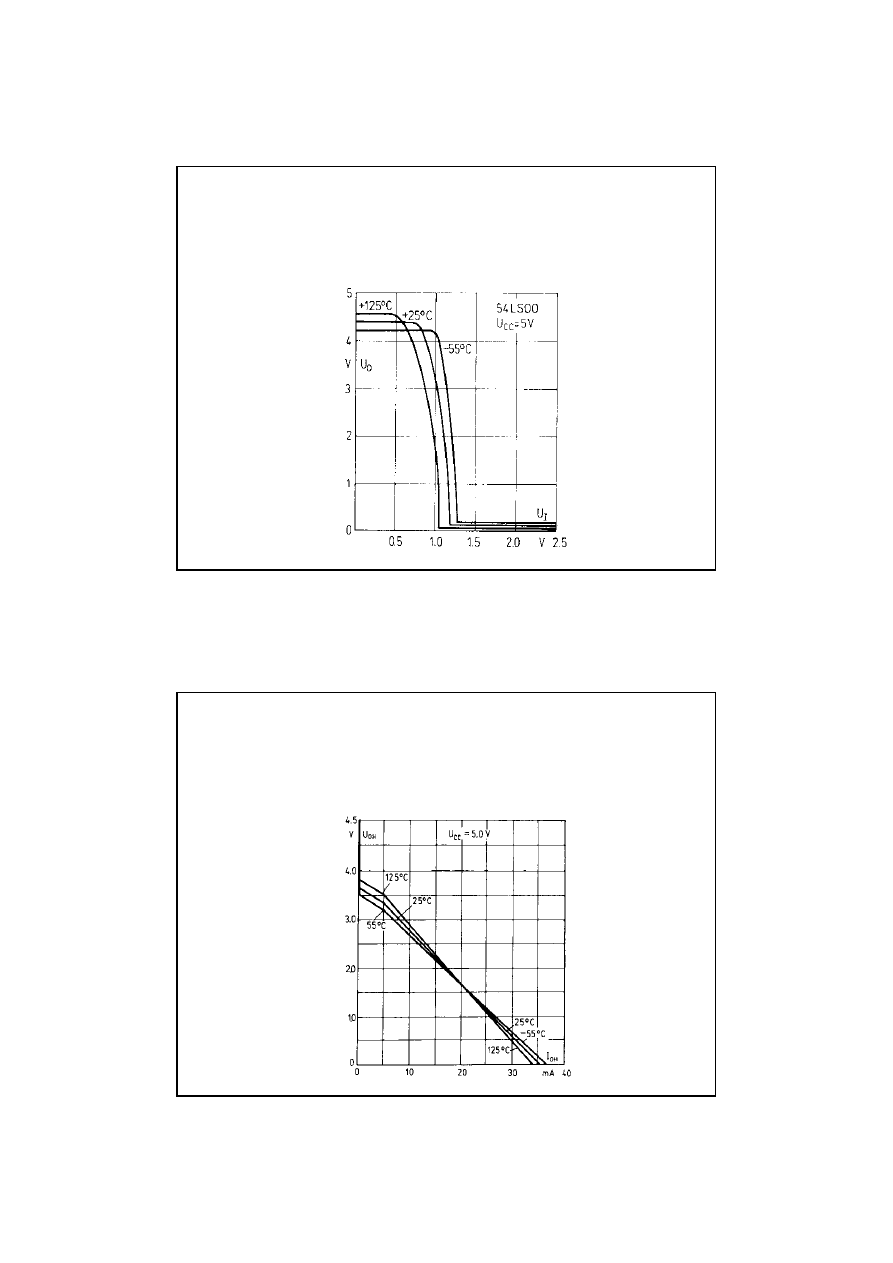

Charakterystyka układu TTL-S

Podstawowa bramka TTL-LS

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

10

Charakterystyka przejściowa układu TTL-LS

Charakterystyka wyjściowa – stan wysoki

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

11

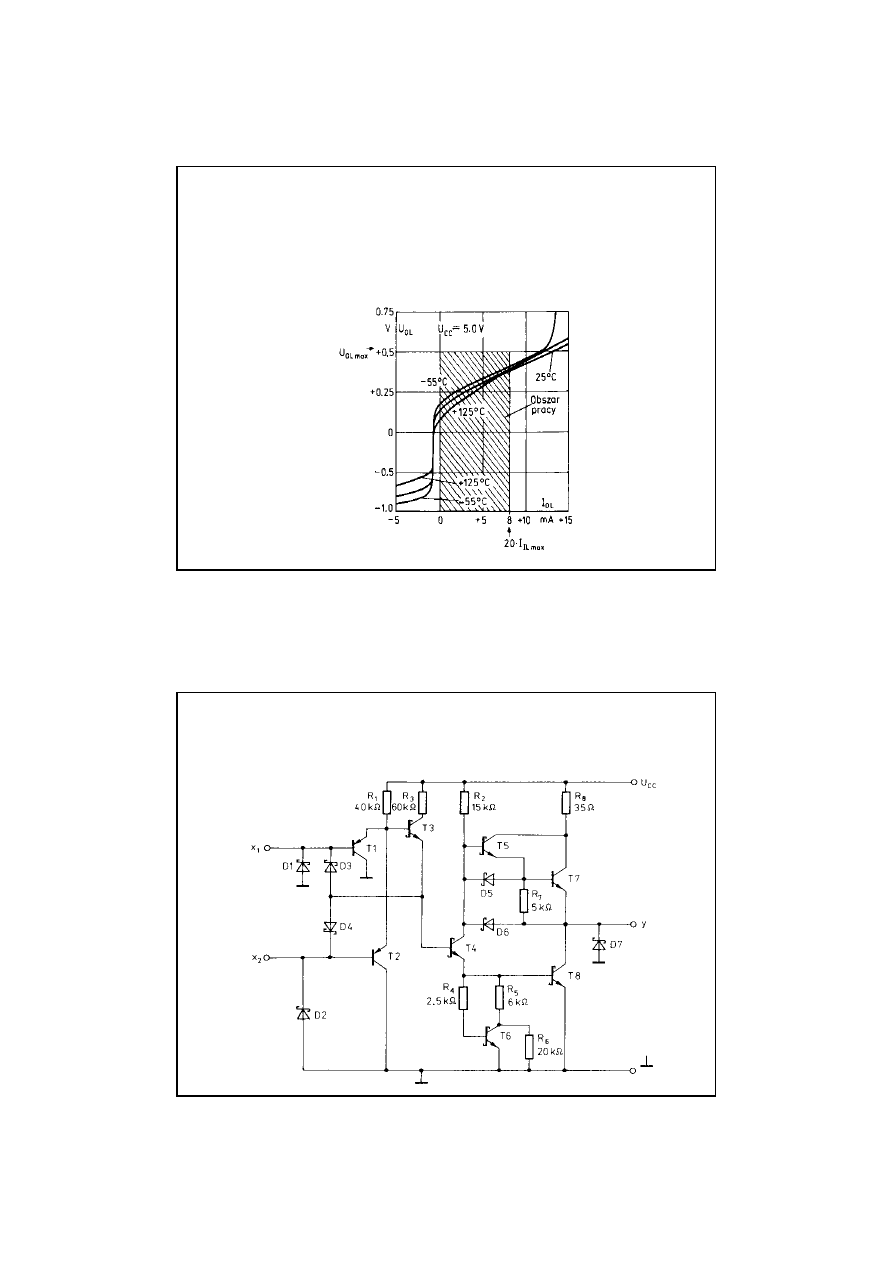

Charakterystyka wyjściowa – stan niski

Technologia ALS

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

12

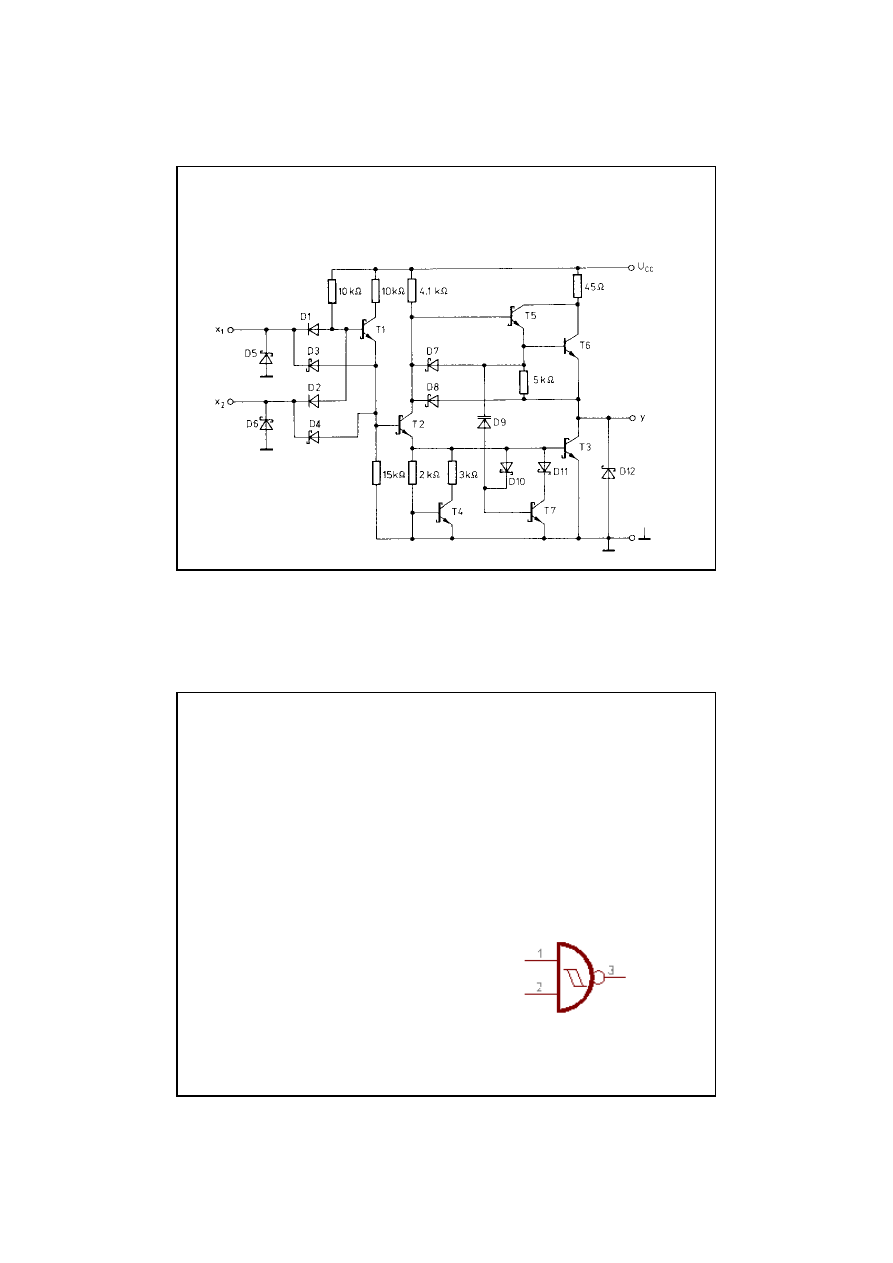

Technologia F

Układy Schmitta

Układ „dyskryminuj

ą

cy”

Zamiana sygnału analogowego na cyfrowy,

Eliminacja zakłóce

ń

Transmisja danych

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

13

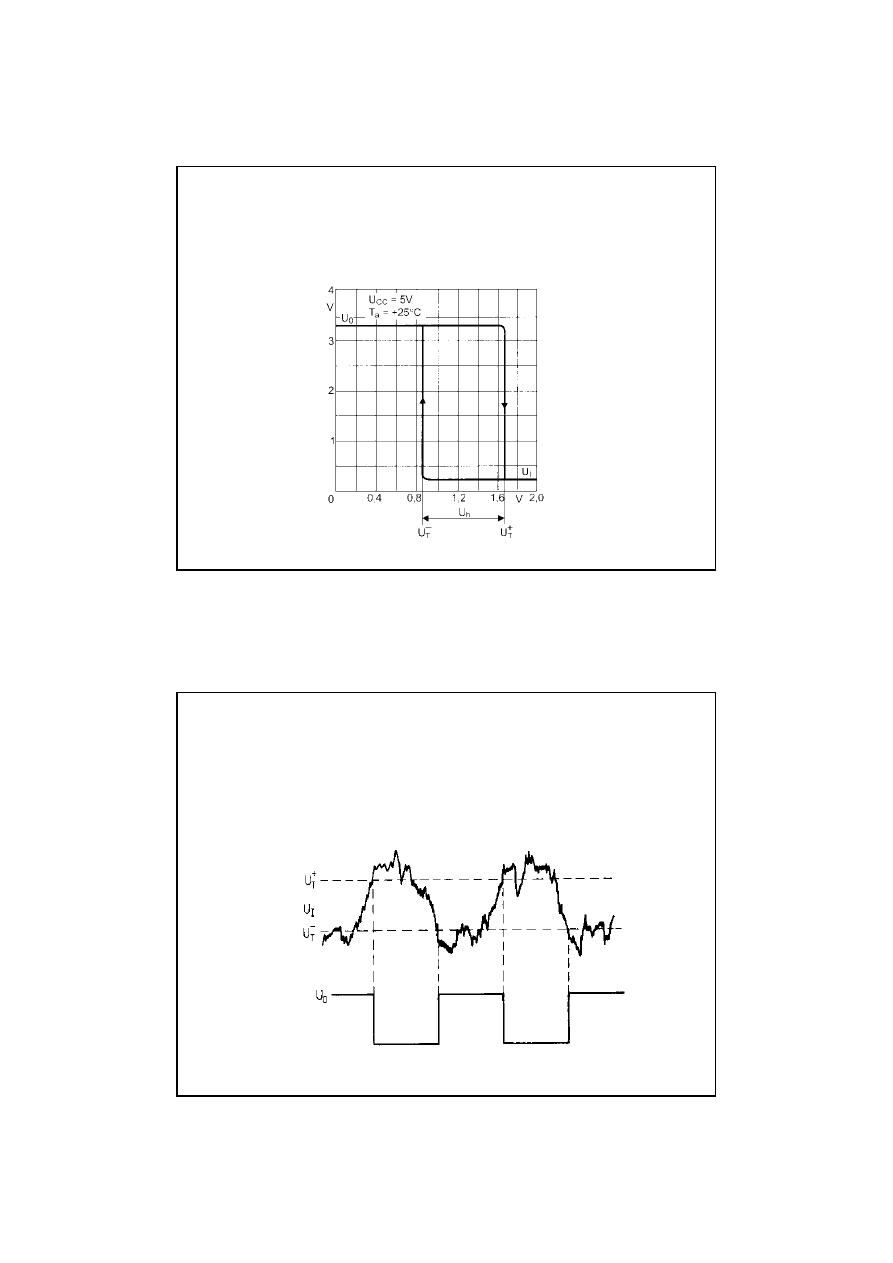

Charakterystyka układy Schmitta

Działanie układu Schmitta w praktyce

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

14

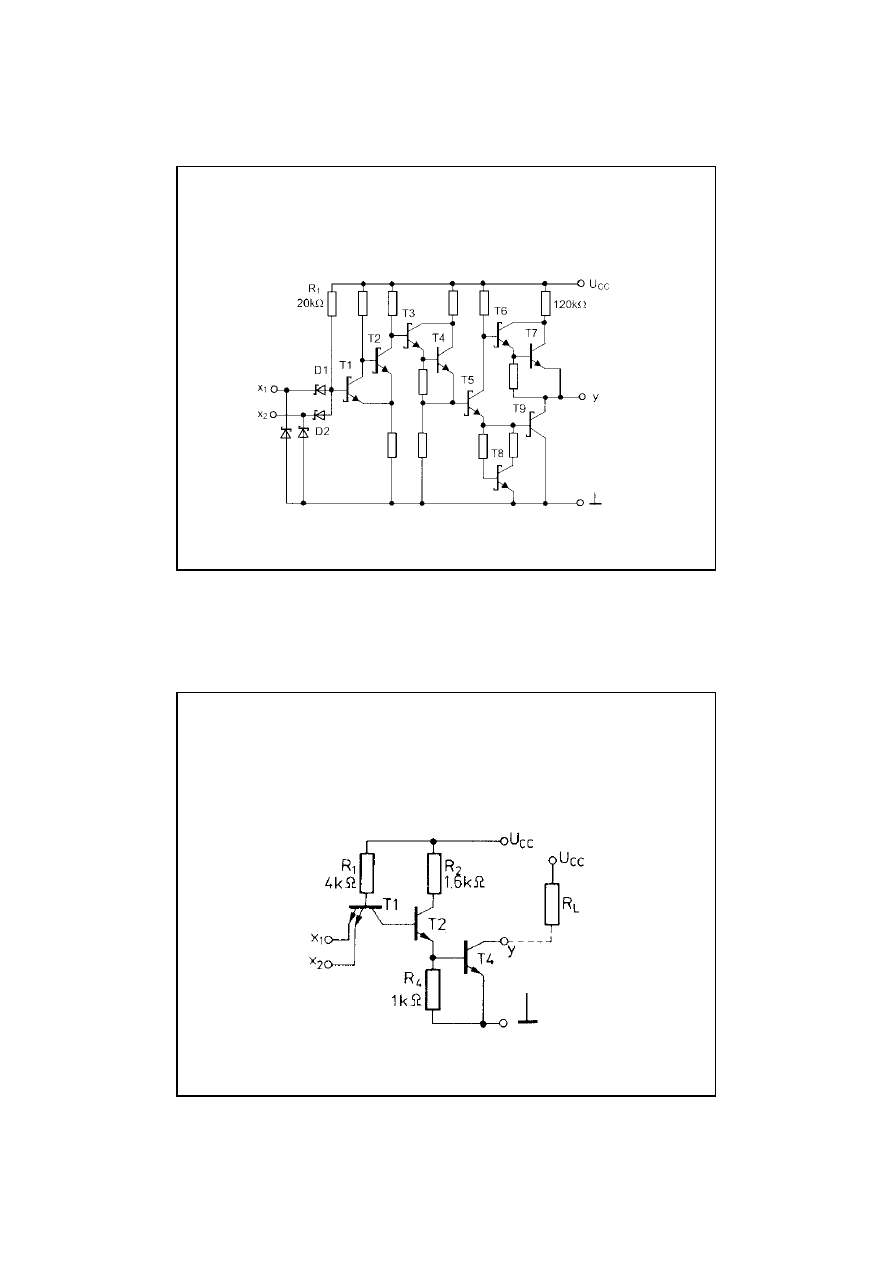

Budowa bramki wejściem Schmitta

Bramki „otwarty kolektor”

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

15

Technologia MOS

Mniejszy mo

ż

liwy rozmiar tranzystora,

Uproszczenie konstrukcji i produkcji,

Rodziny NMOS, PMOS

CMOS (Complementary MOS)

Wada to wra

ż

liwo

ść

na ładunki elektrostat.

(osto

ż

nie z paluchami!!!)

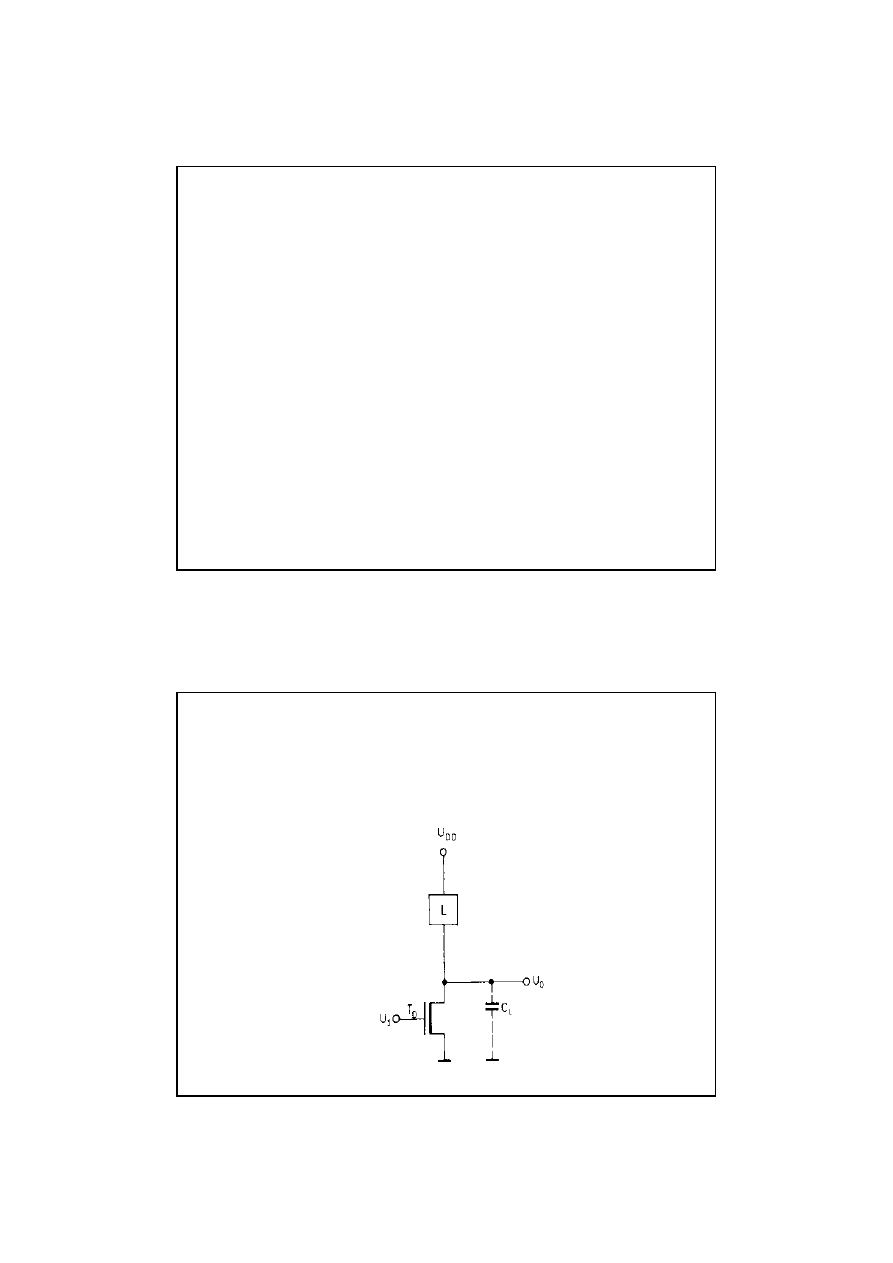

Najprostsza bramka MOS

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

16

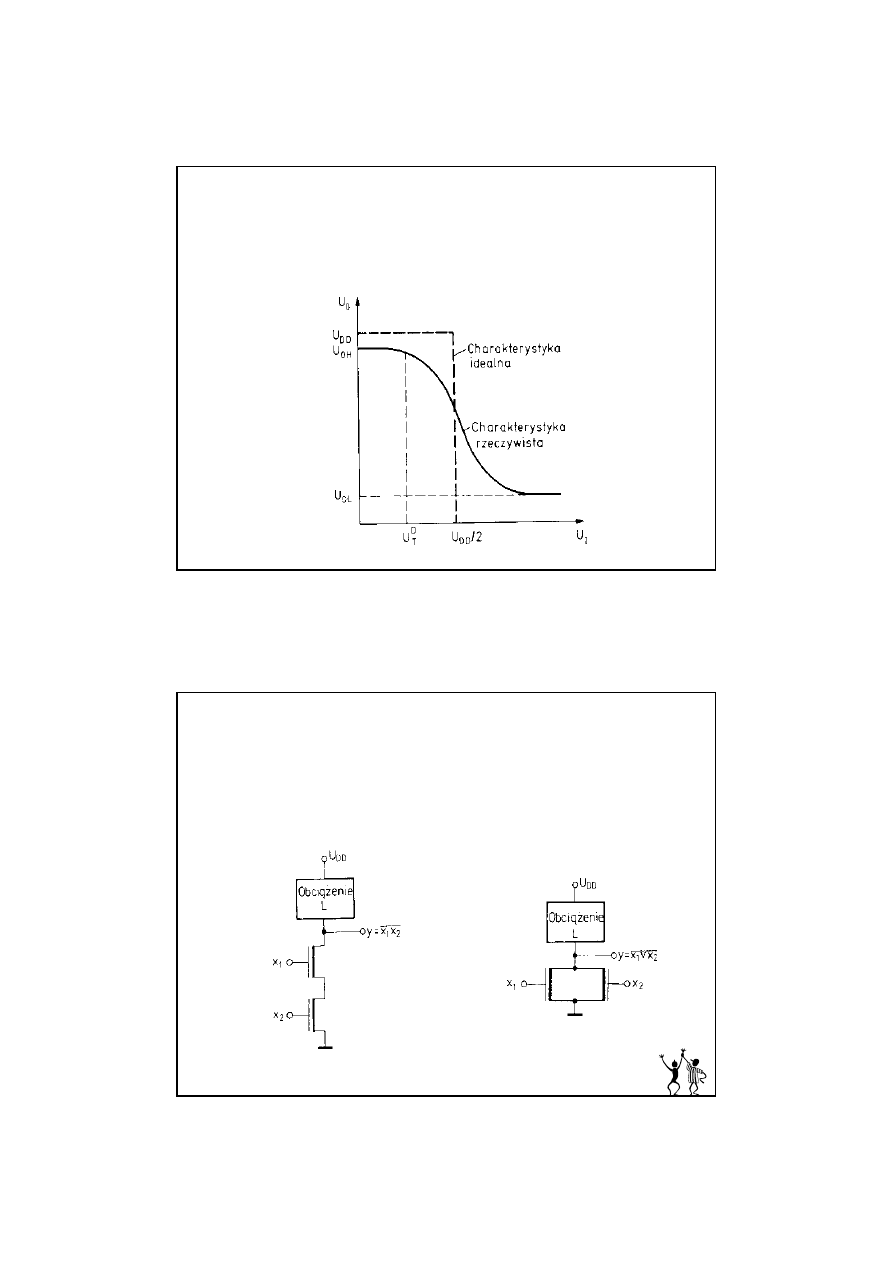

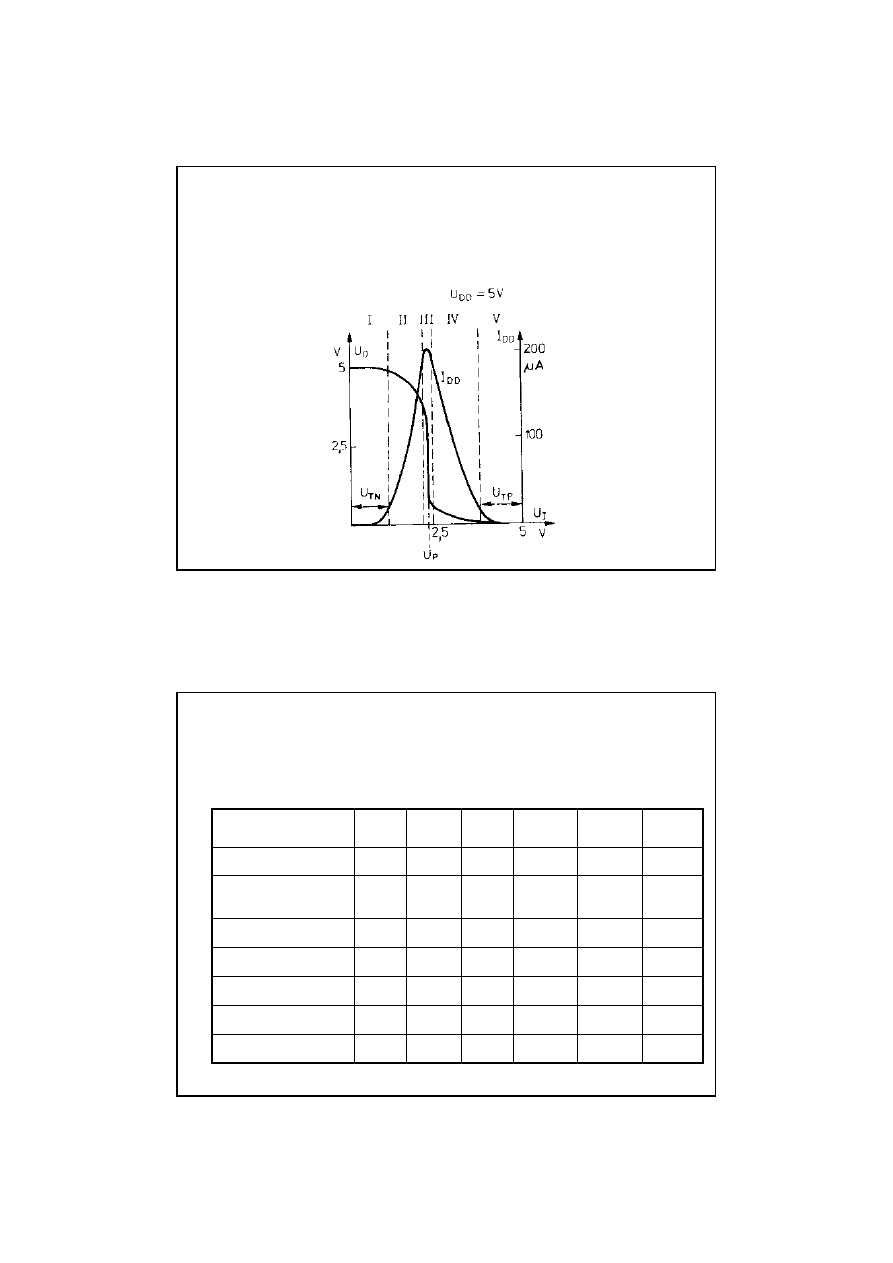

Charakterystyka przejściowa

Podstawowa bramka MOS

NAND

NOR

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

17

Charakterystyki napięciowa i prądowa

Porównanie parametrów TTL-CMOS

3-18

3-18

3-18

5

±

5%

5

±

5%

5

±

5%

Nap zasil

1

1

0,1

600

200

400

Pr

ą

d wej I

ILmax

[uA]

8

4

0,4

20

8

8

Pr

ą

d wyj I

LOHmax

[mA]

8

4

2,1

1

0,4

0,4

Pr

ą

d wyj I

OHmax

[mA]

115

50

4

150

50

33

Max. Cz

ę

st. Rob [MHz]

0,0025

0,0025

0,001

5,5

1

2

Moc strat na bramk

ę

P

O

[mW]

5,2

8

125

3,5

5

9

Czas propagacji t

p

[ns]

AHC

HC

CMOS

F

ALS

LS

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

18

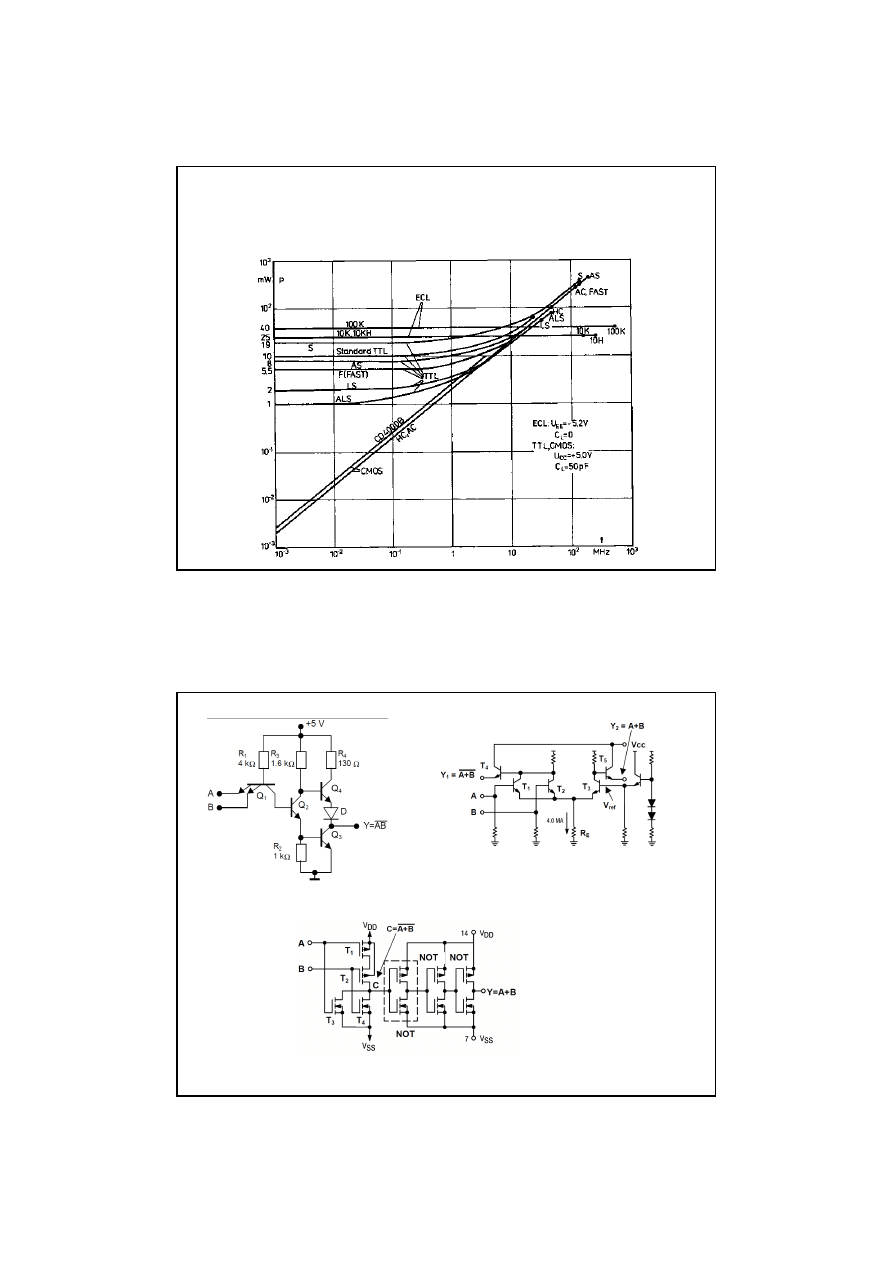

Pobór mocy w funkcji częstotliwości

Bramka NAND w standardowej serii TTL

Bramka (N)OR w technologii CMOS

Bramka NOR OR w standardowej serii ECL

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

19

Układy ASIC

Application Specific Integrated Circuits

Podstawowy podział cyfrowych układów scalonych:

• Wielkie standardy: standardowe, uniwersalne elementy o strukturze niemodyfikowalnej po

wyprodukowaniu; np. bramki i układy funkcjonalne rodzin TTL, ECL, MOS, mikroprocesory, pamięci...

• Układy ASIC: użytkownik ma w pewien sposób wpływ na strukturę logiczna układu

Full-Custom

Semi-Custom

• Standard Cells

• Gate Arrays

Field Programmable Gate Arrays (układy FPGA)

Programmable Logic Devices (układy PLD)

Rodzaje układów ASIC

• Dwie pierwsze klasy układów ASIC (Full Custom, Semi Custom) – programowalne

w procesie produkcji (programowalne maską).

Użytkownik przekazuje projekt producentowi u.s., układy po wyprodukowaniu mają

już ostateczną architekturę, która nie ulega zmianom.

• Dwie pozostałe klasy układów (PLD, FPGA): wszystkie układy określonego typu

opuszczają producenta identyczne (produkcja wielkoseryjna, niskie koszty),

programowanie układu po jego wykonaniu poprzez utworzenie połączeń w istniejącej

sieci ścieżek sygnałowych.

Zalety ASIC:

Niższe koszty zaprojektowania, wykonania i uruchomienia systemu cyfrowego,

szczególnie przy produkcji wielkoseryjnej.

Możliwości reprogramowania układu - ułatwione testowanie, wprowadzanie zmian w projekcie...

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

20

Full-Custom ASIC

• Użytkownik sam projektuje wszystkie lub wybrane komórki logiczne układu, rozmieszczenie

oraz połączenia.

• Stosowane przeważnie w układach nowych lub wysoce specjalizowanych, gdy brak gotowych

projektów wymaganych komórek.

• Produkcja we wsadach po 5 ÷ 30 wafli (wafer), każdy wafel zawiera 10 ÷ 100 układów.

Standard-Cell ASIC

• Układ projektowany z predefiniowanych standardowych komórek (standard cells),

zaprojektowanych w trybie full-custom; dostępne komercyjne biblioteki standardowych komórek.

• Duże komórki, realizujące złożone bloki funkcjonalne (np. mikroprocesory) - tzw. mega cells, cores.

• Regularny rozkład komórek w układzie, zwykle rzędy (wiersze) komórek

o stałej wysokości i zmiennej długości ⇒ uporządkowana struktura połączeń.

Gate-Array ASIC

• Regularna, niezmienna struktura elementów układu (matryca elementarnych bloków logicznych),

użytkownik projektuje sieć połączeń (warstwy metalizacji).

• Standardowe układy produkowane seryjnie i „magazynowane”, po otrzymaniu projektu dodawane

tylko warstwy metalizacji.

• Taniej i szybciej niż standard-cell. Cykl produkcji dni-tygodnie.

Układy PLD (Programmable Logic Devices)

• Standardowe, produkowane masowo układy scalone opuszczają producenta w identycznej postaci.

• Nie ma modyfikowanych masek (komórki logiczne czy metalizacje),

jeden duży blok programowanych połączeń programowanie wyłącznie po stronie użytkownika.

Przykłady:

- programowalne pamięci tylko do odczytu (PROM)

- układy PAL, PLA: dwupoziomowa struktura sumy iloczynów,

realizująca zaprogramowaną funkcję boolowską.

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

21

Układy FPGA

• Nazywane także FPLD (Field Programmable Logic Devices).

• Zasada programowania podobna do PLD, ale bardziej złożona struktura.

• Programowanie nie tylko sieci połączeń (jak w PLD), ale także pewien sposób konfigurowania

funkcji komórek logicznych:

- struktura układu: regularny układ komórek logicznych, które zawierają pewną (programowalną)

logikę kombinacyjną oraz przerzutnik(i);

- komórki logiczne otoczone siecią (programowalnych) linii sygnałowych.

• Liderzy architektur FPGA: firmy Xilinx oraz Altem.

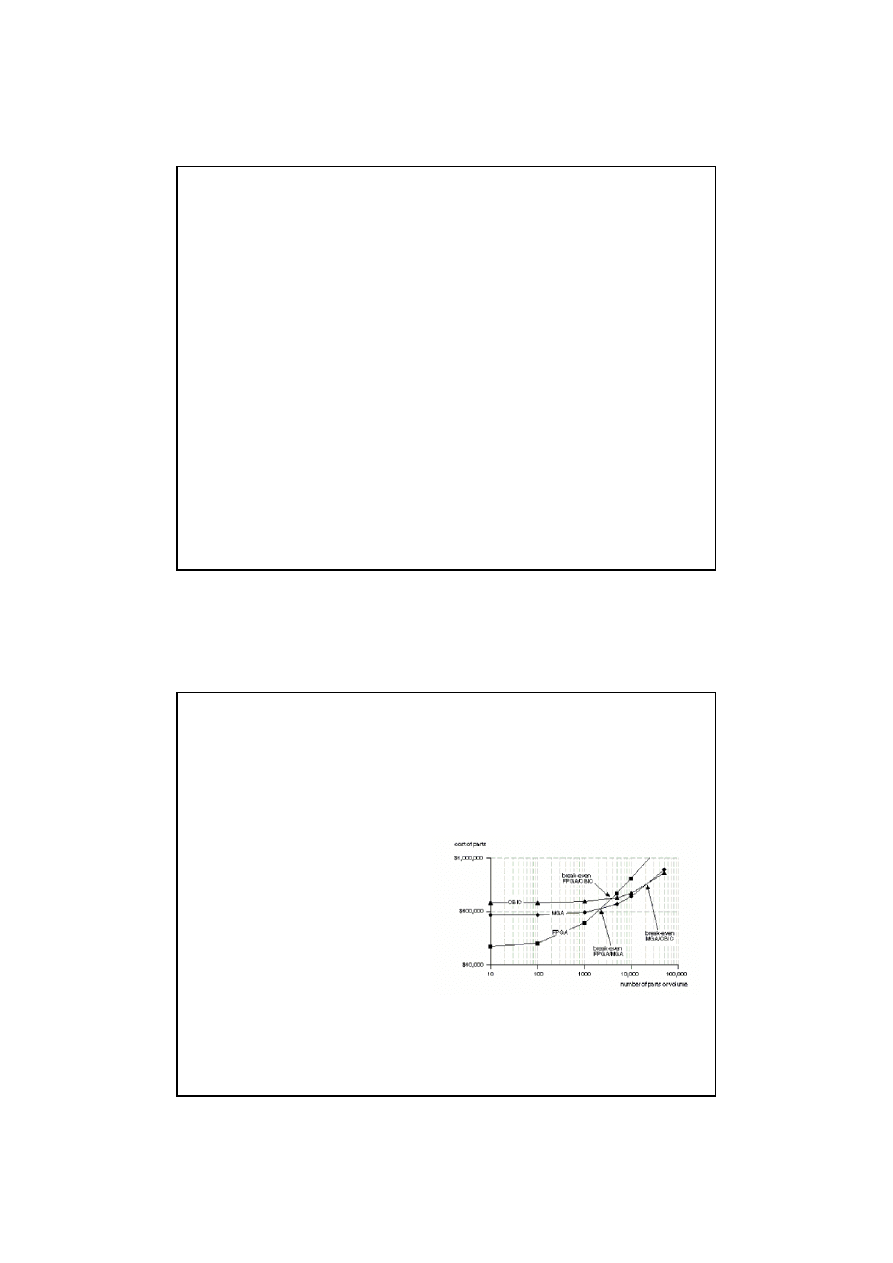

Rachunek ekonomiczny układów ASIC

Koszt całkowity projektu i produkcji” =

= koszt stały (przygotowanie projektu) +koszt jednostkowy (koszt u.s., montażu itp.) x liczba egzemplarzy

Przykład:

Porównanie trzech technologii

CBIC (cell-based IC = standard cell ASIC)

MCA (mask programmable gate array)

FPGA

Koszty:

(stały)

(jednostkowy)

CBIC:

146000 $ 8 $

MGA:

86000 $

10 $

FPGA:

21800 $

39 $

Wyrównanie kosztów:

FPGA vs Gate Array

2000 szt.

FPGA vs. Standard Cells

4000 szt.

Gate Array vs. StandardCells

20000 szt.

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

22

Układy programowalne

PLD

SPLD

CPLD

FPGA

OTP

(EPROM, Fuse)

OTP

(EPROM)

OTP

(Antifuse)

Reprogramowalne

(EEPROM, Flash)

Reprogramowalne

(EEPROM, Flash)

Reprogramowalne

(SRAM)

Klasyfikacja układów programowalnych

Programowanie układów PLD & FPGA

• „Programowanie układu”: utworzenie (lub nie) połączeń w określonych punktach linii sygnałowych,

tzw. punktach programowalnych ⇒ określenie dróg przesyłania sygnałów pomiędzy elementami

układu (bramkami, przerzutnikami, blokami funkcjonalnymi) i uzyskanie w ten sposób układu

kombinacyjnego lub sekwencyjnego o żądanej funkcji.

• Ogólna struktura nie zaprogramowanego układu wyznacza nieprzekraczalne ramy projektu

(programowaniu podlega sieć połączeń między elementami zawartymi w układzie,

nie rodzaj i liczba owych elementów).

• Trzy główne technologie programowania - analogiczne do realizacji programowalnych pamięci

tylko do odczytu (ROM):

- programowanie jednokrotne (Programmable ROM, PROM)

- programowanie kasowalne przez naświetlenie promieniami UV

(Erasable Programmable ROM, EPROM)

- programowanie kasowalne elektrycznie (Electrically Erasable PROM, EEPROM, E

2

PROM)

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

23

Programowanie nieodwracalne (One -Time Programming, OTP)

A. Bezpieczniki (Fuses)

• Technologia chronologicznie pierwsza, związana z układami bipolarnymi.

• Metoda: przepalenie bezpiecznika - fragmentu odpowiednio przygotowanej ścieżki metalizacji.

B. Antybezpieczniki (Antifuses)

• Antybezpiecznik jest normalnie rozwarty (off); przepuszczenie odpowiednio dużego

prądu (5 ÷ 15 mA) stapia izolujący dielektryk i powoduje stałe zwarcie (on).

• Antybezpieczniki zajmują mniej miejsca, dzięki niskiej rezystancji i pojemności są także szybkie.

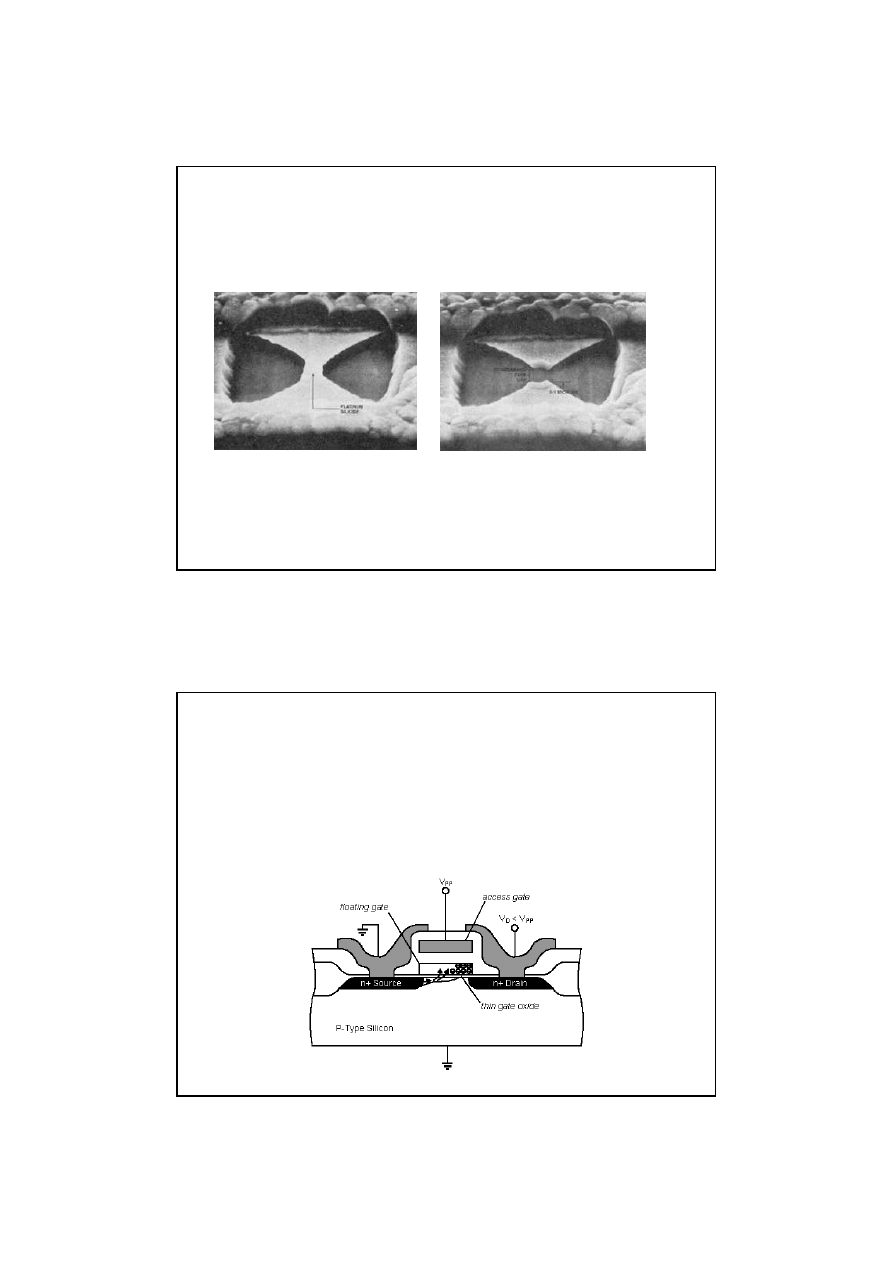

Programowanie kasowalne (Erasable Programming)

• Technologia MOS, jako programowane połączenie tranzystor

• EPROM i EEPROM: tranzystor nMOS z bramka swobodną (floating gate)

• Programowanie EPROM - hot electron tunneling:

Napięcie programowania V

PP

>>+5V (+15 ÷ 20V), lawinowe wstrzykniecie elektronów

na bramkę swobodną ⇒ przesunięcie napięcia progowego tranzystora powyżej +5 V

(tranzystor stale odcięty)

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

24

Kasowanie:

• Naświetlenie promieniowaniem jonizującym (UV 2537 ), jonizacja dielektryka umożliwia

wzbudzonym elektronom spłynięcie z bramki swobodnej.

• Obudowy z oknem ze szkła kwarcowego.

• Powolne; trwa od kilku sekund do kilkunastu minut.

• Jeśli trwa za długo niebezpieczeństwo nieodwracalnego pozbawienia bramki swobodnej możliwości

uwięzienia elektronów (over-erasure).

• Samoczynne kasowanie pod wpływem promieniowania słonecznego, promieniowania tła

(trwałość zapisu ograniczona).

• Ograniczona ilość cykli programowanie - kasowanie; rzędu 1000.

W sumie:

• Czas programowania dość długi (5 ÷ 10 µs), ale najkrótszy wśród metod programowania odwracalnego.

• Bardzo dobre możliwości scalania (pojedynczy tranzystor jako jednocześnie urządzenie

programujące i odczytujące).

Programowanie kasowalne elektrycznie (Electrically Erasable Programming)

• Inna metoda wprowadzania elektronów na bramkę swobodną:

efekt tunelowy Fowlera - Nordheima, wstrzyknięcie elektronów wprost z drenu.

• Cieńsza warstwa dielektryka, niższe napięcie programowania (V

GD

~ +12V):

• Niższe natężenie prądu ⇒ dłuższy czas programowania, zwykle rzędu-5 ms.

• Kasowanie: ten sam efekt przy odwróconej polaryzacji napięć = odprowadzenie

elektronów z bramki swobodnej.

• Podczas kasowania niebezpieczeństwo silnego dodatniego naładowania bramki swobodnej

(tranzystor stale otwarty) ⇒ specjalne układy kontrolujące rozładowanie.

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

25

Różne technologie programowania wielokrotnego - podsumowanie:

EPROM

EEPROM

Flash

NOR

NAD

V

cc

[V]

5; 12

5

5; 3,3; 2,5

5; 3,3

Program/erase cycles

~10

3

~10

5

~10

5

~10

6

Program method

Hot electron

FN tunneling

Hot electron

FN tunneling

Erase method

UV light

FN tunneling

FN tunneling

FN tunneling

Program time

10 µs / Byte

5 ms / Byte

10 µs / Byte

300 µs / 512 Byte

Erase time

~30 min

10 ms / chip

1 s / 64 kByte

5 ms / 16 kByte

Pamięci Flash = technologia E

2

PROM + możliwość jednoczesnego kasowania wszystkich

lub grupy komórek.

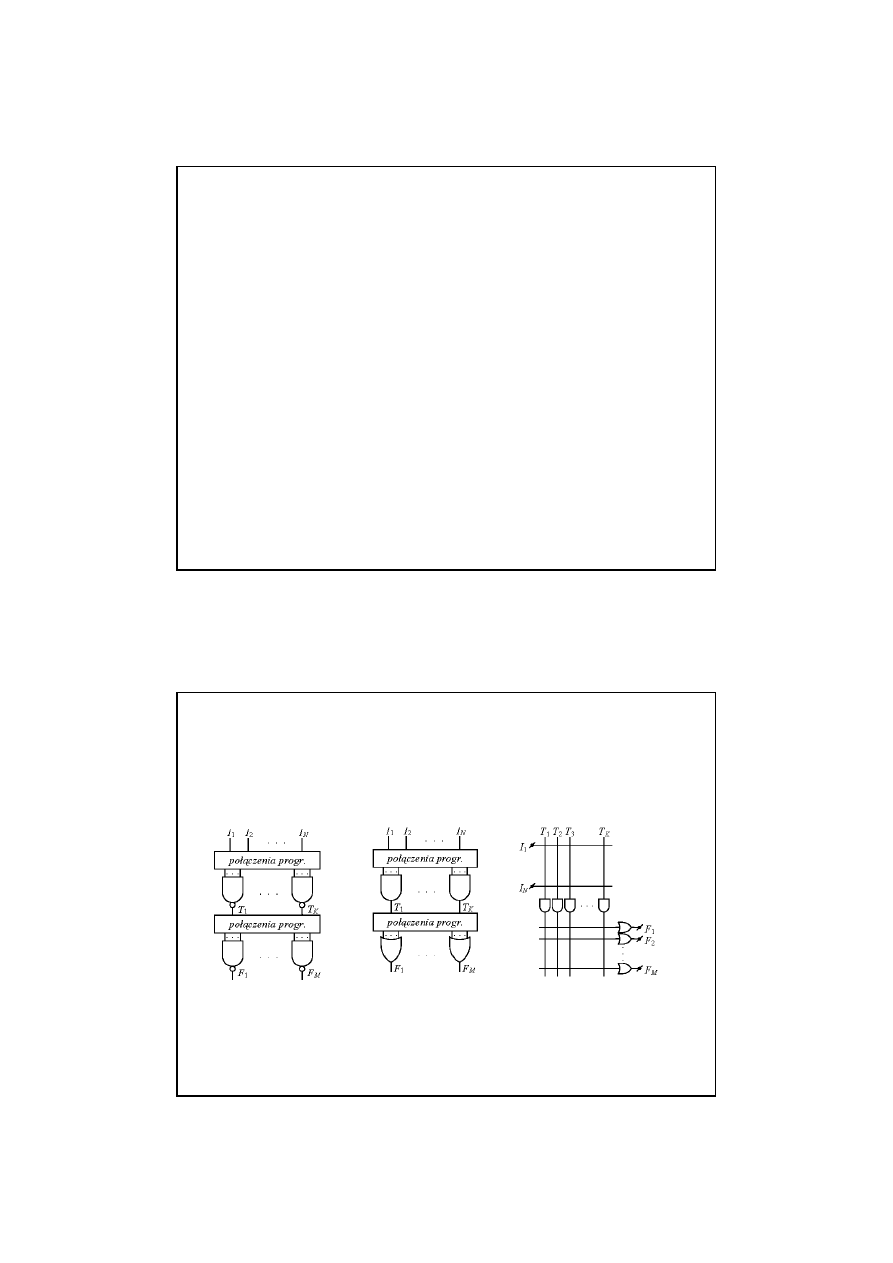

Układy PLD

Matryca programowalna

Elementy:

• N linii poziomych z sygnałami WE I

1

...I

N

,

• K linii pionowych reprezentujących

tzw. termy T

1

... T

K

,

• M linii poziomych z sygnałami WY F

1

...F

M

,

• połączenia programowalne (oznaczone

kółkami).

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

26

Analiza pracy:

• Tranzystory MOS otwierane poziomem „0” logicznego (napięciem niskim).

Wówczas:

T

k

= 0 wszystkie tranzystory termu k w matrycy górnej są zamknięte punkty są

nie zaprogramowane lub na dołączonych wejściach I

i

= 1.

• Czyli: T

k

= 0 wszystkie uczestniczące w nim sygnały WE są równe 1 ⇒ funkcja NAND:

T

k

= NAND(α

k1

+I

1

, α

k2

+ I

2

, ..., α

kN

+ I

N

)

gdzie:

α

ij

= 0 punkt programowalny jest zwarty (WE I

j

dołączone)

α

ij

= 1 punkt programowalny jest rozwarty (WE I

j

nie dołączone)

• Analogicznie pracuje matryca dolna:

F

m

= NAND(β

m1

+T

1

, β

m2

+T

2

, ..., β

mN

+ T

N

)

gdzie:

β

ij

= 0 lub 1 w zależności od zaprogramowania j.w.

a) Schemat symboliczny matrycy programowalnej

b) Schemat równoważny z praw de Morgana

c) Postać symboliczna używana w schematach układów PLD

Podstawy Techniki Cyfrowej i

Mikroprocesorowej

27

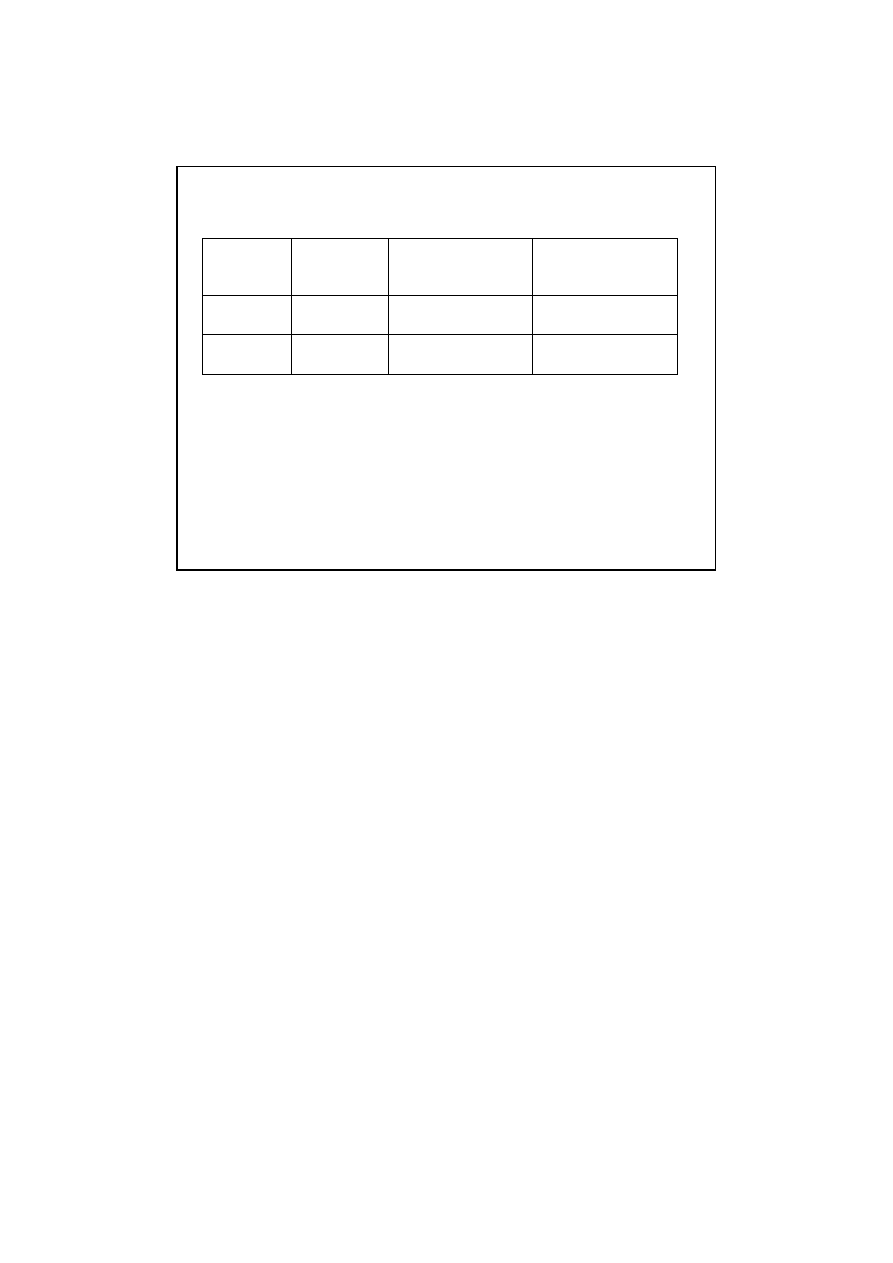

Klasyfikacja architektur PLD

Typ układu:

PAL

(Pragrammable

Array Logic)

PLE

(Programmable Logic

Element)

PLA

(Programmable Logic Array)

Matryca AND:

Programowalna

NIEprogramowalna

Programowalna

Matryca OR:

NIEprogramowalna

Programowalna

Programowalna

• Nieprogramowalność oznacza, że w danej matrycy linie sygnałowe są na stałe dołączone do

określonych bramek.

• Np. w układach PAL linie termów są na stałe dołączone do bramek OR: matryca OR

jest nieprogramowalna, każda bramka OR ma swój zestaw termów, każdy term na dołączony do

dokładnie jednej bramki OR. Programowanie decyduje o tym, jakie sygnały WE uczestniczą

w wyznaczaniu poszczególnych termów.

Wyszukiwarka

Podobne podstrony:

TECHNIKA CYFROWA wykład3

TECHNIKA CYFROWA1 WYKLAD11

Technika cyfrowa Wykład II, Arytmetyka systemów cyfrowych cd

Cyfrówka wykład ściąga, Semestr V, Technika cyfrowa

Technika Cyfrowa (mazurkiewicz) -wyklady, edu, el, pwr, Technika Cyfrowa (mazurkiewicz) -wyklady

TC2 wyklad 2009, Elektronika i Telekomunikacja, EiT pwr, Semestr 4, Technika Cyfrowa 2

NOTAKI Z TECHNIKI CYFROWEJ

Metody i techniki?dań społecznych wykład

Technika komputerowa w obrocie towarowym TECHNIKA KOMPUTEROWA wykłady

Laboratorium 4, Politechnika Koszalińska, III semestr, Laboratorium techniki cyfrowej

Przekazniki i styczniki, Nauki Ścisłe Politechnika, Elektronika Teoria, Technika Cyfrowa, Technika C

Lab0, ZUT, Technika Cyfrowa, Technika Cyfrowa, sprawozdaniaTC

4 Podstawy techniki cyfrowej, Podstawy techniki cyfrowej

Lab4, ZUT, Technika Cyfrowa, Technika Cyfrowa, sprawozdaniaTC

techniki komunikacyjne wyklad 4 Notatek pl

ZAGADNIENIA NA EGZAMIN Z MECHANIKI TECHNICZNEJ II DLA SEMESTRU III, sem III, +Mechanika Techniczna I

więcej podobnych podstron