ELEKTRONIKA CYFROWA

SPIS TREŚCI

1. WPROWADZENIE

WPROWADZENIE

Systemy liczbowe

Cyframi arabskimi są znaki: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Cyfry te służą do zapisywania liczb.

Do podstawowych systemów zapisywania liczb należą systemy pozycyjno - wagowe, w których wartość cyfry zależy od miejsca, czyli pozycji, jaką ta cyfra zajmuje w napisanej liczbie. Każda pozycja ma określoną stałą wagę liczbową (znaczenie).

Oznaczając podstawę dowolnego pozycyjnego systemu liczbowego przez p, można każdą n - cyfrową liczbę całkowitą przedstawić w postaci szeregu:

![]()

lub w skróconej postaci:

![]()

gdzie:

p - podstawa systemu, którą jest liczba całkowita dodatnia,

n - numer pozycji

ai - cyfry z zakresu od 0 do p - 1.

Pierwszej cyfrze w lewo od przecinka przypisuje się wagę p0, drugiej − p1, a trzeciej − p2. Natomiast cyfrom zapisywanym w prawo od przecinka przypisuje się kolejno następujące wagi: pierwszej − p-1, drugiej − p-2, trzeciej p-3 itd. (patrz przykład 1.1 i 1.2).

W systemach cyfrowych bardzo ważną rolę odgrywają zbiory znaków złożone z 2, 8, 10 i 16 elementów. Zbiory takie nazywamy odpowiednio:

zbiorem dwójkowym (binarnym) o podstawie p = 2,

zbiorem ósemkowym (oktalnym) o podstawie p = 8,

zbiorem dziesiątkowym o podstawie p = 10,

zbiorem szesnastkowym (heksadecymalnym) o podstawie p = 16.

Najważniejszą rolę w systemach cyfrowych odgrywa zbiór dwójkowy, ponieważ układy podstawowe, z których zbudowane są te systemy, mają naturę dwójkową.

W tablicy 1.1 przedstawiono cyfry używane w systemach o p = 2, 3, 8, 10 i l6. Zauważmy, że dla p > 10 należy wprowadzić dodatkowe znaki.

Tablica 1.1

Podstawa p |

System liczbowy |

Cyfry używane w systemie liczbowym |

2 |

Dwójkowy |

0, 1 |

3 |

Trójkowy |

0, 1, 2 |

8 |

Ósemkowy |

0, 1, 2, 3, 4, 5, 6, 7 |

10 |

Dziesiętny |

0, 1, 2, 3, 4, 5, 6, 7, 8, 9 |

16 |

Szesnastkowy |

0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F |

Tablica 1.2 Przykłady liczb wyrażonych w różnych systemach

System dziesiętny |

System dwójkowy |

System ósemkowy |

System szesnastkowy |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

2 |

10 |

2 |

2 |

3 |

11 |

3 |

3 |

4 |

100 |

4 |

4 |

5 |

101 |

5 |

5 |

6 |

110 |

6 |

6 |

7 |

111 |

7 |

7 |

8 |

1000 |

10 |

8 |

9 |

1001 |

11 |

9 |

10 |

1010 |

12 |

A |

11 |

1011 |

13 |

B |

12 |

1100 |

14 |

C |

13 |

1101 |

15 |

D |

14 |

1110 |

16 |

E |

15 |

1111 |

17 |

F |

16 |

10000 |

20 |

10 |

17 |

10001 |

21 |

11 |

18 |

10010 |

22 |

12 |

19 |

10011 |

23 |

13 |

20 |

10100 |

24 |

14 |

100 |

1100100 |

144 |

64 |

1000 |

1111101000 |

1750 |

3E8 |

Dziesiętny system liczbowy

Do zapisania dowolnej liczby w powszechnie stosowanym dziesiętnym systemie liczbowym wykorzystuje się dziesięć (wszystkie) cyfr arabskich. W dziesiętnym systemie liczbowym podstawa systemu p = 10. Kilka wybranych liczb dziesiętnych przedstawiono w pierwszej kolumnie tablicy 1.2.

Przykład 1.1:

Liczbę 15, zapisana w systemie dziesiętnym można zapisać:

15 = (1 x 101)+(5 x 100)

Liczba ta składa się z elementów o wadze 100 = 1 i jednego elementu o wadze 101 = 10

Przykład 1.2:

Zapis:

574, 2810

jest skróconym zapisem wyrażenia :

(5 x 102)+(7 x 101)+(4 x 100)+(2 x 10-1)+(8 x 10-2)

W tym przykładzie 5 jest na pozycji setek (102), 7 na pozycji dziesiątek (101), 4 na pozycji jedności (100), 2 na pozycji dziesiętnych (10-1) i 8 na pozycji setnych (10-2).

Dwójkowy system liczbowy

Najprostszym systemem liczbowym wykorzystującym zapis pozycyjny jest system dwójkowy. Elementami zbioru znaków systemu dwójkowego jest para cyfr: 0 i 1. Znak dwójkowy (ang. Binary Digit) często jest nazywany w skrócie bit. W dwójkowym systemie liczbowym podstawa systemu p = 2. Kilka wybranych liczb dwójkowych przedstawiono w drugiej kolumnie tablicy 1.2.

Przykład 1.3:

Zapis:

11012

oznacza liczbę powstałą z sumowania

(1 x 23)+(1 x 22)+(0 x 21)+(1 x 20) = 1310

Przykład 1.4:

Zapis:

1001, 1 1012

jest zapisem skróconym wyrażenia:

(1 x 23)+(0 x 22)+(0 x 21)+(1 x 20)+(1 x 2-1)+(1 x 2-2)+(0 x 2-3)+(1 x 2-4) = 9,812510

Przykład ten może posłużyć również jako ilustracja konwersji liczby dwójkowej na równoważną jej liczbę dziesiętną.

Konwersji dziesiętno - dwójkowej można dokonać na drodze wielokrotnego dzielenia na 2 całkowitej części oraz mnożenia przez 2 ułamkowej części przetwarzanej liczby dziesiętnej.

Przykład 1.5:

Niech N10 = 9,8125

9 : 2 = 4 reszta 1 (LSB)

4 : 2 = 2 0

2 : 2 = 1 0

1 : 2 = 0 1 (MSB)

0,8125 x 2 = 1,6250 = 0,6250 nadmiar 1 (MSB)

0,6250 x 2 = 1,2500 = 0,2500 1

0,2500 x 2 = 0,5000 = 0,5000 0

0,5000 x 2 = 1,0000 = 0,0000 1 (LSB)

Ostatecznie otrzymujemy:

9,812510 = 1001,11012

Szesnastkowy system liczbowy

Szesnastkowy system liczbowy jest to taki system pozycyjny, którego podstawa p = 24. Do przedstawienia liczb w tym systemie potrzebnych jest 16 znaków. Dziesięć znaków stanowią cyfry arabskie, a pozostałe 6 znaków pierwsze litery alfabetu: A reprezentuje 10, B reprezentuje 11, ..., F reprezentuje l5. Kilka wybranych liczb szesnastkowych przedstawiono w czwartej kolumnie tablicy 1.2.

Przykład 1.6:

Niech liczba wyrażona w systemie szesnastkowym ma postać:

F3A, C816

Równoważną jej liczbą dziesiętną jest liczba o postaci:.

(15 x 162) + (3 x 161) + (10 x 160) + (12 x 16-1) + (8 x 16-2) = 3898,7812510

Przykład 1.7:

Liczba zapisana w systemie heksadecymalnym ma postać: 3F16. Liczba ta oznacza liczbę powstałą przez sumowanie:

(3 x 161) + (15 x 160) = 63.

Konwersji dziesiętno - szesnastkowej można dokonać na drodze wielokrotnego dzielenia na 16 części całkowitej oraz mnożenia przez 16 części ułamkowej przetwarzanej liczby dziesiętnej.

Przykład 1.8:

Niech N10 = 2527,7812510

252710 = 9DF16

0,7812510 = C816

Wynik konwersji: 2527,7812510 = 9DF, C816

Tablica 1.3 Tablica potęg liczby 2

2n |

n |

2-n |

1 |

0 |

1.0 |

2 |

1 |

0.5 |

4 |

2 |

0.25 |

8 |

3 |

0.125 |

16 |

4 |

0.062 5 |

32 |

5 |

0.031 25 |

64 |

6 |

0.015 625 |

128 |

7 |

0.007 812 5 |

256 |

8 |

0.003 906 25 |

512 |

9 |

0.001 953125 |

1 024 |

10 |

0.000 976 562 5 |

2 048 |

11 |

0.000 488 281 25 |

4 096 |

12 |

0.000 244 140 625 |

8 192 |

13 |

0.000 122 070 312 5 |

16 384 |

14 |

0.000 061 035 156 25 |

32 768 |

15 |

0.000 030 517 578 125 |

65 536 |

16 |

0.000 015 258 789 062 5 |

131 072 |

17 |

0.000 007 629 394 531 25 |

262 144 |

18 |

0.000 003 814 697 265 625 |

524 288 |

19 |

0.000 001 907 348 632 812 5 |

1 048 576 |

20 |

0.000 000 953 674 316 406 25 |

2 097 152 |

21 |

0.000 000 476 837 158 203 125 |

4 194 304 |

22 |

0.000 000 238 418 579 101 562 5 |

8 388 608 |

23 |

0.000 000 019 209 289 550 781 25 |

16 777 216 |

24 |

0.000 000 059 604 644 775 390 625 |

33 554 432 |

25 |

0.000 000 029 802 322 387 695 312 5 |

67 108 864 |

26 |

0.000 000 014 901 161 193 847 656 25 |

134 217 728 |

27 |

0.000 000 007 450 580 596 923 828 125 |

268 435 456 |

28 |

0.000 000 003 725 290 298 461 914 062 5 |

536 870 912 |

29 |

0.000 000 001 862 645 149 230 957 031 25 |

1 073 741 824 |

30 |

0.000 000 000 931 322 574 615 478 515 625 |

2 147 483 648 |

31 |

0.000 000 000 465 661 287 307 739 257 812 5 |

4 294 967 296 |

32 |

0.000 000 000 232 830 643 653 869 628 906 25 |

8 589 934 592 |

33 |

0.000 000 000 116 415 321 826 934 814 453 125 |

17 179 869 184 |

34 |

0.000 000 000 058 207 660 913 467 407 226 562 5 |

34 359 738 368 |

35 |

0.000 000 000 029 103 830 456 733 703 613 281 25 |

68 719 476 736 |

36 |

0.000 000 000 014 551 915 228 366 851 806 640 625 |

Liczba przedstawiona w systemie dwójkowym może być bezpośrednio przetworzona na liczbę przedstawioną w systemie szesnastkowym. W tym celu należy liczbę dwójkową podzielić na grupy czterobitowe (tetrady) poczynając od przecinka w lewo i w prawo i zastąpić otrzymane tetrady ekwiwalentnymi cyframi szesnastkowymi.

Przykład 1.9

Niech N2 = 11010101000,1111010111

0110 1010 1000, 1111 0101 1100

6 A 8, F 5 C

zatem 1101010100,11110101112 = 6A8,F5CH

Kody

Kodem nazywamy reguły uporządkowujące poszczególne kombinacje zmiennych. Parametry określające kod to:

długość m - jest to liczba bitów informacji albo liczba zmiennych,

pojemność P - jest to liczba kombinacji wartości zmiennych występujących w kodzie.

W celu zautomatyzowania procesów przetwarzania i transmisji informacji dyskretnej, zamiast znaków graficznych, którymi posługujemy się na co dzień, są wykorzystywane specjalne kody zbudowane z bardzo prostych symboli w systemach cyfrowych. Za pomocą kodów najczęściej opisuje się liczby. W układach cyfrowych najczęściej stosuje się dwójkowy system kodowy, zwany kodem binarnym, i jego szczególny przypadek system dwójkowo - dziesiętny.

Kody zbudowane z symboli dwuwartościowych noszą nazwę kodów dwójkowych. Symbole dwuwartościowe (lub dwójkowe), które przyjmują wartości cyfrowe 0 lub 1, nazywają się bitami. Znaki przedstawia się w postaci ciągów symboli dwójkowych, a ciągi te nazywane są słowami kodowymi. Inaczej mówiąc, m (czyt. liczba) bitów, które odpowiadają wartościom M zmiennych tworzy tzw. słowo dwójkowe (kodowe). Jedno słowo dwójkowe składające się z m bitów informacji może reprezentować 2m różnych elementów informacji, np. kod dwójkowy złożony z siedmiu bitów umożliwia zakodowanie 27 = 128 znaków. Kodowanie za pomocą kodu dwójkowego oznacza zapisanie liczb w systemie dwójkowym.

Najlepiej jest, gdy wszystkie znaki są przedstawione za pomocą słów kodowych o jednakowej długości. Z uwagi na szybkość i wydajność procesów przetwarzania informacji, należy posługiwać się słowami o jak najmniejszej długości.

Kodowanie informacji pozwala na zmniejszenie liczby torów transmisji potrzebnych do przesłania tej informacji. Natomiast dekodowanie pozwala nam przywrócić do pierwotnego systemu.

Kody możemy podzielić na:

W zależności od parametru P kody zupełne i niezupełne:

kody zupełne, które zawierają wszystkie możliwe kombinacje wartości zmiennych,

kody niezupełne, które nie wykorzystują wszystkich kombinacji.

Kody systematyczne i niesystematyczne:

kody systematyczne tworzy się na podstawie reguły formalnej, w której każda kombinacja wartości zmiennych jest zdefiniowana w sposób jednoznaczny, do kodów systematycznych zaliczamy m.in. wszystkie kody wagowe,

kody niesystematyczne wymagają podania tabeli, która określa kolejność poszczególnych kombinacji występujących w dowolnym porządku, do kodów niesystematycznych zaliczamy kod Watha, dalekopisowy i inne.

Kody dwójkowe wagowe i niewagowe.

Jeśli każdy bit (pozycja) kodu dwójkowego ma określoną i niezmienną wagę (znaczenie) liczbową to taki kod nazywamy kodem wagowym; pozostałe kody są kodami niewagowymi. Wagi są przeważnie liczbami całkowitymi i mogą przyjmować wartości ujemne. Wartości liczbowe słowa kodowego będą sumą wag tych pozycji, które zawierają jedynki. Najprostszym wagowym kodem dwójkowym jest tzw. naturalny kod dwójkowy (kod binarny, kod BIN) (tablica 1.4).

Wagi naturalnego kodu dwójkowego n - bitowego (n - pozycyjnego) wynoszą 2i, (gdzie i = 0, 1, 2, ..., 2n-1), tzn. są kolejnymi potęgami liczby 2.

Powszechnie stosowanym kodem dwójkowym niewagowym jest kod Graya, w którym sąsiednie słowa różnią się wartością tylko jednego bitu.

Tablica 1.4 Kody 4 - bitowe: naturalny i Graya

Kod Dwójkowy |

Kod Graya |

||

|

A B C D 8 4 2 1 |

|

X Y W Z Niewagowy |

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

0 0 0 0 0 0 0 1 0 0 1 1 0 0 1 0 0 1 1 0 0 1 1 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 1 1 1 1 1 1 1 1 0 1 0 1 0 1 0 1 1 1 0 0 1 1 0 0 0 |

Kody dwójkowo - dziesiętne.

Ważną odmianę kodów dwójkowych stanowią kody dwójkowo - dziesiętne BCD (ang. Binary Coded Decimal). W kodach tych poszczególne cyfry dziesiętne są przedstawione w kodzie dwójkowym, każdej cyfrze kodu dziesiętnego są przyporządkowane cztery bity kodu binarnego. Do zakodowania dziesięciu cyfr potrzebne są co najmniej cztery bity, bo: 23 < 10 < 24. Sześć spośród szesnastu kombinacji kodu 4 - bitowego nie będzie wykorzystanych.

Kody BCD mogą być wagowe i niewagowe (przedstawione w tablicy 1.5 i 1.6). W kodach wagowych każda pozycja ma określoną wagę. Ciąg wag kodu jest zwykle używana jako nazwa kodu.

Podstawowym wagowym kodem BCD jest kod 8421 BCD lub po prostu kod BCG (tablica 1.5), w którym wykorzystuje się pierwsze dziesięć tetrad 4 - bitowego naturalnego kodu dwójkowego.

Przykładem kodu niewagowego BCD jest kod z nadmiarem 3 (tablica 1.6). Kod ten otrzymuje się dodając trzy do cyfry dziesiętnej i zapisując ją następnie w kodzie 8421. W kodzie nie ma możliwości przypisania wagi każdej pozycji.

Tablica 1.5 Kody dwójkowo - dziesiętne wagowe

Kod: |

Naturalny |

|

Aikena |

|

|

Cyfra |

8 4 2 1 |

2* 4 2 1 |

2 4 2 1 |

7 4 2 1 |

8 4-2-1 |

0 1 2 3 4 5 6 7 8 9 |

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 |

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 1 1 0 1 1 1 1 |

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 1 0 0 0 1 0 0 1 1 0 1 0 |

0 0 0 0 0 1 1 1 0 1 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 |

Tablica 1.6 Kody dwójkowo - dziesiętne niewagowe

Cyfra |

Z nadmiarem 3 ( + 3, plus 3, excess 3. XS3) |

Graya z nadmiarem 3 |

Wattsa |

Johnsona pseudopierście niowy |

Wskaźników cyfrowych siedmiosegmentowych |

0 1 2 3 4 5 6 7 8 9 |

0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 |

0 0 1 0 0 1 1 0 0 1 1 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 1 1 1 1 1 1 1 1 0 1 0 1 0 |

0 0 0 0 0 0 0 1 0 0 1 1 0 0 1 0 0 1 1 0 1 1 1 0 1 0 1 0 1 0 1 1 1 0 0 1 1 0 0 0 |

0 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 0 0 1 1 0 0 0 1 0 0 0 0 |

0 1 1 1 1 1 1 0 0 0 0 1 1 0 1 0 1 1 0 1 1 1 0 0 1 1 1 1 1 1 0 0 1 1 0 1 1 0 1 1 0 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 0 0 1 1 1 |

PODSTAWOWE FUNKCJE LOGICZNE I FUNKTORY UKŁADÓW LOGICZNYCH

Wstęp

Istotą techniki cyfrowej jest wytwarzanie cyfrowych sygnałów wyjściowych jako odpowiedzi na cyfrowe sygnały wejściowe. Na przykład sumator przetwarza doprowadzone do wejść dwie liczby 16 - bitowe na sumę 16 - bitową tych liczb oraz bit przeniesienia. Można także zbudować układ do mnożenia dwóch liczb. Są to operacje w rodzaju tych, jakie powinna wykonywać jednostka arytmetyczna komputera. Innym zadaniem może być porównanie dwóch liczb w celu sprawdzenia, która z nich jest większa.

Typowymi zadaniami układów cyfrowych jest pobranie pewnych liczb binarnych, ich wyświetlenie, wydrukowanie lub wydziurkowanie jako znaków dziesiętnych. We wszystkich tych zadaniach sygnały (stany) wyjściowe są zdeterminowanymi funkcjami sygnałów (stanów) wejściowych. Wszystkie zadania mogą być wykonane za pomocą urządzeń zwanych bramkami, które realizują działania algebry Boole'a w dziedzinie układów dwustanowych (binarnych) i sieci złożonych z takich elementów, którymi są bramki. Każda ze zmiennych boolowskich może być równa tylko zeru lub równa tylko jedynce. To założenie można zapisać w postaci:

X = 0, jeśli X ≠ 1

X ≠ 1, jeśli X = 0

Funkcję, której zmienne lub ona sama przyjmuje wartości ze zbioru {0, 1} nazywamy funkcją boolowską (logiczną, przełączającą). Natomiast układ przetwarzający logiczne sygnały wejściowe na logiczne sygnały wyjściowe nazywa się układem logicznym.

Przy projektowaniu dwustanowych (0 - stan niski, 1 - stan wysoki) układów cyfrowych posługujemy się algebrą Boole'a.

Algebra Boole'a, którą stosujemy w układach, opiera się na trzech zasadniczych funkcjach, którymi są:

Iloczyn logiczny I (ang. AND), Y = A · B

Suma logiczna LUB (ang. OR), Y = A + B

Negacja (inwersja) NIE (ang. NOT),

Stosowane są również operatory złożone (pochodne), jak:

Suma zanegowana:

NORIloczyn zanegowany:

NANDRównoważność:

EX-NORNierównoważność, zwana sumą modulo 2:

EOR, XOR

Jedną z postaci algebry Boole'a jest znany rachunek zdań, gdzie zamiast znaków sumy + stosuje się łącznik lub, zamiast znaku iloczynu - łącznik i, a do negacji używamy słowa nie. Algebra Boole'a posługuje się szeregiem praw i tożsamości.

W algebrze Boole'a obowiązują następujące podstawowe prawa:

Prawo przemienności mnożenia i dodawania:

Prawo łączności:

Prawo rozdzielczości:

Prawa podstawowe:

Prawa de Morgana:

Podstawowe tożsamości algebry Boole'a:

jeżeli co najmniej jeden z argumentów jest równy 1, to wynik jest równy 1. Zatem suma logiczna jest równa 0 tylko dla przypadku, gdy wszystkie argumenty są równe 0.

wynik iloczynu jest równy 1, wtedy i tylko wtedy, gdy wszystkie argumenty przyjmują wartość 1.

dowolna n - argumentowa funkcja logiczna jest określona dla 2n różnych kombinacji argumentów,

liczba różnych n - argumentowych funkcji logicznych jest skończona i równa 2n.

I (AND),

LUB (OR),

I - NIE (NAND),

LUB - NIE (NOR),

ALBO (Ex - OR),

NIE (NOT) oraz wzmacniacz logiczny (IDENTITY), które są omówione w podrozdziale 2.4.

Podstawowe funkcje logiczne

Sposoby przedstawiania funkcji logicznych

Funktory układów logicznych

b)

Układy TTL

TTL (ang. Transistor - Transistor Logic - logika tranzystorowo - tranzystorowa) - technologia bipolarna,

CMOS (ang. Complementary Metal - Oxide - Semiconductor) - technologia unipolarna.

duża szybkość przełączania,

mały pobór mocy,

duża odporność na zakłócenia,

duża obciążalność,

duży współczynnik powielania logicznego,

małe impedancje wyjściowe w stanie 0 i 1,

pojedyncze źródło napięcia zasilania,

praca w szerokim zakresie temperatur,

duża pewność działania,

duży asortyment, który obejmuje ponad 500 różnych układów logicznych od pojedynczych bramek po wielkie pamięci i mikroprocesory.

UKŁADY KOMBINACYJNE I SEKWENCYJNE

Wstęp

układy kombinacyjne,

układy sekwencyjne.

określić funkcję logiczną rozpatrywanego problemu, np. za pomocą tablicy wartości,

dokonać minimalizacji funkcji logicznej wykorzystując tablice Karnaugha, przedstawione w poniższym rozdziale, lub metody algebraiczne,

sporządzić schemat układu logicznego, realizującego zminimalizowaną funkcję logiczną.

Metoda analityczna algebry Boole'a.

Metoda z użyciem tablicy Karnaugha (czyt. karnafa).

układy synchroniczne

układy asynchroniczne.

Metoda Karnaugha

b)

Każdą liczbę, dla której funkcja wyjściowa przyjmuje wartość 1 przedstawiamy za pomocą kodu dwójkowego (rys. 3.6a).

Każdą liczbę możemy zapisać za pomocą czterech bitów (czterech sygnałów wejściowych). Zatem potrzebna jest czterowejściowa tablica Karnaugha.

W poszczególne pola tej tablicy należy wpisać wartości funkcji Y dla poszczególnych kombinacji sygnałów wejściowych. W tym miejscu zwykle wyłania się problem. Jak w stosunkowo krótkim czasie znaleźć pola odpowiadające danej kombinacji wejściowej (problem ten ma większe znaczenie, gdy tworzymy tablice o większej liczbie sygnałów wyjściowych). Kombinacje sygnałów wejściowych dzielimy przerywaną linią w taki sposób, aby przebiegała ona między sygnałami opisującymi kolumny a sygnałami opisującymi wiersze tablicy Karnaugha (rys. 3.6a). W naszym przykładzie bity A, B opisują wiersze, a bity C,. D - kolumny. Zatem każde pole jest opisane kolumną i wierszem.

W tablicy Karnaugha odszukujemy wiersz opisany kombinacją AB (sygnałów wejściowych).

Po odnalezieniu odpowiedniego wiersza. poruszamy się wzdłuż niego, szukając kolumny opisanej kombinacja CD.

W pole tablicy leżące na przecięciu odszukanego wiersza i kolumny wpisujemy wartość 1. (Strzałkami zaznaczono pola, które odpowiadają poszczególnym kombinacjom).

Jeżeli funkcja określała pola, którym odpowiadają poziomy 1, to w pozostałe wolne pola należy wpisać 0.

są one położone obok siebie, tzn. w sąsiednich polach,

jedynka ma odbicie lustrzane wzdłuż osi L - L' lub M - M'.

jedna para jedynek jest odbiciem lustrzanym drugiej pary wzdłuż osi L - L' lub M - M',

obie pary stykają się bokiem w obrębie jednego z kwadratów T lub T'. W analogiczny sposób skleja się czwórki w ósemki, a ósemki w szesnastki.

wyszukujemy grupy o największej liczbie konstytuent, zawierające te same wartości (jedynki lub zera),

liczba konstytuent musi być liczbą parzystą siatek 2n,

poszczególne konstytuent muszą być cyklicznie sąsiednie (tzn. pierwsza musi być sąsiednia z drugą, druga z trzecią , ..., a ostatnia z pierwszą.

Wypełnić siatkę Karnaugha dla funkcji, której schemat logiczny pokazano na rys. 3.11.

Zrealizować funkcję na bramkach NOR.

metodę Quine'a,

metodę Quine'a - Mc Cluskeya,

metodę Patricka,

metodę Blake'a i inne.

PRZERZUTNIKI

Wstęp

wejścia asynchroniczne - oznaczone małymi literami,

wejścia synchroniczne - oznaczone dużymi literami.

Dwa wejścia informacyjne asynchroniczne s i r.

Dwa wejścia informacyjne synchroniczne A i B (programujące).

Wejście zegarowe C.

Dwa wyjścia komplementarne Q i

(proste i zanegowane).przerzutniki wyzwalane poziomem,

przerzutniki wyzwalane zboczem,

przerzutniki dwuzboczowe (dwustopniowe).

czasy propagacji sygnałów od wejścia synchronizującego do wyjść Q i

,czasy propagacji sygnałów od wejść asynchronicznych do wyjść Q i

,czas ustalenia ts (t setup),

czas przetrzymywania th (t thold),

minimalny czas trwania określonych sygnałów,

maksymalna częstotliwość przebiegu synchronizującego.

Przerzutniki asynchroniczne

dominujące wejście wpisujące,

dominujące wejście zerujące,

aktywny poziom (sygnał) wysoki H, (ustawienie wartości Q = 1 odbywa się sygnałem s = 1, jeśli s = 0 wtedy nie zmienia się stan układu),

aktywny poziom (sygnał) niski L, (ustawienie wartości Q = 1 odbywa się sygnałem s = 0, jeśli s = 1 wtedy nie zmienia się stan układu),

aktywny sygnał wysoki i dominujący sygnał wpisujący,

aktywny sygnał niski i dominujący sygnał wpisujący,

aktywny sygnał wysoki i dominujący sygnał zerujący,

aktywny sygnał niski i dominujący sygnał zerujący.

Przerzutniki synchroniczne

Wstęp

na wejścia informacyjne synchroniczne podaje się odpowiednie stany, stosownie do tablicy stanów przerzutnika,

impuls zegarowy umożliwia oddziaływanie tych stanów na stan przerzutnika,

stany na wyjściach przerzutnika można ustalić przez chwilową lub dowolnie długo trwającą zmianę stanu wejść informacyjnych asynchronicznych niezależnie od impulsu zegarowego i stanu na wejściach informacyjnych synchronicznych; wejścia asynchroniczne zawsze mają priorytet w stosunku do innych wejść przerzutnika.

0 - zerowanie przerzutnika,

1 - ustawianie przerzutnika,

Qn - niezmieniony stan wyjścia,

- zmieniony stan wyjścia, (na przeciwny),X - niedozwolony stan na wejściu, tzn. że nie jest określony stan jaki pojawi się na wyjściach Q i

. Na obu wyjściach mogą się pojawić zera lub jedynki.Przerzutnik synchroniczny D

Przerzutnik synchroniczny T

Przerzutnik synchroniczny RS

nie zmienić stanu na wyjściach Q i

, jeśli R = S = 0,przyjąć na wyjściu Q stan 0 i na wyjściu

stan 1 (stan na wyjściu Qn = 0), jeśli R = 1 i S = 0,przyjąć na wyjściu Q stan 1 i na wyjściu

stan 0 (stan na wyjściu Qn = 1), jeśli R = 0 i S = 1.Przerzutnik synchroniczny JK

schemat logiczny: M - część Master, S - część Slave,

fazy przełączania przerzutnika

przebiegi czasowe.

przerwanie połączenia między częścią Master i częścią Slave (odseparowanie wejść przerzutnika Slave od wyjść Master), zablokowanie bramek 3 i 4;

zmiana stanu przerzutnika Master stosownie do stanu wejść informacyjnych, otwarcie wejść bramek (1 i 2) dla sygnałów J i K oraz zapamiętanie pobudzeń w części Master;

zablokowanie wejść części Master (zablokowanie bramek 1 i 2);

przepisanie wartości zmiennych wyjściowych przerzutnika Master do przerzutnika Slave, tzn. na wyjście układu.

REJESTRY

Wstęp

równoległe - umożliwiające równoległe wprowadzanie i wyprowadzanie informacji (całymi słowami) jednocześnie do wszystkich i ze wszystkich pozycji,

szeregowe - umożliwiające szeregowe wprowadzanie i wyprowadzanie informacji, tzn. bit po bicie , w takt sygnału zegarowego,

szeregowo - równoległe - umożliwiające szeregowe wprowadzanie i równoległe wyprowadzanie informacji,

równoległo - szeregowe - umożliwiające równoległe wprowadzanie i szeregowe wyprowadzanie informacji.

długość rejestru równa liczbie n zawartych w nim przerzutników,

szybkość pracy rejestru równa czasowi trwania lub wyprowadzania informacji dla rejestru równoległego, a dla rejestru szeregowego jest to maksymalna częstotliwość impulsów taktujących.

szeregowo - szeregowy,

szeregowo - równoległy,

równoległo - szeregowy,

równoległo - równoległy,

pierścieniowy.

rejestry asynchroniczne - zbudowane z przerzutników asynchronicznych,

rejestry synchroniczne - zbudowane z przerzutników synchronicznych.

Rejestry równoległe

rejestry o „wpisywaniu jednoprzewodowym”,

rejestry o „wpisywaniu dwuprzewodowym”.

5.3 Rejestry szeregowe

PAMIĘCI

6.1 Wstęp

czas dostępu (ang. access time),

czas cyklu (ang. cycle time),

szybkość transmisji (ang. transfer speed).

wejścia adresowe (A0,...,An);

wejścia / wyjścia danych (D0,...,Dn);

wejścia sterujące (WE, CS, OE), służące do wyboru funkcji wykonywanej przez układ,

niekiedy wejścia strobujące adresów (ALE, RAS, OE).

pamięci o dostępie swobodnym, typu zapis / odczyt

pamięci stałe , tylko do odczyt

6.2 Pamięci o dostępie swobodnym RAM

statyczne SRAM - komórką pamiętającą jest przerzutnik bistabilny (najczęściej asynchroniczny typu RS) w technologii MOS lub technologii bipolarnej. Zapisana informacja utrzymuje się w nich dopóki nie zostanie zastąpiona inną albo nie zaniknie napięcie zasilające.

dynamiczne DRAM - funkcje elementów pamiętających pełnią pojemności wejściowe tranzystorów MOS gromadzące ładunek lub odprowadzające go. Zawartość tych elementów musi być odświeżana, musi być uzupełniany ubytek ładunku.

Pamięci stałe ROM

Pamięć programowana maską MROM - bitową strukturę jej wnętrza ustala się w czasie produkcji (macierz tranzystorów MOS).

Programowalna pamięć stała PROM - programowana przez użytkownika przez przepalanie cienkich połączeń po odpowiednim ich zaadresowaniu i po odprowadzeniu właściwych sygnałów sterujących. Pamięci PROM są dość szybkie (25 ÷ 50 ns), które pobierają dużo mocy (bipolarne 0,5 ÷ 1 W), o małych i średnich pojemnościach (od 32x8 do 8Kx8). Są to pamięci bipolarne i są wykonywane w technice MOS.

Reprogramowalna pamięć stała EPROM- bity informacji są zapisywane jako ładunki elektryczne na pływających bramkach tranzystorów MOS. Kasowanie tych ładunków z bramek następuje przez naświetlenie matrycy pamięciowej promieniami UV - ultrafioletowymi o dużej intensywności przez kilkadziesiąt minut (gdy w obudowie tych pamięci znajdują się okienka kwarcowe przepuszczające ultrafiolet), lub promieniami X (gdy obudowa układu jest nieprzezroczysta). Pamięci EPROM są niezbyt szybkie (200 ns), pobierają niewiele mocy i mają duże pojemności (od 8Kx8 do 12Kx8). Pamięci tego typu produkuje się techniką NMOS i CMOS.

Elektrycznie kasowalne PROM - EEPROM - zachowuje się jak pamięć EPROM, ale jest programowana i kasowana elektrycznie, napięciem +5 V, bez wyjmowania z układu aplikacyjnego. Polega to na podaniu impulsów prądowych o określonych parametrach (wartość, kształt, czas trwania), które powodują przepalenie połączeń matrycy pamięciowej. Czas programowania pamięci EEPROM jest długi i wynosi ok. 100 μs.

Zastosowania pamięci ROM (PROM)

konwersji kodów, '

realizacji funkcji logicznych,

realizacji funkcji arytmetycznych,

realizacji generatorów funkcji,

tablicowania funkcji,

mikroprogramowania.

pamięci stałej,

układu zmiany adresu (adres zmieniany jest w zależności od postaci ostatniej instrukcji oraz od stanu warunków wymuszających skoki warunkowe i bezwarunkowe),

rejestru mikroinstrukcji.

wygenerowanie słowa wyjściowego z pamięci z dokonaniem ewentualnej modyfikacji adresu słowa pamięci,

przekazanie do układów wykonawczych danych określających następną mikrooperację sterującą.

LICZNIKI CYFROWE

Wiadomości ogólne

Liczniki o stałej długości cyklu,

Liczniki o nastawionej długości cyklu.

Liczniki modulo s (dzielnik liczby lub częstotliwości impulsów przez s),

Liczniki do s.

Liczniki jednokierunkowe:

zliczające w przód, jeśli liczby reprezentujące zawartość informacyjną licznika wzrastają w trakcie liczenia kolejnych impulsów,

zliczające wstecz, jeśli liczby reprezentujące zawartość informacyjną licznika maleją w trakcie liczenia kolejnych impulsów,

Liczniki dwukierunkowe

Liczniki asynchroniczne (szeregowe),

Liczniki synchroniczne (równoległe).

Liczniki asynchroniczne

Ustalić liczbę przerzutników niezbędnych do realizacji licznika (w zależności od pojemności licznika 2n).

Na wejścia informacyjne T lub JK (zwarte) - podać „1”.

Jeżeli licznik liczy w przód - połączyć wejścia zegarowe następnego przerzutnika z wyjściem „Q” poprzedniego.

R9(1) i R9(2) - ustawia (w dwójkową reprezentację liczby 9),

R0(1) i i - zerowania.

Zaprojektować licznik liczący od 3 do 14 w przód (zerowanie przy impulsie 15).

Zaprojektować licznik liczący od 7 do 3 w przód (zerowanie przy impulsie 4).

Zaprojektować licznik liczący od 9 do 4 w tył (zerowanie przy impulsie 3).

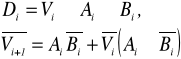

Liczniki synchroniczne

Ustalić liczbę przerzutników w zależności od pojemności licznika.

Ustalić i wykonać tabele stanów licznika (uwzględniając tabele wzbudzeń przerzutników, na których realizujemy licznik). Polega to na rozpisaniu kolejności następujących po sobie stanów i odpowiadającym im stanów przerzutnika, czyli wypełnienie tablicy stanów, a następnie na podstawie tablicy wzbudzeń przerzutnika wypełnia się tablicę Karnaugha, osobno dla poszczególnych wejść informacyjnych każdego przerzutnika.

Zaprojektować układ kombinacyjny ograniczający zliczanie.

tablica wzbudzeń przerzutnika JK,

tablica stanów.

UKŁADY ARYTMETYCZNE

Wstęp

dwójkowe, gdzie działania dokonuje się na liczbach dwójkowych,

dziesiętne, wykonujące działania na liczbach dziesiętnych kodowanych dwójkowo.

równoległe:

z przeniesieniem szeregowym,

z przeniesieniem równoległym,

szeregowe.

komparatory równoległe,

komparatory szeregowe.

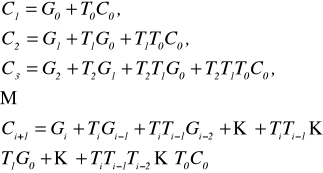

Sumatory

suma

przeniesienie

suma

przeniesienie

Sumatory równoległe

sumatory z przeniesieniem szeregowym, zwane również sumatorami kaskadowymi albo iteracyjnymi,

sumatory z przeniesieniem równoległym.

Sumatory szeregowe

jego prostota,

mała liczba elementów logicznych potrzebnych do jego realizacji.

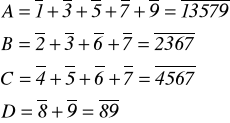

Komparatory

Komparatory jednobitowych liczb dwójkowych

Komparatory równoległe

jeśli bit liczby A z pozycji n - 1 jest równy 1 (albo 0), a bit liczby B z tej pozycji jest równy 0 (albo 1), to A > B (albo A < B) i określenie nierówności jest dokonane,

jeśli bity z pozycji n - 1 liczb A i B są tożsame (równe), to porównujemy, tak jak poprzednie, bity z pozycji n - 2.

Komparatory szeregowe

UKŁADY KOMUTACYJNE

Wstęp

konwertery kodów (w tym kodery i dekodery),

demultipleksery,

multipleksery.

Enkodery

Dekodery

pełny, jeśli dla rozpatrywanego dekodera zachodzi równość 2n = m,

niepełny, jeśli dla rozpatrywanego dekodera zachodzi nierówność 2n > m, gdzie nie wszystkie słowa kodowe są wykorzystane.

Transkodery

zbudowanych z enkodera i dekodera,

zbudowanych w postaci kombinacyjnego układu wielowyjściowego.

Przykłady syntezy i rozwiązań transkoderów

tablica rozpatrywanych kodów,

tablice Karnaugha,

schemat logiczny.

oznakowanie segmentów wskaźnika,

przedstawienie cyfr i znaków dodatkowych,

tablica prawdy,

tablice Karnaugha dla funkcji a,

schemat logiczny transkodera scalonego 49.

Multipleksery i demultipleksery

Wstęp

Multipleksery

8 wejść informacyjnych,

3 wejścia adresowych,

wejście strobujące S (próbkujące)

wyjście komplementarne (pozycyjne lub negacyjne).

schemat logiczny, b) tablica ilustrująca działanie.

połączyć odpowiadające sobie wejścia adresowe;

wejście strobujące S multipleksera, mającego odpowiadać za wejścia adresowe o niższych numerach, przyłączyć do dodatkowego wejścia E;

wejście strobujące S multipleksera, mającego odpowiadać za wejścia adresowe wyższych numerach, przyłączyć do dodatkowego wejścia E przez negator;

wyjścia połączyć przez bramkę AND, jeżeli dane są zanegowane, lub przez bramkę NAND, jeżeli dane są nienegowane.

Demultipleksery

GENERATORY

Przerzutniki monostabilne

wejścia wyzwalające A1, A2 oraz B,

wejścia służące do dołączenia zewnętrznych elementów (R, C) ustalających czas trwania impulsów wyjściowych,

wyjścia przerzutnika Q i

.Generatory fali prostokątnej

Generowanie pojedynczego impulsu

Opóźnienie sygnału o zadany czas

Generowanie ciągu impulsów

BIBLIOGRAFIA:

Chwaleba Augustyn, Moeschke Bogdan, Płoszajski Grzegorz: Elektronika, Wydawnictwo Szkolne i Pedagogiczne, Warszawa 1996.

Piecha Jan: Elementy cyfrowe TTL, Katowice 1985.

Piecha Jan: Elementy i układy cyfrowe, PWN, Warszawa 1990.

Pieńkoś Jan, Turczyński Janusz: Układy scalone TTL w systemach cyfrowych, Wydawnictwo Komunikacji i Łączności, Warszawa 1980.

Pióro Barbara, Pióro Marek: Podstawy elektroniki cz.1, cz.2, Wydawnictwo Szkolne i Pedagogiczne, Warszawa 1996.

Rusek Andrzej: Podstawy elektroniki, Wydawnictwo Szkolne i Pedagogiczne, Warszawa 1986.

Skorupski Andrzej: Podstawy budowy i działania komputerów, Wydawnictwo Komunikacji i Łączności, Warszawa 1997.

A

KOD 1 z n

Kod 1 z 10

Kod 1 z 10

Kod

Adres

Adres

We

Y

A

B

A

C

B

C

Wejścia

Wyjścia

A

W

W

B

X

Wejścia

Sterowanie

WE

a |

A+B = B+A |

b |

A · B = B · A |

a |

mnożenia A+B+C = A+(B+C) = (A+B)+C |

b |

dodawania A · B · C = A · (B · C) = (A · B) ·C |

a |

mnożenia względem dodawania A ·(B + C) = A · B + A ·C |

b |

dodawania względem mnożenia A + B · C = (A + B) · (A + C) |

a |

A + 1 = 1 |

b |

A · 1 = A |

a |

A + 0=A |

b |

A · 0 = 0 |

a |

A + A = A |

b |

A · A = A |

a |

|

b |

|

a |

|

b |

|

a |

A · B + A · C = A · (B + C) |

b |

(A + B) · (A + C) = A + B · C |

a |

A · B +B·C+ |

b |

(A + B) · (B + C) · ( |

a |

A · B + |

b |

(A + B) · ( |

Funkcje: sumy, iloczynu i negacji tworzą tzw. podstawowy system funkcjonalnie pełny. System funkcji logicznych nazywamy funkcjonalnie pełnym, jeśli za pomocą zasad superpozycji i podstawiania argumentów można uzyskać dowolną funkcję logiczną. Podstawowy system funkcjonalnie pełny nie jest minimalny, ponieważ sumę lub iloczyn można zrealizować za pomocą dwóch pozostałych operatorów, korzystając z praw de Morgana:

![]()

![]()

Operacja sumy logicznej jest zdefiniowana następująco:

Operacja iloczynu logicznego jest zdefiniowana następująco:

Operacja negacji jest operacją jednoargumentową i jest zdefiniowana jako zmiana wartości argumentu, tj. jeśli argument ma wartość 1, to operacja ta daje w wyniku wartość 0, a jeśli argument ma wartość 0, to operacja ta daje w wyniku wartość 1.

Łatwo można wykazać, że:

Dowolną funkcję logiczną można wyrazić przez funkcje logiczne dwóch zmiennych (tablica 2.1). Kilka funkcji przedstawionych w tablicy 2.1 jest szczególnie interesujących, ponieważ są one realizowane za pomocą układów w postaci bramek scalonych TTL.

Do funkcji takich należą funkcje:

Funkcja I (AND)

Do przedstawienia iloczynu logicznego X np. dwu zmiennych A i B są stosowane wyrażenia:

![]()

Najczęściej używane jest pierwsze i drugie wyrażenie. Funkcję I (AND) dwóch zmiennych boolowskich przedstawiono na rys. 2.1.

Funkcja iloczynu logicznego przyjmuje wartość 1 wtedy i tylko wtedy, gdy wszystkie zmienne, A i B przyjmują wartość 1. W każdym innym przypadku iloczyn logiczny tych sygnałów wynosi 0.

A |

B |

X = AB |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

Rys. 2.1 Tablica dwuargumentowej funkcji I (AND).

Rys. 2.2 Realizacja fizyczna dwuargumentowej funkcji I (AND)

Operację iloczynu logicznego X, realizują szeregowo połączone klucze A i B w obwodzie elektrycznym. Napięcie baterii będzie wykorzystane do rozświecenia żarówki, tzn. X = 1 tylko wtedy, jeśli zarówno klucz A, jak i klucz B będą zamknięte, tzn. A = 1 i B = 1 (patrz rys. 2.1).

Funkcja LUB (OR)

Do przedstawienia sumy logicznej Y np. dwu zmiennych A i B są stosowane wyrażenia:

![]()

Najczęściej używane jest pierwsze wyrażenie.

Jeżeli na wejścia układu podamy sygnał A i sygnał B, to na jego wyjściu otrzymamy sygnał będący ich sumą A + B. Przyjmuje ona poziom 1, gdy A lub B ma poziom 1. Funkcja sumy logicznej przyjmuje wartość 0 wtedy, gdy wszystkie zmienne przyjmują wartość 0.

Funkcję LUB (OR) dwóch zmiennych boolowskich przedstawiono na rys. 2.3, który ilustruje różnicę między sumą logiczną a sumą arytmetyczną. W ostatnim wierszu tablicy widzimy, że 1 + 1 = 1 dla sumy logicznej. Liczba zmiennych sumowanych logicznie może być dowolna.

A |

B |

Y=A+B |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

Rys. 2.3 Tablica dwuargumentowej funkcji LUB (OR).

Obwód elektryczny z równolegle połączonymi kluczami A i B, które realizują operację sumy logicznej Y, jest przedstawiony na rys. 2.4. Napięcie baterii rozświeci żarówkę, tzn. Y = l, wówczas, gdy klucz A lub klucz B, lub obydwa są zamknięte (patrz rys. 2.3).

Rys. 2.4 Realizacja fizyczna dwuargumentowej funkcji LUB (OR).

Funkcja NIE (NOT)

Do przedstawienia negacji N np. zmiennej A są stosowane wyrażenia:

![]()

Najczęściej używane jest pierwsze wyrażenie. Symbol A odczytuje się jako „nie A” lub „A zanegowane”, lub „dopełnienie A".

Funkcja NIE (NOT) polega na inwersji (negacji) zmiennej, zamienia stan wysoki (1) na stan niski (0) lub odwrotnie. Jeżeli na wejście podamy sygnał logiczny A, to na wyjściu otrzymamy jego negację ![]()

(„nie A”). Funkcję NIE (NOT) przedstawiono na rys. 2.5.

A |

N |

0 |

1 |

1 |

0 |

Rys. 2.5 Tablica funkcji NIE (NOT).

Tablica 2.1 Funkcje dwóch zmiennych

i |

Tablica wartości |

Tablica Karnaugha |

Zapis algebraiczny |

Nazwa funkcji w języku |

polskim |

||

|

X |

Y |

fi |

|

|

|

angielskim |

|

0 0 1 1 |

0 1 0 1 |

0 0 0 0 |

|

f0 = 0 |

stała 0 |

|

|

|

|

|

|

|

ZERO NULL FUNCTION |

|

|

0 0 1 1 |

0 1 0 1 |

0 0 0 1 |

|

f1 = X⋅Y |

I Koniunkcja |

|

|

|

|

|

|

|

AND CONJUNCTION |

|

|

0 0 1 1 |

0 1 0 1 |

0 0 1 0 |

|

f2 = X⋅ |

Zakaz przez Y |

|

|

|

|

|

|

|

INHIBIT |

|

|

0 0 1 1 |

0 1 0 1 |

0 0 1 1 |

|

f3 = X |

Zmienna X |

|

|

|

|

|

|

|

INDENTITY X |

|

|

0 0 1 1 |

0 1 0 1 |

0 1 0 0 |

|

f4 = |

Zakaz przez X |

|

|

|

|

|

|

|

INHIBIT |

|

|

0 0 1 1 |

0 1 0 1 |

0 1 0 1 |

|

f5 = Y |

Zmienna Y |

|

|

|

|

|

|

|

IDENTITY Y |

|

|

0 0 1 1 |

0 1 0 1 |

0 1 1 0 |

|

f6 =

|

ALBO Suma modulo 2 Wyłącznie LUB |

|

|

|

|

|

|

|

EXCLUSIVE - OR |

|

|

0 0 1 1 |

0 1 0 1 |

0 1 1 1 |

|

f7 = X +Y |

LUB Dysjunkcja Alternatywa |

|

|

|

|

|

|

|

OR DISJUNCTION |

|

Tablica 2.1 Funkcje dwóch zmiennych - ciąg dalszy

i |

Tablica wartości |

Tablica Karnaugha |

Zapis algebraiczny |

Nazwa funkcji w języku |

polskim |

||

|

X |

Y |

fi |

|

|

|

angielskim |

|

0 0 1 1 |

0 1 0 1 |

1 0 0 0 |

|

f8 = |

LUB - NIE Strzałka Peirce'a |

|

|

|

|

|

|

|

NOR PEIRCE FUNCTION |

|

|

0 0 1 1 |

0 1 0 1 |

1 0 0 1 |

|

f9 = |

ALBO - NIE Równoważność |

|

|

|

|

|

|

|

EXCLUSIVE - NOR EQUALITY COINCIDENCE |

|

|

0 0 1 1 |

0 1 0 1 |

1 0 1 0 |

|

f10 = |

Negacja Y |

|

|

|

|

|

|

|

NOT Y |

|

11 |

0 0 1 1 |

0 1 0 1 |

1 0 1 1 |

|

f11 = |

Implikacja X przez Y |

|

|

|

|

|

|

|

IMPLICATION |

|

|

0 0 1 1 |

0 1 0 1 |

1 1 0 0 |

|

f12 = |

Negacja X |

|

|

|

|

|

|

|

NOT X |

|

13 |

0 0 1 1 |

0 1 0 1 |

1 1 0 1 |

|

f13 = |

Implikacja Y przez X |

|

|

|

|

|

|

|

IMPLICATION |

|

|

0 0 1 1 |

0 1 0 1 |

1 1 1 0 |

|

f14 = |

I - NIE Kreska Sheffera |

|

|

|

|

|

|

|

NAND SHEFFER STROKE |

|

|

0 0 1 1 |

0 1 0 1 |

1 1 1 1 |

|

f15 = 1 |

Stała1 |

|

|

|

|

|

|

|

ONE |

|

Do przedstawiania funkcji logicznych służy nam opis słowny. Na podstawie opisu można sporządzić tablicę wartości (rys. 2.6), zwaną tablicą wierności lub tablicą prawdy (ang. Truth Table).

j |

X0 X1 X2 . . Xn-1 |

f |

0 1 2 3

2n - 1 |

0 0 0 . . . 0 0 0 0 . . . 1

1 1 1 . . . 1 |

|

Rys. 2.6 Tablica wartości n - argumentowej funkcji logicznej.

Tablice prawdy bramek rzeczywistych operują bądź abstrakcyjnymi stanami logicznymi 0 i 1, bądź dwoma poziomami wielkości fizycznych określanych umownie jako niski (L) i wysoki (H). Tablica ta składa się z wierszy, w których wpisuje się wszystkie kombinacje zero - jedynkowe zmiennych niezależnych. Wszystkie kombinacje zmiennych zapisujemy tak, aby tworzyły kolejne liczby dziesiętne zapisane w systemie dwójkowym. Ostatnia kolumna jest przeznaczona do zapisania wartości funkcji dla poszczególnych kombinacji zero - jedynkowych.

Inną metodą bezpośredniego zapisu funkcji n zmiennych są tablice Karnaugha. Tablice te są prostokątne i zwierają 2n pól. Jest to zapis bardzie zwarty i prostszy w użyciu niż tablica wartości. Tablice Karnaugha są dokładniej opisane w podrozdziale 3.2.

Funkcję logiczną o dowolnej liczbie argumentów można również przedstawić w postaci algebraicznej, za pomocą algebry Boole'a. Postać ta nie jest zazwyczaj tworzone bezpośrednio z opisu, lecz pośrednio bądź z tablicy wartości, bądź z tablic Karnaugha.

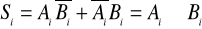

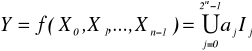

Dowolną funkcję logiczną n zmiennych można przedstawić jako:

(2.1)

gdzie: ![]()

lub 1, a znak ![]()

oznacza sumę logiczną.

Współczynnik aj przyjmuje wartość 1, gdy dla danego j jest ![]()

, natomiast wartość 0, gdy ![]()

.

Ta postać algebraiczna zapisu funkcji nosi nazwę dysjunkcyjnej postaci kanonicznej i jest nazywana krótko postacią ![]()

.

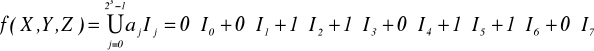

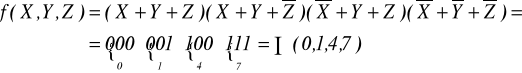

Przykład 2.1:

Wyrazić funkcję f(X, Y, Z), zadaną tablicą wartości z rys. 2.7 w postaci ![]()

.

j |

X |

Y |

Z |

f |

0 1 2 3 4 5 6 7 |

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 0 1 1 0 1 1 0 |

Rys. 2.7 Tablica wartości funkcji f(X, Y, Z).

Jak wynika z tablicy wartości, funkcja ta przyjmuje wartość 1 w wierszach 2, 3, 5 i 6, a wartość 0 w pozostałych wierszach. Zatem funkcja f(X, Y, Z) wyrażona jako ![]()

przyjmuje postać:

Każdy składnik typu ![]()

nie zmienia wartości funkcji, może więc być wyeliminowany. Wtedy funkcja ta przyjmuje postać:

![]()

Jako składniki sumy wchodzą te iloczyny Ij, które odpowiadają kombinacjom zero - jedynkowym zmiennych niezależnych i, dla których funkcja przyjmuje wartość 1.

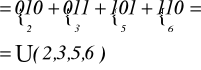

Jeśli funkcja zależy od wielu argumentów, to tworzenie postaci kanonicznej jest pracochłonne i dlatego często jest stosowany zapis skrócony (liczbowy), polegający na wpisywaniu odpowiednich liczb dziesiętnych, symbolizujących składniki jedności.

Przykład 2.2:

Wyrazić funkcję ![]()

w postaci zapisu liczbowego ![]()

.

![]()

Drugą postacią algebraiczną funkcji n - zmiennych jest koniunkcyjna postać kanoniczna, nazywana ![]()

.

(2.2)

gdzie: ![]()

lub 1, a znak ![]()

oznacza iloczyn logiczny.

Przykład 2.3:

Wyrazić funkcję f(X, Y, Z) zadaną tablicą wartości z rys. 2.7 w postaci ![]()

.

Jak wynika z tablicy wartości, funkcja ta przyjmuje wartość 0 w wierszach 0, 1, 4 i 7, a wartość 1 w pozostałych wierszach. Zatem funkcja wyrażona jako ![]()

przyjmuje postać:

![]()

Każdy czynnik typu ![]()

nie zmienia wartości funkcji, może więc być wyeliminowany. Zatem:

![]()

Jako czynniki do iloczynu wchodzą te sumy Sj, które odpowiadają kombinacjom zero - jedynkowym zmiennych niezależnych, dla których funkcja przyjmuje wartość 0.

Jeśli funkcja zależy od wielu argumentów, podobnie jak w przypadku zapisu ![]()

, jest stosowany liczbowy zapis ![]()

.

Przykład 2.4:

Wyrazić funkcję

![]()

w postaci zapisu liczbowego ![]()

.

Bramkami nazywane są kombinacyjne układy cyfrowe, realizujące proste funkcje logiczne jednej lub wielu zmiennych logicznych. Zmienną logiczną jest sygnał elektryczny występujący na wejściach i wyjściach tych układów.

Poniżej zostanie przedstawione działanie logiczne podstawowych typów bramek logicznych.

BRAMKA I (AND)

Bramka ta jest układem o dwu lub większej liczbie wejść, realizującym funkcję iloczynu logicznego zmiennych wejściowych.

W przypadku ogólnym bramki mogą mieć dowolną liczbę wejść, ale typowy układ scalony zawiera zwykle cztery bramki 2 - wejściowe, trzy bramki 3 - wejściowe lub dwie bramki 4 - wejściowe. Wyjście bramki AND jest w stanie wysokim tylko wtedy, gdy oba wejścia są w stanie wysokim (rys. 2.8).

W algebrze Boole'a symbolowi AND odpowiada kropka (·). „A I B” jest zapisywane jako A · B lub po prostu AB.

|

B |

F |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

![]()

Rys. 2.8 Dwuwejściowa bramka I (AND): a) tablica prawdy, b) symbol graficzny.

BRAMKA LUB (OR)

Bramka ta jest układem o dwu lub większej liczbie wejść, realizującym funkcję sumy logicznej zmiennych wejściowych (rys. 2.9). Wyjście bramki OR (LUB) jest w stanie wysokim, jeżeli któreś z wejść (lub oba) jest w stanie wysokim. Można to wyrazić za pomocą „tablicy prawdy”.

a) b)

|

B |

F |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

![]()

Rys. 2.9 Dwuwejściowa bramka LUB (OR): a) tablica prawdy, b) symbol graficzny.

W algebrze Boole'a symbolowi OR odpowiada symbol „+”. „A LUB B” jest zapisywane jako A + B.

BRAMKA NIE (NOT)

Często potrzebujemy zmienić stan logiczny na przeciwny, nazywa się to również negowaniem stanu logicznego. Jest to funkcja inwertora, „bramki” o jednym wejściu (rys. 2.10).

Boole'owskim odpowiednikiem symbolu NOT (negacji Nie) jest kreska pozioma stawiana nad negowanym elementem, a czasem apostrof(`). „NIE A” jest zapisywane jako ![]()

lub jako A'.

a) b)

A |

F |

0 |

1 |

1 |

0 |

![]()

Rys. 2.10 Bramka NIE (NOT): a) tablica prawdy, b) symbol graficzny.

Do podstawowych bramek negacyjnych należy bramka I-NIE (Not AND lub krócej NAND) oraz bramka LUB-NIE (Not OR lub krócej NOR).

BRAMKA I - NIE (NAND)

Bramka ta jest układem realizującym funkcję negacji iloczynu, a więc zgodnie z prawem de Morgana również funkcje sumy negacji zmiennych wejściowych (rys. 2.11).

Funkcja NOT może być połączona z innymi funkcjami, tworząc NAND. Bramka I-NIE (NAND) jest bramką podstawową w kilku klasach scalonych układów cyfrowych.

a) b)

|

B |

F |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

![]()

Rys. 2.11 Bramka I - NIE (NAND): a) tablica prawdy, b) symbol graficzny.

BRAMKA LUB - NIE (NOR)

Bramka ta jest układem realizującym funkcję negacji sumy, a więc zgodnie z prawem de Morgana również funkcję iloczynu negacji zmiennych wejściowych. Podobnie jak bramka I-NIE (NAND), również i ta bramka jest podstawową bramką w kilku klasach scalonych układów cyfrowych (rys. 2.12). Ponieważ funkcje I-NIE (NAND) i LUB-NIE (NOR) są wzajemnie dualne, zatem układ bramek LUB-NIE (NOR) realizujący funkcję f(A, B, ..., Z) po zamianie bramek LUB-NIE (NOR) na bramki I-NIE (NAND), bez zmiany jego struktury, realizować będzie funkcję dualną ![]()

.

a) b)![]()

|

B |

F |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

![]()

Rys. 2.12 Bramka LUB - NIE (NOR): a) tablica prawdy, b) symbol graficzny.

BRAMKA ALBO (EX - OR)

Exclusive - OR (czyli WYŁĄCZNIE LUB) - wyjście bramki XOR jest w stanie wysokim, jeżeli jedno albo drugie wejście jest w stanie wysokim - jest to zawsze funkcja dwóch zmiennych (rys. 2.13). Mówiąc inaczej, wyjście jest w stanie wysokim, jeżeli stany wejść są różne. Bramka XOR realizuje dodawanie bitów modulo - 2.

a) b)

|

B |

F |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

![]()

Rys. 2.13 Bramka ALBO (EX - OR): a) tablica prawdy, b) symbol graficzny.

BRAMKA ALBO - NIE (EX - NOR)

Bramka ALBO (Ex-OR) umożliwia bardzo prostą realizację funkcji ALBO - NIE (rys. 2.14), która ma postać:

F(A, B) = AB+![]()

= A⊗B

Funkcja ALBO-NIE (Exclusive-NOR lub krócej funkcja Ex-NOR), może być zrealizowana bądź za pomocą bramki ALBO (Ex-OR), jeśli na jedno z jej wejść zostanie podany, zamiast sygnału prostego, sygnał zanegowany:

![]()

A⊗B

bądź przez zanegowanie sygnału wyjściowego tej bramki:

![]()

⊗B

a) b)

|

B |

F |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

![]()

Rys. 2.14 Bramka ALBO - NIE (EX -NOR): a) tablica prawdy, b) symbol graficzny.

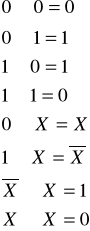

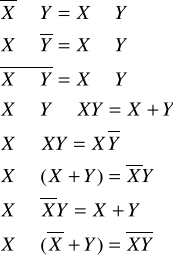

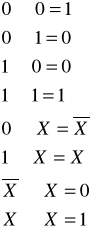

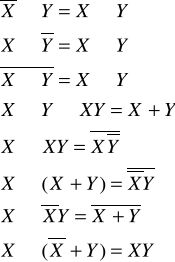

Podstawowe tożsamości dla funkcji ALBO (Ex - OR) i funkcji ALBO - NIE (Ex - NOR) przedstawiono poniżej w tablicy 2.2.

Tablica 2.2 Podstawowe tożsamości dla funkcji ALBO (Ex - OR) i ALBO-NIE (Ex - NOR)

|

|

||

|

|

|

|

Przy projektowaniu układów cyfrowych należy mieć na uwadze, że za pomocą pewnych rodzajów bramek można utworzyć inne. Na przykład, jeżeli potrzebna jest bramka AND, a mamy do dyspozycji dwie dwuwejściowe bramki NAND, możemy zastosować chwyt jaki przedstawia rys. 2.15a.

a)

b)

c)

d)

Rys. 2.15 Przykłady realizacji podstawowych funkcji logicznych.

Funktory (bramki logiczne) są produkowane w postaci scalonej.

Wyróżnia się dwie główne technologie wytwarzania cyfrowych układów scalonych:

Z daną technologią wiąże się określony standard. Standard TTL określa charakterystyczne właściwości scalonych układów logicznych zbudowanych z tranzystorów bipolarnych.

Określony standard jest to ogólnie przyjęta norma definiująca poziomy napięć zasilających, sygnałów wejściowych i wyjściowych, które gwarantują wymienność układów wykonywanych przez różnych producentów oraz poprawne działanie cyfrowych układów scalonych.

W układach TTL najważniejszą częścią standardu są wymagania dotyczące zakresów wartości napięć wejściowych, które układ wykonany w tym standardzie będzie traktował jako określony stan logiczny (0 lub 1) na wejściu oraz zakresów wartości napięć wyjściowych, które układ będzie gwarantował przy określonym poziomie logicznym (0 lub 1) na wyjściu.

Na rys. 2.16 przedstawiono zakres napięć wejść i wyjść scalonych układów logicznych.

Rys. 2.16 Zakresy napięć wejściowych i wyjściowych scalonych układów logicznych wykonanych w technice TTL.

Po prawej stronie osi zaznaczono dozwolone zakresy wartości napięć wejściowych układu TTL:

0,5 ÷ 0,8 V - poziom niski (stan 0);

2 ÷ 5 V - poziom wysoki (stan 1).

Po lewej stronie osi zaznaczono gwarantowane zakresy wartości napięć na wyjściu:

0 ÷ 0,4 V - poziom niski (stan 0);

2,5 ÷ 5 V - poziom wysoki (stan 1).

Do głównych zalet układów TTL należy:

Przykładem układu wykonanego w technice TTL jest układ 7400, zawierający cztery bramki NAND. Schemat jednej bramki NAND pokazano na rys. 2.17.

Rys. 2.17 Schemat ideowy bramki podstawowej NAND (I - NIE).

Bramka spełnia funkcję iloczynu, czyli: ![]()

. Stopień wejściowy bramki stanowi tranzystor wieloemiterowy T1. Tranzystor T2 pracuje w układzie jako wzmacniacz sterujący (rozdzielacz faz), który dostarcza sygnał o odpowiedniej amplitudzie i wydajności prądowej do stopnia wyjściowego zrealizowanego na tranzystorach T3 i T4.

Do wejść bramki są dołączone diody, które tłumią oscylacje powstałe w liniach łączących bramki w czasie ich przełączania i zapobiegają powstawaniu ujemnych napięć o wartości większej niż około 0,5 V.

Jeśli na oba wejścia bramki zostaną podane jedynki, to złącza Baza - Emiter tranzystora T1 będą w stanie nieprzewodzenia (czyli zostaną spolaryzowane zaporowo), prąd Bazy popłynie przez złącze Baza - Kolektor T1 do Bazy tranzystora T2, powodując jego nasycenie (tranzystor T2 przewodzi) oraz zatkanie tranzystora T3.

Typowa wartość napięcia wyjściowego bramki będącej w stanie 0 (na wyjściu jest stan 0) przy prądzie 16 mA - wynosi 220 mV. Dla bramki NAND w stanie 0 napięcie wyjściowe powinno wynosić UOL ≤ 0,4 V, jeżeli prąd wyjściowy IOL ≤ 16 mA.

Gdy choć na jedno wejście będzie podany sygnał 0, spowoduje to przewodzenie (nasycenie) złącza Baza - Emiter tranzystora T1 i spolaryzowanie złącza Baza - Kolektor w kierunku zaporowym. Wynikiem tego jest zatkanie tranzystorów T2 i T4, przewodzenie tranzystora T3 i diody D3.

Jeśli pobór prądu wyjściowego (w stanie wysokim)wynosi 400 μA, a napięcie wejściowe wynosi 0,8 V, to napięcie wyjściowe jest nie mniejsze niż 2,4 V. Jeżeli napięcie wejściowe jest mniejsze niż 0,8 V, to typowa wartość napięcia wyjściowego wynosi około 3,3 V.

Do układów przełączających logicznych zaliczamy:

Cechą odróżniającą układy kombinacyjne i sekwencyjne jest właściwość pamiętania stanów logicznych, które charakteryzują się układy sekwencyjne, a której są pozbawione układy kombinacyjne.

Układ kombinacyjny służy do przetwarzania informacji dyskretnej dwuwartościowej. Informacja dyskretna składa się ze znaków, którymi mogą być zarówno litery, cyfry, jak i inne symbole.

W układzie kombinacyjnym każda kombinacja sygnałów wejściowych określa jednoznacznie kombinację sygnałów wyjściowych. Sygnały wejścia i sygnały wyjścia przyjmują skończoną liczbę kombinacji i skończoną liczbę wartości. Kombinacje sygnałów wejściowych są to stany wejść układu, a kombinacje sygnałów wyjściowych - stany wyjść układu.

Z układem kombinacyjnym mamy do czynienia, jeżeli wartość zmiennych ze zbioru Y zależy od wartości zmiennych ze zbioru X.

Działanie układu kombinacyjnego możemy opisać wyrażeniem:

Y = f (X) (3.1)

gdzie: X - zbiór wszystkich możliwych, dla danego układu stanów wejść,

X = {x1, x2,...,xn,},

Y - zbiór wszystkich możliwych, dla danego układu stanów wyjść,

Y = {y1, y2,,...,yn}.

Zależność Y = f (X) jest równoważna zespołowi (rodzinie) funkcji logicznej:

y1 = f1 (x1...xn) (3.2)

y2 = f2 (x2...xn) (3.3)

ym = fm (x1...xn) (3.4)

gdzie: n - liczba wejść układu kombinacyjnego,

m - liczba wyjść układu kombinacyjnego.

Układ przełączający (logiczny) o n wejściach i m wyjściach można przedstawić w postaci wielobiegunnika pokazanego na rys. 3.1.

Rys. 3.1 Wielobiegunnik układu przełączającego X = {x1, x2,...,xn}, Y = {y1, y2,,...,yn}: a) wyróżniający poszczególne zmienne, zapis uproszczony.

Do realizacji fizycznej kombinacyjnych układów cyfrowych są stosowane bramki logiczne, omówione w rozdziale 2, a także generatory funkcji logicznych, omówione w rozdziale 10.

W układach kombinacyjnych stosuje się metodę Karnaugha.

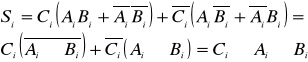

Synteza układu kombinacyjnego sprowadza się do realizacji zespołu funkcji logicznych określonych na tym samym zbiorze zmiennych. O złożoności układowej świadczy liczba funktorów w układzie oraz liczba połączeń, czyli sumaryczna liczba wejść wszystkich funktorów. Obie te liczby stanowią o koszcie układu.

Przy syntezie zespołu funkcji logicznych należy dążyć do minimalizacji funkcji kosztu, biorąc pod uwagę możliwość wykorzystania wspólnych iloczynów (sum) wchodzących w skład rozpatrywanych funkcji.

W celu dokonania realizacji układu kombinacyjnego należy:

Istnieją dwie podstawowe metody minimalizacji funkcji:

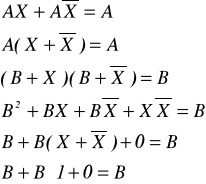

Minimalizacja analityczna metodą algebry Boole'a polega na zapisaniu funkcji logicznej, a następnie zminimalizowaniu (skróceniu zapisu jej z zastosowaniem praw algebry Boole'a (podanych w rozdz. 2).

Przykład 3.1:

Zapisać i zminimalizować funkcję logiczną

Y(A, B, C, D) = (0, 1, 4, 5).

Zapisujemy tę funkcję jako sumę logiczną wszystkich jej elementów: Y(A,B,C,D) = ![]()

.

Grupujemy po dwa iloczyny logiczne:

Y(A,B,C,D) = ![]()

.

Korzystamy z prawa rozdzielności mnożenia względem dodawania:

Y(A,B,C,D) = ![]()

.

Następnie korzystamy z tożsamości:

(![]()

+D = 1)

i z prawa rozdzielności mnożenia względem dodawania:

Y(A,B,C,D) = ![]()

.

Układ sekwencyjny jest to układ dyskretny, którego stan wyjścia nie tylko zależy od stanu wejścia, ale także od wcześniejszego stanu wyjścia. Inaczej mówiąc stan wyjścia zależy od stanu wejścia i stanu wyjścia w chwili T. Oprócz zmiennych wejściowych i wyjściowych, istnieją tzw. stany wewnętrzne Q, a zbiór stanów wewnętrznych określa pamięć układu Q1, Q2,...

Układy sekwencyjne dzielimy na:

Układ synchroniczny to układ, w którym zmiany stanów wewnętrznych i stanów wyjścia odbywa się w ściśle określonych interwałach czasu, czyli w takt impulsu zegarowego.

Układ asynchroniczny to układ, w którym sygnały na wejściu bezpośrednio oddziałują na stany wewnętrzne układu i stany na wyjściu. Układ ten pracuje z szybkością wyznaczoną przez opóźnienie elementów wewnętrznych układu. W układach asynchronicznych sekwencyjnych stosuje się metodę Huffmana.

Układ sekwencyjny może być opisany następującymi równaniami:

![]()

(3.5)

![]()

(3.6)

Równanie (3.5) zwane jest równaniem stanów wewnętrznych. Równanie (3.6) zwane jest równaniem wyjść układu sekwencyjnego. Czasami przyjmuje ono postać:

![]()

(3.7)

Wyżej wymienione równania można przedstawić za pomocą schematów blokowych.

a)

b)

Rys. 3.2 Schemat blokowy układu sekwencyjnego: a) Mealy'ego,

b) Moore'a: UP - układ pamięci, KBW -Kombinacyjny Blok Wyjściowy.

Równanie (3.5) i (3.6) opisują układ sekwencyjny zwany układem Mealy`ego, a wyrażenia (3.5) i (3.7) układ Moore`a (rys. 3.2).

Podstawowymi funktorami sekwencyjnych układów cyfrowych są funktory, umożliwiające budowę układu kombinacyjnego, czyli bramki logiczne oraz przerzutniki, które są omówione w rozdziale 4.

Najczęściej stosowanym i najprostszym rodzajem opisu układu kombinacyjnego jest tablica wartości, która ukazuje zależność sygnałów wyjściowych Y od sygnałów zmiennych wejściowych X.

Tablice Karnaugha służą do bezpośredniego zapisu n zmiennych. Tablice te są prostokątne i zawierają 2n pól. Kolumnom (i wierszom) siatek zostały przypisane wartości w kodzie, zwanym kodem cyklicznym Graya, gdzie dwie sąsiednie pozycje różnią się jednym znakiem.

Kolejność taka jest charakterystyczną właściwością tablicy Karnaugha, która jest wykorzystana do przeprowadzenia uproszczenia w oparciu o tzw. regułę sklejania (patrz tabel 2.2):

gdzie: A, B - zmienne lub funkcje logiczne.

Zmienną, która w dwóch sąsiednich polach przyjmuje różne wartości można pominąć.

Najprostszą z możliwych tablic Karnaugha dla układu dwuwejściowego przedstawiono na rys. 3.3. Za jej pomocą możemy opisać funkcję logiczną dwu sygnałów wejściowych (D0 i D1 ).

a) b)

|

0 |

1 |

|

D1 |

D0 |

|

|

Y = D1 |

|

||||||

0 |

|

|

|

0 |

0 |

0 |

|

D1 |

D0 |

Y |

|

||||

1 |

|

|

|

0 |

1 |

1 |

|

0 |

0 |

0 |

|

||||

|

|

|

|

1 |

1 |

3 |

|

0 |

1 |

0 |

|

D0 D1 |

0 |

1 |

|

|

|

|

|

1 |

0 |

2 |

|

1 |

1 |

0 |

|

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

1 |

1 |

0 |

|

Rys. 3.3 Tablica Karnaugha dla układu dwuwejściowego: a) niewypełniona,

b) przykładowe jej wypełnienie.

Na rysunku zaznaczono strzałkami, jakim kombinacjom sygnałów wejściowych odpowiada dane pole. Tablica ta jest niewypełniona, tzn. nie opisuje żadnej funkcji logicznej. Jej wypełnienie polega na wpisaniu w każde pole takiego stanu (0, 1), jaki powinien pojawić się na wyjściu układu przy danej kombinacji sygnałów wejściowych.

Na rys. 3.3b przedstawiono wypełnioną przykładowo tablicę Karnaugha. Obok niej zapisano występujące możliwe kombinacje stanów logicznych sygnałów wejściowych D0 i D1 oraz odpowiadający im sygnał wyjściowy Y.

Zatem, tablica Karnaugha jest to specjalny rodzaj tablicy, do której w pola opisane jednoznacznie kombinacją sygnałów wejściowych wpisuje się odpowiadającą im wartość sygnału wyjściowego. Na rys. 3.4 przedstawiono tablicę czterech zmiennych. Każde dwa sąsiadujące ze sobą pola (stykające się jednym bokiem oraz leżące przy krawędziach A - A' i B-B') tej tablicy różnią się w opisach odpowiadających im sygnałów wejściowych tylko jednym bitem (jedną pozycją).

CD AB |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

3 |

2 |

01 |

4 |

5 |

7 |

6 |

11 |

12 |

13 |

15 |

14 |

10 |

8 |

9 |

11 |

10 |

Rys. 3.4 Tablica Karnaugha czterech zmiennych.

Aby zapisać do tablicy Karnaugha funkcję o większej liczbie sygnałów wejściowych, należy stopniowo zwiększać jej rozmiary, stosując w tym celu tzw. metodę odbiciu lustrzanego. Sposób tworzenia tablicy dla czterech zmiennych z tablicy dwóch zmiennych przedstawiono na rys. 3.5.

|

0 |

1 |

1 |

0 |

|

|

00 |

01 |

11 |

10 |

0 |

|

|

|

|

|

0 |

|

|

|

|

1 |

|

|

|

|

|

1 |

|

|

|

|

c) d)

|

00 |

01 |

11 |

10 |

|

|

00 |

01 |

11 |

10 |

00 |

|

|

|

|

|

00 |

|

|

|

|

01 |

|

|

|

|

|

01 |

|

|

|

|

11 |

|

|

|

|

|

11 |

|

|

|

|

10 |

|

|

|

|

|

10 |

|

|

|

|

Rys 3.5 Etapy tworzenia tablicy Karnaugha dla czterech sygnałów wejściowych L - L' - oś odbicia lustrzanego.

Polega on na przekształceniu tablicy Karnaugha dla dwóch sygnałów wejściowych A, B (rys. 3.5a) w tablicę dla trzech sygnałów wejściowych A, B, C (rys. 3.5b) a następnie w tablicę dla czterech sygnałów A, B, C, D (rys. 3.5c,d).

Każde zwiększenie liczby sygnałów wejściowych o jeden powoduje podwojenie rozmiarów tablicy.

Następnym krokiem jest wypełnienie pól tak utworzonej tablicy. Funkcja logiczna może być podana na przykład w postaci: opisu słownego, zbioru liczb, dla których reprezentacji dwójkowej odpowiada na wyjściu poziom 1 lub innego jednoznacznego opisu.

Przykład 3.2

Utworzyć tablicę Karnaugha dla funkcji Y(A, B, C, D) = (0, 1 , 4, 5, 10, 14).

Sposób wypełniania tablicy:

Wypełnioną w ten sposób tablicę funkcji Y(A, B, C, D) przedstawiono na rys. 3.6b.

a) b)

|

00 |

01 |

11 |

10 |

|

|

MSB A B |

LSB C D |

||

00 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

01 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

11 |

0 |

0 |

0 |

1 |

|

4 |

0 |

1 |

0 |

0 |

10 |

0 |

0 |

0 |

1 |

|

5 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

10 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

Rys 3.6 Sposób wypełnienia tablicy Karnaugha.

Na podstawie wypełnionej tablicy Karnaugha można przystąpić do realizacji funkcji na bramkach logicznych. Każdemu polu tablicy odpowiada bramka AND. Powstaje pytanie, czy przy dużej liczbie jedynek w tablicy należy również stosować tak dużo bramek, czy nie można zmniejszyć ich liczby? Okazuje się, że można. Liczba bramek zależy od tego, w jakim stopniu uda się zminimalizować funkcję Y.

Jeżeli dwie kombinacje sygnałów wejściowych, przy których na wyjściu powinien pojawić się poziom 1 różnią się między sobą na jednym bicie (jednym sygnałem wyjściowym, np. 0001 i 0011), oznacza to, że sygnał wyjściowy dla tych kombinacji nie zależy od wartości tego bitu. Zatem, zamiast dwóch bramek AND czterowejściowych można użyć tylko jednej bramki AND trójwejściowej.

W tablicy Karnaugha odpowiada to połączeniu w odpowiedni sposób jedynek w pary. Jedynki można również łączyć w czwórki, ósemki, szesnastki itp. Taką operację nazywamy sklejaniem jedynek lub sprowadzeniem zapisu funkcji do kanonicznej postaci sumy (suma iloczynów).

Sklejanie dwóch jedynek w tablicy Karnaugha jest możliwe, jeżeli:

Na rys. 3.7 przedstawiono tablicę Karnaugha ze sklejonymi parami jedynek.

|

00 |

01 |

11 |

10 |

00 |

1 |

1 |

1 |

0 |

01 |

0 |

1 |

1 |

0 |

11 |

0 |

0 |

0 |

1 |

10 |

0 |

0 |

1 |

1 |

Rys 3.7 Przykłady sklejenia dwóch jedynek.

Sklejane dwójki jedynek można połączyć w czwórki (rys. 3.7), jeżeli:

|

000 |

001 |

011 |

010 |

110 |

111 |

101 |

100 |

00 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

01 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

11 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

10 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

Rys 3.8 Przykłady sklejenia dwóch dwójek.

Najogólniej mówiąc minimalizację siatki Karnaugha otrzymamy, gdy zastosujemy następujące zasady:

Przykład 3.3:

Zminimalizować funkcję Y(A, B, C, D) = ![]()

(0, 1, 4, 5, 10, 14) za pomocą tablicy Karnaugha.

W tablicy na rys. 3.6b znajduje się sześć jedynek, które można połączyć w trzy dwójki (rys. 3.9a). Dwie dwójki można połączyć w czwórkę (rys. 3.9a). Realizację tej funkcji logicznej na bramkach przedstawiono na rys. 3.9b.

a)

|

00 |

01 |

11 |

10 |

00 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

11 |

0 |

0 |

0 |

1 |

10 |

0 |

0 |

0 |

1 |

![]()

b)

![]()

Rys 3.9 Realizacja funkcji Y = (0, 1, 4, 5, 10, 14): a) wypełniona tablica Karnaugha z zakreślonymi parami jedynek (pary jedynek połączone w czwórki), b) układ zbudowany z bramek

Może się zdarzyć, że fizyczne warunki działania urządzenia nie dopuszczają wystąpienia pewnych kombinacji zmiennych. Jeśli dana kombinacja zero - jedynkowa nigdy na wejściu układu się nie pojawia lub gdy nie jest istotne, jaki stan logiczny pojawi się na wyjściu przy tej kombinacji, można przyjąć, że dla takiej kombinacji wartość funkcji może wynosić 0, jak również 1. Taka możliwość przyjęcia dowolnej wartości funkcji jest bardzo przydatna w procesie minimalizacji.

W tablicach, dla oznaczenia dowolnej wartości funkcji zapisuje się umownie symbol: -, ∼, ∅, X.

Niektóre funkcje logiczne , zwłaszcza takie, w których przeważa liczba jedynek nad liczbą zer, można zrealizować w prosty sposób dzięki sklejaniu zer (tak samo jak jedynek). Jedyną różnicą jest to, że otrzymaną funkcję należy zanegować, czyli podać na wyjście układu przez negator.

Przykład 3.4:

Zrealizować funkcję Y(A, B, C, D) = ![]()

(5, 7, 8, 9, 12, 15).

W celu zminimalizowania funkcji należy przedstawić ją w tablicy Karnaugha (rys. 3.10a). W tablicy znjduje się sześć jedynek, które można połączyć w cztery pary. Z tablicy otrzymuje się:

![]()

Układ służący do realizacji tej funkcji można zbudować z bramek I (AND), LUB (OR), NIE (NOT). Układem równoważnym jest układ zbudowany z bramek I - NIE (NAND), który przedstawiono na rys. 3.10b.

Po przekształceniach funkcja przyjmie postać:

![]()

Układ służący do realizacji tej funkcji zbudowany z bramek I (AND), NIE (NOT) i ALBO (Ex - OR) przedstawia rys. 3.10c.

a)

|

00 |

01 |

11 |

10 |

00 |

0 |

0 |

0 |

0 |

01 |

0 |

1 |

1 |

0 |

11 |

1 |

0 |

1 |

0 |

10 |

1 |

1 |

0 |

0 |

b) c)

Rys. 3.10 Funkcja Y(A, B, C, D) = ![]()

(5, 7, 8, 9, 12, 15):

a) tablica Karnaugha, b, c)schematy logiczne.

Przykład 3.5:

Rys. 3.11 Schemat logiczny funkcji.

Aby uzupełnić siatkę Karnaugha należy najpierw określić stany w punktach a, b, c, d, e, co pokazano w tabeli 3.1.

Tablica 3.1

A B C D |

a

|

b

|

c

|

d

|

e

|

0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 |

1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 |

0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 |

1 1 1 0 0 0 0 1 0 0 0 1 0 0 0 1 |

1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 |

0 0 0 1 1 1 1 0 1 1 1 1 1 1 1 1 |

Następnie wpisujemy wynik z punktu e w tablicę Karnaugha (rys. 3.12). Z tablicy otrzymujemy:

![]()

|

00 |

01 |

11 |

10 |

00 |

0 |

0 |

1 |

0 |

01 |

1 |

1 |

0 |

1 |

11 |

1 |

1 |

1 |

1 |

10 |

1 |

1 |

1 |

1 |

Rys. 3.12 Siatka Karnaugha dla funkcji.

Układ budujemy z trzech 3 - wejściowych i jednej 4 - wejściowej bramki NOR (rys. 3.13).

Rys. 3.13 Realizacja funkcji na bramkach NOR.

Oprócz przedstawionej wyżej metody, minimalizację funkcji logicznych można przeprowadzić stosując:

Zadanie:

Udowodnić, że dla siatki Karnaugha pokazanej na rys. 3.14 funkcja ma postać:

Y = X2 X0![]()

X1X0 X3X2 |

00 |

01 |

11 |

10 |

00 |

0 |

X |

X |

0 |

01 |

X |

X |

X |

0 |

11 |

X |

X |

X |

X |

10 |

0 |

X |

X |

0 |

Rys. 3.14 Siatka Karnaugha do zadania.

Zapamiętywanie wartości zmiennych binarnych, jak również sekwencji tych wartości odbywa się w układach zwanych elementami pamięci. Podstawowym elementem jest funktor, którego podstawową funkcją jest pamiętanie jednego bitu informacji, zwany przerzutnikiem.

Przerzutniki mogą występować oddzielnie lub w zespołach, połączone w rejestry, liczniki lub bloki pamięci.

W przerzutnikach scalonych TTL wyróżnia się dwa podstawowe rodzaje wejść informacyjnych:

Wejścia asynchroniczne - to takie, w których zmiana wartości informacji wywołuje bezpośrednio zmianę wartości zmiennych wyjściowych.

Wejścia synchroniczne - używane są do wywołania zmiany wartości zmiennych wyjściowych, ale zmiana następuje w takt impulsu synchronizującego, zwanego też impulsem zegarowym (ang. clock) lub taktującym. Brak impulsu taktującego oznacza, że przerzutnik nie będzie reagował na zmiany wartości zmiennych informacyjnych synchronicznych przerzutnika.

Przerzutnik jest układem posiadającym (rys. 4.1):

Zmienne s i r oddziałują na wartości zmiennych wyjściowych Q i ![]()

. Zmienna s zwana jest zmienną wpisującą (ang. set) lub ustawiającą (ang. preset). Służy ona do ustawiania przerzutnika w stan wysoki (Q = 1; ![]()

= 0). Zmienna r zwana jest zmienną zerującą (ang. reset lub clear). Służy ona do zerowania przerzutnika w stan niski (Q = 0; ![]()

= 1).

Zmienne A i B w różny sposób oddziałują na zmienne wyjściowe Q i ![]()

. Decyduje to o nazwie typu przerzutnika.

Na wejście zegarowe, oznaczone literą C, wprowadza się impuls taktujący. Wejście to zwane jest inaczej synchronizującym albo wyzwalającym.

Rys. 4.1 Schemat graficzny przerzutnika.

W symbolach graficznych i wielu bardziej złożonych układów logicznych niektóre wejścia są oznaczone literą z zaznaczoną nad nią poziomą kreską (negacją). Oznacza to, że funkcja przypisana temu wejściu jest uaktywniana pojawieniem się na nim stanu logicznego 0 (poziomem aktywnym jest stan niski). Do zaznaczenia sposobu oddziaływania wejść na układ stosuje się również oznaczenia graficzne (rys.4.2).

Rys. 4.2 Oznaczenia graficzne wejść przerzutnika.

Jeśli o wartości zmiennej wyjściowej przerzutnika decydują tylko wejścia asynchroniczne to mamy do czynienia z przerzutnikiem asynchronicznym W przerzutniku tym informacja na wyjściu pojawia się w chwilach uzależnionych tylko od zmiany stanu na jego wejściach. Do tej grupy zaliczamy głównie przerzutnik s r.

Gdy stan przerzutnika ulega zmianie pod wpływem impulsu zegarowego, mówimy wtedy o przerzutniku synchronicznym. Podstawowymi typami przerzutników synchronicznych są: RS, D, T i JK.

W układach TTL stosuje się: