Wymień zalety wykorzystania wspomagania komputerowego przy projektowaniu układów cyfrowych:

- programy komp. automatycznie mogą planować położenie elementów;

- istnieje gotowa baza elementów;

- możliwość łatwego przeniesienia ścieżek na płytkę;

Wymień i opisz sposoby specyfikacji projektowanych układów w programie ACTIVE-CAD

- przy pomocy edytora schematów (Schematic Capture), umożliwiającego tworzenie schematów ideowych budowanych układów;

- przy pomocy grafów przejść automatów skończonych FSM (Finite State Machine );

przy użyciu języka opisu sprzętu VHDL.

Scharakteryzuj tryby symulacji w programie ACTIVE-CAD.

Podaj definicję układu kombinacyjnego.

To takie uklady ktorch stnay wysjsc sa zawsze jednoznacznie okreslone przez stany wejsc.Oznacza to ze odprowadzajac na wejsice takich ukladow okreslona kombinacje sygnalow inarnych, otrzymujemy na wyjsciu odpowiedzi specyficzne dla zastosowanaia wymuszen i funkcji logicznej, jaka wykouja uklady, niezaleznie od tego co działo sie z tymi ukladami wczesnej. Mozna zatem powiedizec ze sa to uklady bez pamieci. Ich przedstawiicelami sa bramki.

Podaj definicję układu sekwencyjnego.

- automaty, w których stany wyjściowe zmieniają się w czasie zmiany stanu automatu, a więc zależą tylko od stanu automatu, nazywane są automatami Moore'a,

- automaty, w których stany wyjściowe zmieniają się także w czasie zmiany stanu sygnałów wejściowych, a więc zależą i od stanu automatu i od stanu sygnałów wejściowych, nazywane są automatami Mealy'ego.

Wymień przykłady układów kombinacyjnych i sekwencyjnych.

Układy kombinowane: bramki logiczne...

Układy sekwencyjne: synchroniczne

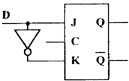

Przerzutnik typu T oraz jego tablica przejść

Przerzutnik typu RS oraz jego tablica przejść

Narysuj tabele prawd bramek logicznych: AND, NAND, OR, NOR, NOT, EXOR.

Narysuj oznaczenia graficzne powyższych bramek.

Przy pomocy bramek NAND zbuduj NOT, AND, OR.

Przy pomocy bramek NOR zbuduj NOT, AND, OR.

Scharakteryzuj bramkę trójstanową.

Co to jest stan ,,wysokiej rezystancji''.

Co to są uniwibrator i multiwibrator.

Narysuj tabele prawd przerzutników RS, JK, D, T.

Napisz równania logiczne przerzutników RS, JK, D, T.

Dokonaj zamiany przerzutnika:

AND |

A |

B |

W |

||||||||||||

|

0 |

0 |

0 |

||||||||||||

|

0 |

1 |

0 |

||||||||||||

|

1 |

0 |

0 |

||||||||||||

|

1 |

1 |

1 |

||||||||||||

NAND |

A |

B |

W |

||||||||||||

|

0 |

0 |

1 |

||||||||||||

|

0 |

1 |

1 |

||||||||||||

|

1 |

0 |

1 |

||||||||||||

|

1 |

1 |

0 |

||||||||||||

OR |

A |

B |

W |

||||||||||||

|

0 |

0 |

0 |

||||||||||||

|

0 |

1 |

1 |

||||||||||||

|

1 |

0 |

1 |

||||||||||||

|

1 |

1 |

1 |

||||||||||||

NOR |

A |

B |

W |

||||||||||||

|

0 |

0 |

1 |

||||||||||||

|

0 |

1 |

0 |

||||||||||||

|

1 |

0 |

0 |

||||||||||||

|

1 |

1 |

0 |

||||||||||||

NOT |

A |

W |

||||||||

|

0 |

0 |

||||||||

|

1 |

0 |

||||||||

|

|

|

||||||||

|

|

|

||||||||

XOR |

A |

B |

W |

|||||||

|

0 |

0 |

0 |

|||||||

|

0 |

1 |

1 |

|||||||

|

1 |

0 |

1 |

|||||||

|

1 |

1 |

0 |

|||||||

XNOR |

A |

B |

W |

|||||||

|

0 |

0 |

1 |

|||||||

|

0 |

1 |

0 |

|||||||

|

1 |

0 |

0 |

|||||||

|

1 |

1 |

1 |

|||||||

NOT a = a NAND a

a AND b = NOT( a NAND b) = ( a NAND b) NAND ( a NAND b )

a OR b = ( NOT a ) NAND ( NOT b ) = ( a NAND a ) NAND ( b NAND b )

NOT a = a NOR a

a OR b = NOT ( a NOR b) = ( a NOR b) NOR ( a NOR b )

a AND b = NOT (( NOT a ) OR ( NOT b )) = ( NOT a ) NOR ( NOT b ) = ( a NOR a ) NOR ( b NOR b )

Zapewniaja wspolprace z szyna danych, przy której niewygodne jest uzywanie obciążenia aktywnego charakterystycznego dla układów dwutranzystorowych. Bramka trojstanowa charakteryzuje się dwoma stanami logicznymi: wysokim i niskim oraz układem o wysokiej impedancji wyjściowej pozwalającej uznac ze bramka w tym trzecim stanie odlaczona jest od reszty układu. Bramka posiada dodatkowe wejście sterujące EN (enable). Przy niskim stanie tranzystory T7 i T8 nie przewodza i bramka dziala normalnie. Przy stanie wysokim tranzystory te sa w stanie nasycenia, co znaczy ze tranzystory T2 T3 T4 nie rpzewodza niezależnie od stanu na wejściach A i B.

Stan wysokiej rezystancji wystepuje wtedy gdy do wejścia strobujacego tranzystora CMOS doprowadzone będzie napiecie o niskiej wartości. Jeśli wystapi taki stan na obu tranzystorach to bramka zrealizuje rozwarcie obwodu miedzy wejściem a wyjsciem.

Uniwibrator - przerzutnik monostabilny, charakteryzuje się jednymn stanem stabilnym i jednym quasi stabilnym. Przejscie ze stanu stabilnego na quasi stabilny nastepuje pod wpływem zewnetznego impulsu wyzwalającego natomiast powrotny samoczynnie. SA stosowane jako układy odtwarzania, lub przetwarzania pojedynczego impulsu, jako układy opóźnień czasowych, bądź selektorow czasowych.

Multiwibrator - charakteryzuje się dowam stanami quasi stabilnym, przejscie z jednego w drugi odbywa się samoczynnie. Stosowane SA jako układy generujące ciagi impulsow prostokątnych np. generatory taktujące (zegarowe) w technice cyfrowej

S |

R |

Qn+1 |

|

We |

Wy (Qn+1=D) |

|

J |

K |

Qn+1 |

|

J |

Qn |

Qn+1 |

0 |

0 |

Qn |

|

D |

Qn>Qn+1 |

|

0 |

0 |

Qn |

|

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 - 0 |

|

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 - 0 |

|

1 |

0 |

1 |

|

1 |

0 |

1 |

1 |

1 |

NA |

|

1 |

0 - 1 |

|

1 |

1 |

Qn(wek) |

|

1 |

1 |

0 |

|

|

|

|

1 |

1 - 1 |

|

|

|

|

|

|

|

|

SR : Qn+1 = S + n * R(wek)

D : Qn+1 = D

JK : Qn+1 = J * Qn(wek) + K * Qn(wek)

T : ????

Zmiana przerzutnika JK -> D

Przerzutnik typu D można uzyskać poprzez odpowiednie zanegowanie złącza J do K przerzutnika JK (inna synchronizacja 1->0):

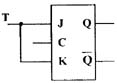

Zmaian przerzutnika JK -> T

Przerzutnik typu Tmożna uzyskać poprzez odpowiednie połączenie złącza K i J przerzutnika JK (inna synchronizacja - 1->0):

Wyszukiwarka

Podobne podstrony:

cw 23 sprawozdanie, Semestr IV, Wspólne, Podstawy elektroniki II

spr 21, Semestr IV, Wspólne, Podstawy elektroniki II

sprawozdanie24, Semestr IV, Wspólne, Podstawy elektroniki II

sprawko ćw 4, Semestr IV, Wspólne, Podstawy elektroniki II

CW 4 wejściówka char pr-nap tyrystora, Semestr IV, Wspólne, Podstawy elektroniki II

elektronika 24 10pkt, Semestr IV, Wspólne, Podstawy elektroniki II

Wejscie Ćwiczenie 24, Semestr IV, Wspólne, Podstawy elektroniki II

infr lotnicz2, Semestr IV, Wspólne, Podstawy Inżynierii Ruchu

ZADANIA Z KOLOKWIUM Z PODST automatyki A[1]. Kochan, Semestr IV, Wspólne, Podstawy automatyki

najlepsza ściąga na PIR, Semestr IV, Wspólne, Podstawy Inżynierii Ruchu

automaty sciaga, Semestr IV, Wspólne, Podstawy automatyki

lot1, Semestr IV, Wspólne, Podstawy Inżynierii Ruchu

SUDA-pytania i odp1, Semestr IV, Wspólne, Podstawy Inżynierii Ruchu

AUTOMATY opracowanie, Semestr IV, Wspólne, Podstawy automatyki

suda sciaga!!!!, Semestr IV, Wspólne, Podstawy Inżynierii Ruchu

infr lotnicz2, Semestr IV, Wspólne, Podstawy Inżynierii Ruchu

Ćwiczenie 7, Semestr IV, Wspólne, Elektrotechnika III

więcej podobnych podstron