169 3

334

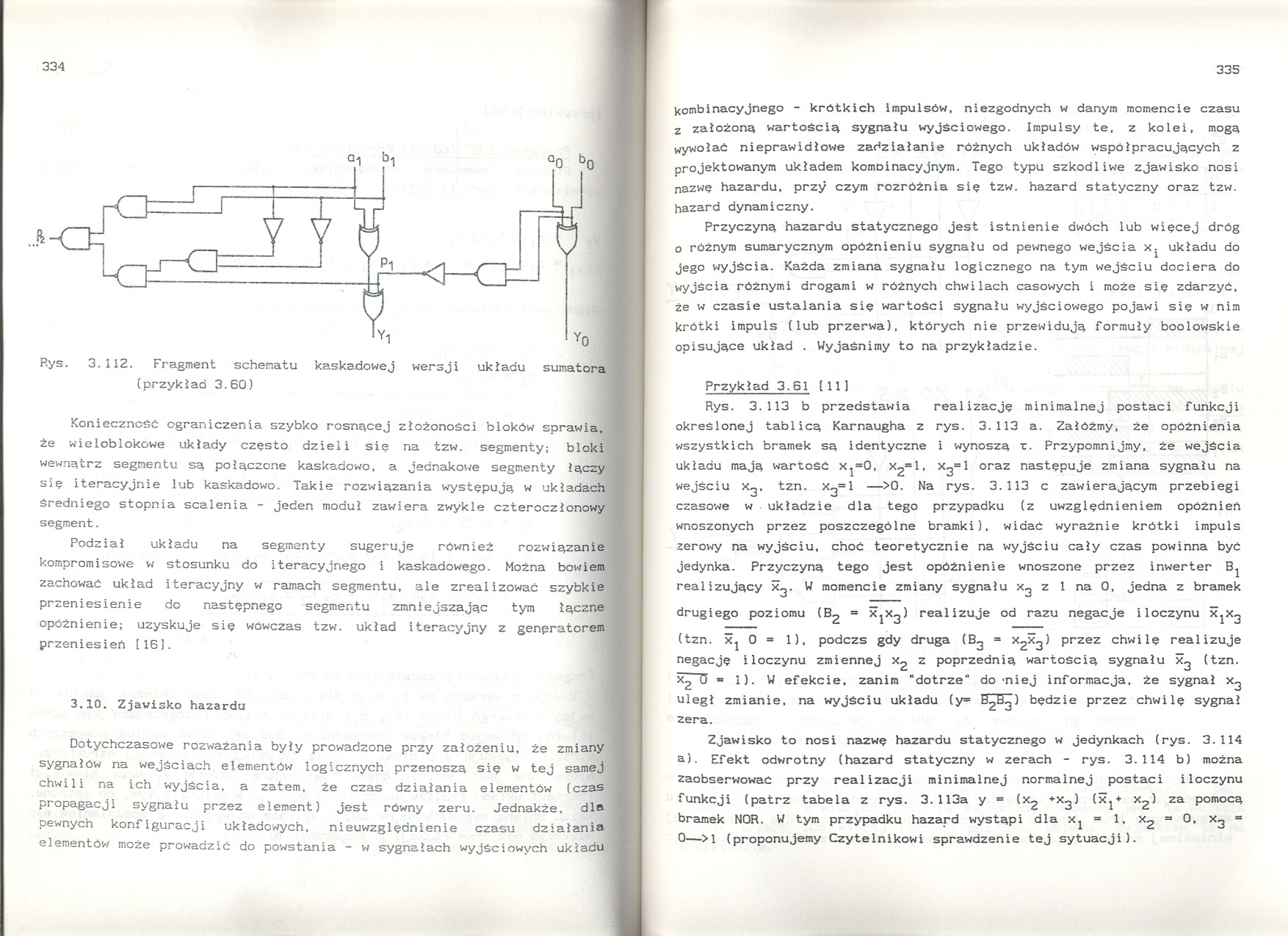

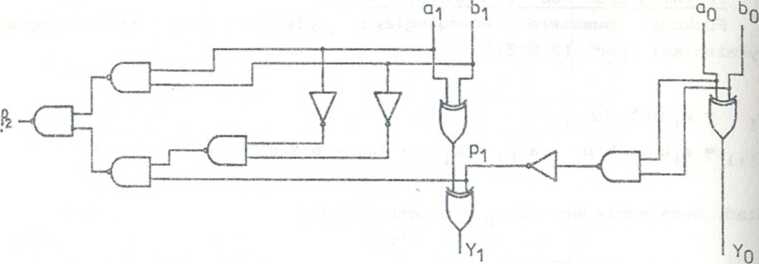

Rys. 3.112. Fragment schematu kaskadowej wersji układu sumatora (przykład 3.60)

Konieczność ograniczenia szybko rosnącej złożoności bloków sprawia, że wieloblokowe układy często dzieli się na tzw. segmenty; bloki wewnątrz segmentu są połączone kaskadowo, a jednakowe segmenty łączy się iteracyjnie lub kaskadowo. Takie rozwiązania występują w układach średniego stopnia scalenia - jeden moduł zawiera zwykle czteroczłonowy segment.

Podział układu na segmenty sugeruje również rozwiązanie kompromisowe w stosunku do iteracyjnego i kaskadowego. Można bowiem zachować układ iteracyjny w ramach segmentu, ale zrealizować szybkie przeniesienie do następnego segmentu zmniejszając tym łączne opóźnienie; uzyskuje się wówczas tzw. układ iteracyjny z generatorem przeniesień [161.

3.10. Zjawisko hazardu

Dotychczasowe rozważania były prowadzone przy założeniu, że zmiany sygnałów na wejściach elementów logicznych przenoszą się w tej samej chwili na ich wyjścia, a zatem, że czas działania elementów (czas propagacji sygnału przez element) jest równy zeru. Jednakże, dla pewnych konfiguracji układowych, nieuwzględnienie czasu działania elementów może prowadzić do powstania - w sygnałach wyjściowych układu kombinacyjnego - krótkich impulsów, niezgodnych w danym momencie czasu z założoną wartością sygnału wyjściowego. Impulsy te, z kolei, mogą wywołać nieprawidłowe zadziałanie różnych układów współpracujących z projektowanym układem komDinacyjnym. Tego typu szkodliwe zjawisko nosi nazwę hazardu, przy czym rozróżnia się tzw. hazard statyczny oraz tzw. hazard dynamiczny.

Przyczyną hazardu statycznego jest istnienie dwóch lub więcej dróg o różnym sumarycznym opóźnieniu sygnału od pewnego wejścia x^ układu do jego wyjścia. Każda zmiana sygnału logicznego na tym wejściu dociera do wyjścia różnymi drogami w różnych chwilach casowych i może się zdarzyć, że w czasie ustalania się wartości sygnału wyjściowego pojawi się w nim krótki impuls (lub przerwa), których nie przewidują formuły boolowskie opisujące układ . Wyjaśnimy to na przykładzie.

Przykład 3.61 [11]

Rys. 3.113 b przedstawia realizację minimalnej postaci funkcji określonej tablicą Karnaugha z rys. 3.113 a. Załóżmy, że opóźnienia wszystkich bramek są identyczne i wynoszą z. Przypomnijmy, że wejścia układu mają wartość Xj=0, x2=l, x3=l oraz następuje zmiana sygnału na wejściu x3, tzn. x3=l —>0. Na rys. 3.113 c zawierającym przebiegi czasowe w układzie dla tego przypadku (z uwzględnieniem opóźnien wnoszonych przez poszczególne bramki), widać wyraźnie krótki impuls zerowy na wyjściu, choć teoretycznie na wyjściu cały czas powinna być jedynka. Przyczyną tego jest opóźnienie wnoszone przez inwerter realizujący x^. W momencie zmiany sygnału x^ z 1 na 0, jedna z bramek

drugiego poziomu (B2 = XjX3) realizuje od razu negacje iloczynu XjX3

(tzn. Xj 0 = 1), podczs gdy druga (B^ = x2x3) przez chwilę realizuje negację iloczynu zmiennej x2 z poprzednią wartością sygnału x3 (tzn. x2 0 = 1). W efekcie, zanim "dotrze" do niej informacja, że sygnał x3 uległ zmianie, na wyjściu układu (y= B-jB^) będzie przez chwilę sygnał zera.

Zjawisko to nosi nazwę hazardu statycznego w jedynkach (rys. 3.114 a). Efekt odwrotny (hazard statyczny w zerach - rys. 3.114 b) można zaobserwować przy realizacji minimalnej normalnej postaci iloczynu funkcji (patrz tabela z rys. 3.113a y = (x2 +x3) (Xj + x2) za pomocą bramek NOR. W tym przypadku hazard wystąpi dla Xj = 1. x2 = 0, x3 = 0—>1 (proponujemy Czytelnikowi sprawdzenie tej sytuacji).

Wyszukiwarka

Podobne podstrony:

DSCF6423 WAŻENIE PAROWANIE t=U2-US C ■ = 1-1.5h: PzOAMR^RYS. 17:3. Fragment schematu blokowego

napoje?zalk�5 365 Rys. 12. Typowy schemat produkcji napojów w skali przemysłowej Przykładowo okres p

223 2 4.7. REGULACJA TURBIN Rys. 4.23. Uproszczony schemat ideowy działania układu regulacji prędkoś

091 3 178 Proponujemy Czytelnikowi zbudowanie odpowiedniego schematu dla wersji Moore’a z rys. 6.14

Rys 6 24 bmp 17Rys. 6-24. Schemat kaskadowego urządzenia chłodniczego (dwuczynniko-wego) [13] l — sp

Rys. 1. Fragment schematu procedury oznaczania i opisu gruntów według PN-EN ISO 14688-1:2006/Apl:201

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

Image305 Na rys. 4.350 przedstawiono schemat logiczny tetrady sumatora dziesiętnego — akumulującego.

Image333 W celu zilustrowania komparacji liczb przedstawionych w kodzie 8421 BCD, na rys. 4.380 prze

skanuj0006 (127) 8.5. ZADANIE - OBLICZENIE PARAMETRÓW TENSOMETRU8.5.1. Wprowadzenie Na rys. 8.4 są p

więcej podobnych podstron