1. Architektura komputera

1/24

1

2

3

4

5

Praktyczny przykład

prostego systemu

komputerowego

1. Architektura komputera

2/24

1

2

3

4

5

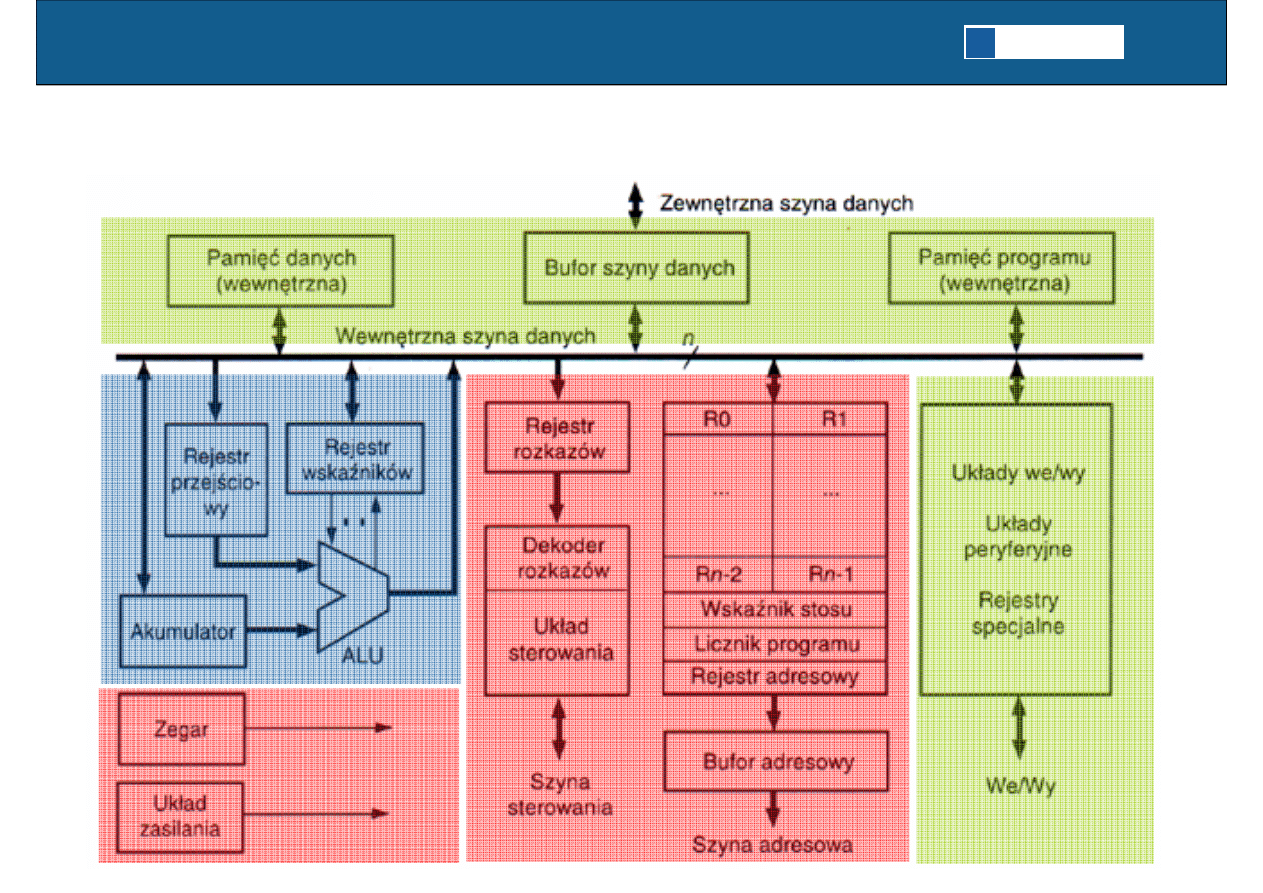

Architektura von Neumanna

1. Architektura komputera

3/24

1

2

3

4

5

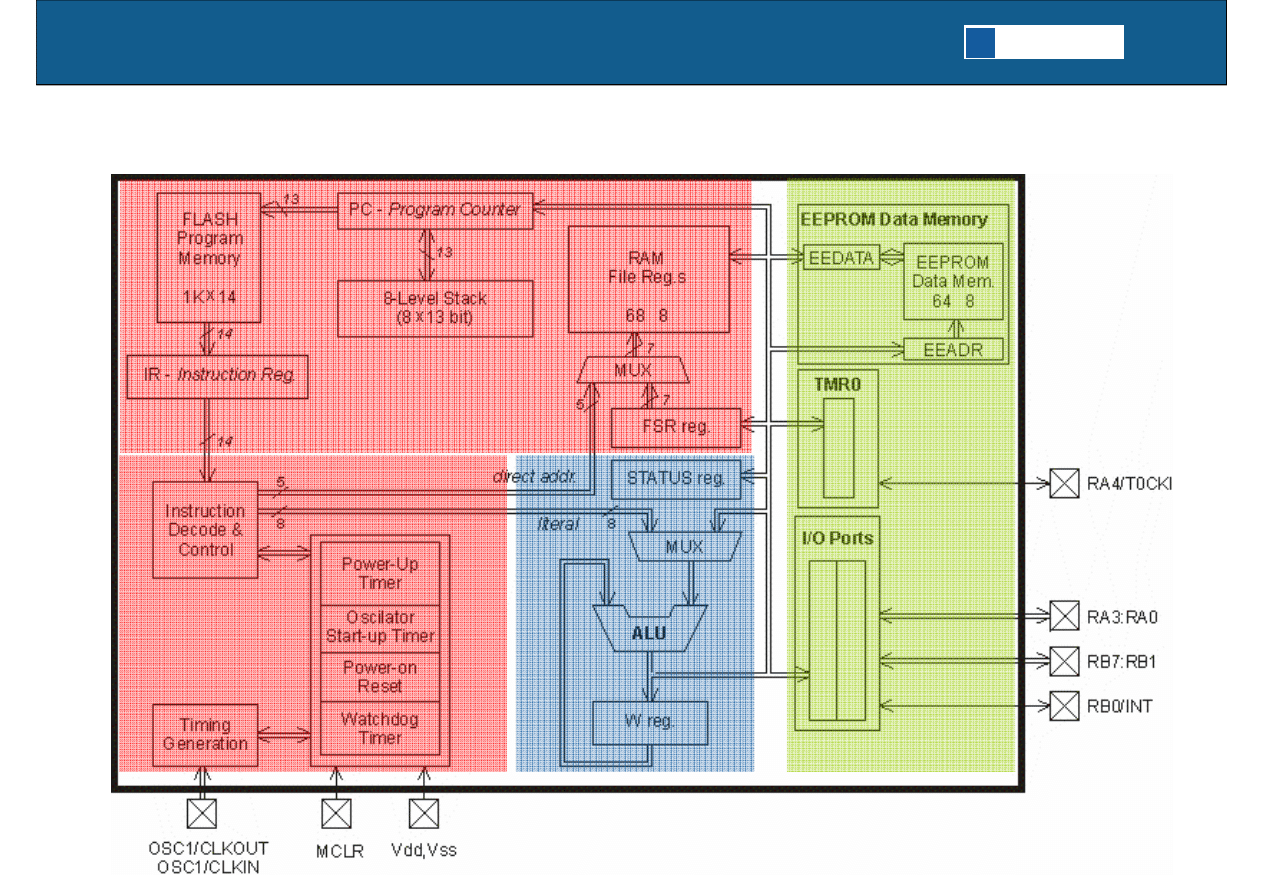

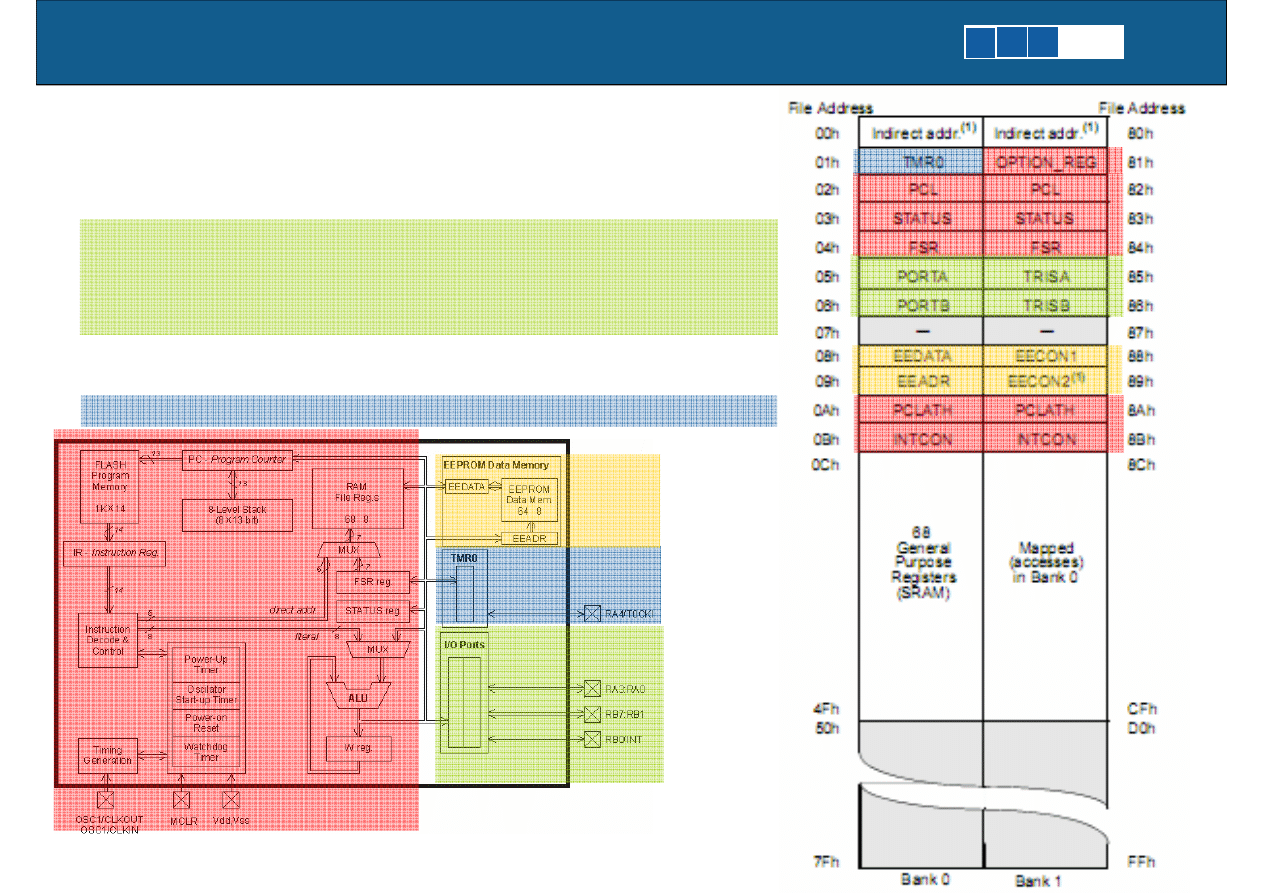

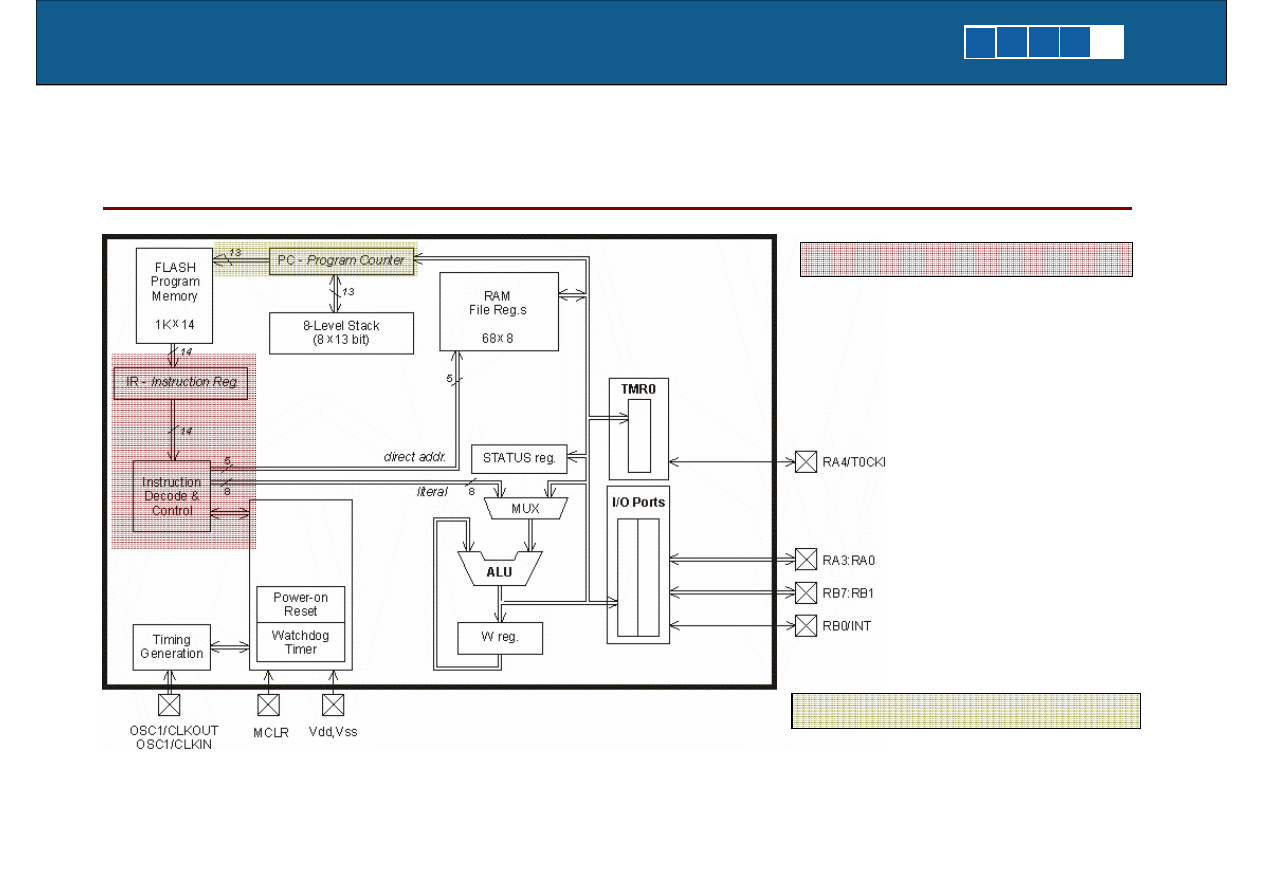

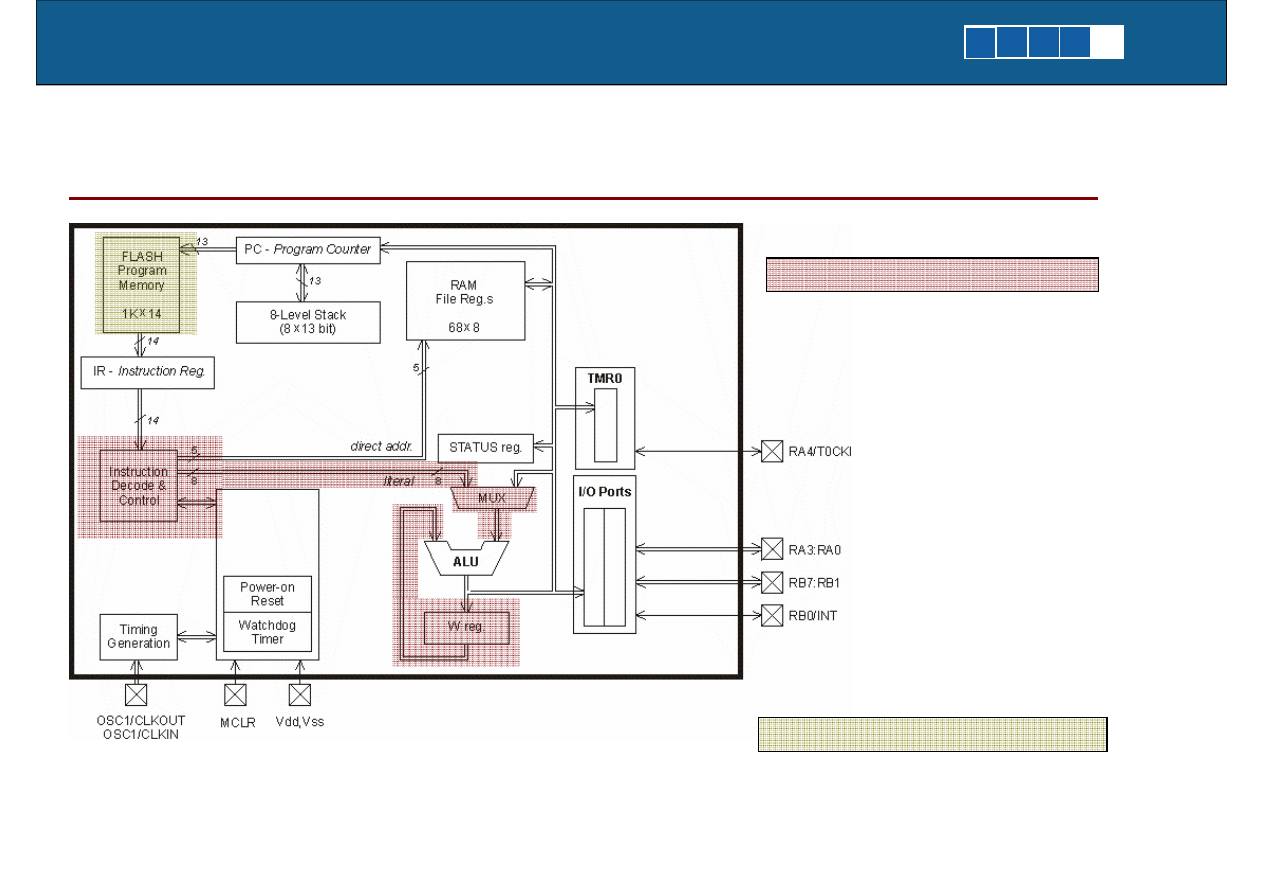

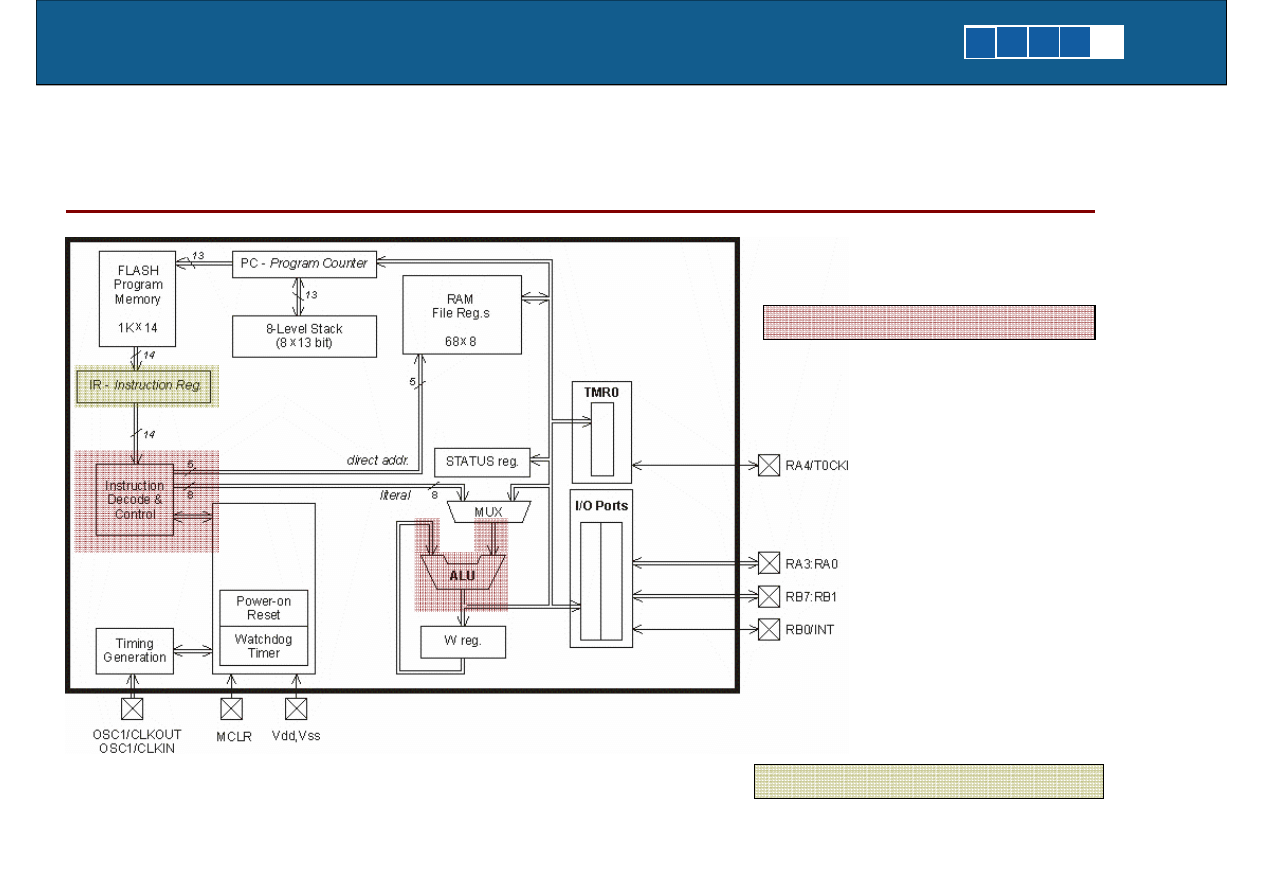

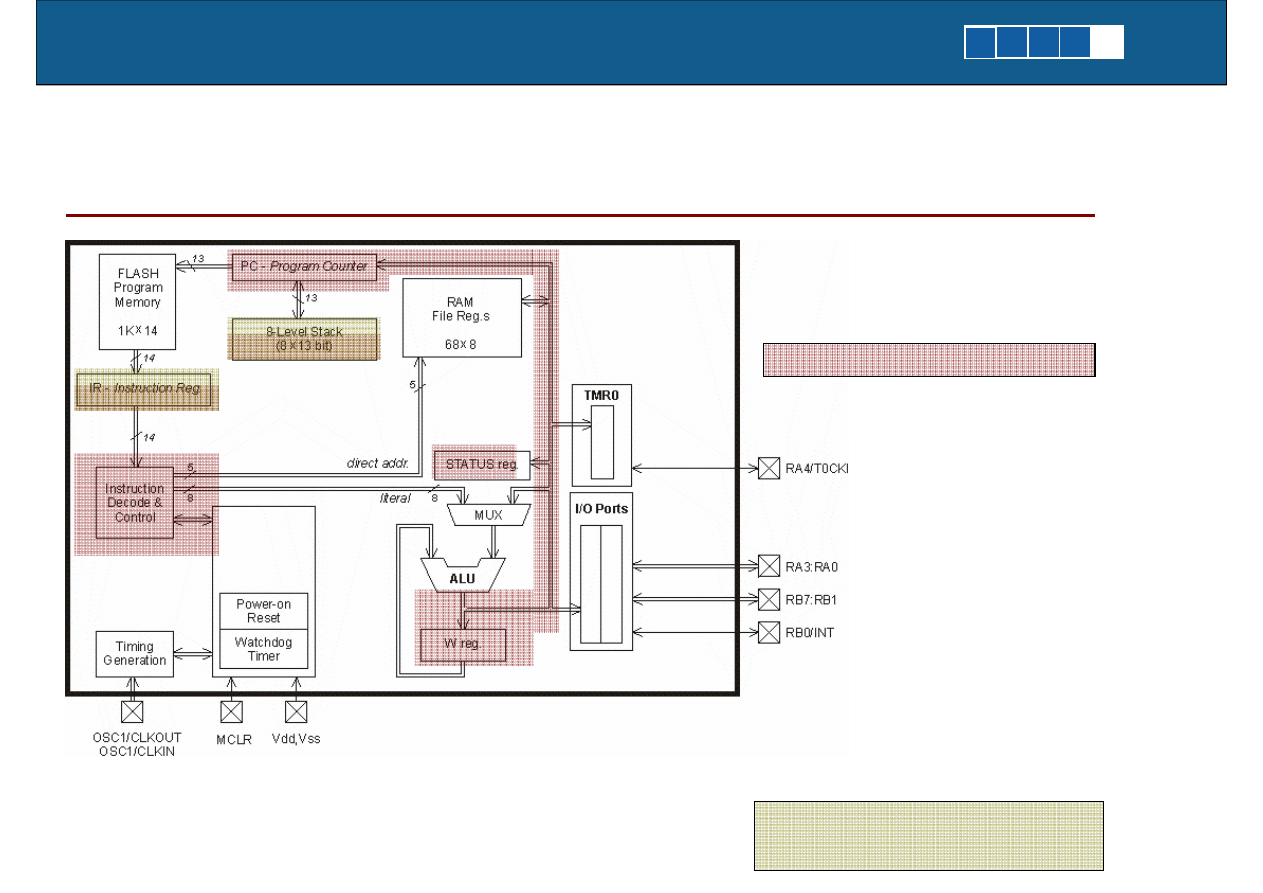

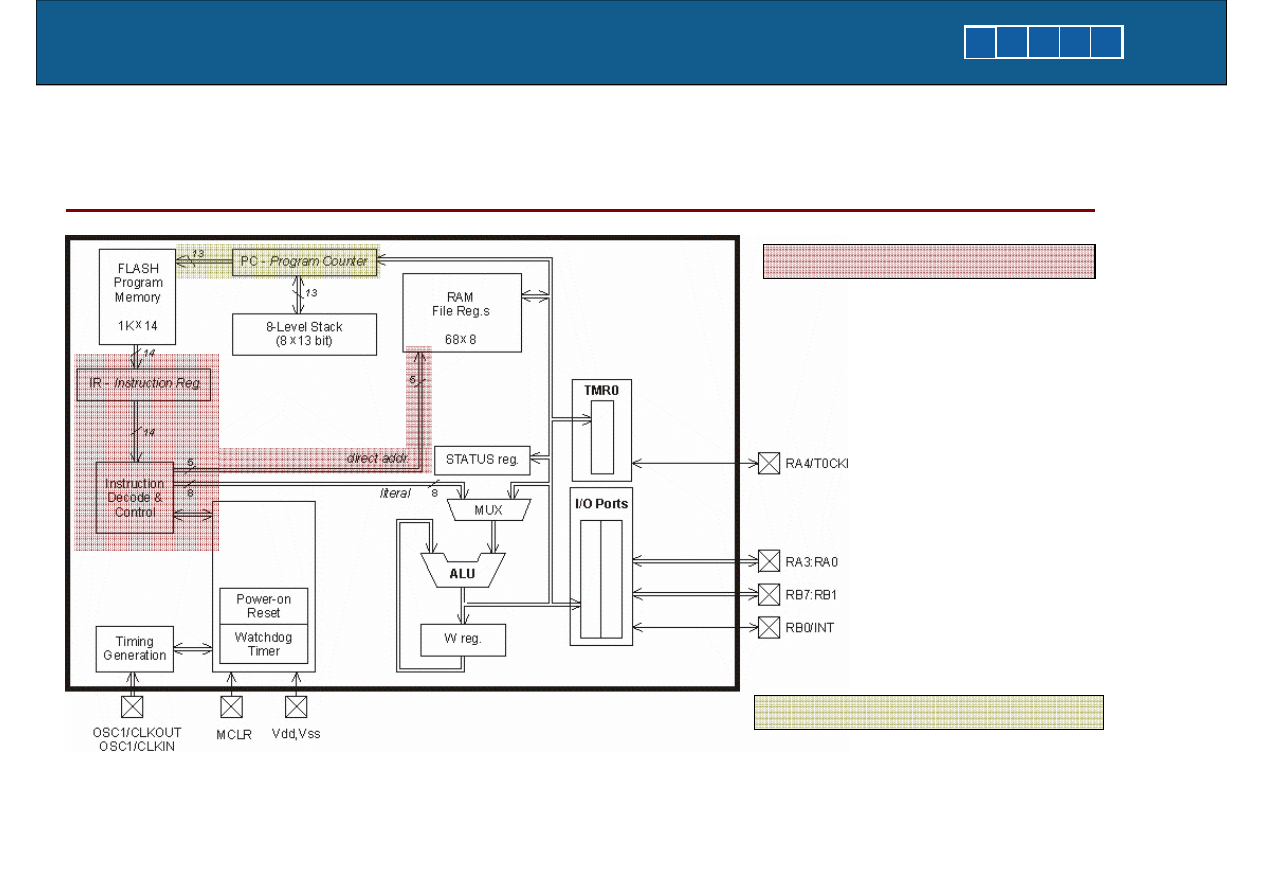

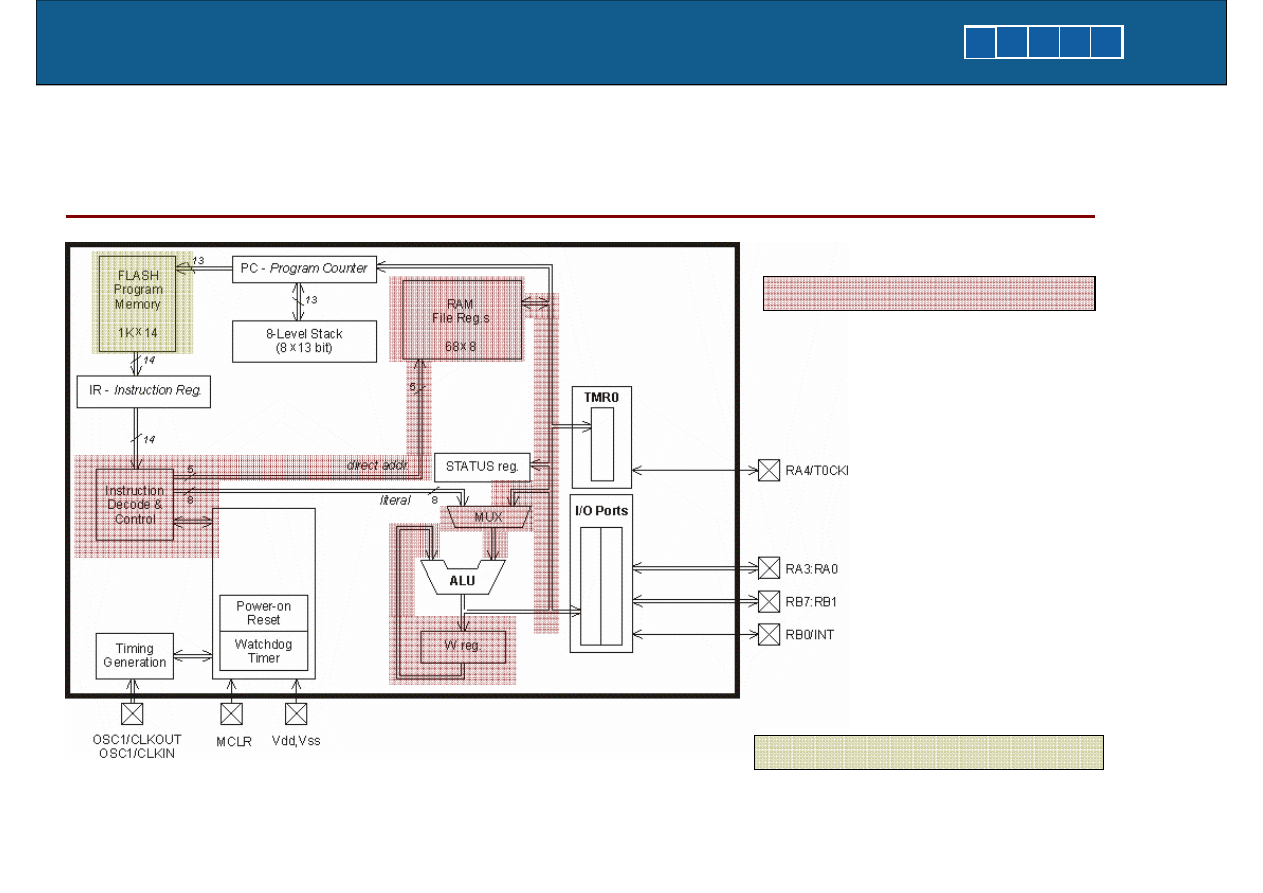

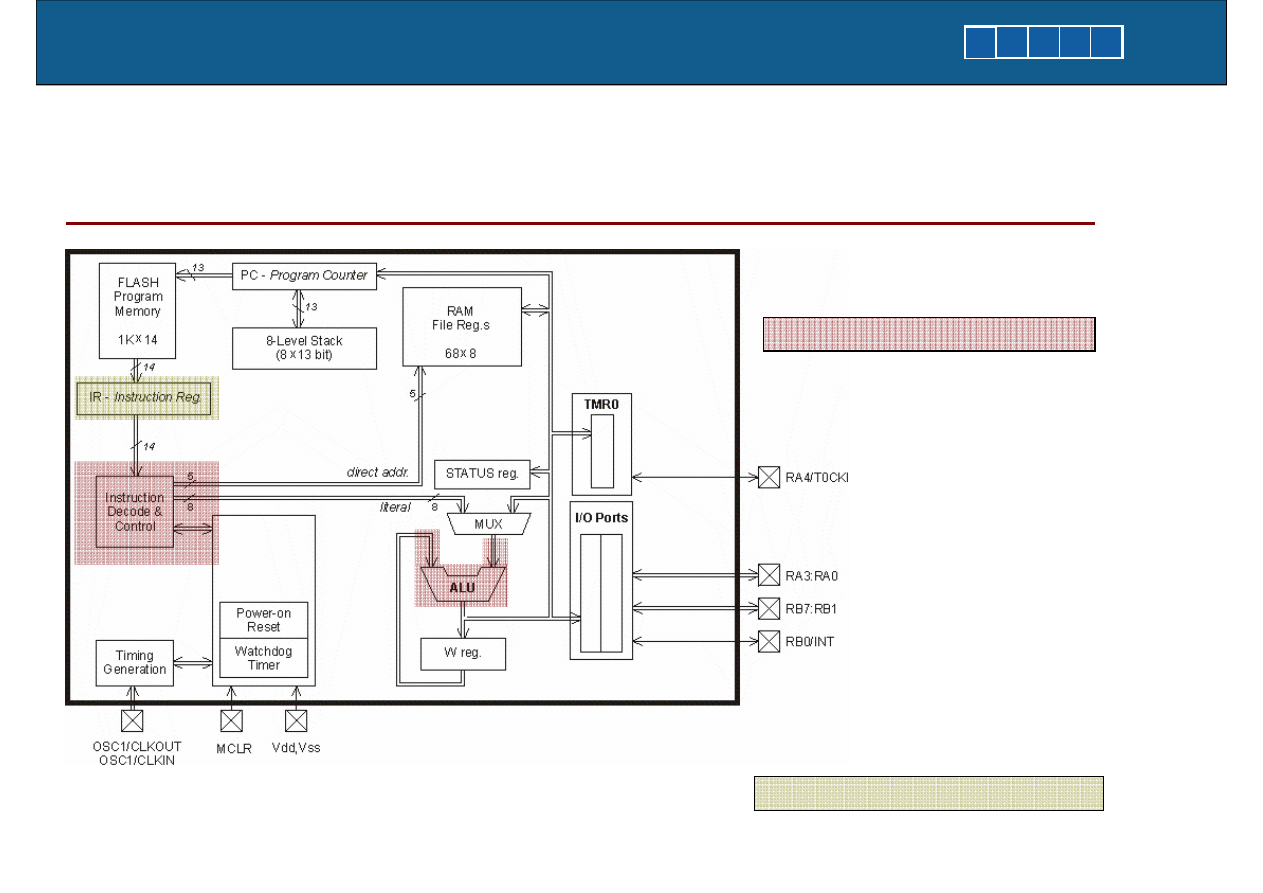

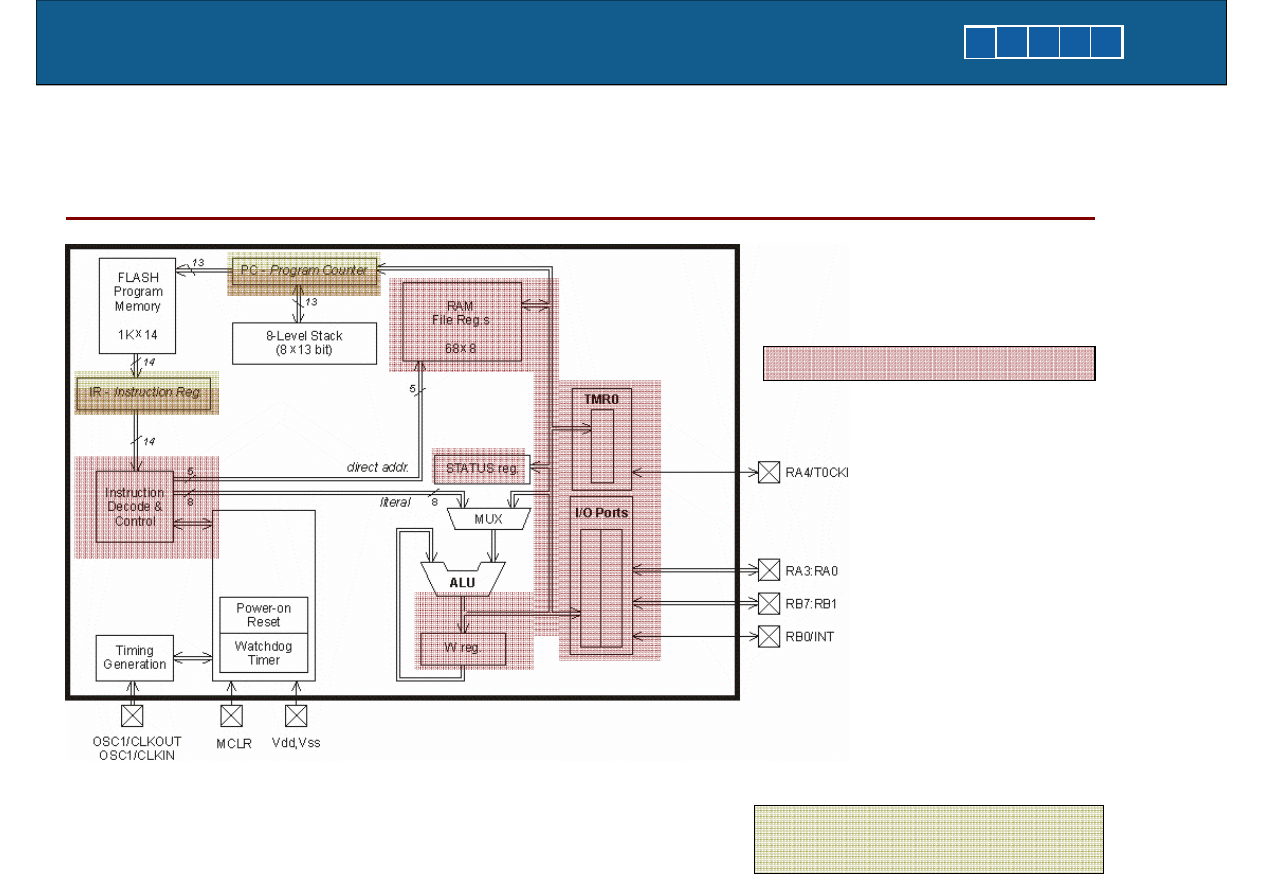

Architektura procesora PIC16F84A

Microchip PIC16F84A

Data Sheet

strona 5

2. Instrukcje procesora

4/24

1

2

3

4

5

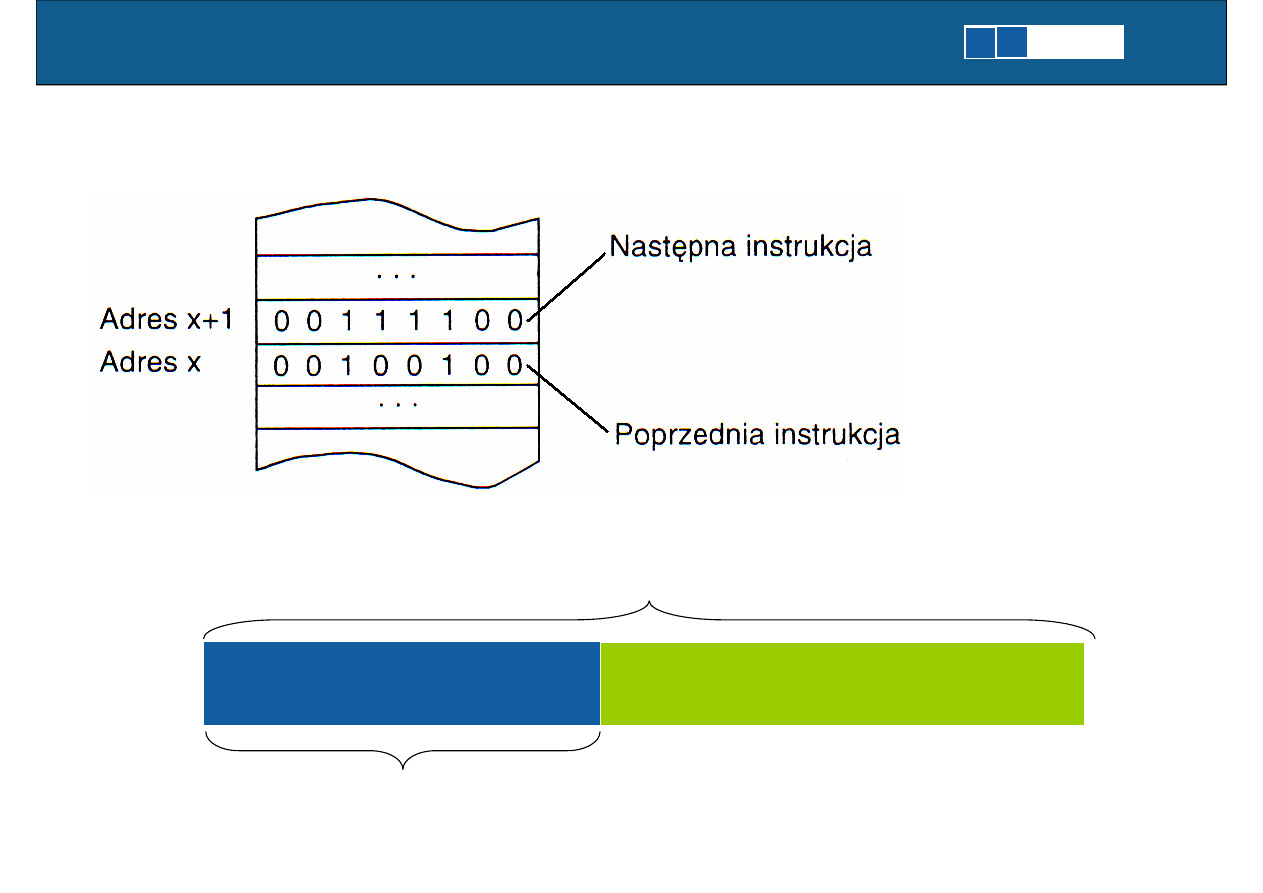

Instrukcja/Operacja

KOD OPERACJI

OPERAND LUB ADRES

INSTRUKCJA

OPERACJA

2. Instrukcje procesora

5/24

1

2

3

4

5

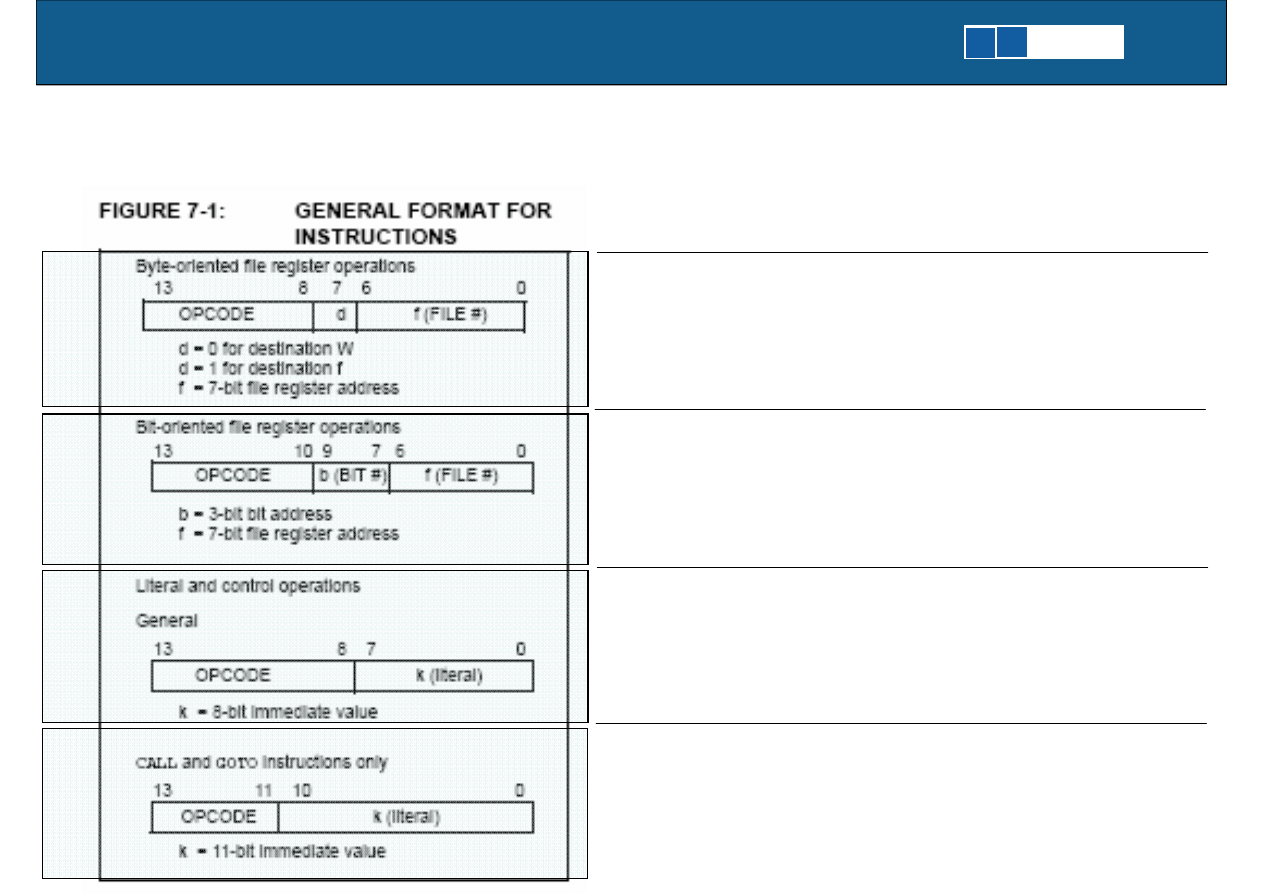

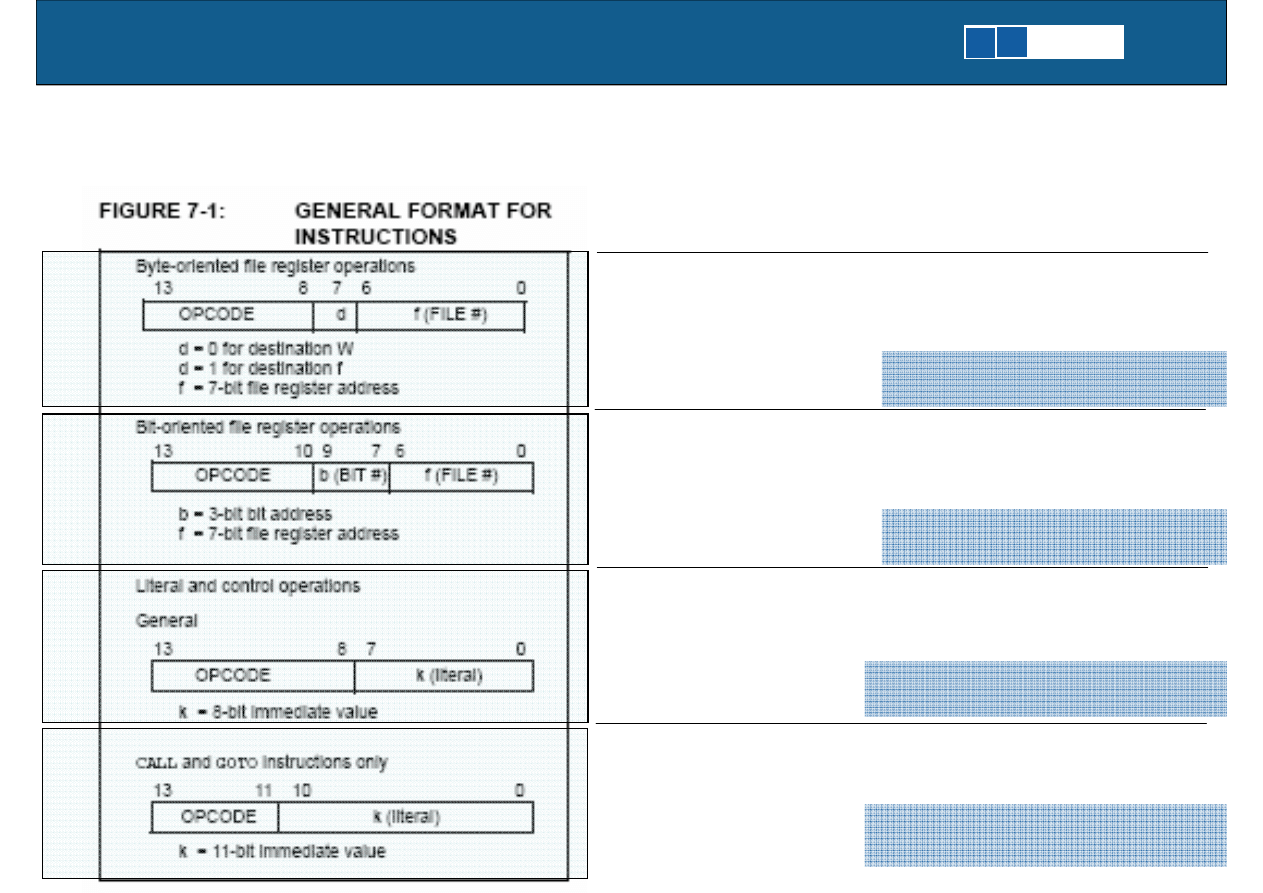

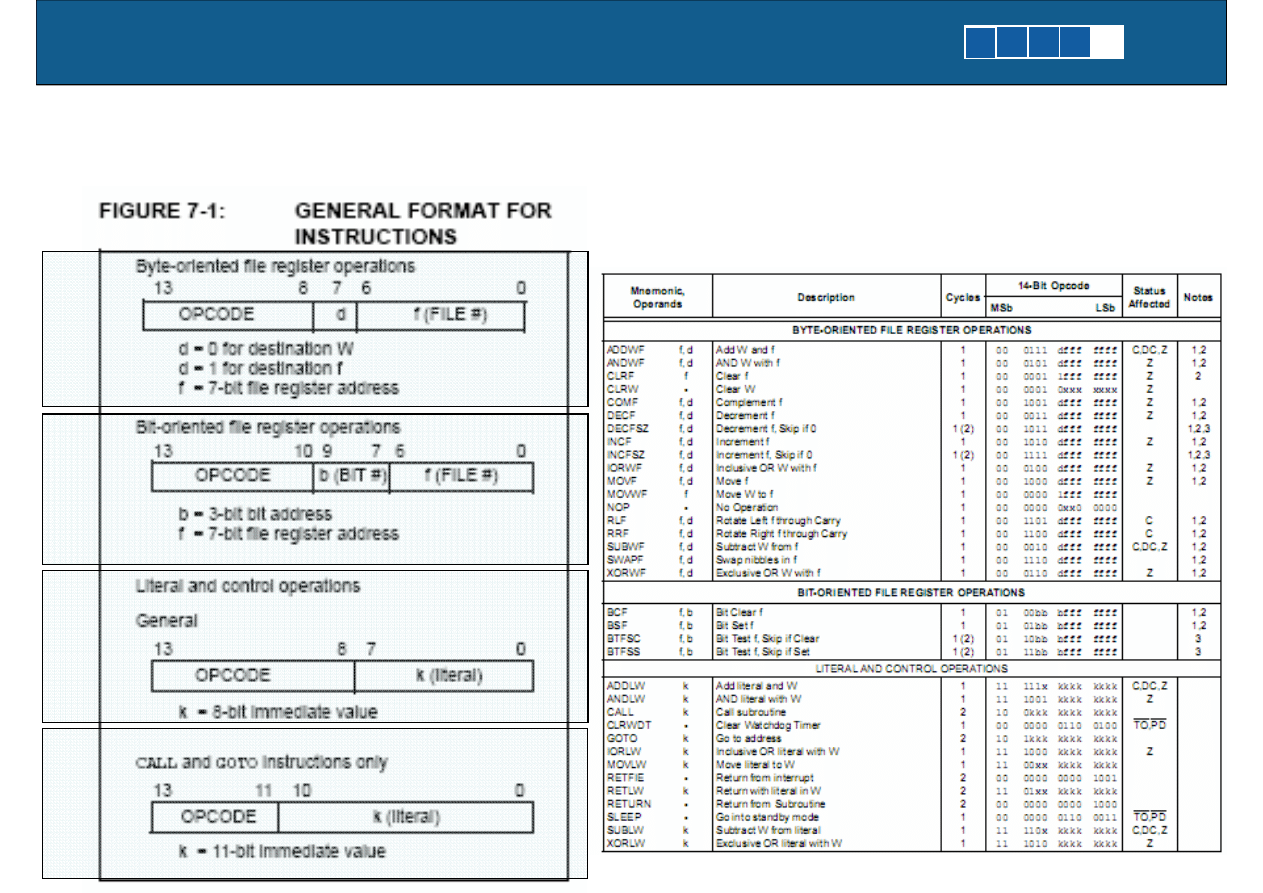

Microchip PIC16F84A

Data Sheet

strona 35

3

2

1

4

Format instrukcji

Operacja na rejestrze o podanym w instrukcji

adresie

Operacja na pojedyńczym bicie rejestru o

podanym w instrukcji adresie

Operacja na stałej

Sterowanie wykonaniem programu (zmiany PC)

ADDWF, ANDWF, XORWF, CLRF, INCF, INCFSZ,

DECF, DECFSZ, MOVWF .......

BCF, BSF, BTFSC, BTFSS

ADDLW, ANDLW, XORLW, MOVLW .......

GOTO, CALL, RETURN, RETLW, RETFIE

2. Instrukcje procesora

6/24

1

2

3

4

5

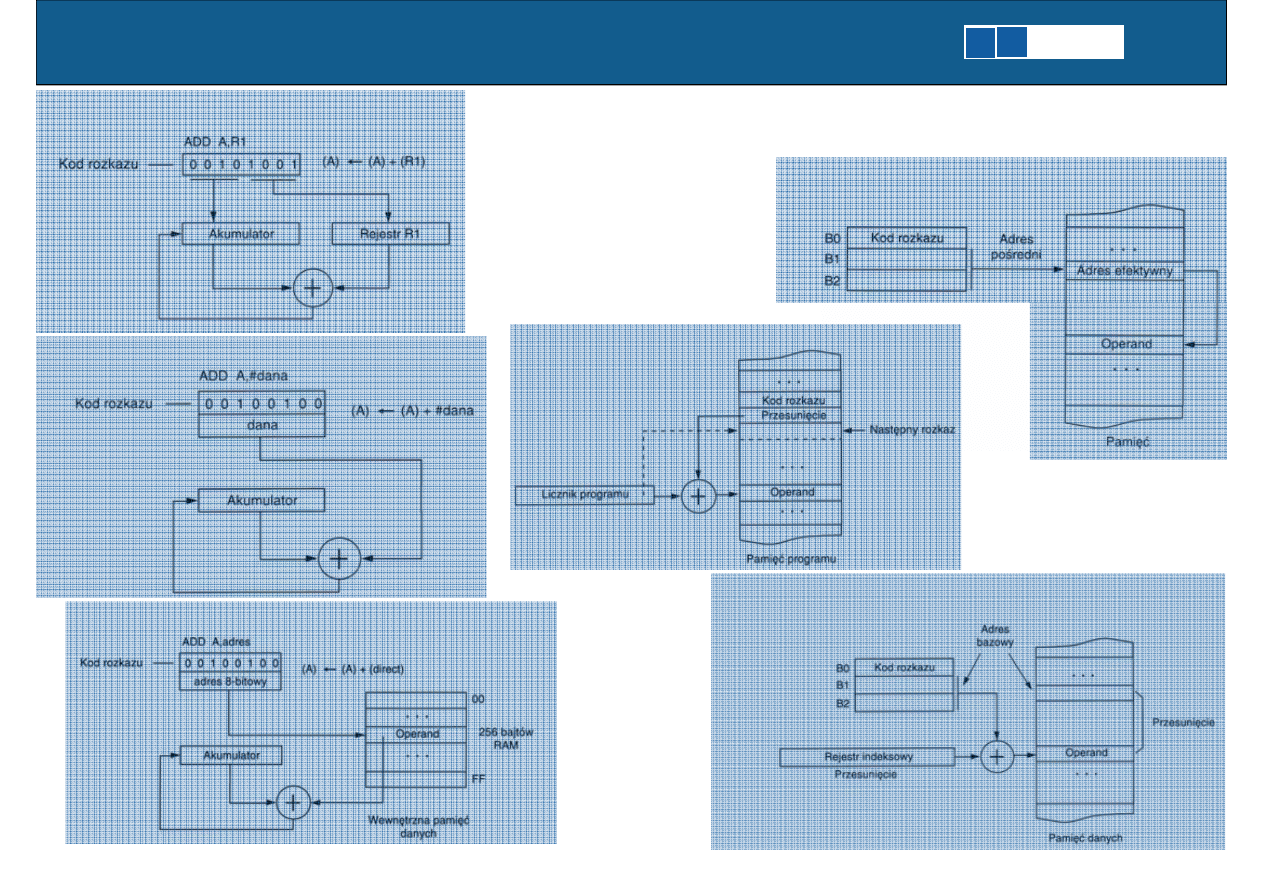

Tryby adresowania

Adresowanie implikowane

Adresowanie natychmiastowe

Adresowanie bezpośrednie

Adresowanie pośrednie

R. Pełka, Mikrokontrolery, architektura, programowanie, zastosowania, WKŁ 2000

Adresowanie indeksowe

Adresowanie

względne

2. Instrukcje procesora

7/24

1

2

3

4

5

3

2

1

4

Operacja na rejestrze o podanym w instrukcji

adresie

Operacja na pojedyńczym bicie rejestru o

podanym w instrukcji adresie

Operacja na stałej

Sterowanie wykonaniem programu (zmiany PC)

ADDWF, ANDWF, XORWF, CLRF, INCF, INCFSZ...

BCF, BSF, BTFSC, BTFSS

ADDLW, ANDLW, XORLW, MOVLW .......

GOTO, CALL, RETURN, RETLW, RETFIE

Adresowanie implikowane

Adresowanie natychmiastowe

Adresowanie bezpośrednie

Adresowanie natychmiastowe

Adresowanie pośrednie

Adresowanie bezpośrednie

Adresowanie pośrednie

Tryby adresowania

2. Instrukcje procesora

8/24

1

2

3

4

5

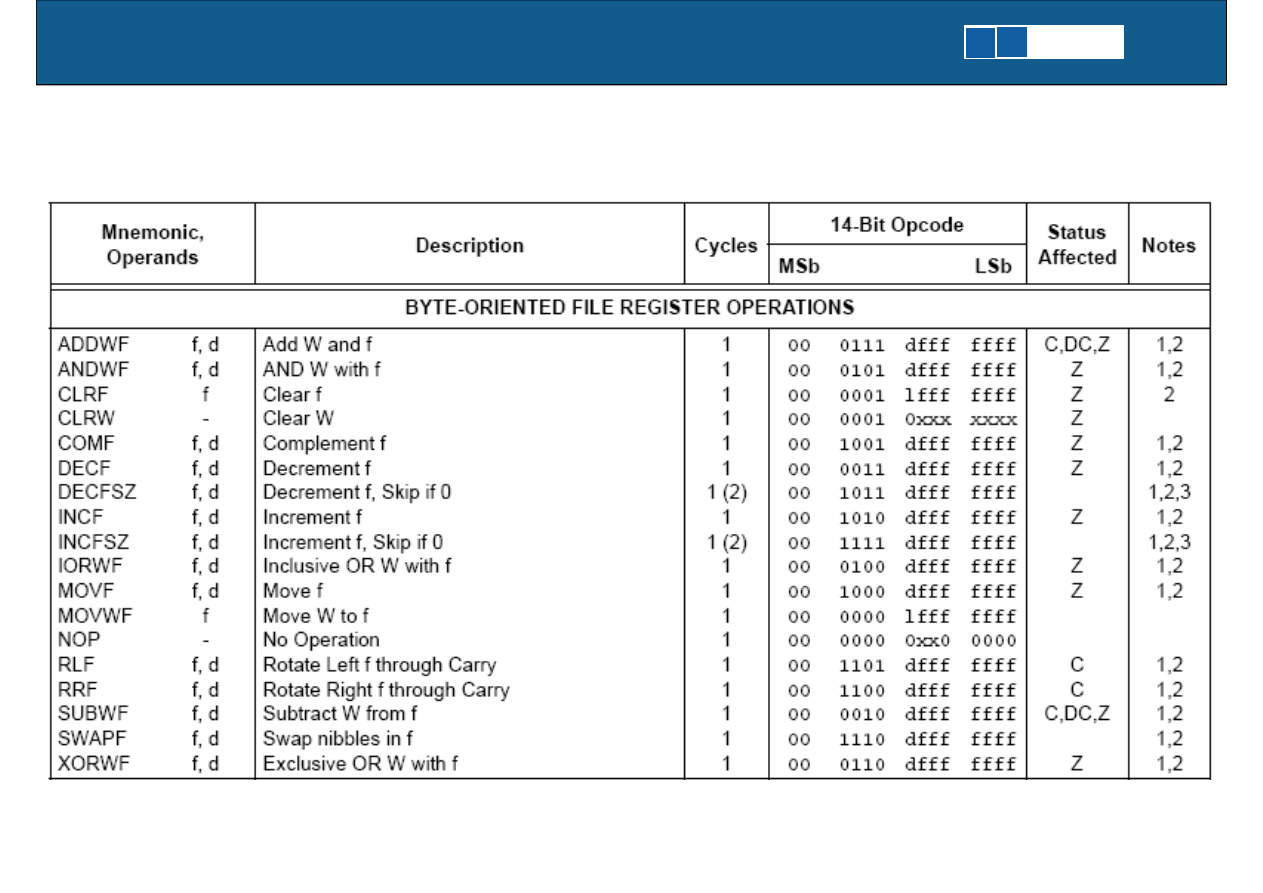

PIC16F84A – instrukcje operujące na rejestrach

2. Instrukcje procesora

9/24

1

2

3

4

5

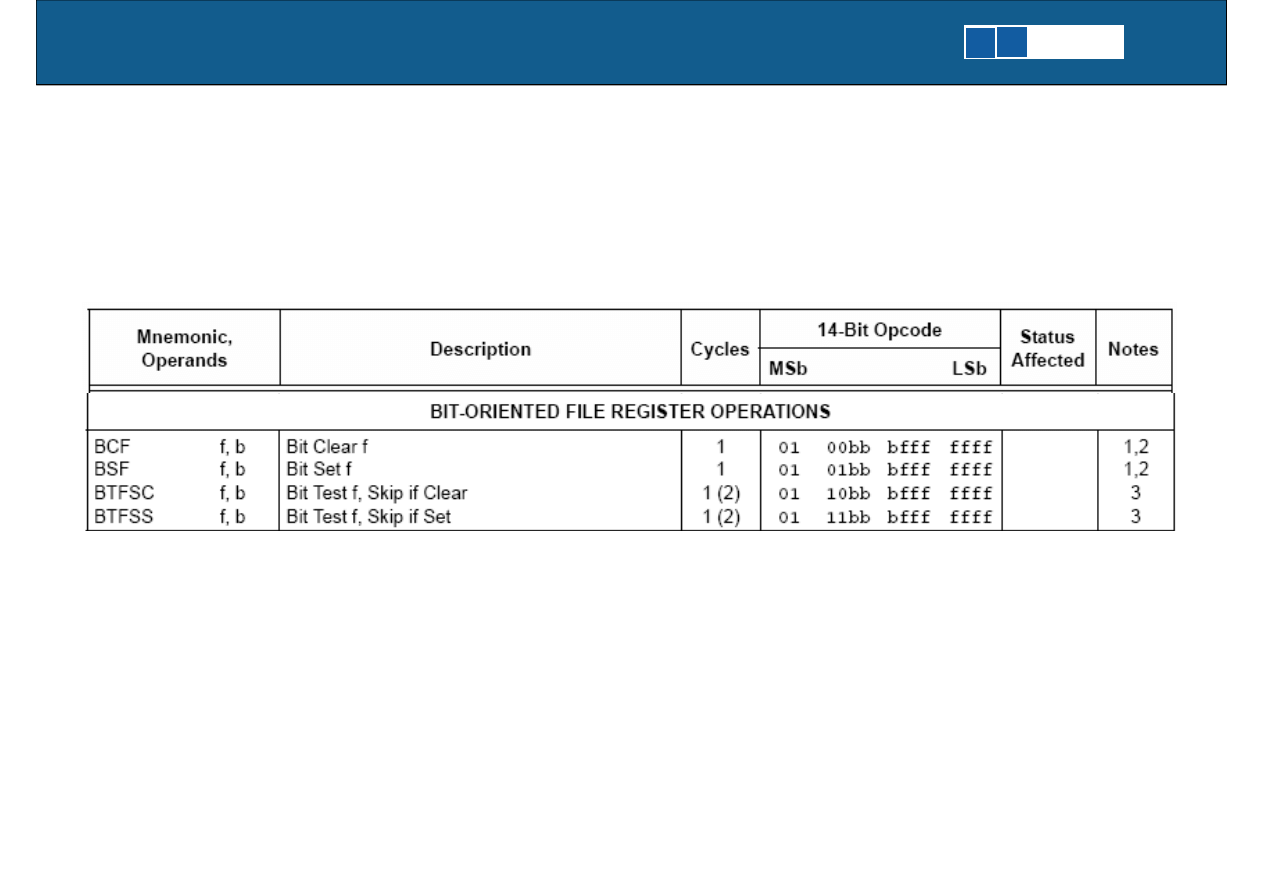

PIC16F84A – instrukcje operujące na bitach rejestru

2. Instrukcje procesora

10/24

1

2

3

4

5

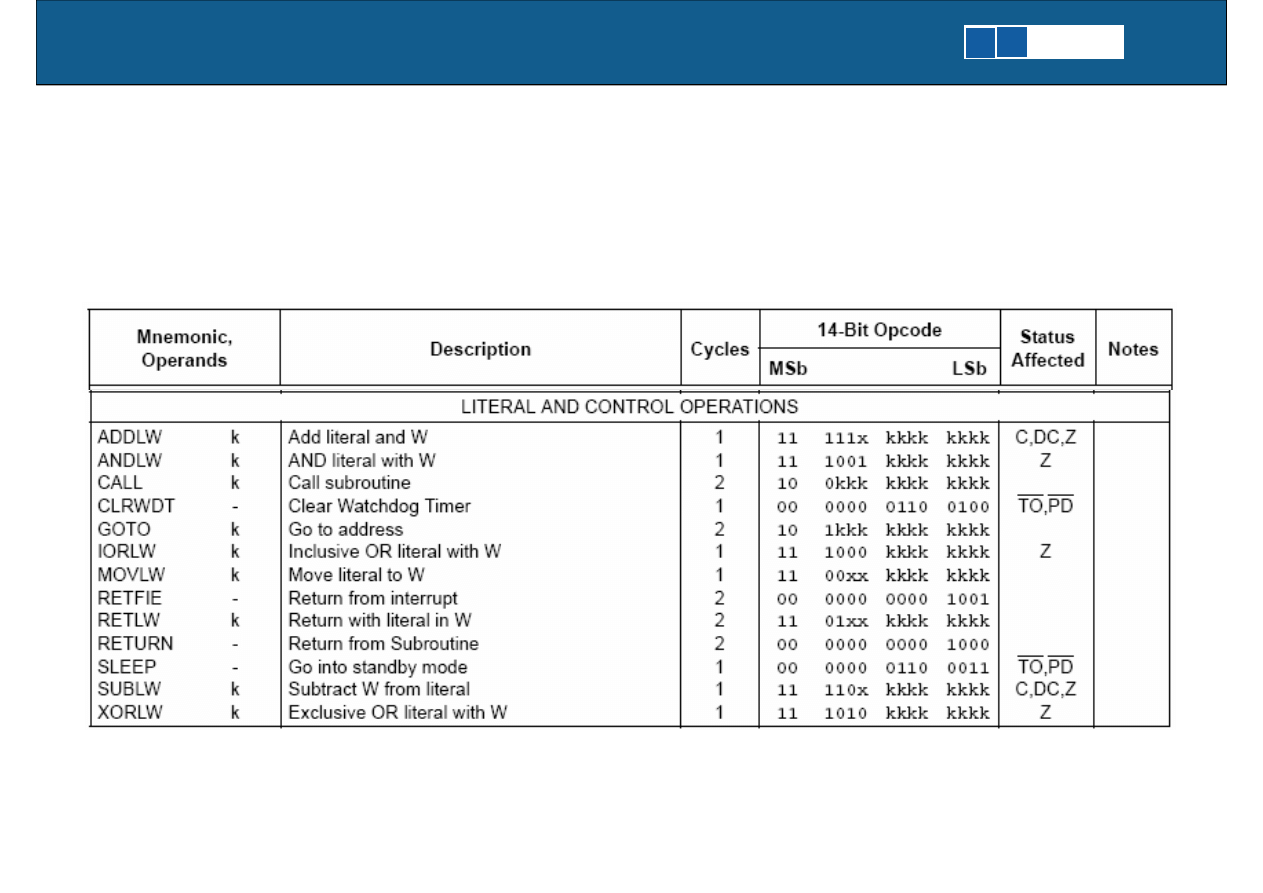

PIC16F84A – instrukcje kontrolne i

operujące na stałych

3. Rejestry procesora

11/24

1

2

3

4

5

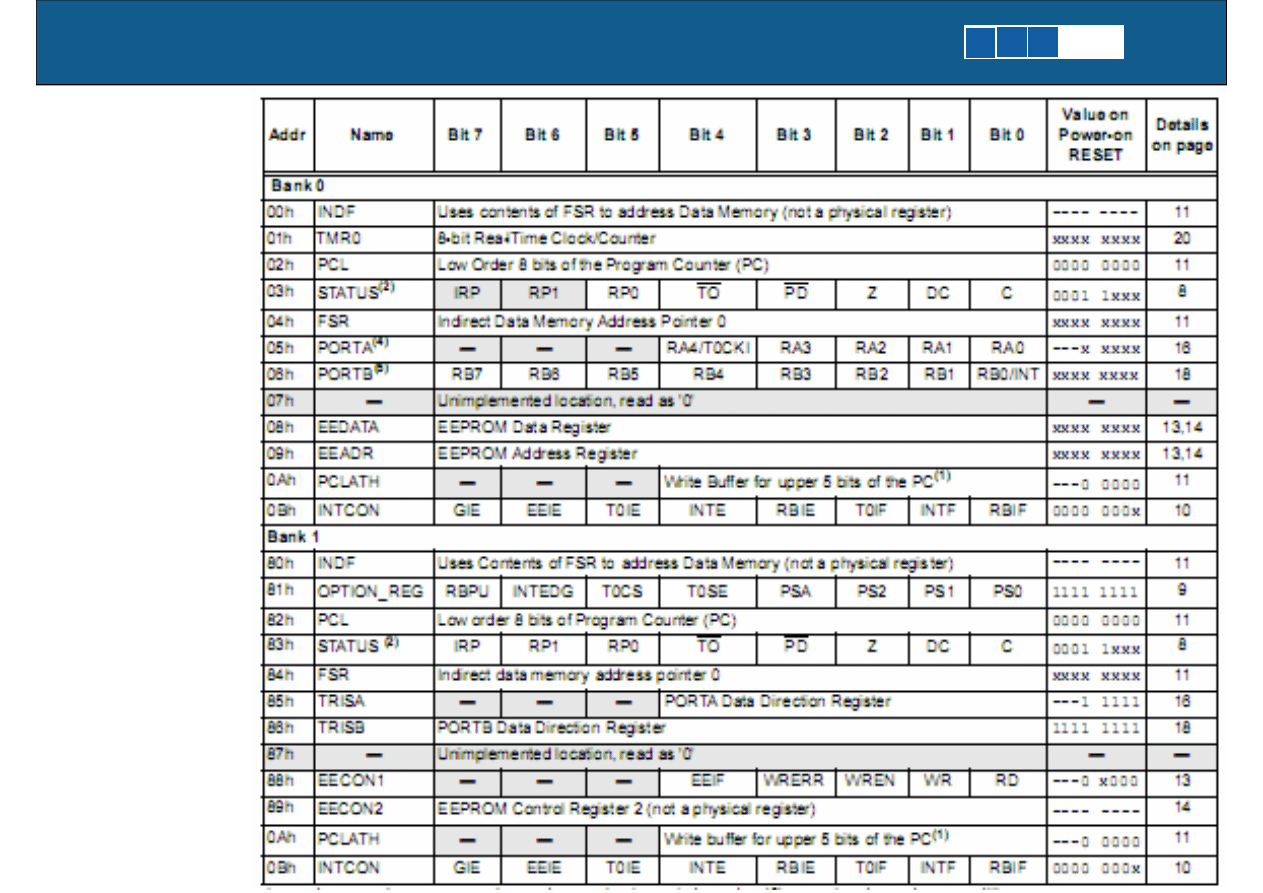

Rejestry procesora

Microchip PIC16F84A

Data Sheet

strona 8

STATUS

PORTA

TRISA

PORTB

TRISB

PCL

PCLATH

TMR0

- rejestr statusu/flag procesora

- reprezentacja stanów linii portu A

- konfiguracja wejść/wyjść na porcie A

- reprezentacja stanów linii portu B

- konfiguracja wejść/wyjść na porcie B

- Młodsze 8 bitów rejestru PC (Program Counter)

- starsza część rejestr PC

- rejestr układu Timera

3. Rejestry procesora

12/24

1

2

3

4

5

Rejestry

procesora

3. Rejestry procesora

13/24

1

2

3

4

5

Mrugająca dioda - przykładowy kod

Animowany GIF

bsf

STATUS, RP0

movlw

0xFE

movwf

TRISA

bcf

STATUS, RP0

Loop:

movlw

0x01

xorwf

PORTA

goto

Loop

TRISA = 0x01;

while(1){

PORTA ^= 0x01;

};

14/24

1

2

3

4

5

4. Mechanizm działania proc. – adr. natychm.

PRZERWA !!!

3

2

1

4

Microchip PIC16F84A

Data Sheet

strona 37

15/24

1

2

3

4

5

4. Mechanizm działania proc. – adr. natychm.

3 i 4 - Operacje na stałych

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

16/24

1

2

3

4

5

4. Mechanizm działania proc. – adr. natychm.

3 i 4 - Operacje na stałych

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

17/24

1

2

3

4

5

4. Mechanizm działania proc. – adr. natychm.

3 i 4 - Operacje na stałych

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

18/24

1

2

3

4

5

4. Mechanizm działania proc. – adr. natychm.

3 i 4 - Operacje na stałych

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

RETLW k

CALL k

GOTO k, RETLW k

GOTO k, RETLW k

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

5. Mechanizm działania proc. – adr. bezpośr.

19/24

1

2

3

4

5

1 i 2 - Operacje na rejestrach

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

5. Mechanizm działania proc. – adr. bezpośr.

20/24

1

2

3

4

5

1 i 2 - Operacje na rejestrach

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

5. Mechanizm działania proc. – adr. bezpośr.

21/24

1

2

3

4

5

1 i 2 - Operacje na rejestrach

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

5. Mechanizm działania proc. – adr. bezpośr.

22/24

1

2

3

4

5

1 i 2 - Operacje na rejestrach

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

DECFZ, BTFSZ

DECFZ, BTFSZ

5. Mechanizm działania proc. – adr. bezpośr.

23/24

1

2

3

4

5

Polecana literatura

1) R. Pełka, Mikrokontrolery, architektura, programowanie, zastosowania, WKŁ 2000

2) Microchip, PIC16F84A Data Sheet

Rozdział 2. Budowa i zasada działania mikrokontrolera

strony 15 - 29

3) W. Stallings, Organizacja i architektura systemu komputerowego, WNT 2003

Rozdział 9, 10, 11, str 368-496

4) J. Stokes, Inside the Machine, No Starch Press, 2007

Rozdział 2,3. The Mechanics of Program Execution,

Pipelined Execution strony 19 - 58

14 stron

44 stron

128 stron

39 stron

5. Mechanizm działania proc. – adr. bezpośr.

24/24

1

2

3

4

5

KONIEC

dr inż. Mariusz Kapruziak

mkapruziak@wi.ps.pl

pok. 107, tel. 449 55 44

Wyszukiwarka

Podobne podstrony:

ASK 02 PawelKopec AdrianMakuch

ASK 02 PawelKopec AdrianMakuch

ASK 02 arch x86

ASK 02 PiotrGębala MateuszMacięga

ASK 02 Kernel

ASK 02 Kernel

02 ASK Harmonogram referatów 2012

Wyk 02 Pneumatyczne elementy

02 OperowanieDanymiid 3913 ppt

02 Boża radość Ne MSZA ŚWIĘTAid 3583 ppt

OC 02

PD W1 Wprowadzenie do PD(2010 10 02) 1 1

więcej podobnych podstron