Funkcjonowanie procesora

1/41

Funkcjonowanie

procesora, instrukcja,

tryby adresowania i x86

1. Powtórka

2/41

1

2

3

4

5

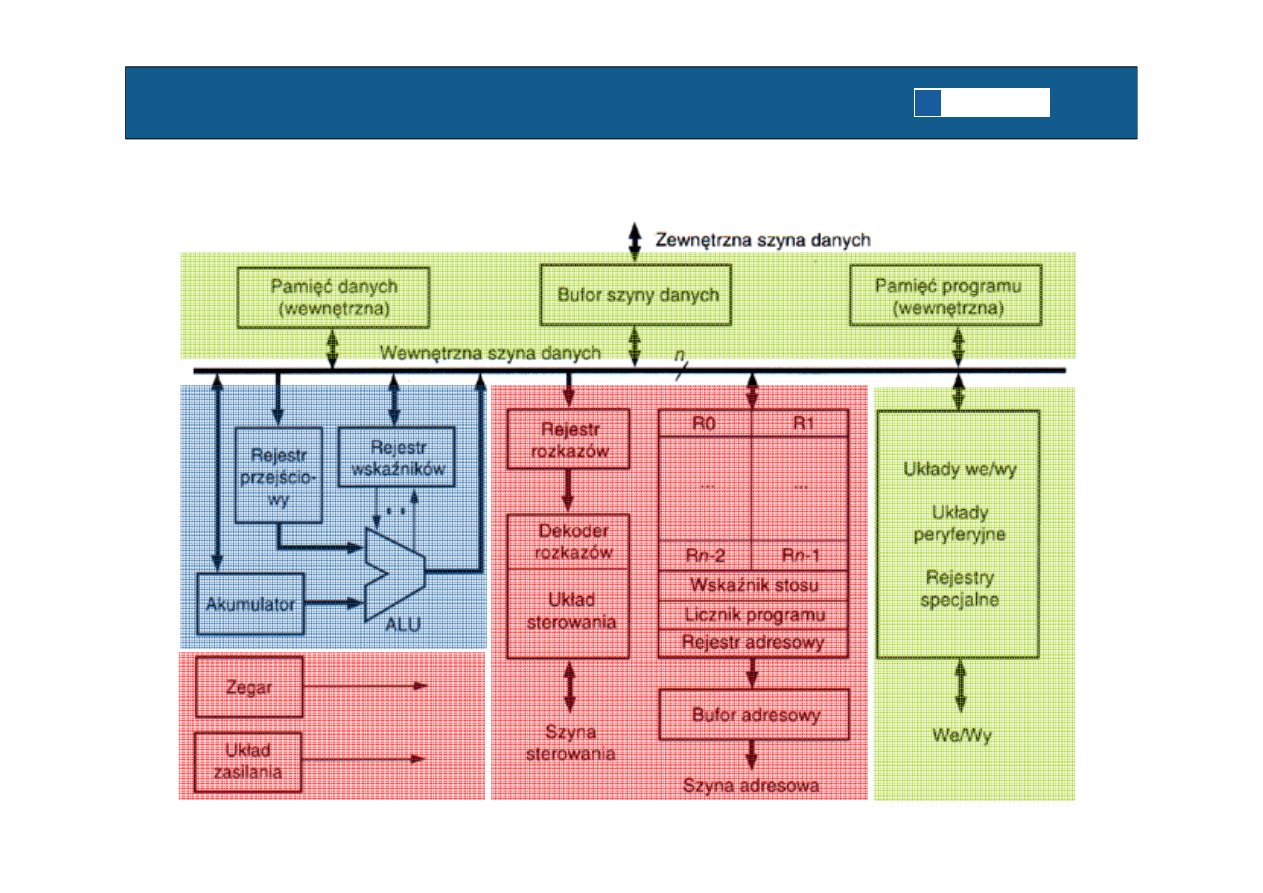

Architektura von Neumanna

1. Powtórka

3/41

1

2

3

4

5

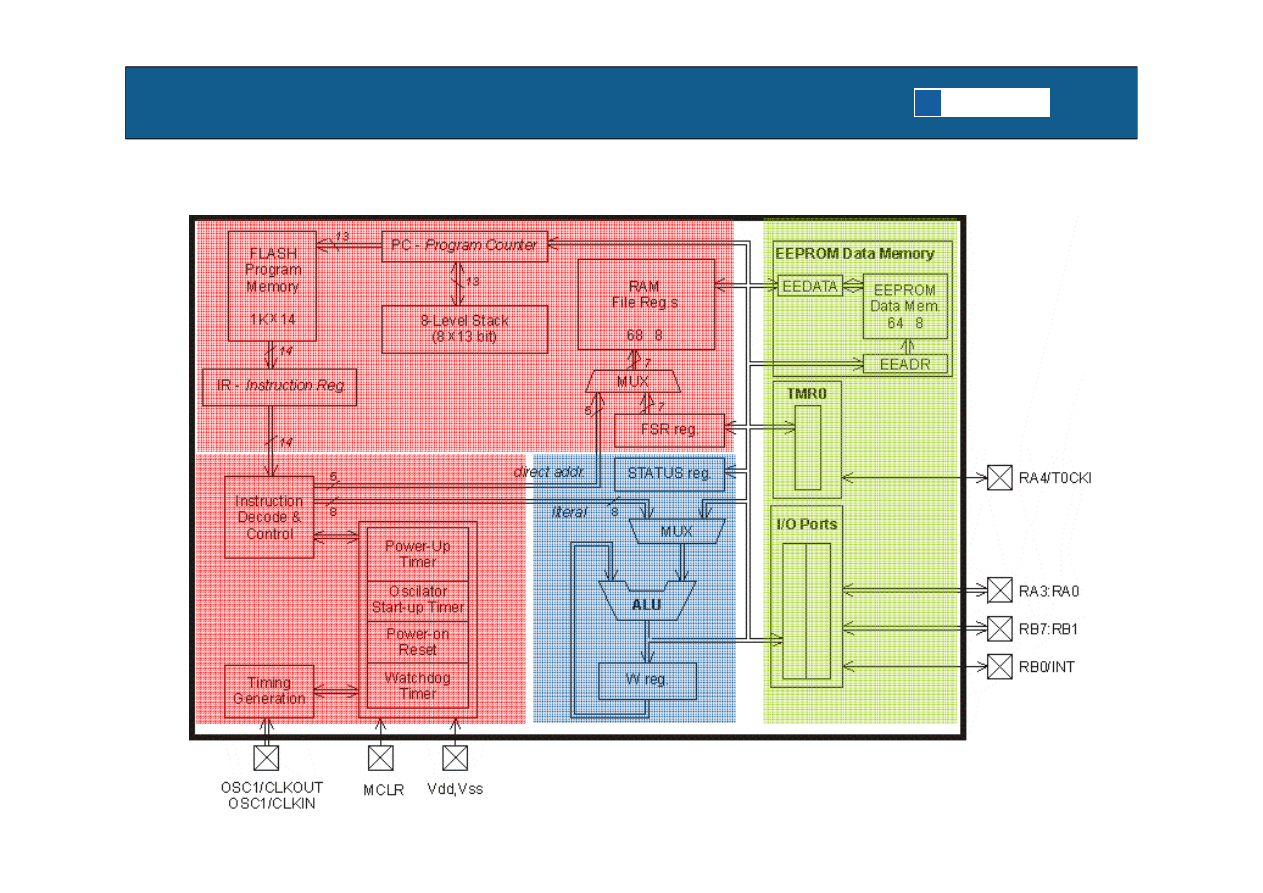

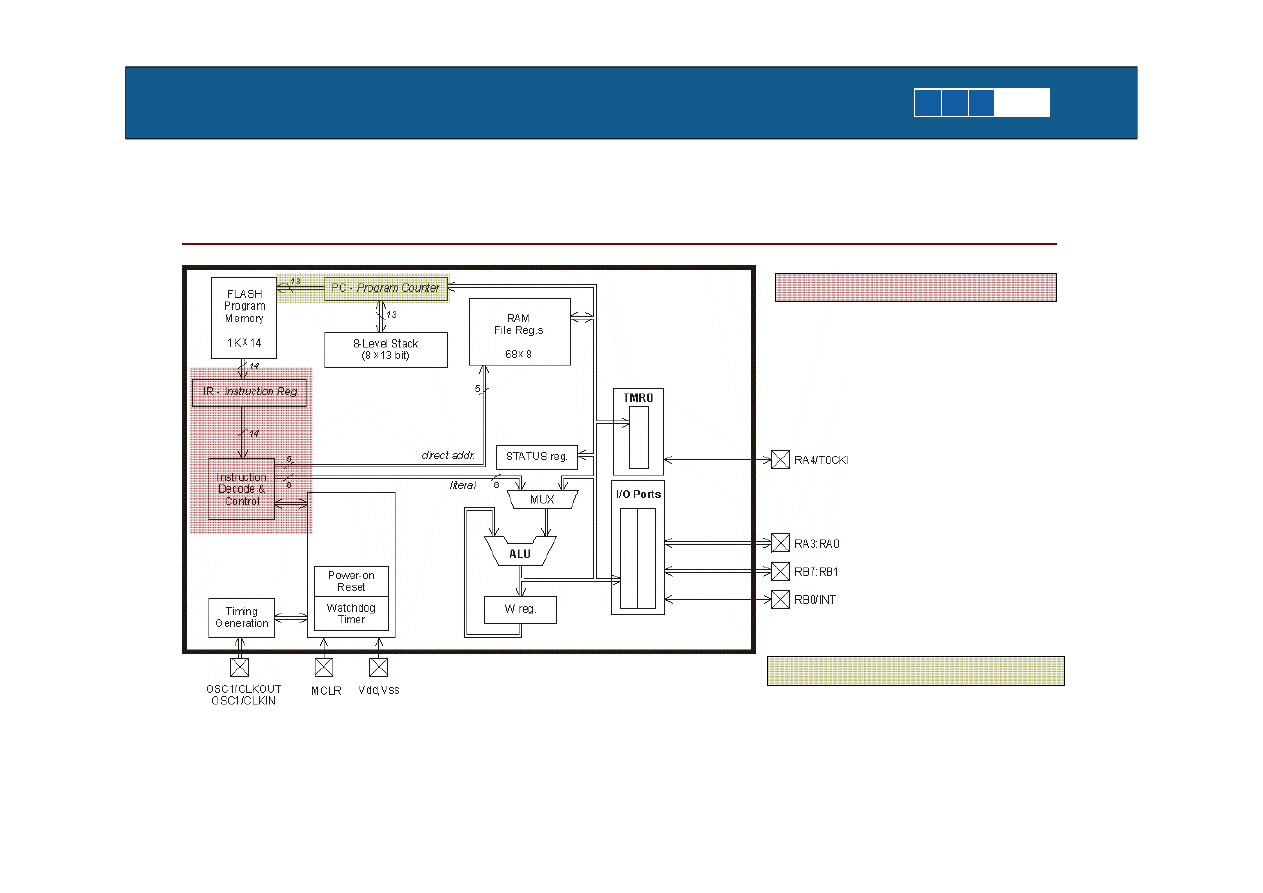

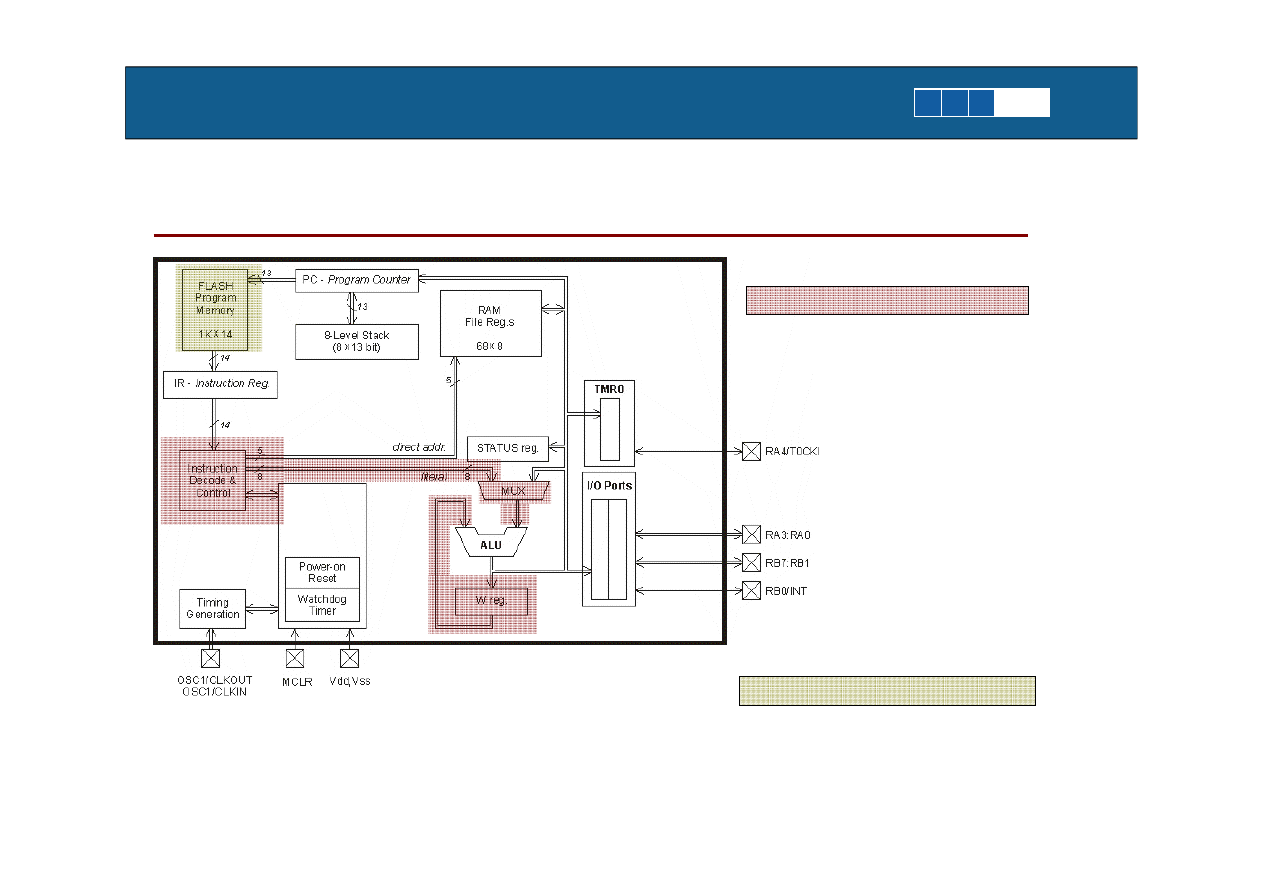

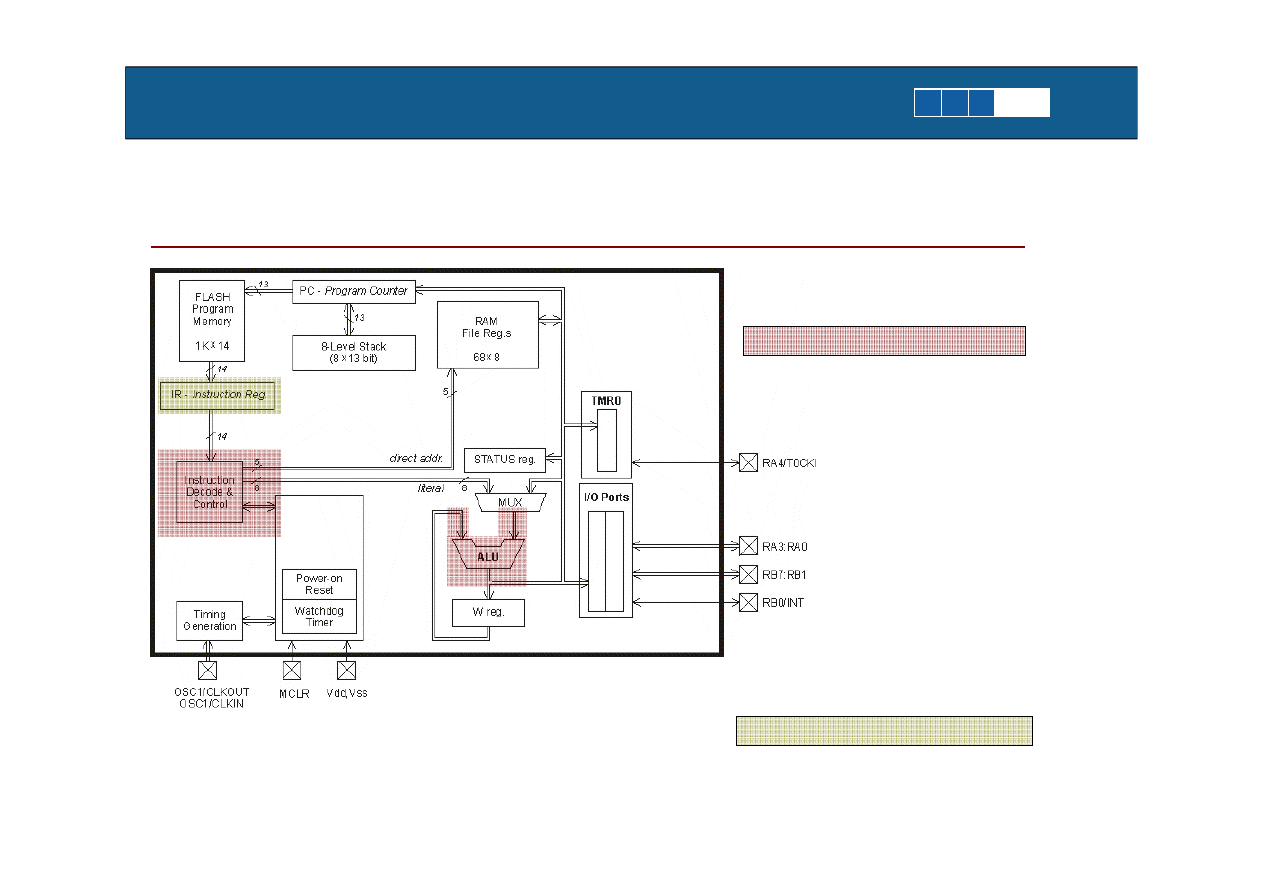

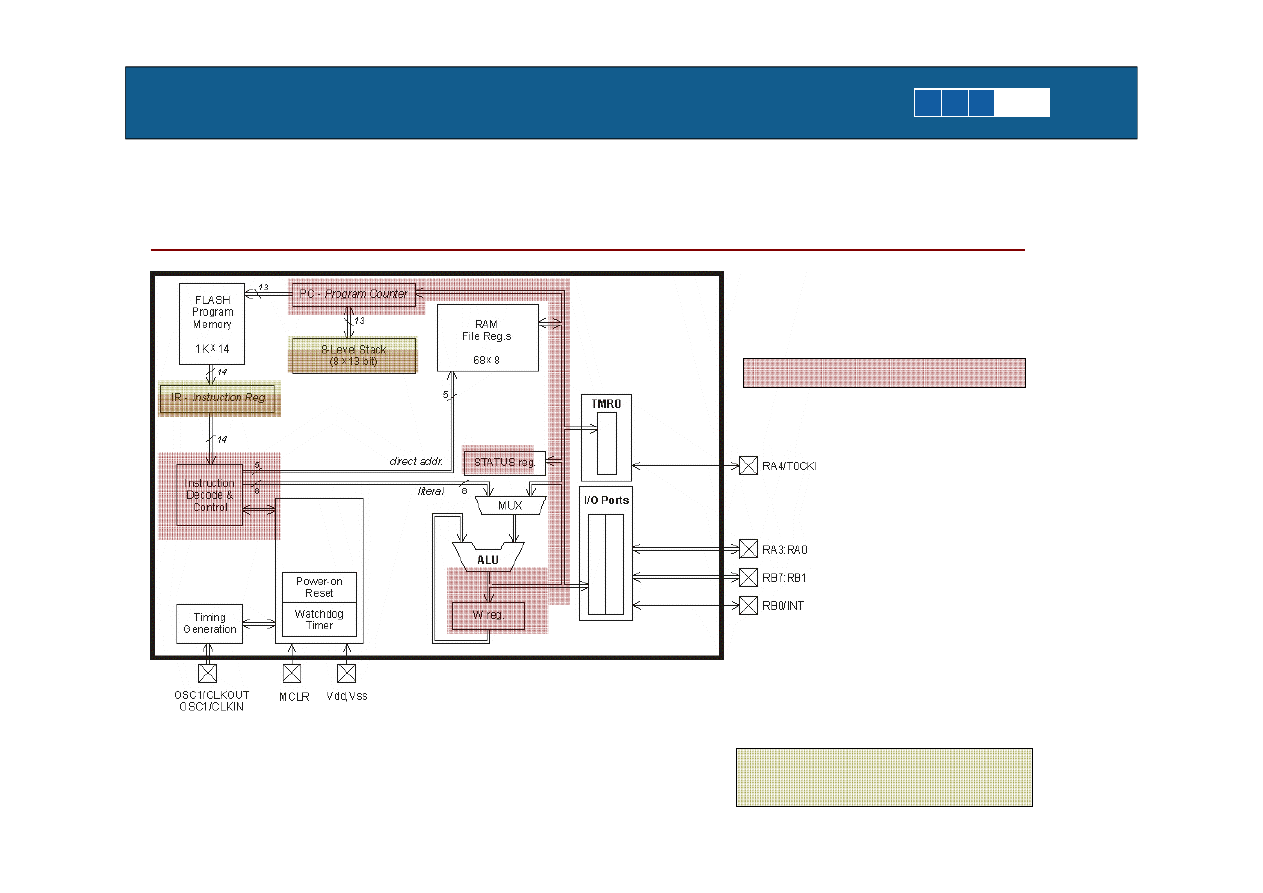

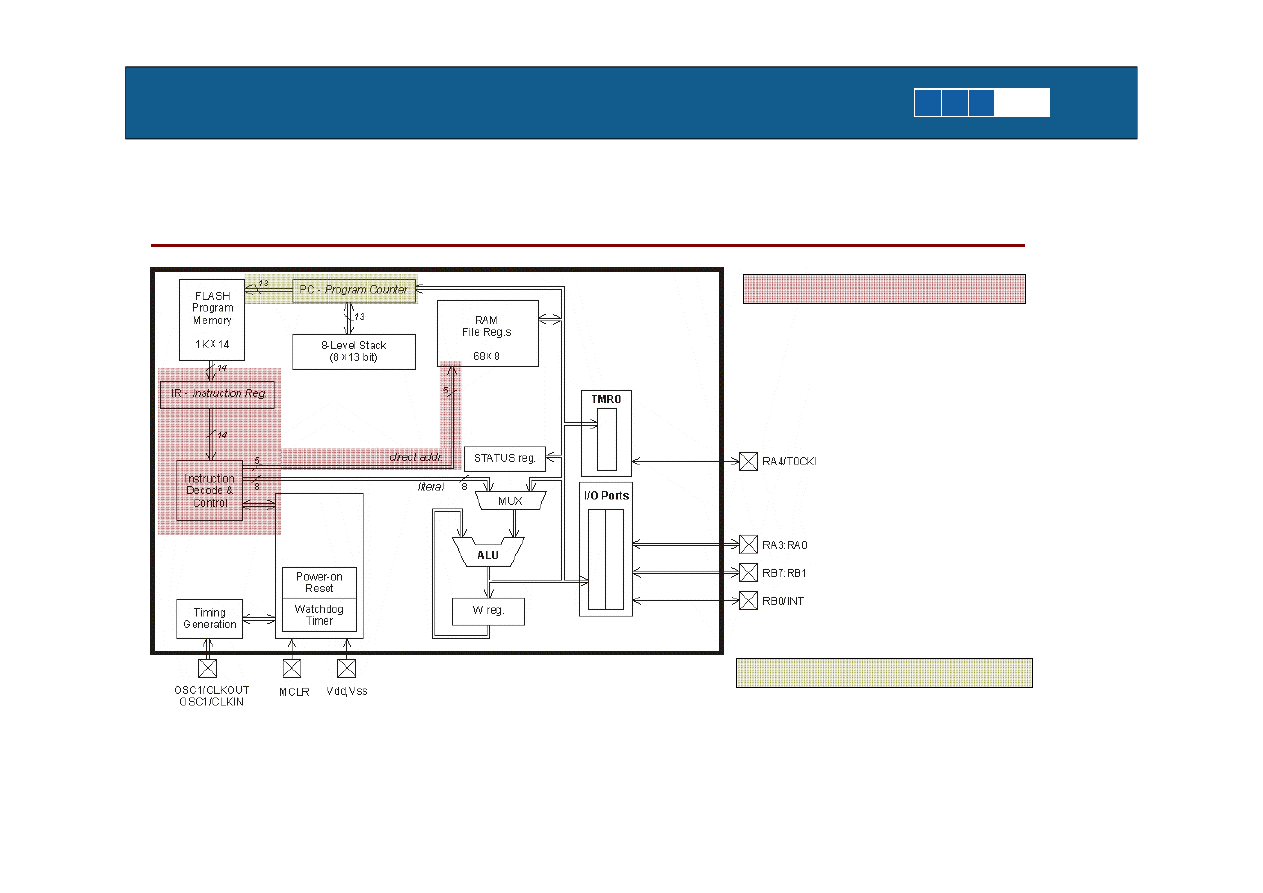

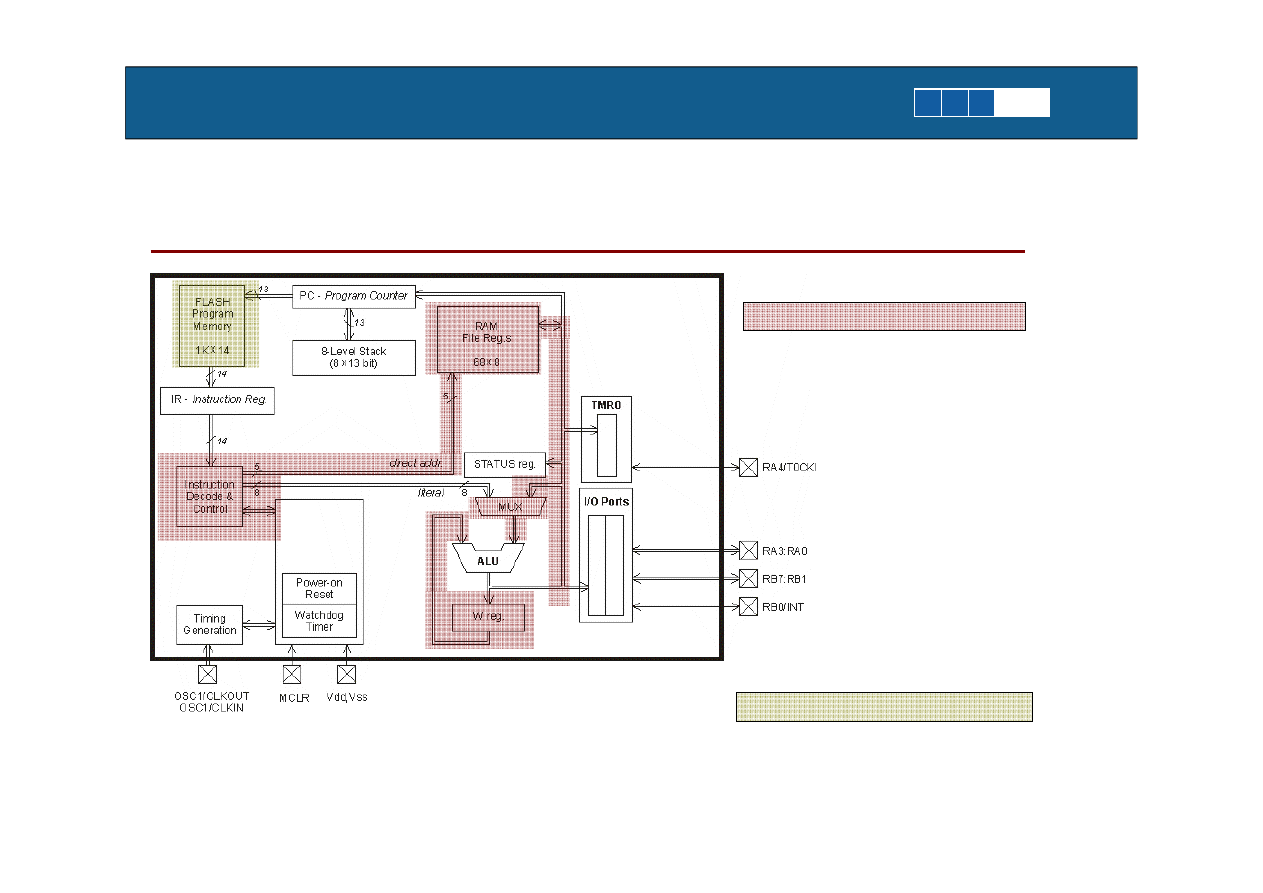

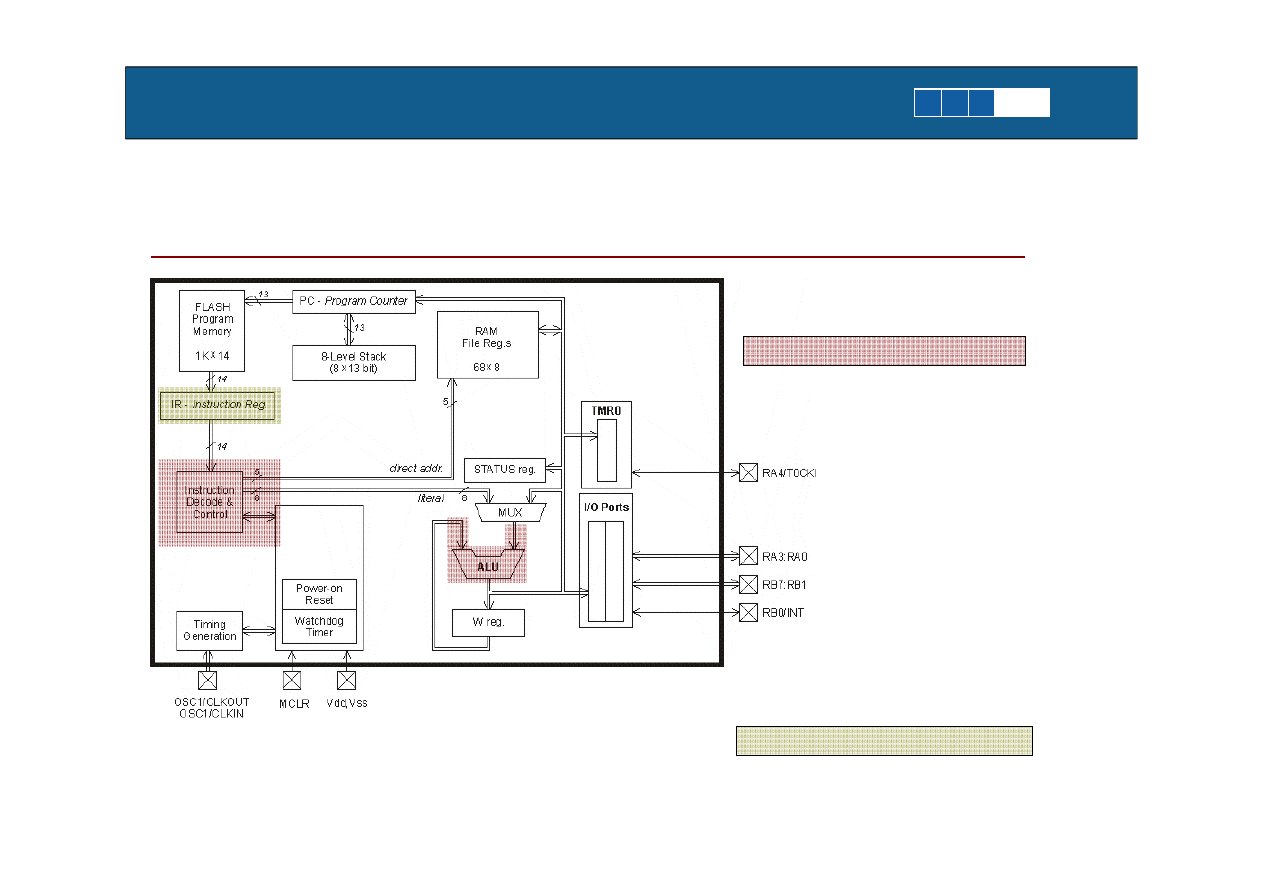

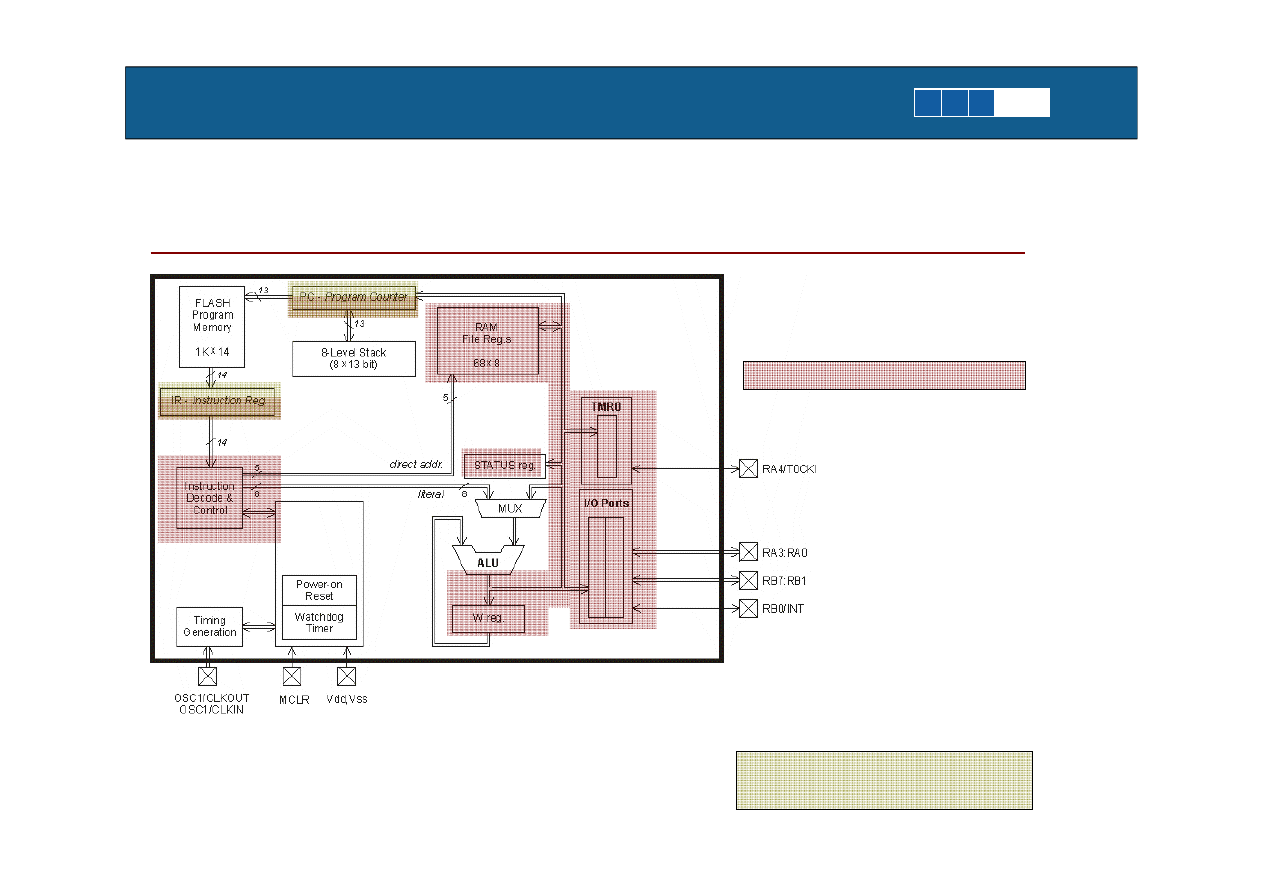

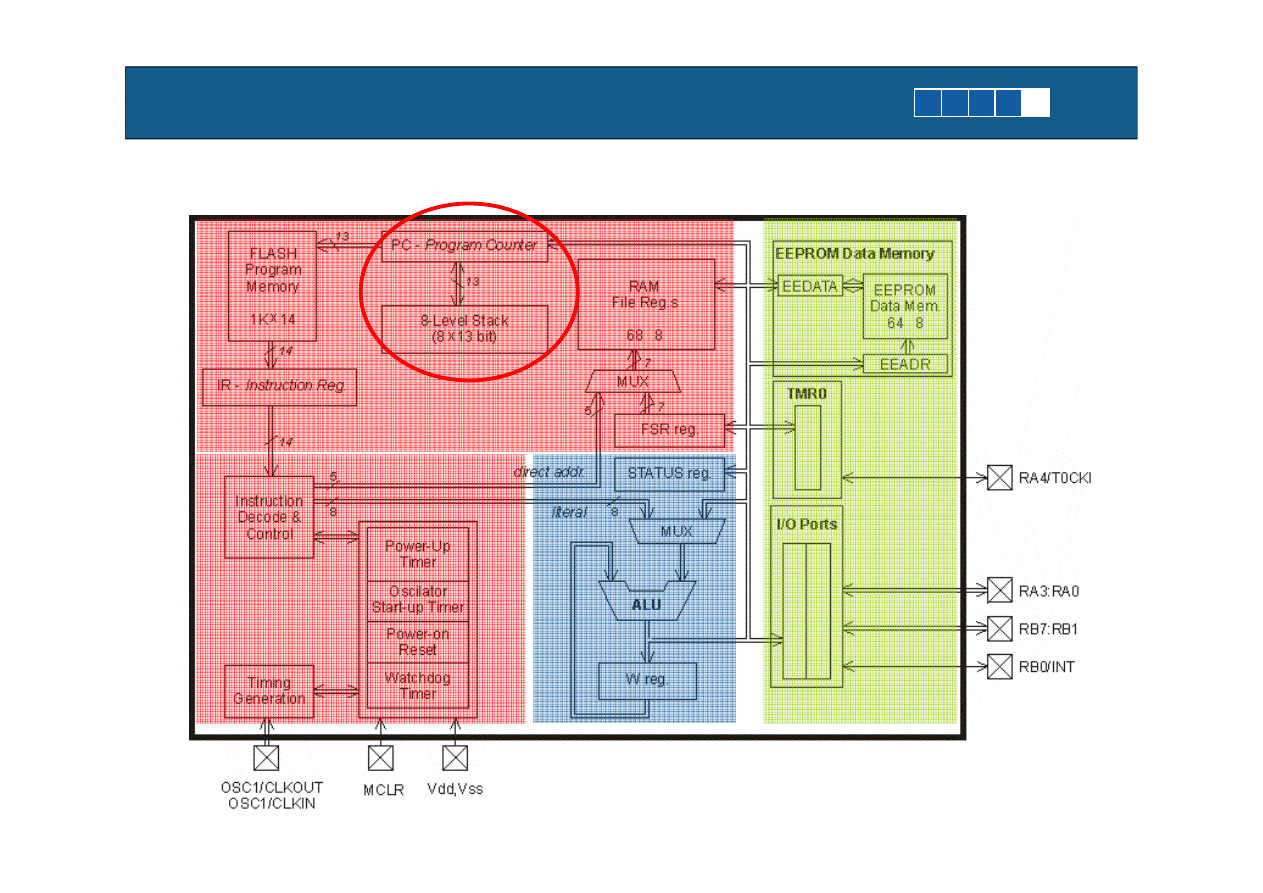

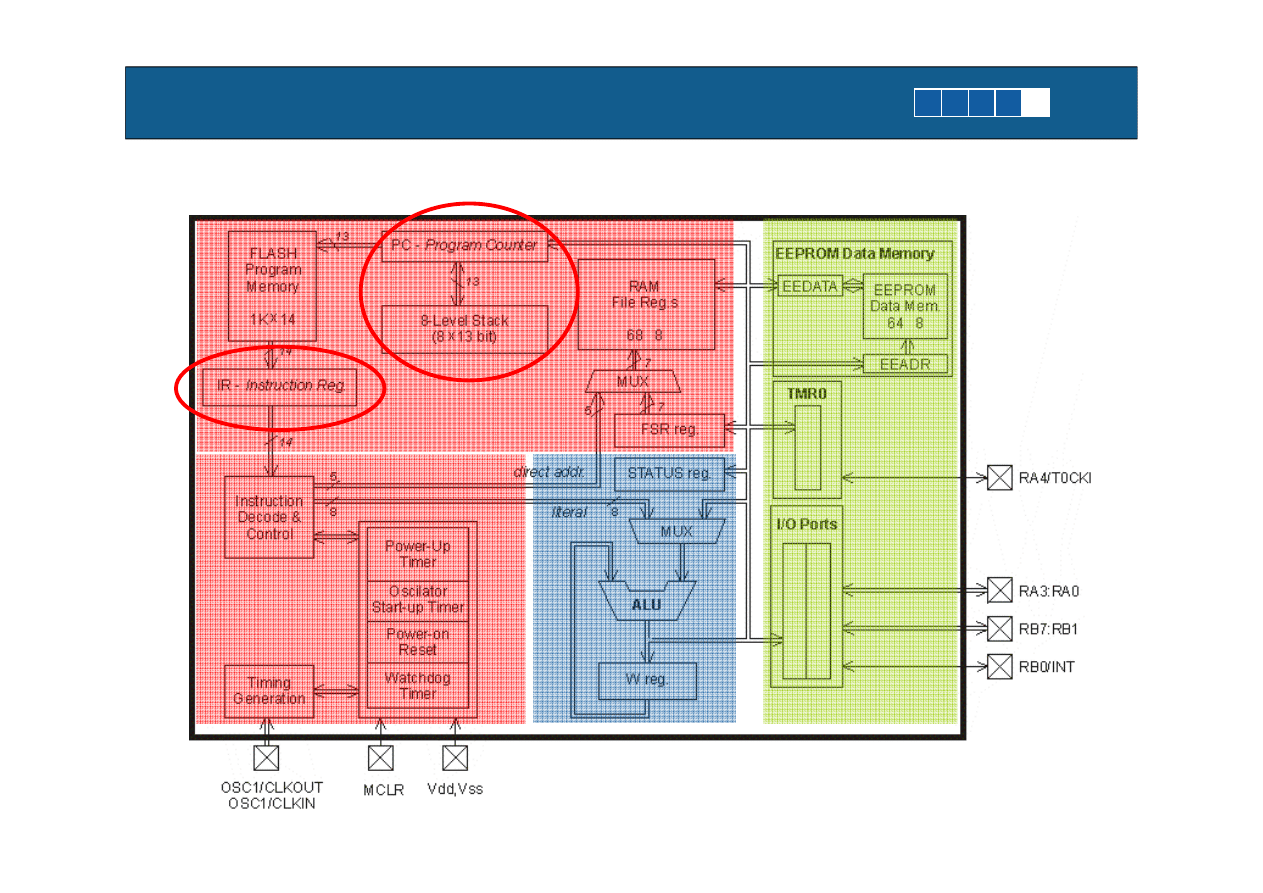

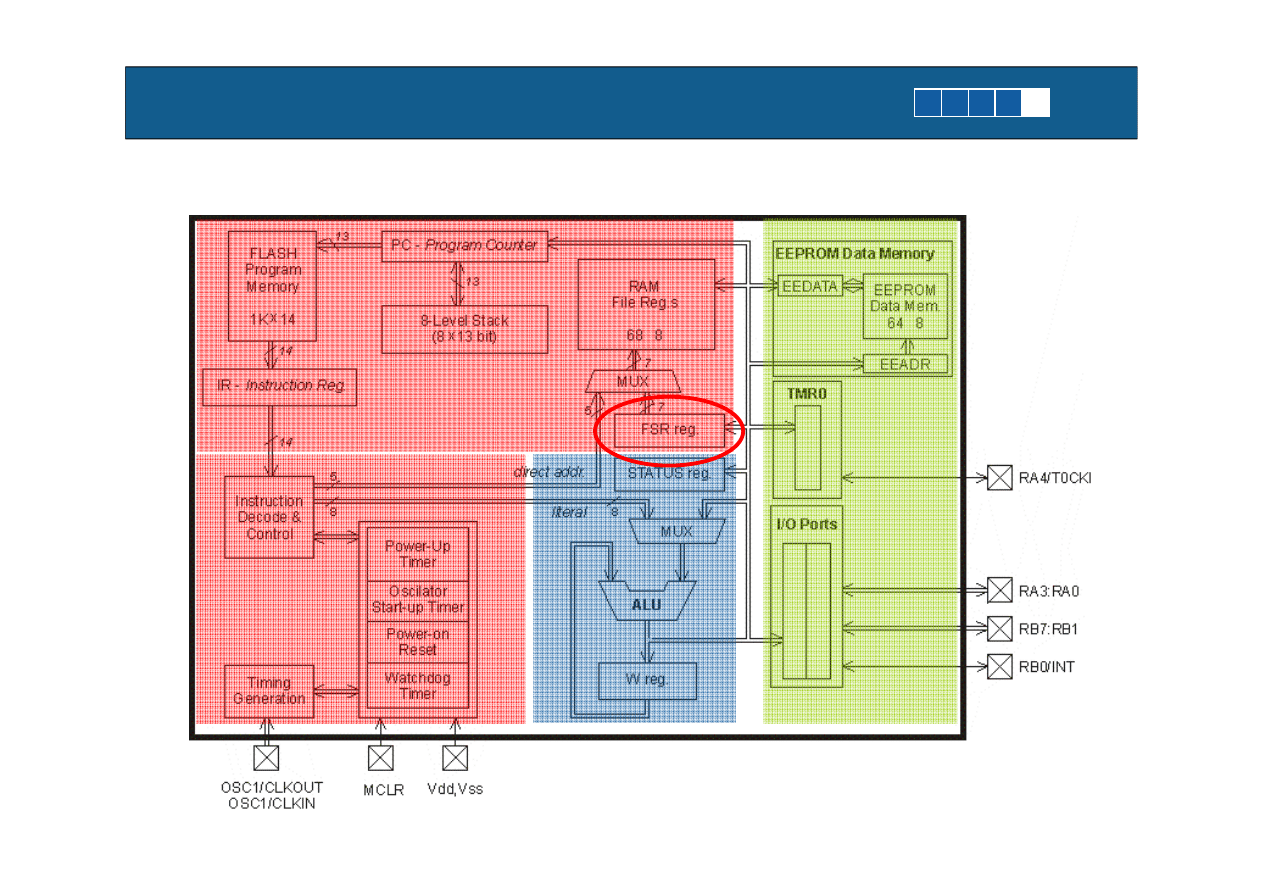

Architektura procesora PIC16F84A

Microchip PIC16F84A

Data Sheet

strona 5

1. Powtórka

4/41

1

2

3

4

5

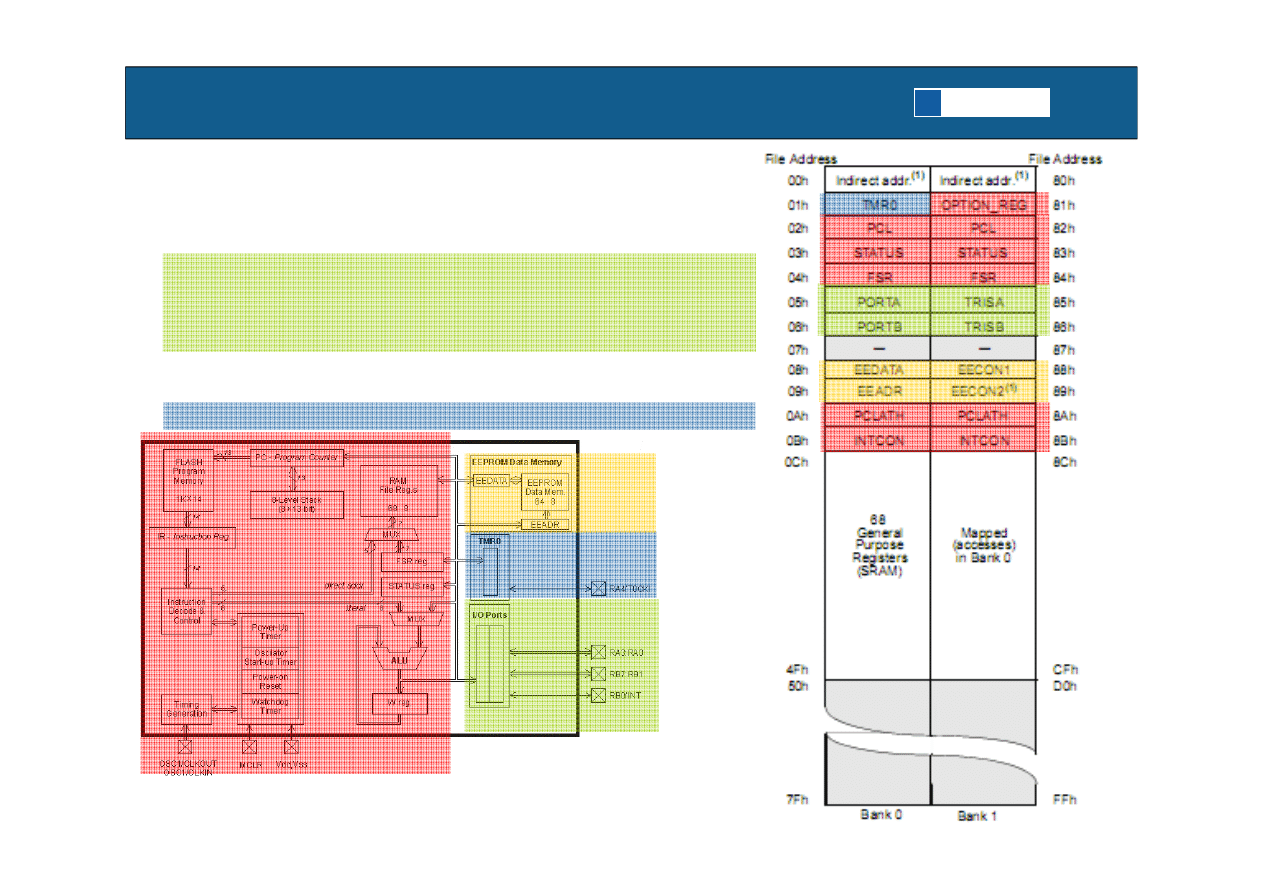

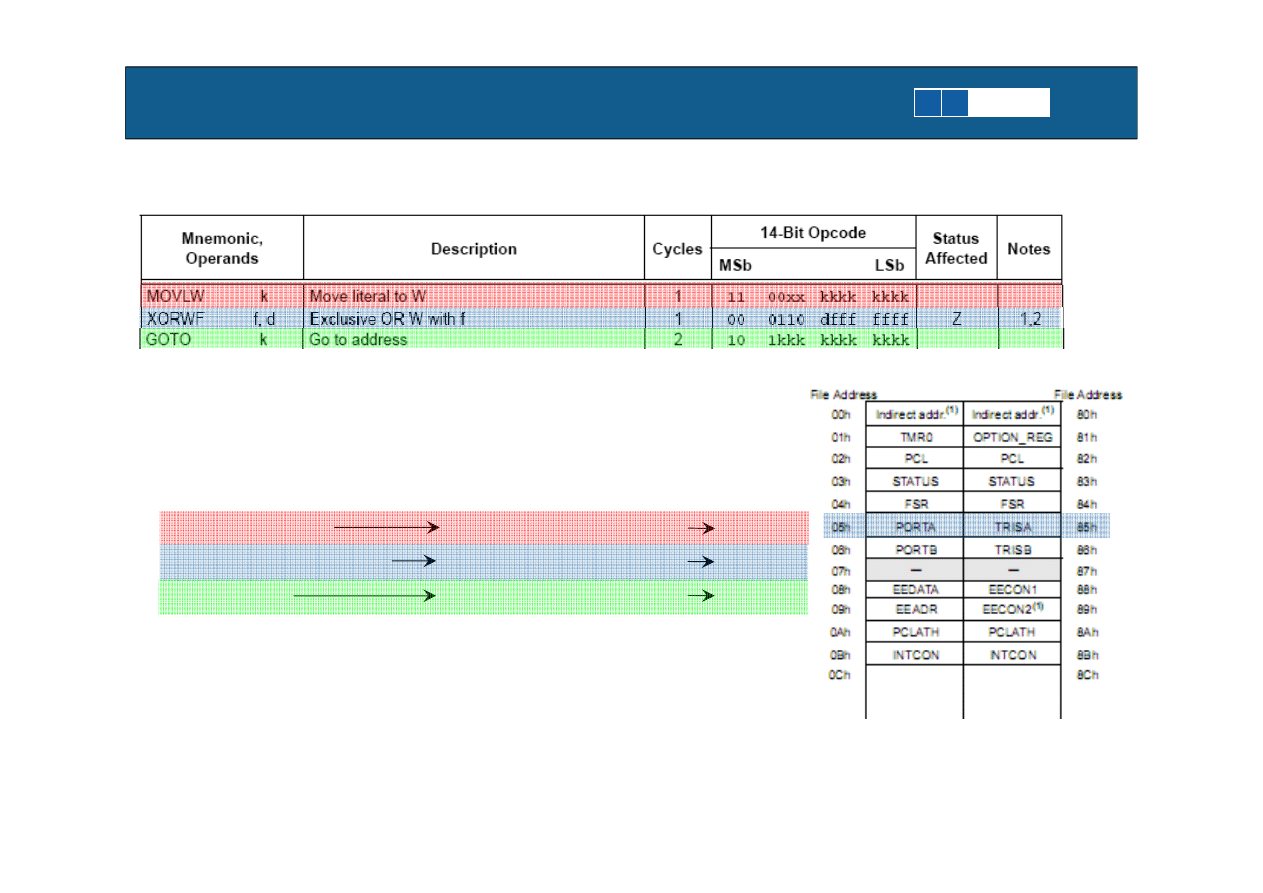

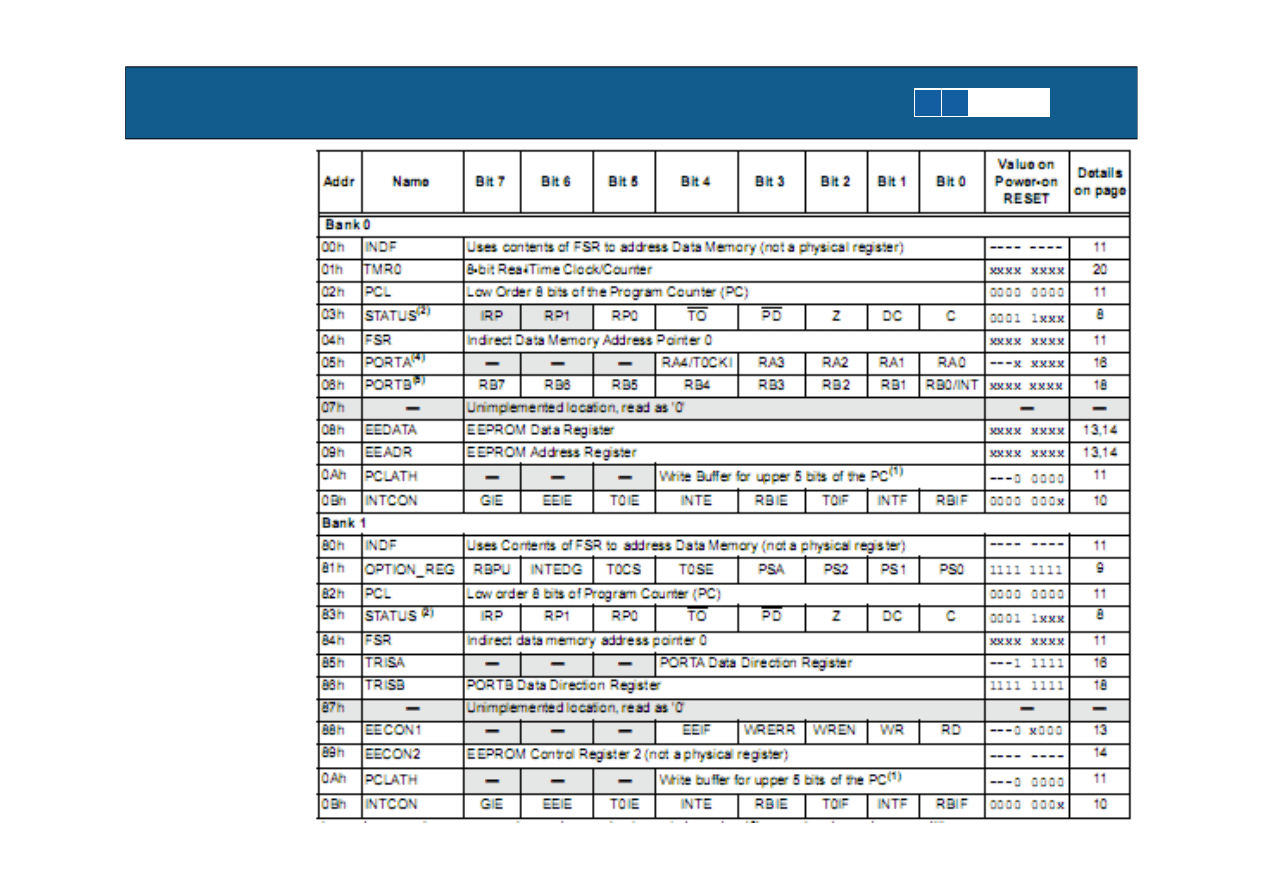

Rejestry procesora

Microchip PIC16F84A

Data Sheet

strona 8

STATUS

PORTA

TRISA

PORTB

TRISB

PCL

PCLATH

TMR0

- rejestr statusu/flag procesora

- reprezentacja stanów linii portu A

- konfiguracja wejść/wyjść na porcie A

- reprezentacja stanów linii portu B

- konfiguracja wejść/wyjść na porcie B

- Młodsze 8 bitów rejestru PC (Program Counter)

- starsza część rejestr PC

- rejestr układu Timera

1. Powtórka

5/41

1

2

3

4

5

Mrugająca dioda - przykładowy kod

Animowany GIF

bsf

STATUS, RP0

movlw

0xFC

movwf

TRISA

bcf

STATUS, RP0

Loop:

movlw

0x03

xorwf

PORTA

goto

Loop

TRISA = 0xFC;

while(1){

PORTA ^= 0x03;

};

1. Powtórka

6/41

1

2

3

4

5

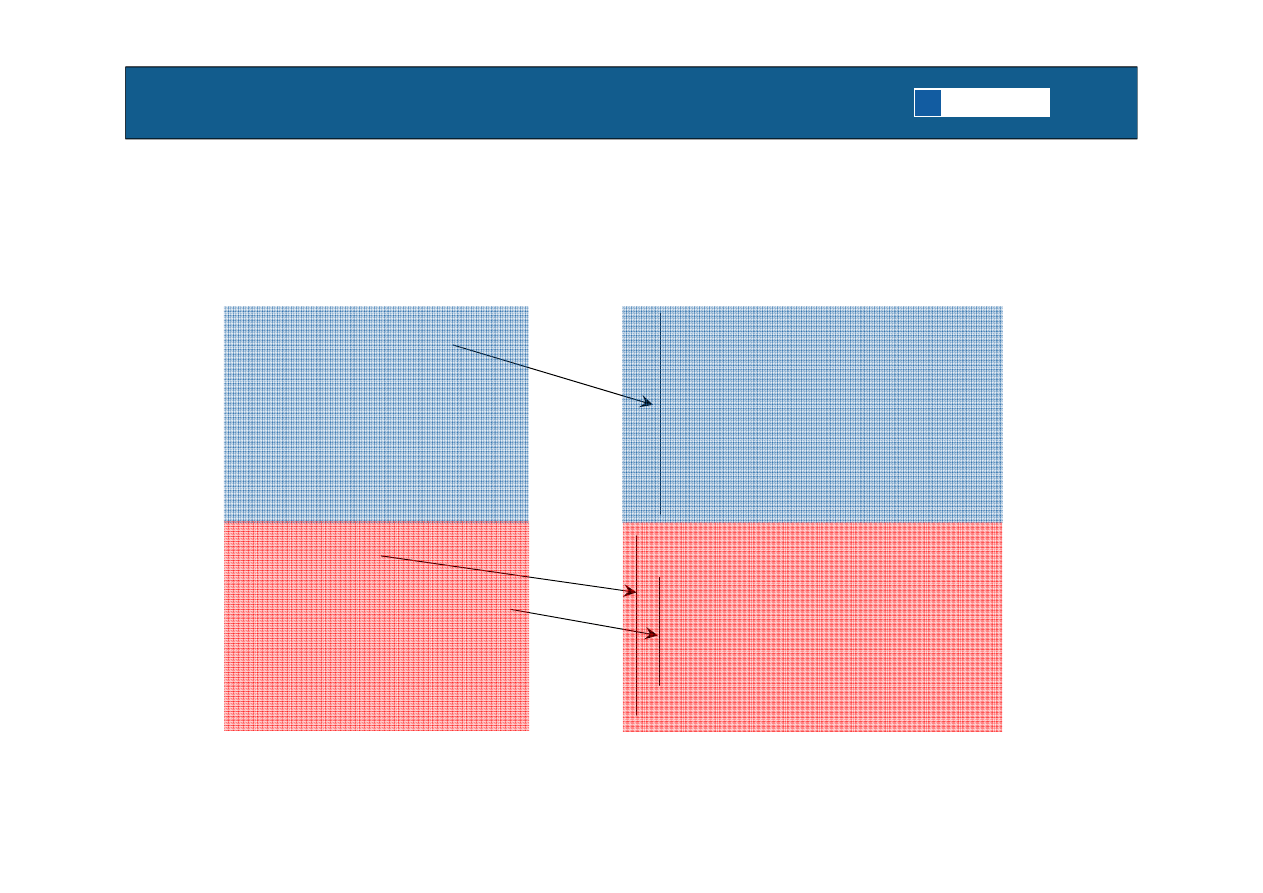

Maski

const

b AND

0 0 0

0 1 0

1 0 0

1 1 1

0

b

const

b OR

0 0 0

0 1 1

1 0 1

1 1 1

b

1

const

b XOR

0 0 0

0 1 1

1 0 1

1 1 0

b

b

movlw 0x03

xorwf a, F

a

7

a

6

a

5

a

4

a

3

a

2

a

1

a

0

= a

0 0 0 0 0 0 1 1

= 3

a

7

a

6

a

5

a

4

a

3

a

2

a

1

a

0

XOR

Zadanie:

1)

Ustawianie/zerowanie/negowanie bitów

2)

Zerowanie wartości rejestru

3)

Odwracanie bajtu

4)

Liczenie jedynek w bajcie

1. Powtórka

7/41

1

2

3

4

5

2. Instrukcja i tryby adresowania

8/41

1

2

3

4

5

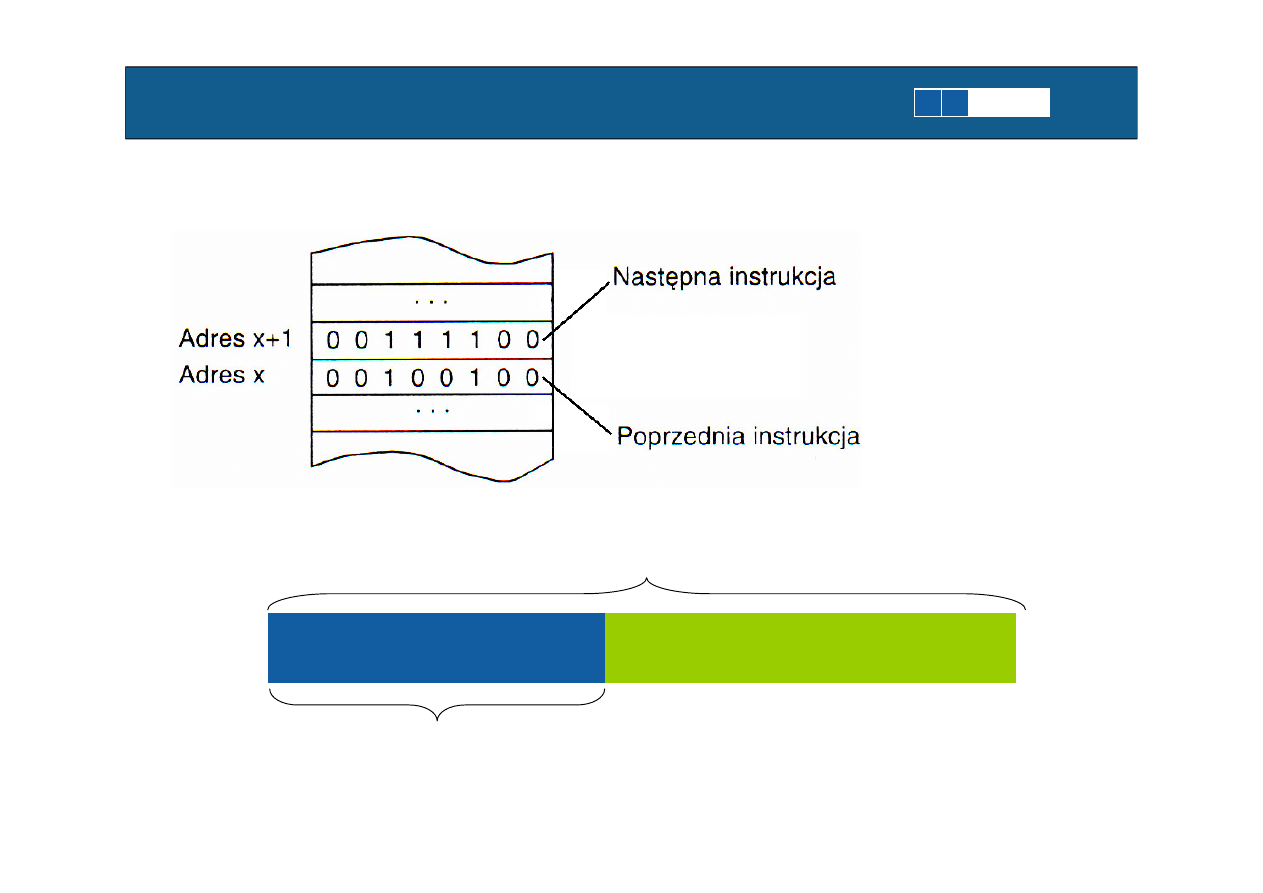

Instrukcja/Operacja

KOD OPERACJI

OPERAND LUB ADRES

INSTRUKCJA

OPERACJA

2. Instrukcja i tryby adresowania

9/41

1

2

3

4

5

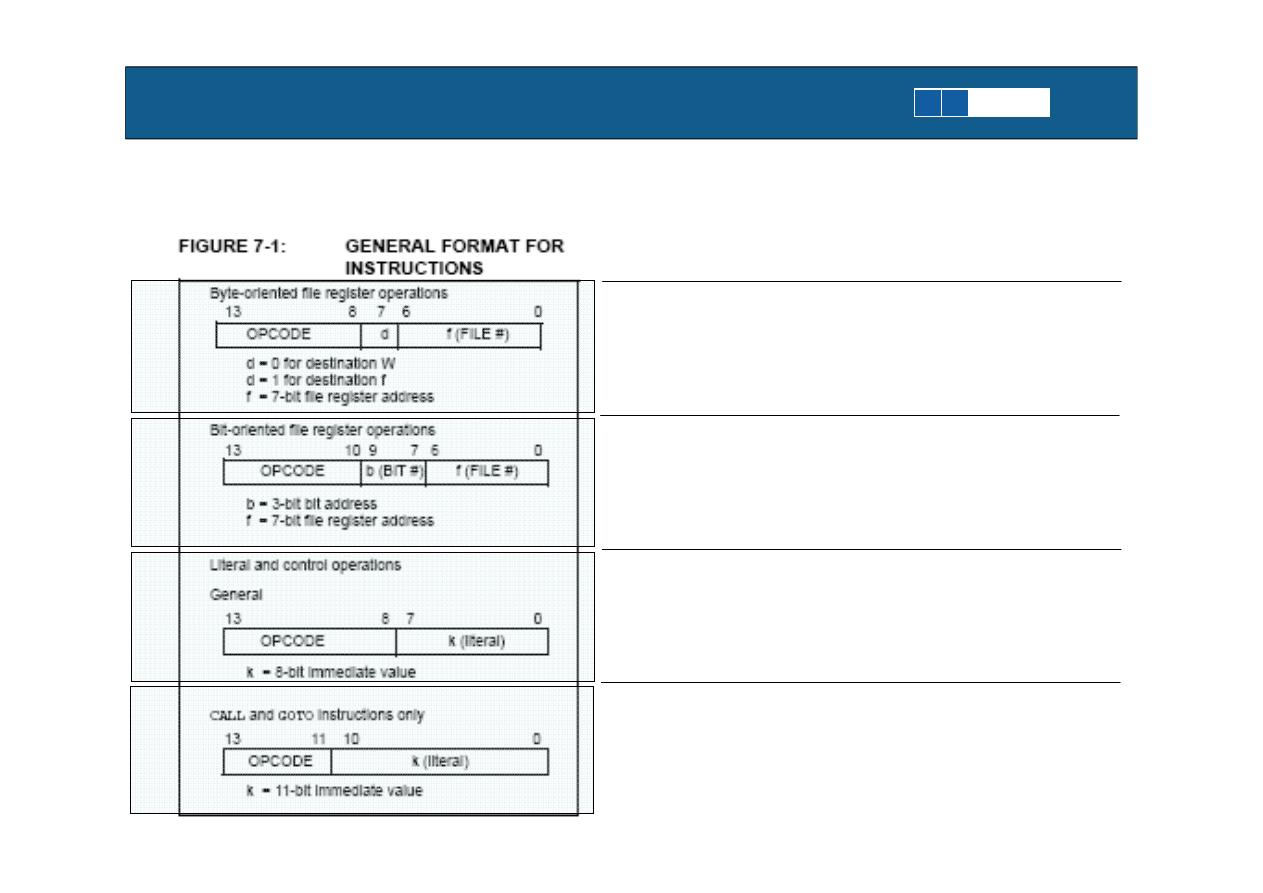

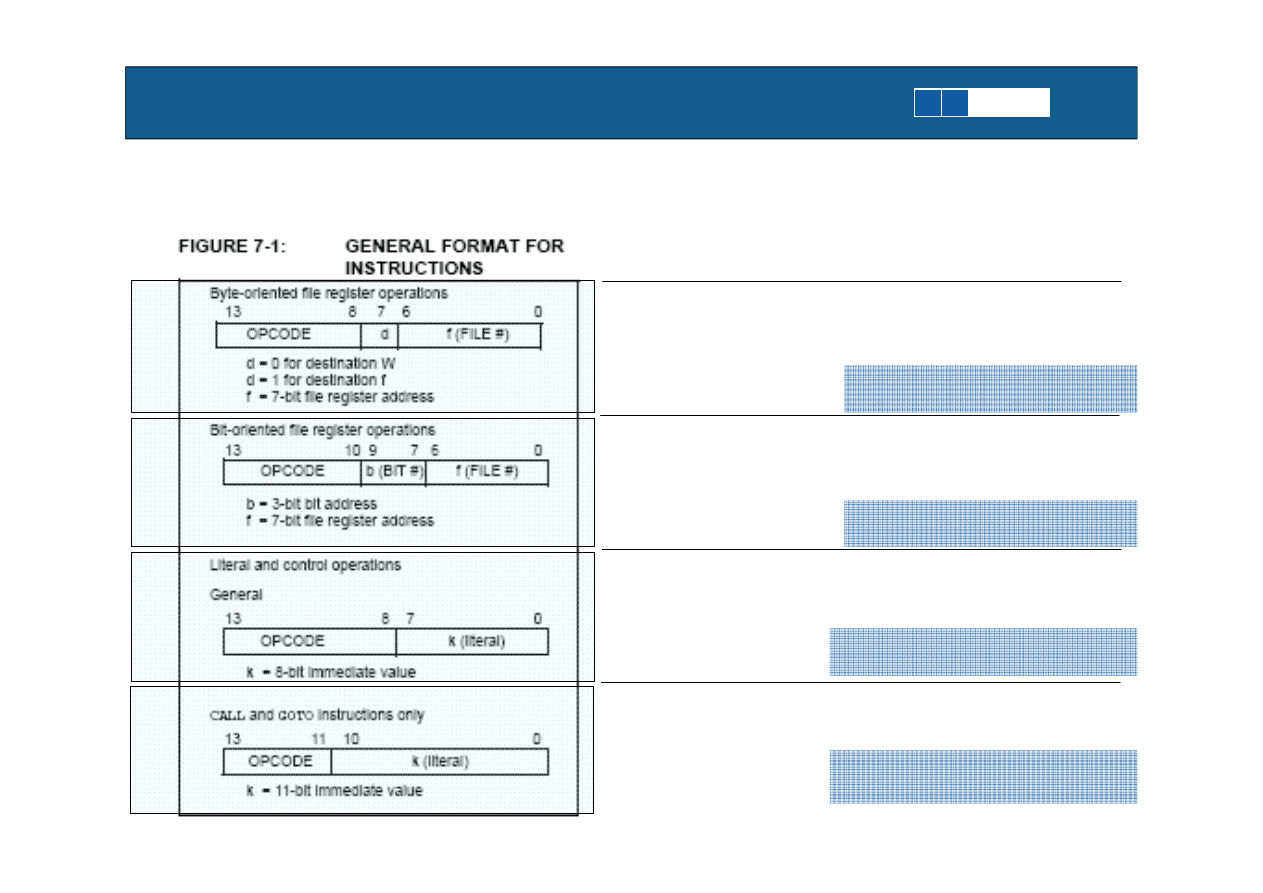

Microchip PIC16F84A

Data Sheet

strona 35

3

2

1

4

Format instrukcji

Operacja na rejestrze o podanym w instrukcji

adresie

Operacja na pojedyńczym bicie rejestru o

podanym w instrukcji adresie

Operacja na stałej

Sterowanie wykonaniem programu (zmiany PC)

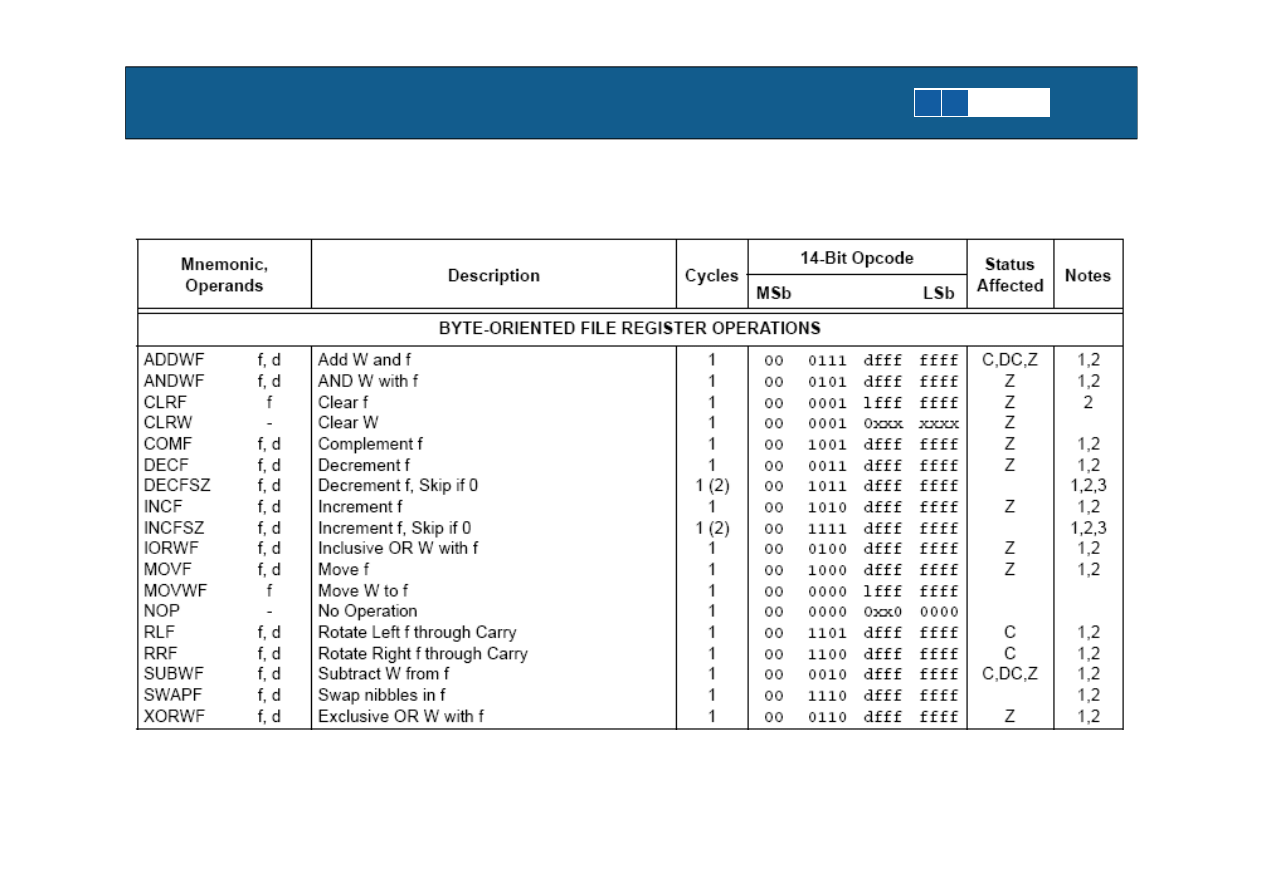

ADDWF, ANDWF, XORWF, CLRF, INCF, INCFSZ,

DECF, DECFSZ, MOVWF .......

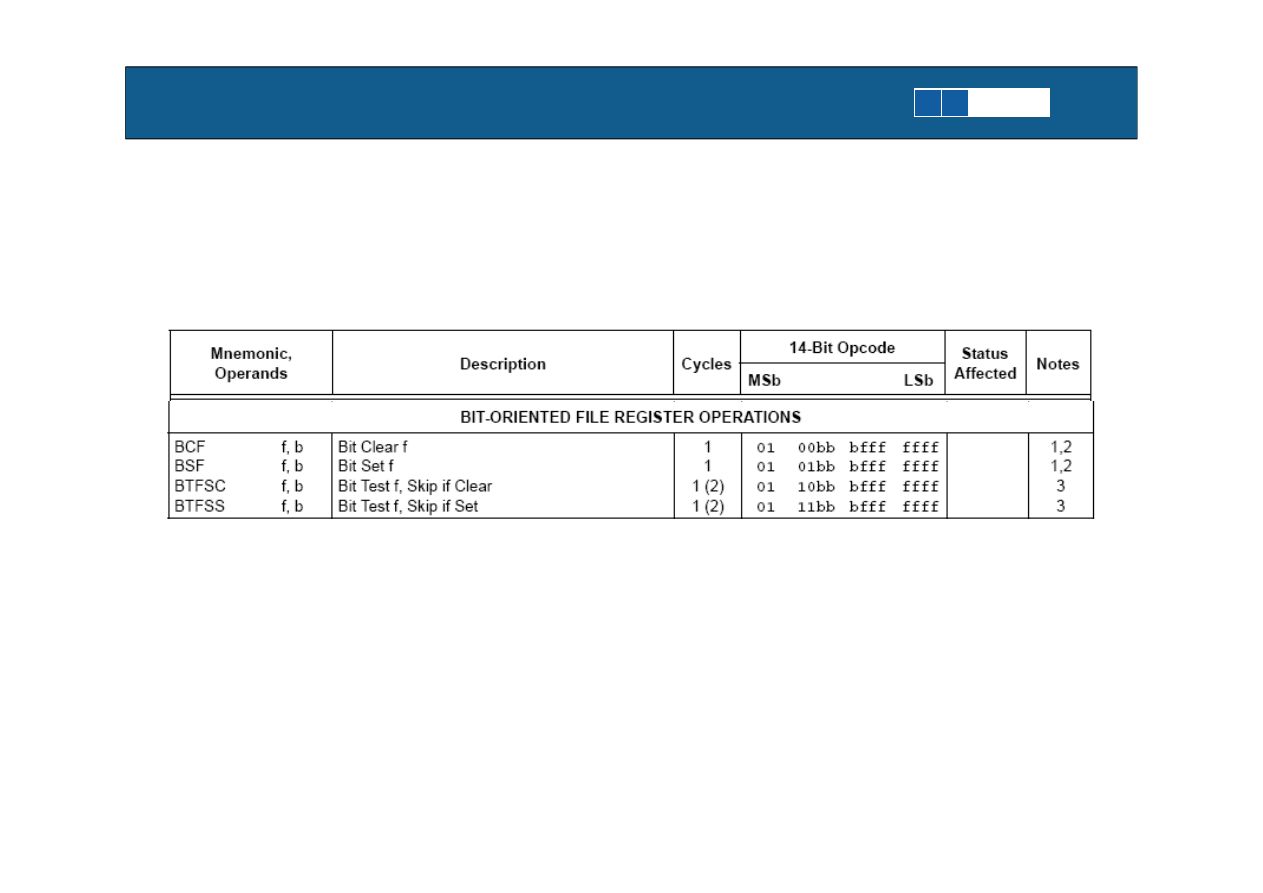

BCF, BSF, BTFSC, BTFSS

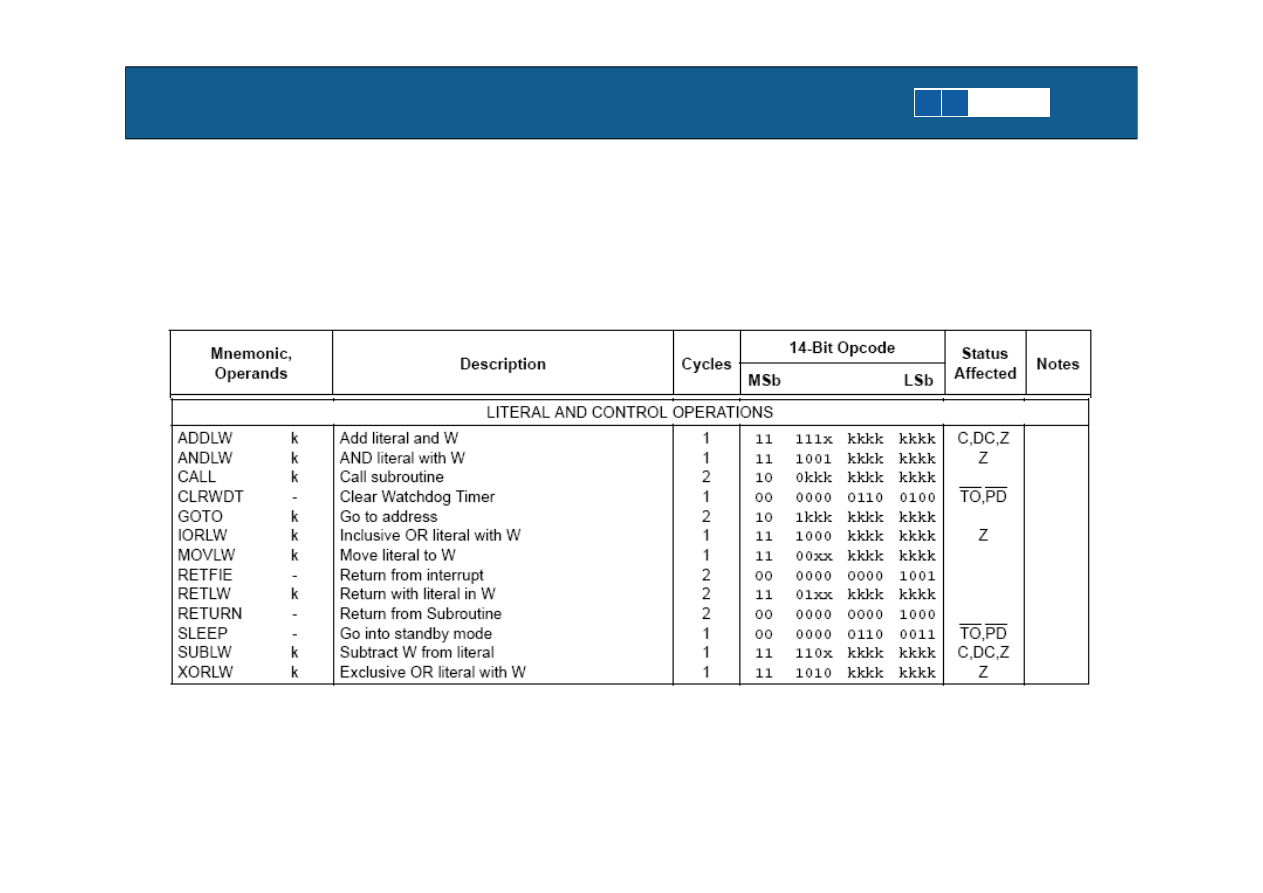

ADDLW, ANDLW, XORLW, MOVLW .......

GOTO, CALL, RETURN, RETLW, RETFIE

2. Instrukcja i tryby adresowania

10/41

1

2

3

4

5

PIC16F84A – ASM a kod maszynowy

loop:

movlw 0x03

xorwf PORTA, F

goto loop

…

11 0000 0000 0011 3003h

00 0110 1000 0101

0685h

10 1000 0000 0000

2800h

2. Instrukcja i tryby adresowania

11/41

1

2

3

4

5

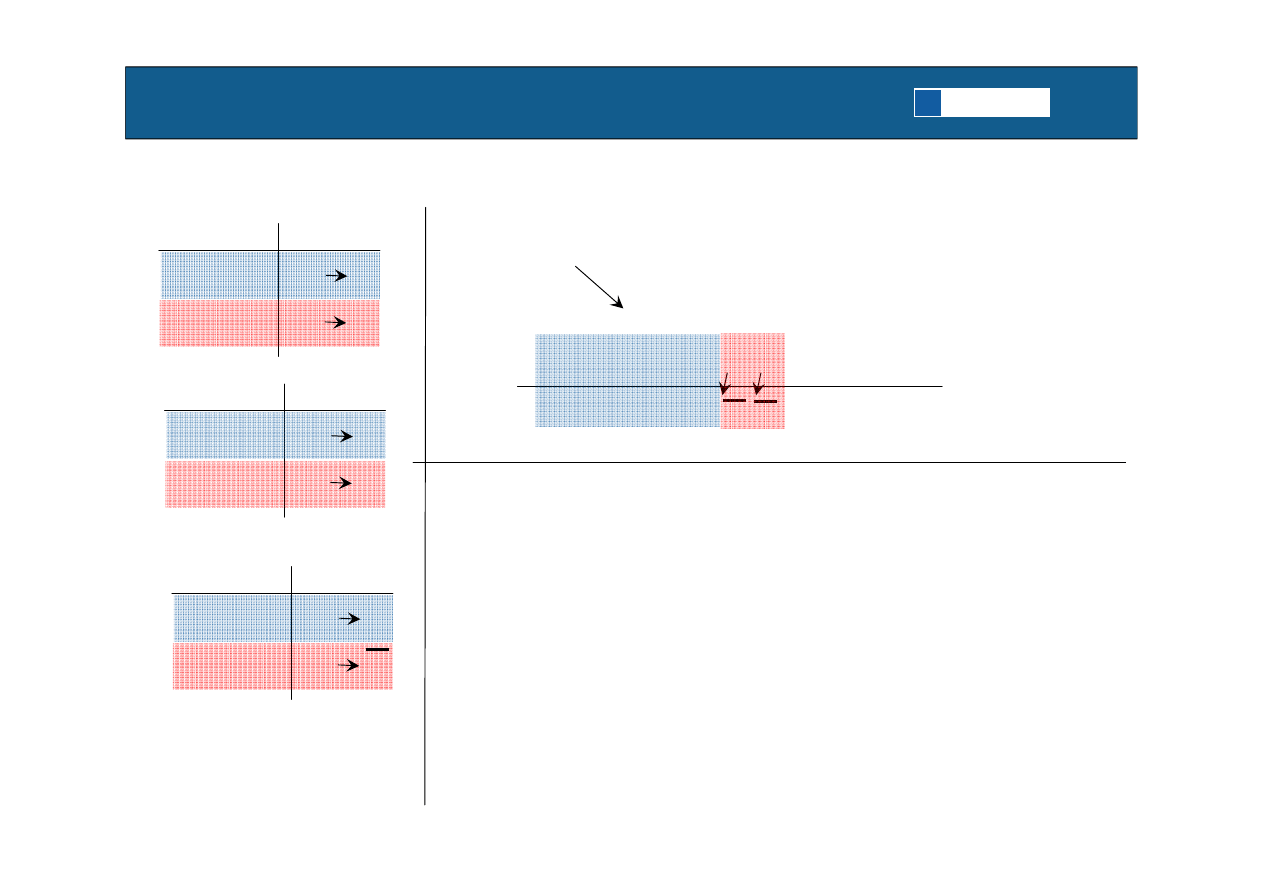

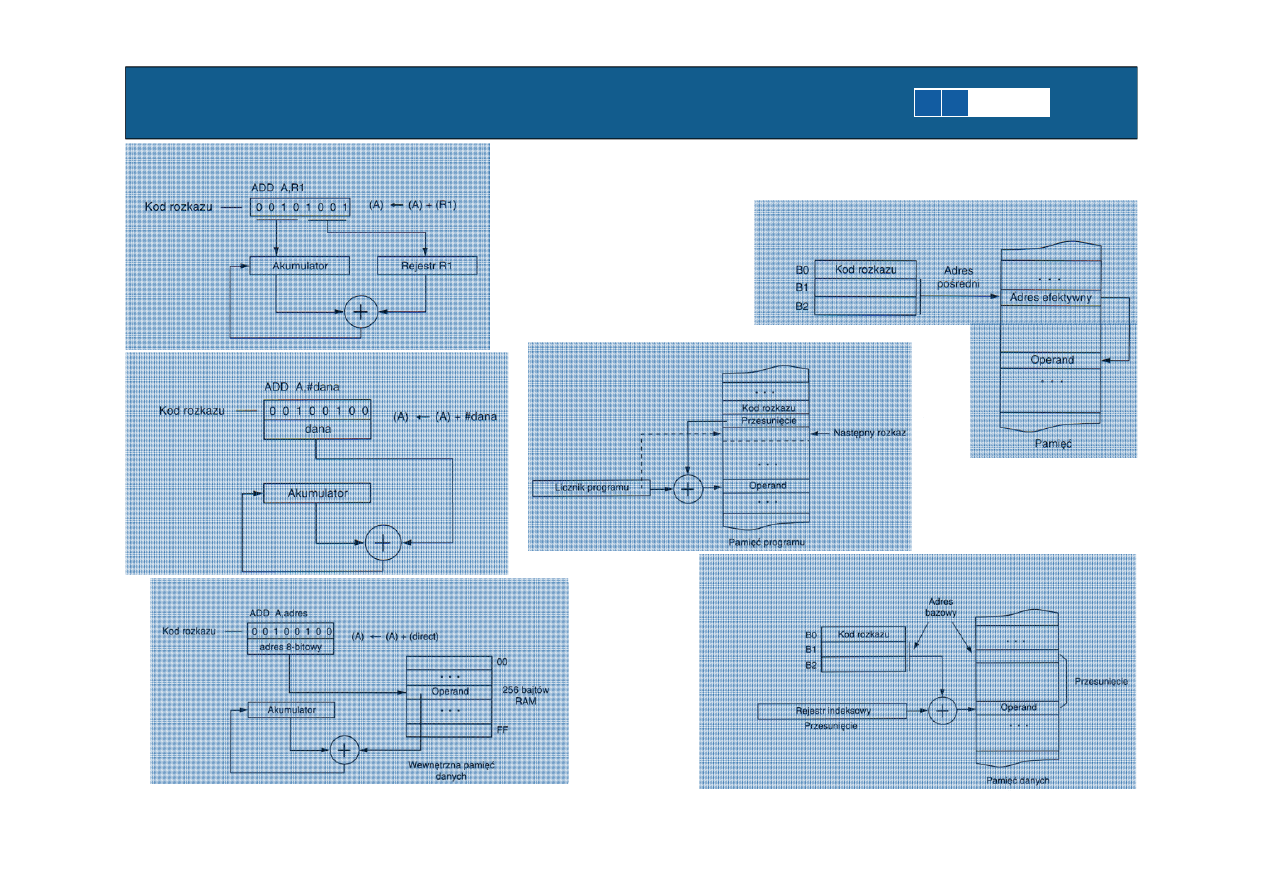

Tryby adresowania

Adresowanie implikowane

Adresowanie natychmiastowe

Adresowanie bezpośrednie

Adresowanie pośrednie

R. Pełka, Mikrokontrolery, architektura, programowanie, zastosowania, WKŁ 2000

Adresowanie indeksowe

Adresowanie

względne

2. Instrukcja i tryby adresowania

12/41

1

2

3

4

5

3

2

1

4

Operacja na rejestrze o podanym w instrukcji

adresie

Operacja na pojedyńczym bicie rejestru o

podanym w instrukcji adresie

Operacja na stałej

Sterowanie wykonaniem programu (zmiany PC)

ADDWF, ANDWF, XORWF, CLRF, INCF, INCFSZ...

BCF, BSF, BTFSC, BTFSS

ADDLW, ANDLW, XORLW, MOVLW .......

GOTO, CALL, RETURN, RETLW, RETFIE

Adresowanie implikowane

Adresowanie natychmiastowe

Adresowanie bezpośrednie

Adresowanie natychmiastowe

Adresowanie pośrednie

Adresowanie bezpośrednie

Adresowanie pośrednie

Tryby adresowania

2. Instrukcja i tryby adresowania

13/41

1

2

3

4

5

PIC16F84A – instrukcje operujące na rejestrach

2. Instrukcja i tryby adresowania

14/41

1

2

3

4

5

PIC16F84A – instrukcje operujące na bitach rejestru

2. Instrukcja i tryby adresowania

15/41

1

2

3

4

5

PIC16F84A – instrukcje kontrolne i

operujące na stałych

2. Instrukcja i tryby adresowania

16/41

1

2

3

4

5

Rejestry

procesora

2. Instrukcja i tryby adresowania

17/41

1

2

3

4

5

3. Mechanizmy działania procesora

18/41

1

2

3

4

5

3 i 4 - Operacje na stałych

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

3. Mechanizmy działania procesora

19/41

1

2

3

4

5

3 i 4 - Operacje na stałych

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

3. Mechanizmy działania procesora

20/41

1

2

3

4

5

3 i 4 - Operacje na stałych

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

3. Mechanizmy działania procesora

21/41

1

2

3

4

5

3 i 4 - Operacje na stałych

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

RETLW k

CALL k

GOTO k, RETLW k

GOTO k, RETLW k

ADDLW k

SUBLW k

MOVLW k

ANDLW k

IORLW k

XORLW k

GOTO k

RETLW k

CALL k

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

3. Mechanizmy działania procesora

22/41

1

2

3

4

5

1 i 2 - Operacje na rejestrach

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

3. Mechanizmy działania procesora

23/41

1

2

3

4

5

1 i 2 - Operacje na rejestrach

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

3. Mechanizmy działania procesora

24/41

1

2

3

4

5

1 i 2 - Operacje na rejestrach

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

3. Mechanizmy działania procesora

25/41

1

2

3

4

5

1 i 2 - Operacje na rejestrach

1) Dekodowanie instr.

2) Pobranie argumentów

3) Wykonanie (ALU)

4) Zapis wyników

1) PC->szyna; PC++

2) Odczyt FLASH

3) Wypełnienie IR

4) Zmiany IR i PC

zależne od danych

ADDWF F,d

ANDWF F,d

DECF F,d

DECFSZ F,d

MOVEF F,d

MOVWF F

RLF F,d

BSF F,b

BTFSS F,b

DECFZ, BTFSZ

DECFZ, BTFSZ

26/41

1

2

3

4

5

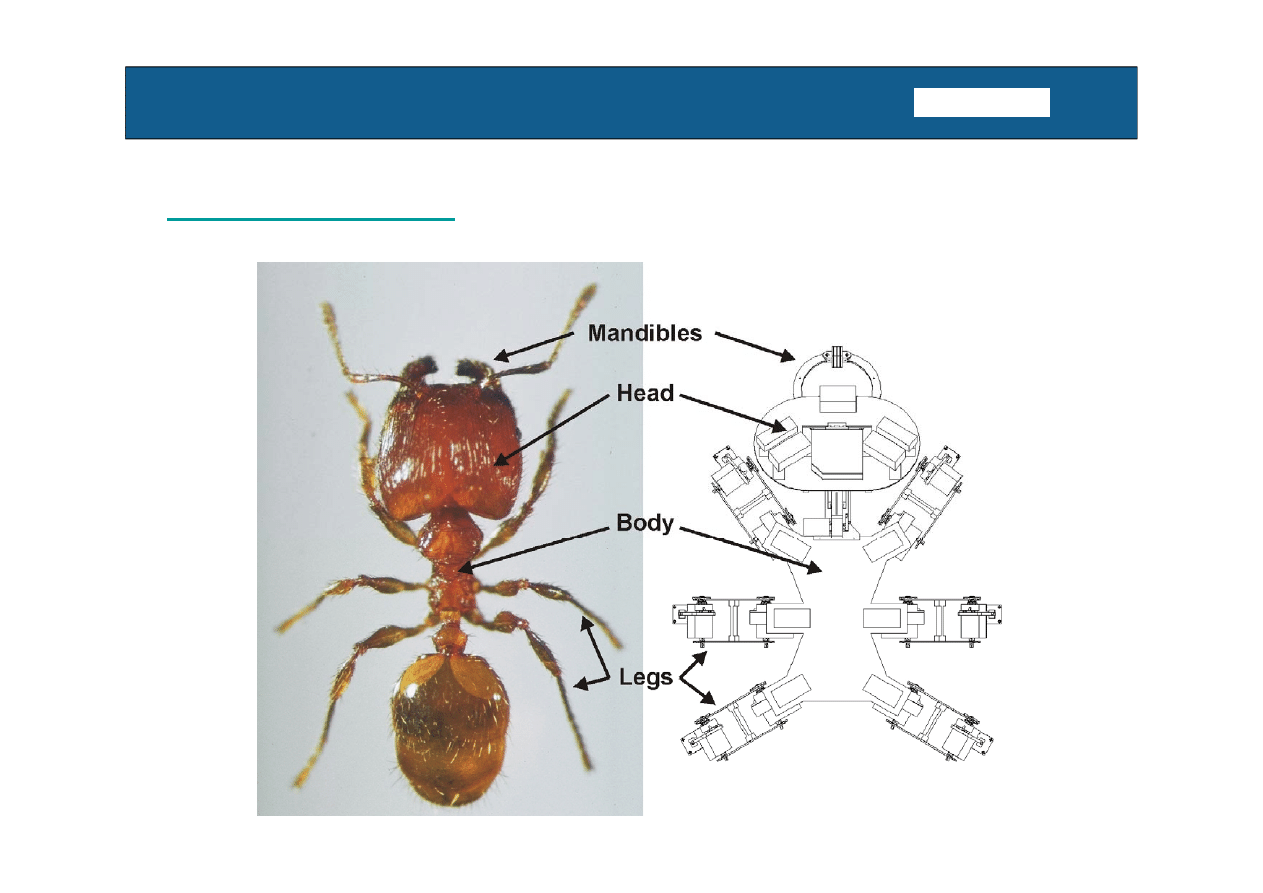

4. call, goto, przerwania i adr. pośrednie

PRZERWA

http://biorobots.cwru.edu/projects/billant/

27/41

1

2

3

4

5

4. call, goto, przerwania i adr. pośrednie

PIC16F84A – call i goto

28/41

1

2

3

4

5

4. call, goto, przerwania i adr. pośrednie

PIC16F84A – call i goto - zadania

Funkcja sin jako wartości ztablicowane

255

1

1,57079633

90

251

0,98480775

1,3962634

80

240

0,93969262

1,22173048

70

221

0,8660254

1,04719755

60

195

0,76604444

0,87266463

50

164

0,64278761

0,6981317

40

128

0,5

0,52359878

30

87

0,34202014

0,34906585

20

44

0,17364818

0,17453293

10

0

0

0

0

255*sin

sin(rad)

rad

stopnie

?

29/41

1

2

3

4

5

4. call, goto, przerwania i adr. pośrednie

PIC16F84A – przerwania

PROBLEM: instrukcja goto przerwana

przerwaniem

30/41

1

2

3

4

5

4. call, goto, przerwania i adr. pośrednie

PIC16F84A – adresowanie pośrednie

Zadanie: wyczyścić tablicę pomiędzy

adresami 0x20 a 0x30

31/41

1

2

3

4

5

4. call, goto, przerwania i adr. pośrednie

PRZERWA

http://www.servomagazine.com/media-files/555/Ant-Basic.jpg

http://www.ai.mit.edu/projects/ants/social-behavior

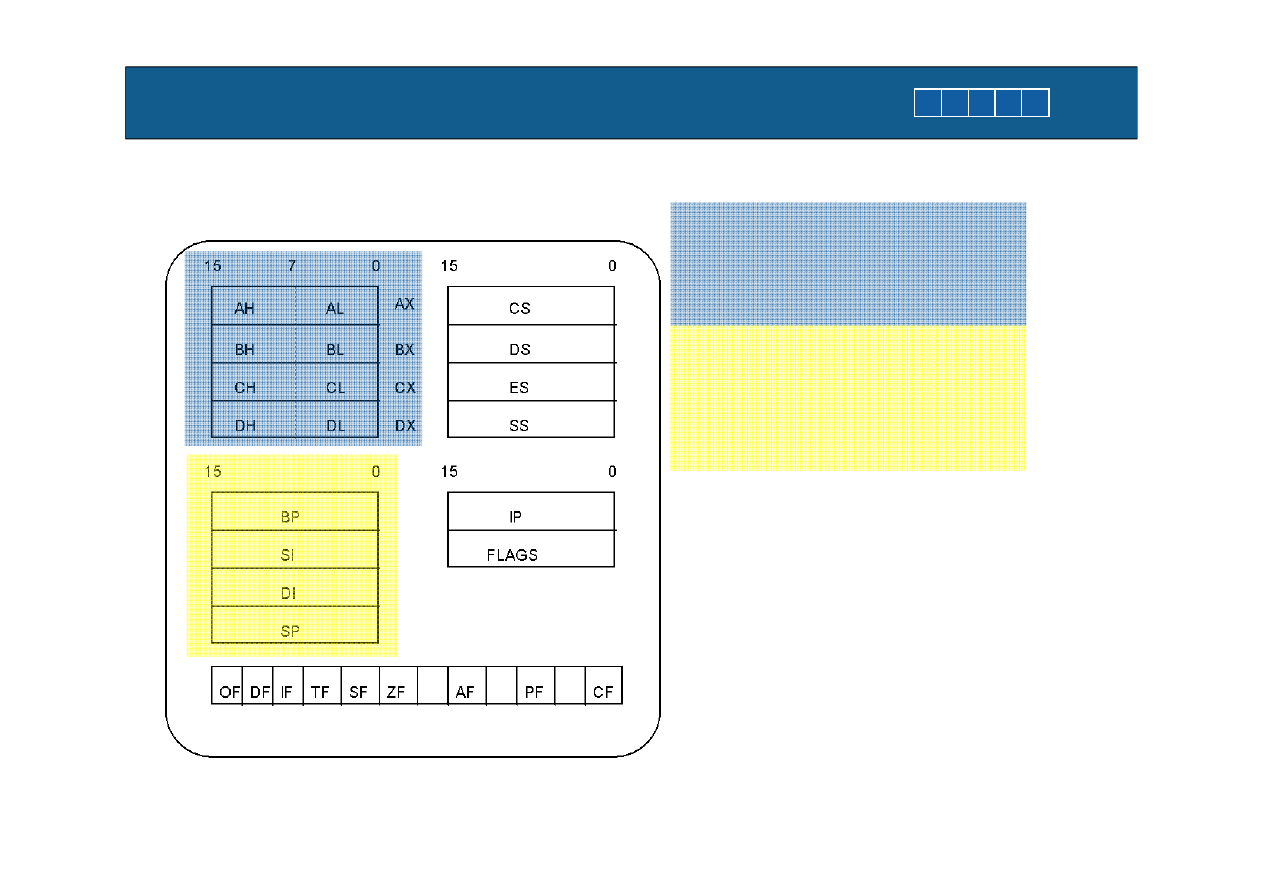

5. Architektura x86 - wprowadzenie

32/41

1

2

3

4

5

Rejestry 8086

AX – Accumulator Register

BX – Base Address Register

CX – Count Register

DX – Data Register

BP – Base Pointer

SP – Stack Pointer

SI – Source Index Register

DI – Destination Index Register

IP – Instruction Pointer

FLAGS:

OF – Overflow Flag

DF – Direction Flag

IF – Interrupt Enable Flag

TF – Trap Flag

SF – Sign Flag

ZF – Zero Flag

AF – Auxiliary Flag

PF – Parity Flag

CF – Carry Flag

5. Architektura x86 - wprowadzenie

33/41

1

2

3

4

5

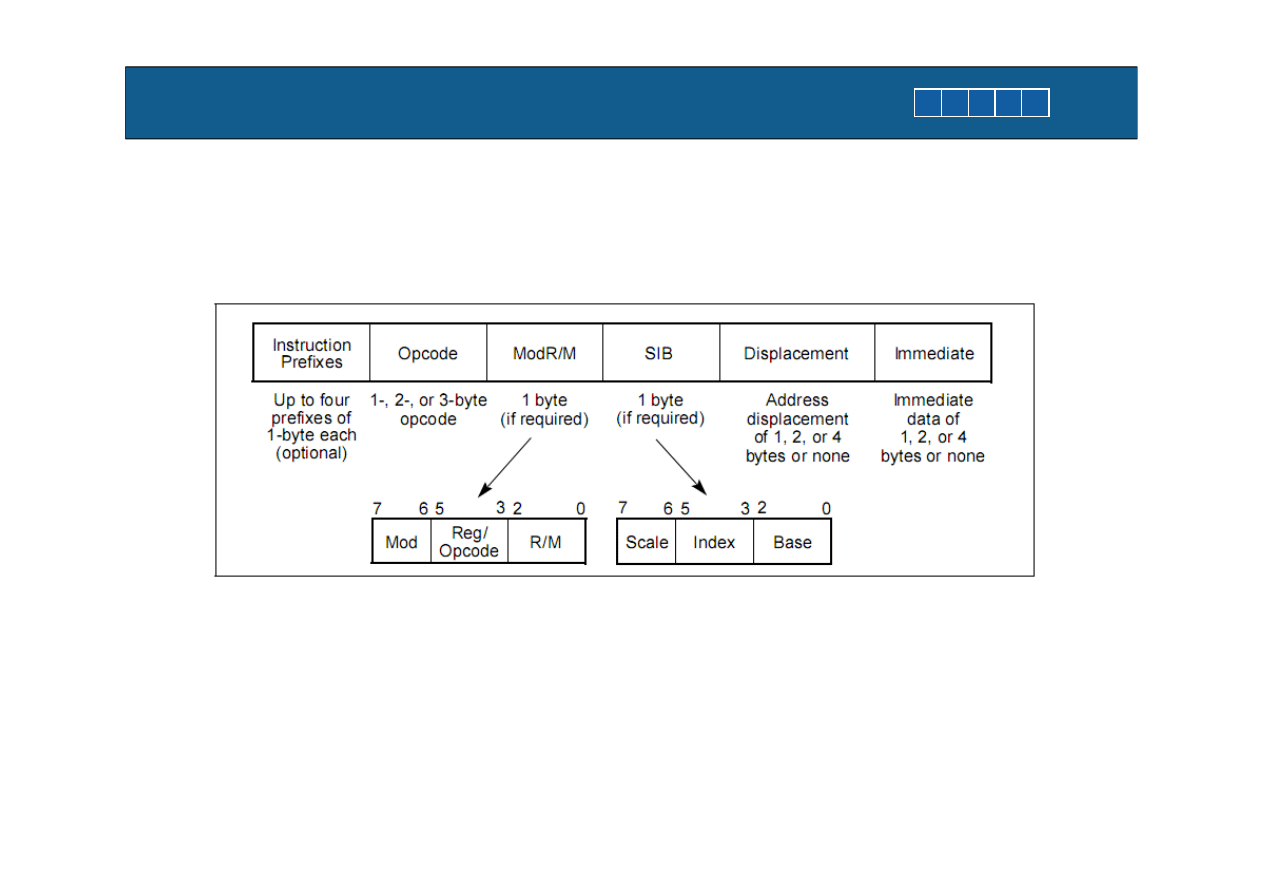

Format Instrukcji 8086

http://www.sandpile.org/ia32/

5. Architektura x86 - wprowadzenie

34/41

1

2

3

4

5

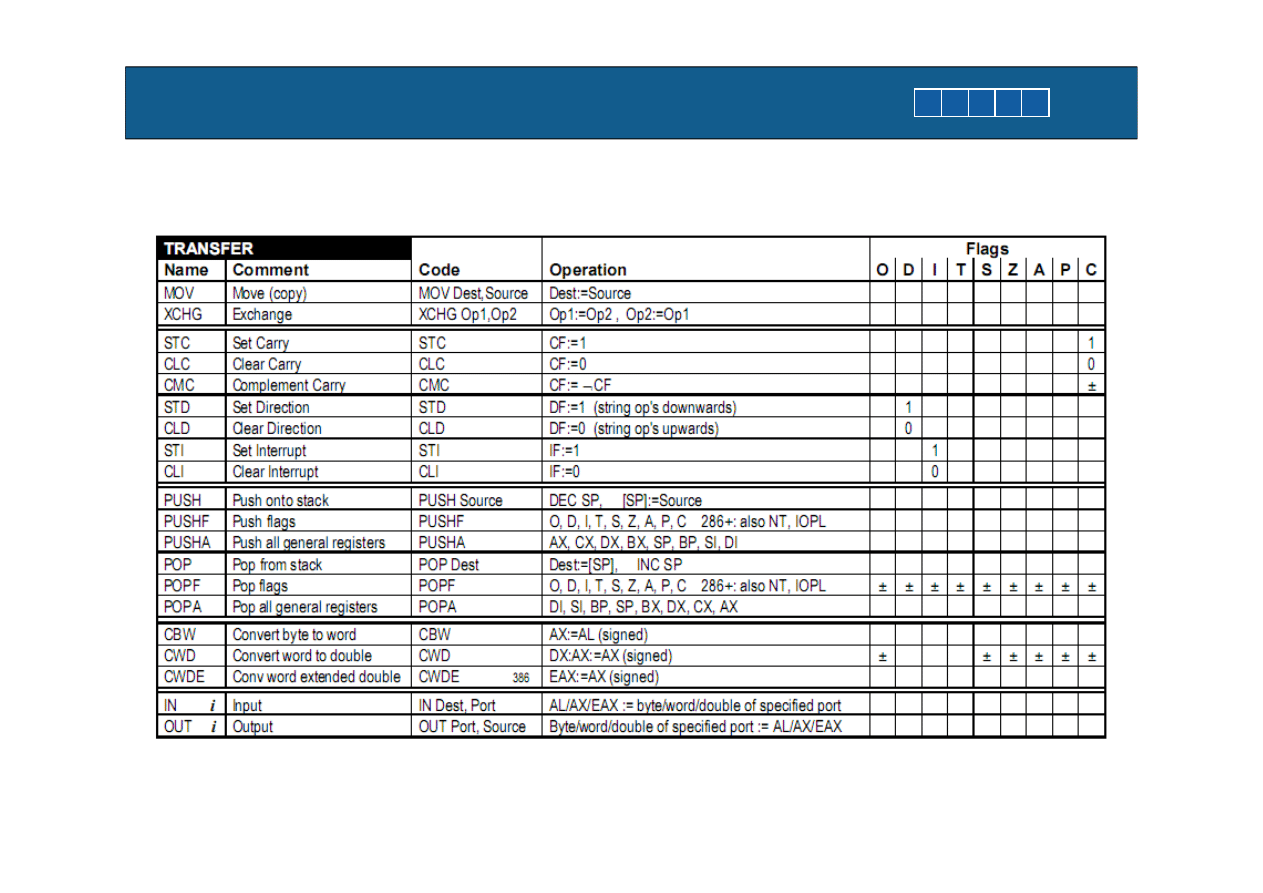

Lista instrukcji 8086 – instrukcje transferu

5. Architektura x86 - wprowadzenie

35/41

1

2

3

4

5

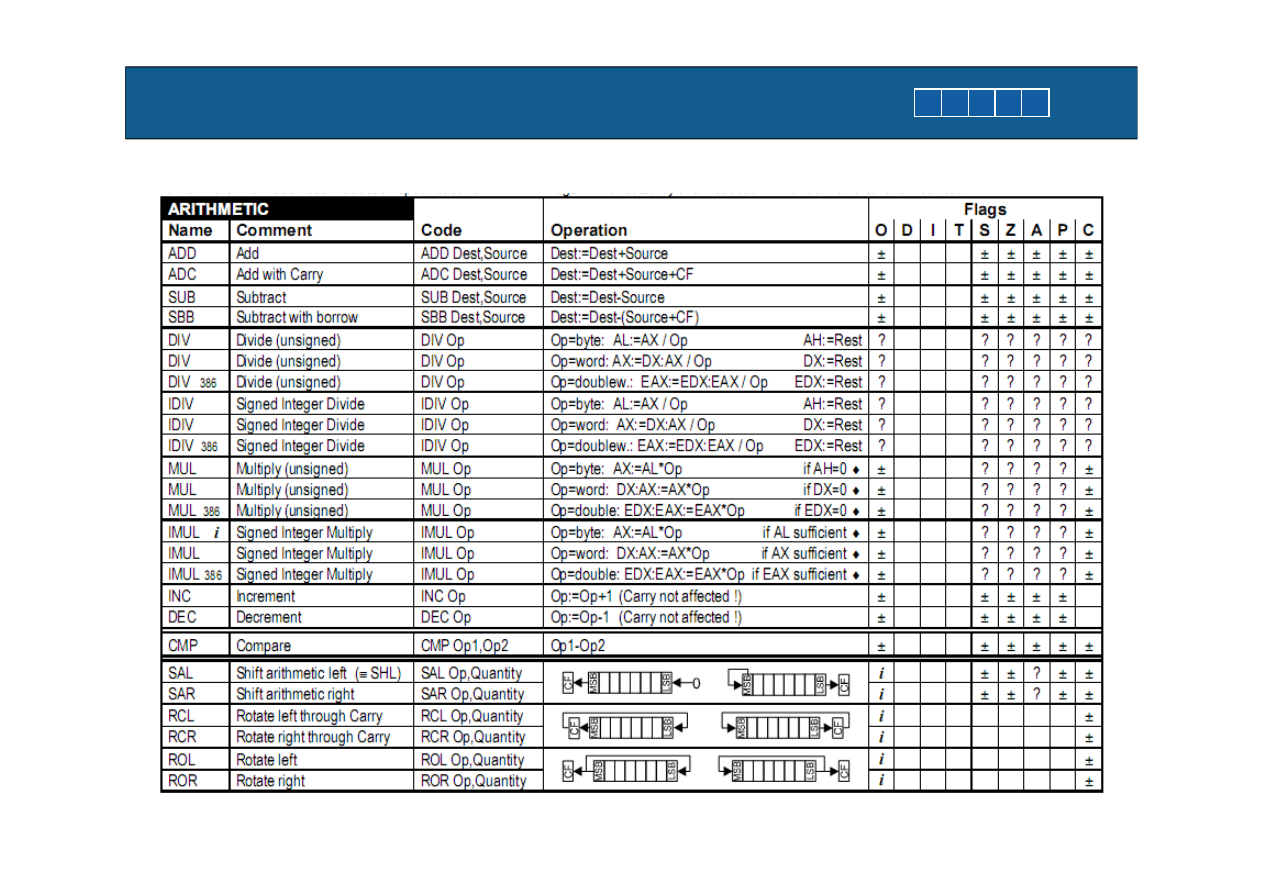

Lista instrukcji 8086 – instrukcje arytmetyczne

5. Architektura x86 - wprowadzenie

36/41

1

2

3

4

5

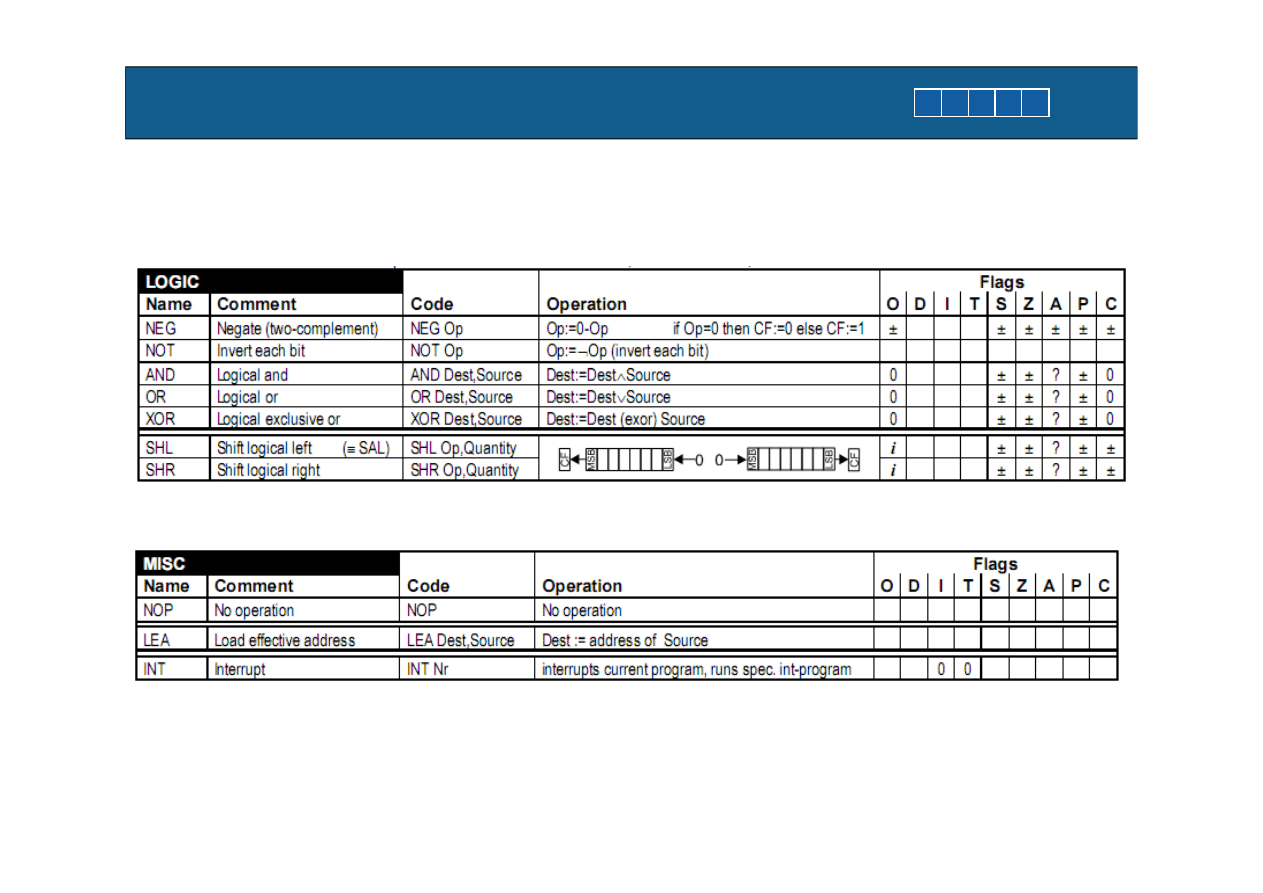

Lista instrukcji 8086 – instrukcje logiczne

5. Architektura x86 - wprowadzenie

37/41

1

2

3

4

5

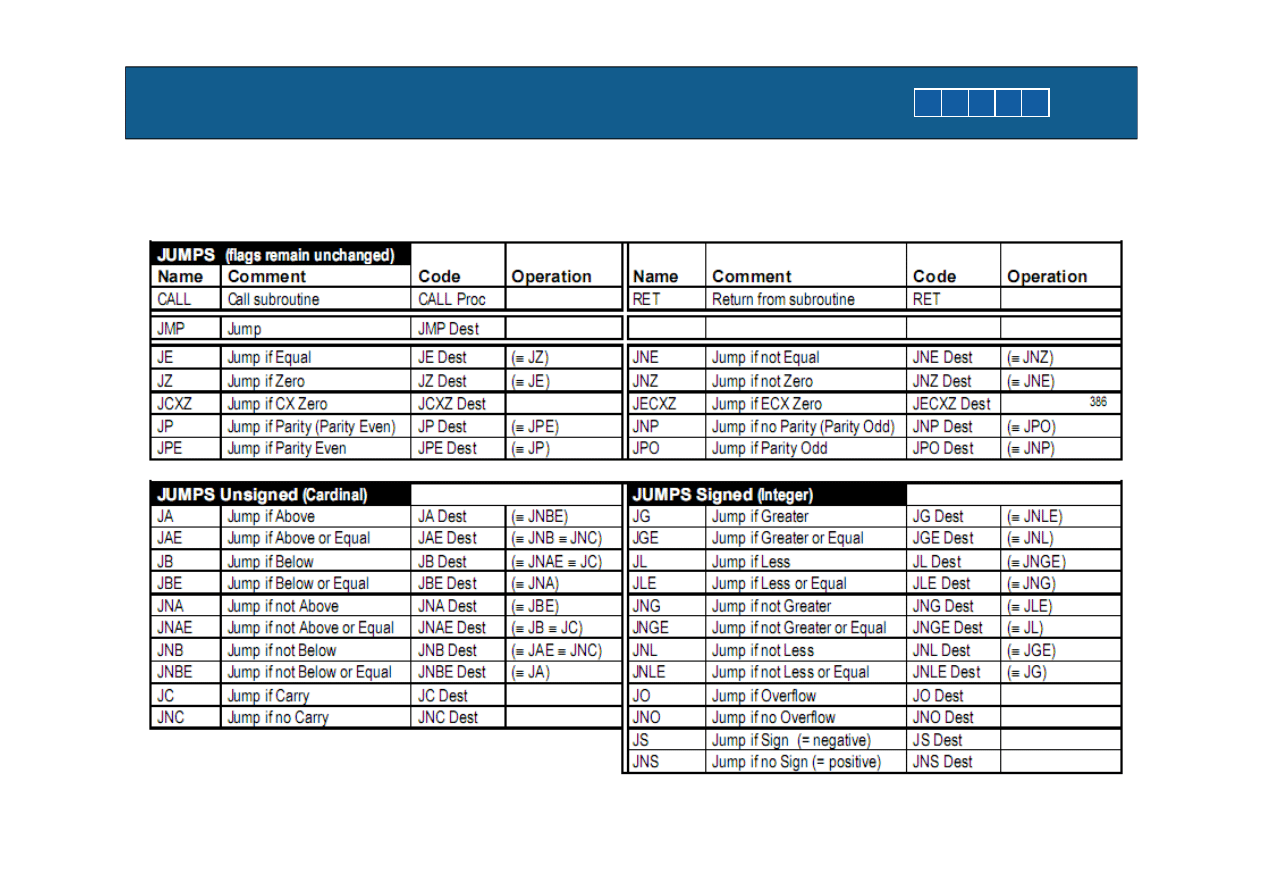

Lista instrukcji 8086 – instrukcje skoku

5. Architektura x86 - wprowadzenie

38/41

1

2

3

4

5

Lista instrukcji 8086 – tryby adresowania

Implied (implikowane) – argument związany jednoznacznie z nazwą instrukcji.

Register (rejestrowe) – argument dotyczy jednego z rejestrów procesora

Immediate (natychmiastowe) – wartość danej zawarta jest w kodzie instrukcji

Direct (bezpośrednie) – instrukcja zawiera adres do pamięci, pod którym znajduje się

wartość argumentu

Register indirect (pośrednie rejestrowe) – instrukcja zawiera adres rejestru, który

zawiera adres do pamięci, pod którym znajduje się wartość danej. Dotyczy to

rejestrów SI, DI, BX oraz BP.

Indexed (indeksowe) – instrukcja zawiera stałą, która dodawana jest do rejestru

bazowego (BX, BP) lub indeksowego (SI, DI), tworząc adres do pamięci, pod którym

znajduje się wartość danej.

Based Indexed (bazowe indeksowe) – zawartość rejestru bazowego (BX, BP) jest

dodawana do zawartości rejestru indeksowego (SI, DI), tworząc adres do pamieci, pod

którym znajduje się wartość danej.

Based Indexed with displacement (bazowe indeksowe z przemieszczeniem) – stała

jest dodawana do rejestru bazowego (BX, BP) oraz rejestru indeksowego (SI, DI),

tworząc adres do pamięci, pod którym znajduje się wartość danej.

RET

MOV AX, BX

JMP 0x0100

JMP AX, licznik

ADD [DI], AX

ADD [DI+8], AX

NOT [BX+DI]

NOT [BX+DI+8]

5. Architektura x86 - wprowadzenie

39/41

1

2

3

4

5

Przykłady, assembler dla x86

1)

Ustawianie/zerowanie/negowanie bitów

2)

Zerowanie wartości rejestru

3)

Odwracanie bajtu

4)

Liczenie jedynek w bajcie

5)

Instrukcje C w asemblerze:

y = a + b; if, while, for…

Funkcjonowanie procesora

40/41

Polecana literatura

1) R. Pełka, Mikrokontrolery, architektura, programowanie, zastosowania, WKŁ 2000

2) Microchip, PIC16F84A Data Sheet

Rozdział 2. Budowa i zasada działania mikrokontrolera

strony 15 - 29

3) W. Stallings, Organizacja i architektura systemu komputerowego, WNT 2003

Rozdział 9, 10, 11, str 368-496

4) J. Stokes, Inside the Machine, No Starch Press, 2007

Rozdział 2,3. The Mechanics of Program Execution,

Pipelined Execution

strony 19 - 58

14 stron

44 stron

128 stron

39 stron

5) Intel IA-32 Software Developers Manual, August 2007

Funkcjonowanie procesora

41/41

Dziękuje

dr inż. Mariusz Kapruziak

mkapruziak@wi.ps.pl

pok. 107, tel. 449 55 44

Wyszukiwarka

Podobne podstrony:

ASK 02 PawelKopec AdrianMakuch

ASK 02 PIC1

ASK 02 PawelKopec AdrianMakuch

ASK 01 arch PC

ASK 01 arch PC bw

ASK 02 PiotrGębala MateuszMacięga

ASK 02 Kernel

ASK 02 Kernel

02 x86 vs x86 64

02 ASK Harmonogram referatów 2012

arch pojecia, Studia-WSTI (vizja.net), ASK - wykłady

arch zal, Studia Informatyka 2011, Semestr 1, Architektura systemów komputerowych, Zaliczenie z ASK

ARCH B rys 02

02 x86 vs x86 64

ARCH B rys 02

02 x86 vs x86 64

więcej podobnych podstron