F2-31

Układy CMOS - 10

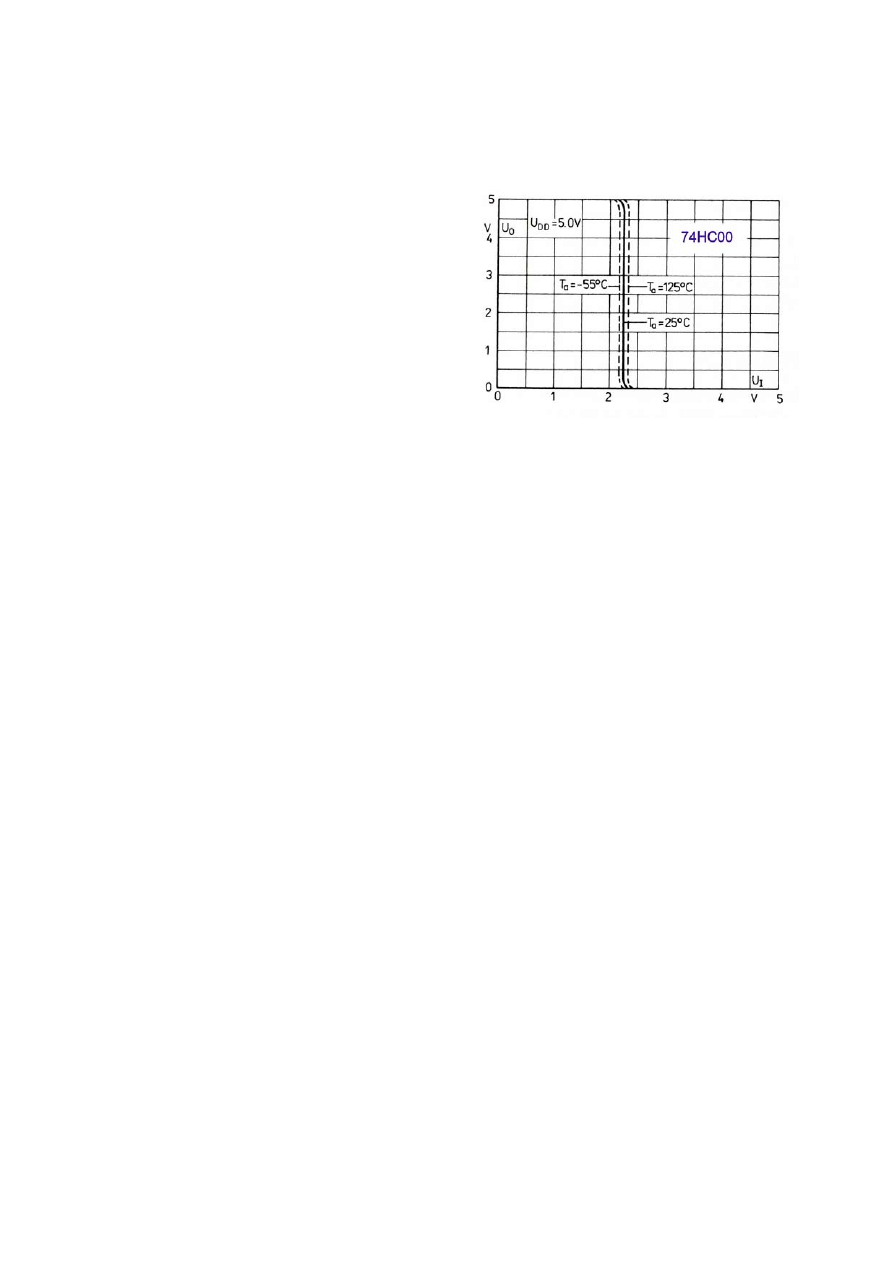

Margines zakłóceń

Wartości

typowe

napięcia

wyjściowego struktury CMOS

przy obciążeniu innymi

układami CMOS

:

U

OH typ

= U

DD

, U

OL typ

= 0

Typowa

wartość napięcia

progowego: U

T

= U

DD

/2

Typowy

margines zakłóceń: 0.45 U

DD

(bliski ideału!)

Wartości

najgorsze

napięcia wyjściowego zależą od serii. Np.

dla serii 74HC, przy U

DD

= 4.5 V :

U

OL

max

= 0.1 V,

U

IL

max

= 1.35 V

U

OH

min

= 4.4 V,

U

IH

min

= 3.15 V

Gwarantowane

marginesy zakłóceń

M

L

min

= 1.35 – 0.1 = 1.25 V

M

H

min

= 4.4 – 3.15 = 1.25 V

czyli M / U

DD

= 1.25 / 4.5 ≈ 0.28

• Generalnie przyjmuje się

gwarantowany

margines zakłóceń

układów CMOS o wartości 0.3 U

DD

.

• Przy obciążeniu układu CMOS układem TTL wartość M maleje

• Przy porównywaniu odporności na zakłócenia różnych rodzin i

serii trzeba również uwzględniać różnice wartości R

OL

i R

OH

© J. Kalisz, WAT, 2005

Wyszukiwarka

Podobne podstrony:

F2 17 Układy CMOS 1 Inwerter

F2 19 Układy CMOS 3 Parametry

F2 35A Układy CMOS 11 Przerzutniki

F2 34 Układy CMOS 13 Bramki transmisyjne

F2 28 Układy CMOS 7 Wejścia

F2 18 Układy CMOS 2 Struktury

F2 30 Układy CMOS 9 Szybkość działania

F2 29 Układy CMOS 8 Charakterystyki

F2 36 Układy CMOS 15 Wyjście trójstanowe

F2 33 Układy CMOS 12 Bramki transmisyjne

F2 27 Układy CMOS 6 Bramki

F2 26 Układy CMOS 5 Bramki

więcej podobnych podstron