Układ sterujący (część 1)

1

Przedmioty prowadzone w ramach

Programu Rozwoju WSFiZ w Białymstoku realizowane są w ramach

Programu Operacyjnego Kapitał Ludzki, Priorytet IV Szkolnictwo wyższe i nauka, Poddziałanie 4.1.1

Wzmocnienie potencjału dydaktycznego uczelni, współfinansowanego ze środków

Europejskiego Funduszu Społecznego (POKL.04.01.01-00-030/08)

8.

Układ sterujący (część 1)

Spis treści

8.1

Wstęp

Jak to już było powiedziane układ sterujący (US) jest „mózgiem” procesora: potrafi rozpoznać

rozkaz i uruchomić sekwencję kolejnych kroków wykonywanych przez ALU oraz sekwencję

przesłań pomiędzy różnymi rejestrami procesora, która to sekwencja prowadzi do wykonania

wyżej wymienionego rozkazu. Sekwencje takie występują przy realizacji każdej z faz cyklu

rozkazu. Najbardziej rozbudowane są przy realizacji złożonych operacji ALU, takich jak np.

mnożenie czy dzielenie.

Znane są dwie metody realizacji układów sterujących. Pierwsza z nich, nazywana hardware’ową,

polega ma zbudowaniu układu ze standardowych bramek logicznych (docelowo układu VLSI –

ang. very large scale integration) i druga, która realizuje go jako tzw. układ mikroprogramowany.

Metoda pierwsza ze względu na hardware’ową realizację algorytmów sterujących jest szybsza,

ale raz stworzony układ jest praktycznie niezmienialny. Druga - realizuje istotną część

algorytmów sterujących w oparciu tzw. mikroprogram zapamiętany w specjalnie do tego

przeznaczonej pamięci. Jest od tej pierwszej wolniejsza, ale koncepcyjnie bardziej klarowna,

dająca szansę na wprowadzenie zmian w stosunku do wcześniej uruchomionej wersji. Ideę

takiego rozwiązania ogłosili w 1951r. Wilkes i Stringer. Możliwości realizacyjne otworzyły sie

przed nią dopiero po wprowadzeniu układów scalonych LSI (ang. large scale integration,) i

VLSI. Rozdział ten poświęcony jest omówieniu właśnie tej metody jak i realizującego ją układu

(często nazywanego mikrokontrolerem).

8.2

Struktura podstawowa i zasady działania

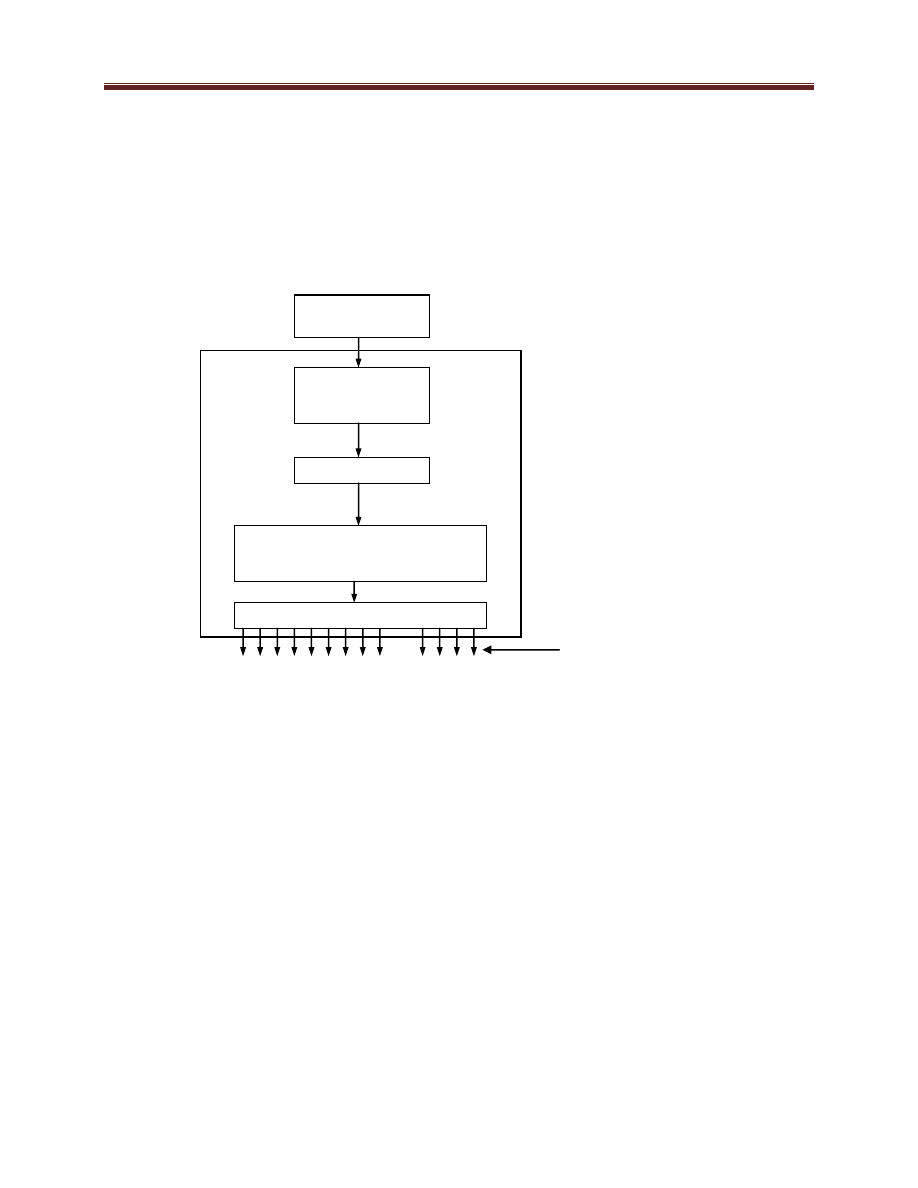

Podstawowa struktura mikroprogramowanego układu sterującego pokazana jest na rysunku 8.1

(patrz niżej).

Przypomina ona nieco (zwłaszcza w działaniu, o czym za chwilę) strukturę procesora. Dla

odróżnienia obu struktur między sobą oraz dla podkreślenia, że w przypadku US chodzi o

strukturę działającą o poziom głębiej (tj. wewnątrz procesora), a w związku z tym w sposób dużo

Układ sterujący (część 1)

2

bardziej elementarny, używa się przedrostka mikro- i to zarówno do niej samej jak i do jej

składowych.

Informacją wejściową dla US jest zawartość rejestru rozkazów, a więc kod realizowanego

rozkazu. Funkcjonalnie pierwszym zadaniem US jest zdekodowanie tego rozkazu, tj. określenie

na podstawie zapisanych w nim wartości bitów sekwencji działań, które ma podjąć procesor. W

przyjętym modelu procesora każde jego elementarne działanie dotyczy albo polecenia przesłania

informacji pomiędzy wskazanymi rejestrami albo zlecenia wykonania określonej operacji przez

ALU lub pamięć.

IR

Generator

Adresów

Początkowych

μPC

Pamięć sterująca

Słowo sterujące

...

sygnały sterujące

Rysunek 8.1. Struktura mikrokontrolera

Ponieważ przesyłanie informacji wewnątrz procesora zachodzi za pośrednictwem jego

wewnętrznej szyny to każde przesłanie między rejestrem Ri a Rj jest w istocie przesłaniem

pomiędzy rejestrem Rj a szyną, a następnie szyną a rejestrem Rj. Wydanie dowolnego z tych

poleceń polega na wygenerowaniu odpowiedniego sygnału sterującego. Liczba wszystkich

sygnałów sterujących jest skończona i silnie zależy od ilości elementów składowych procesora

biorących udział w realizacji rozkazów. Można je zapisywać w słowie pamięci w taki sposób, że

każda czynność będzie związana z bitem o konkretnym, ustalonym numerze. Wartość bitu 1

oznacza konieczność wygenerowania sygnału, 0 oznacza brak takiej konieczności. Ilość bitów w

słowie byłaby równa ilości sygnałów sterujących. Generalnie, jeżeli w takim słowie w danej

chwili występuje k jedynek, to oznacza to konieczność jednoczesnego wygenerowania zestawu

(zbioru) k sygnałów sterujących. Jeżeli chcielibyśmy zapisać sekwencję zbiorów sygnałów

sterujących o określonym następstwie w czasie (tzn. żeby jeden, określony zbiór sygnałów został

wygenerowany przed innym, wskazanym zbiorem sygnałów) to wystarczy ułożyć sekwencję

odpowiadających tym zbiorom słów. Tak rozumiane słowo nazywać będziemy mikrorozkazem, a

sekwencję słów – mikroprogramem.

Jak to widać na rysunku 8.1 (wyżej) w skład układu sterującego wchodzi pamięć (nazywana

pamięcią sterującą albo mikropamięcią), w której zapisane są mikroprogramy realizujące

Układ sterujący (część 1)

3

wszystkie rozkazy z listy rozkazów procesora. Można powiedzieć, że wykonanie rozkazu

oznacza wykonanie odpowiadającego mu mikroprogramu.

GAP

mikropamięć adresy

0

1

...

215

k mikro-

216

rozkazów

programu

... realizującego

rozkaz o kodzie

215+k C4 (MULL3)

...

Rysunek 8.2. Struktura GAP

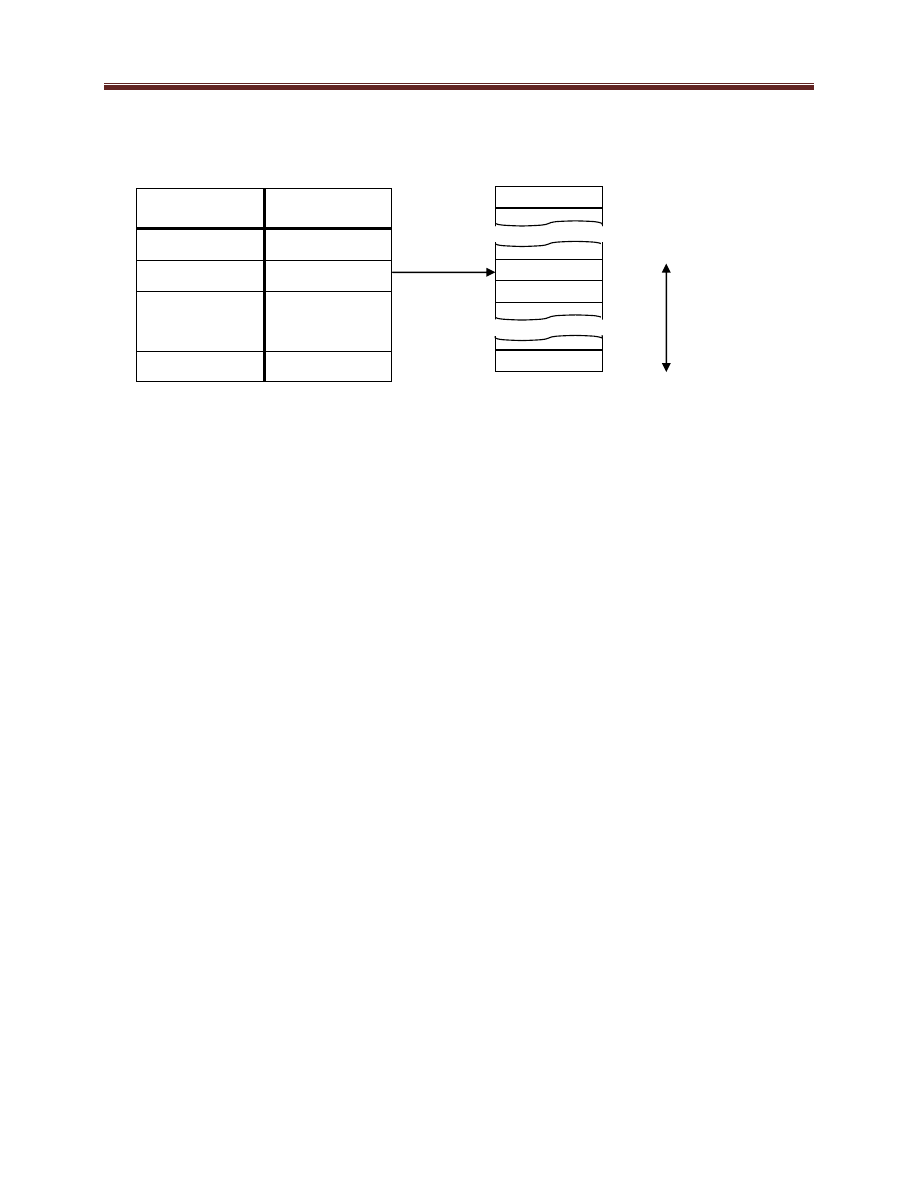

Informacje o początkowych adresach każdego z programów zapisane są w bloku Generatora

adresów początkowych (GAP). Blok ten realizuje odwzorowanie: kod r rozkazu procesora →

adres pierwszego mikrorozkazu realizującego rozkaz r (patrz rysunek 8.2 wyżej). Sięganie do

mikropamięci i odczytywanie z niej mikrorozkazów działa analogicznie jak sięganie do pamięci

komputera i odczytywanie z niej rozkazów programu. Tak jak na poziomie procesora

specjalizowany rejestr przechowuje adres następnego rozkazu do wykonania – jest to jak

wiadomo licznik programu (PC), tak na poziomie układu sterującego rolę tą pełni mikrolicznik

programu (μPC). To do niego ładowany jest adres wygenerowany przez GAP. Następnie

realizowane są czynności znane z opisu fazy pobierania rozkazu cyklu rozkazowego procesora.

Na rysunku 8.2 pokazana jest przykładowa lokalizacja w mikropamięci k mikrorozkazów

realizujących rozkaz procesora o kodzie C4. Mikroprogram rozpoczyna się od adresu 215

wyznaczonego przez Generator Adresów Początkowych na podstawie kodu rozkazu. W

podrozdziale 7.8 Przykład założyliśmy, że jest to kod rozkazu MULL3.

Oprócz podobieństw w realizacja rozkazu i mikrorozkazu są również istotne różnice. Po

pierwsze: mikrorozkazy nie mają argumentów, a więc w cyklu realizacji mikrorozkazu brak jest

fazy lub faz pobierania argumentu(ów). Po drugie – faza wykonania rozkazu polega na przesłaniu

zlecenie do ALU. W układzie sterującym odpowiada ona fazie wykonania mikrorozkazu, która

polega na umieszczenie aktualnie wskazywanego przez μPC słowa mikropamięci sterującej w

słowie sterującym (patrz rysunek 8.1 wyżej). Słowo sterujące jest rodzajem rejestru mającego

dokładnie tyle bitów, ile jest w każdym słowie pamięci sterującej. Jest ono w stanie

wygenerować sygnały sterujące z tych pozycji, na których w załadowanym do niego słowie

pamięci są jedynki. Natura tych sygnałów zostanie omówiona w rozdziale 8.2 Sygnały sterujące.

Zapisywanie mikroprogramów w pamięci sterującej stwarza ciekawą możliwość modyfikacji

fragmentów lub całości mikroprogramu przeprowadzonej w celu np. zamiany algorytmu

mnożenia na inny (krótszy, szybszy, generalnie uznany za lepszy). Ponieważ mikropamięć

sterująca jest realizowana najczęściej na pamięciach typu ROM (patrz rozdział 9.2.1.2

Klasyfikacja ze względu na technologię wytwarzania), to możliwość taka jest mocno ograniczona

(przynajmniej dla zwykłych użytkowników). Tym niemniej na poziomie producenta jest całkiem

realne wytwarzać komputery różniące się jedynie zawartością mikropamięci, a więc

kod rozkazu

adres

C4

215

....

....

Układ sterujący (część 1)

4

realizującego instrukcje tego samego procesora inaczej albo realizujące zupełnie inne zestawy

instrukcji.

8.3

Sygnały sterujące

Jak to już było powiedziane sygnały sterujące służą spowodowaniu transferu informacji z

rejestrów na szynę wewnętrzną procesora, z szyny do rejestrów, przesłaniu do ALU informacji o

tym, który z rozkazów ma wykonać bądź przesłaniu do pamięci informacji o żądanej operacji.

Można wyobrażać sobie, że infrastruktura niezbędna do przesyłania tych sygnałów składa się z

bardzo wielu połączeń elektrycznych oplatających wszystkie części składowe procesora. Ze

względu na realizację procesora w technologii VLSI te połączenia realizowane są środkami

adekwatnymi dla tej technologii.

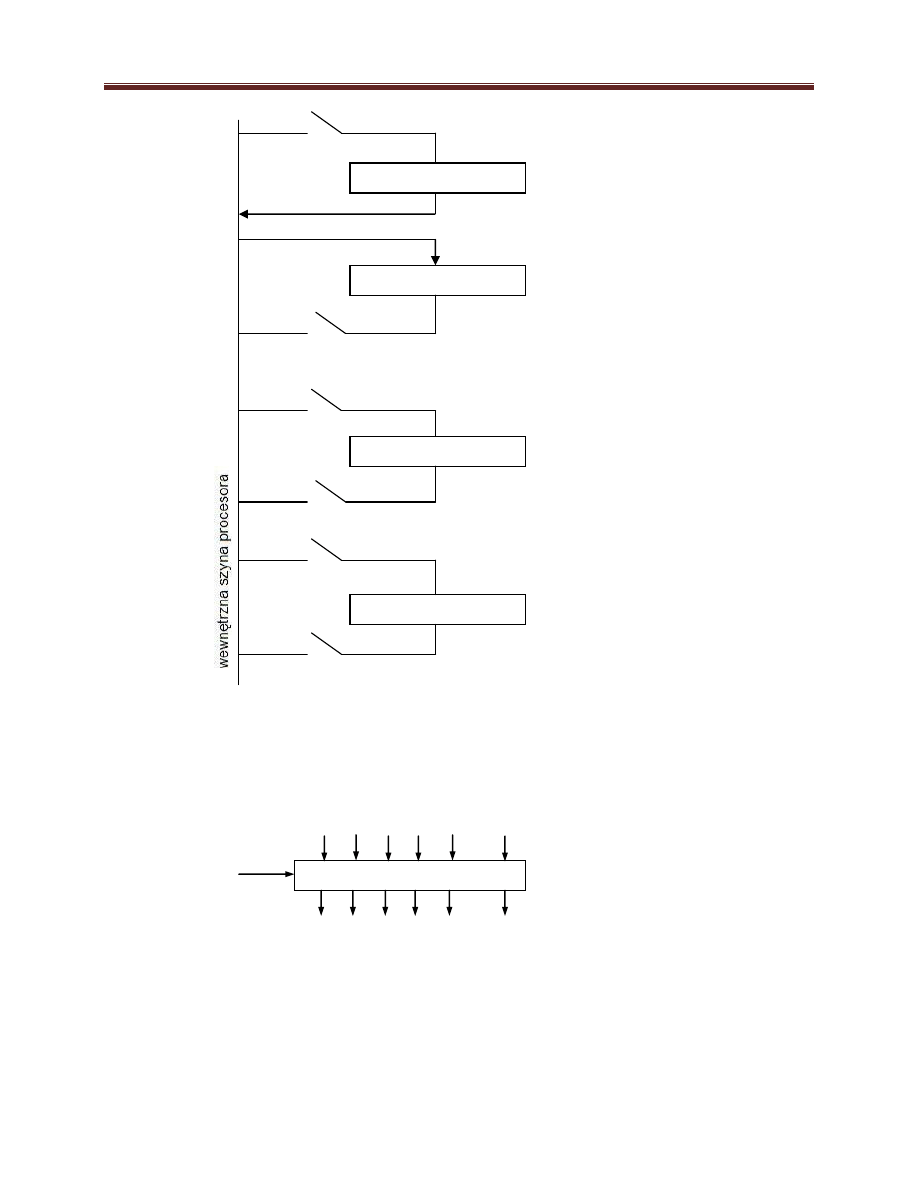

Zajmiemy się nieco bliżej tymi sygnałami. Zaczniemy od połączeń szyna – rejestry. Jest jasne,

że każdy z rejestrów potrzebuje połączeń umożliwiających załadowanie go sygnałami z szyny

oraz niezależnych połączeń umożliwiających wprowadzenie na szynę sygnałów zdefiniowanych

przez bity rejestru. Wyjątkiem jest rejestr adresowy pamięci MAR, którego zawartość jest

wyłącznie ładowana z szyny. Jest również jasne, że jeżeli ładujemy wskazany rejestr, to wejścia

pozostałych rejestrów powinny być w czasie ładowania odcięte od możliwości pobierania

sygnałów z szyny. Podobnie: jeżeli sygnały na szynie mają być ustawione przez stan bitów

wskazanego rejestru, to wyjścia pozostałych rejestrów powinny być w czasie ustawiania odcięte

od szyny. Idea przedstawiona jest rysunku 8.3 (patrz niżej), na którym przez Ri

in

oznaczono

przełącznik wejściowy rejestru i, a przez Ri

out

przełącznik wyjściowy rejestru i; i=0, …, 15.

Przedstawia on sytuację, w której rejestr R0 wprowadza sygnały na szynę (

R0

out

zwarte

). Sygnały

te odczytuje z szyny rejestr R1 (

R1

in

zwarte

).

Pozostałe rejestry mają w tym czasie elektrycznie

odcięte od szyny wejścia przez przełączniki wejściowe (Ri

in

rozwarte, i=0,2,3, … ,15), oraz

wyjścia – przez przełączniki wyjściowe (Ri

out

rozwarte, i=1,2,3, … ,15). Pojedyncze linie,

których użyto do przedstawienia szyny procesora oraz jej połączeń z rejestrami należy rozumieć,

jako zestaw n połączeń, gdzie n jest szerokością szyny i jednocześnie ilością bitów w rejestrach.

Rejestry są dostępne na rynku jako układy realizowane w technice MSI (ang. middle scale

integration). Co prawda nasze rejestry są wewnętrznymi rejestrami procesora, ale przyjmijmy, że

mechanizm działania jest w obu przypadkach jednakowy.

Układ sterujący (część 1)

5

R0

in

R0

R0

out

R1

in

R1

R1

out

…

Ri

in

Ri

Ri

out

...

R15

in

R15

R15

out

Rysunek 8.3. Konfiguracja przełączników rejestry – szyna przy transferze R0→R1.

Tak więc rejestry mają ustaloną logikę działania zdeterminowaną przez swoją podstawową

funkcję, tj. zapamiętywania podawanego na ich wejście słowa. Stąd rejestr taki ma n wejść i

wyjść oraz dodatkowe wejście sterujące „ładuj”, którego uaktywnienie (przez podanie sygnału

ładuj = 1) powoduje wpisanie i zatrzaśnięcie w rejestrze aktualnego stanu wejść (patrz rysunek

8.4).

we

1

we

2

we

3

we

4

we

5

we

n

...

ładuj

...

wy

1

wy

2

wy

3

wy

4

wy

5

wy

n

Rysunek 8.4. Funkcjonalny model n-bitowego rejestru.

Wejście „ładuj” może z powodzeniem pełnić rolę sygnału sterującego pracą przełącznika R

in

z

rysunku 8.3 (patrz wyżej). Natomiast przełącznik R

out

należy zrealizować jako dodatkowy układ,

ponieważ logika działania rejestru nie przewiduje istnienia czegoś w rodzaju funkcji:

„wyprowadź zapamiętane sygnały na wyjście” – w każdym standardowym rejestrze są one

dostępne na wyjściach w każdej chwili.

Układ sterujący (część 1)

6

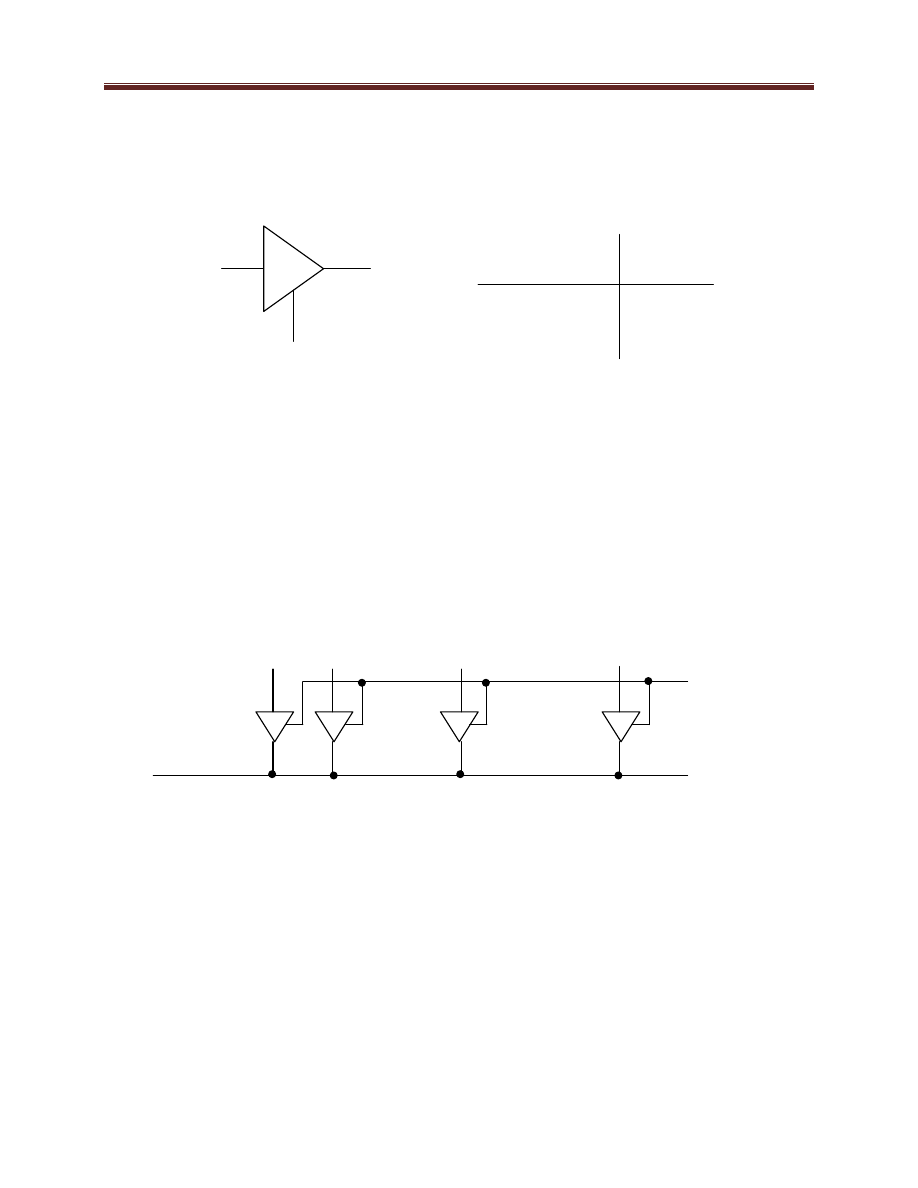

Istnieje specjalny rodzaj bramek, nazywanych bramkami 3-stanowymi albo układami 3-

stanowymi, skonstruowany dokładnie w celu realizacji sterowania elektryczną separacją

(odcięciem) wyjścia z jednego i wejścia do dowolnego, innego układu. Schemat takiej bramki i

tabelę definiującą jej działanie pokazano na rysunku 8.5.

Wejście

Wyjście

Wejście sterujące Wyjście

0

Odcięte

1

Wejście

Wejście

sterujące

Rysunek 8.5. Schemat układu 3-stanowego i tabela definiująca jego działanie.

Jak wynika z tabeli działania bramki 3-stanowej jeżeli na jej wejście sterujące podamy sygnał

zero, to odcinamy wejście od wyjścia. Oznacza to nie tylko, że przy sterowaniu równym 0 żadne

zmiany na wejściu nie przedostają się na wyjście ale przede wszystkim to, że z punktu widzenia

układu, do którego wejścia podłączono wyjście bramki 3-stanowej wspomniane podłączenie nie

istnieje.

Natomiast przy sterowaniu równym 1 wyjście bramki jest równe jego wejściu, czyli sygnały

wejściowe, jakie by nie były ich wartości (u nas 0 albo 1), przedostają się na wyjście. Na rysunku

8.6 (patrz niżej) pokazano sposób zainstalowania bramek 3-stanowych pomiędzy szyną procesora

a wyjściami rejestru. Wejścia sterujące wszystkich bramek są zwarte i sygnał podawany na nie

pełni rolę sygnału sterującego pracą przełącznika R

out

z rysunku 8.3 (patrz wyżej).

Wyjścia z rejestru: wy

1

wy

2

... wy

i

...

wy

n

R

out

...

...

Szyna wewnętrzna

procesora

Rysunek 8.6. Funkcjonowanie bramek 3-stanowych jako przełącznika

R

out

.

Wniosek, jaki wynika z powyższych rozważań jest taki, że układ sterujący musi przesyłać dwa

niezależne sygnały sterujące na każdy rejestr (poza rejestrem adresowym pamięci MAR, który

wymaga tylko jednego sygnału sterującego) Ri

in

i Ri

out

, gdzie i jest numerem rejestru, i = 0, 1, ... ,

15. Ri

in

jest połączone z wejściem sterującym „ładuj” rejestru Ri, a Ri

out

jest połączone z

wejściem sterującym zbioru bramek 3-stanowych (po n bramek na każdy n-bitowy rejestr), każdy

zbiór w układzie takim, jak na rysunku 8.6. Oznacza to również konieczność pamiętania w

mikrorozkazie wszystkich wymienionych sygnałów sterujących, aby na podstawie wartości

odpowiadającym im bitów słowo sterujące mogło wygenerować wspomniane sygnały.

Układ sterujący (część 1)

7

8.4

Grupowanie sygnałów sterujących

Wnioski postawione na końcu poprzedniego podrozdziału ujawniły jedną z głównych wad

mikroprogramowanej wersji układu sterownia. Jest nią konieczność przeznaczenia 1 bitu słowa

sterującego na każdą mikrooperację. W rezultacie uwzględnienia wszystkich niezbędnych

mikrooperacji liczba bitów w słowie sterującym może sięgnąć 200. Dla przykładu spróbujemy

oszacować tą liczbę dla modelu procesora wprowadzonego w rozdziale 7. Do 32 bitów

przeznaczonych do obsługi rejestrów należy dodać 3 bity do obsługi interakcji z pamięcią

(Czytaj/Pisz/Czekaj na pamięć), 3 kolejne na obsługę rejestrów pamięci (2 dla MDR i 1 dla MAR

– do niego tylko piszemy). Jeżeli skromnie założymy, że nasze ALU wykonuje 16 operacji to tyle

kolejnych bitów należy dołożyć do słowa sterującego. Już ich mamy ponad 50, a przecież nie

zostały uwzględnione bity do obsługi licznika rozkazów PC, rejestru rozkazów IR, czy do

obsługi, jak dotychczas wcale nierozważanych, urządzeń WE/WY.

Pomysł, który załagodził ten problem polegał na dwu-krokowej procedurze. Pierwszy krok

polegał na wyszukaniu wśród sygnałów sterujących grup takich sygnałów, które się między sobą

wzajemnie wykluczają, co oznacza, że w każdej z takich grup w danej chwili może wystąpić

tylko jeden sygnał. Załóżmy, ze taka grupa istnieje i że liczy n sygnałów. Zamiast przechowywać

n sygnałów można przechowywać tylko liczbę k, która jest tak dobrana aby n = 2

k

. Znając k

można wyliczyć na podstawie podanej zależności n i wygenerować na linii o tym numerze sygnał

1. To, czego potrzebujemy to układ przekształcający k w n. Powyższe przekształcenie byłoby

krokiem numer 2 wspomnianej wcześniej procedury.

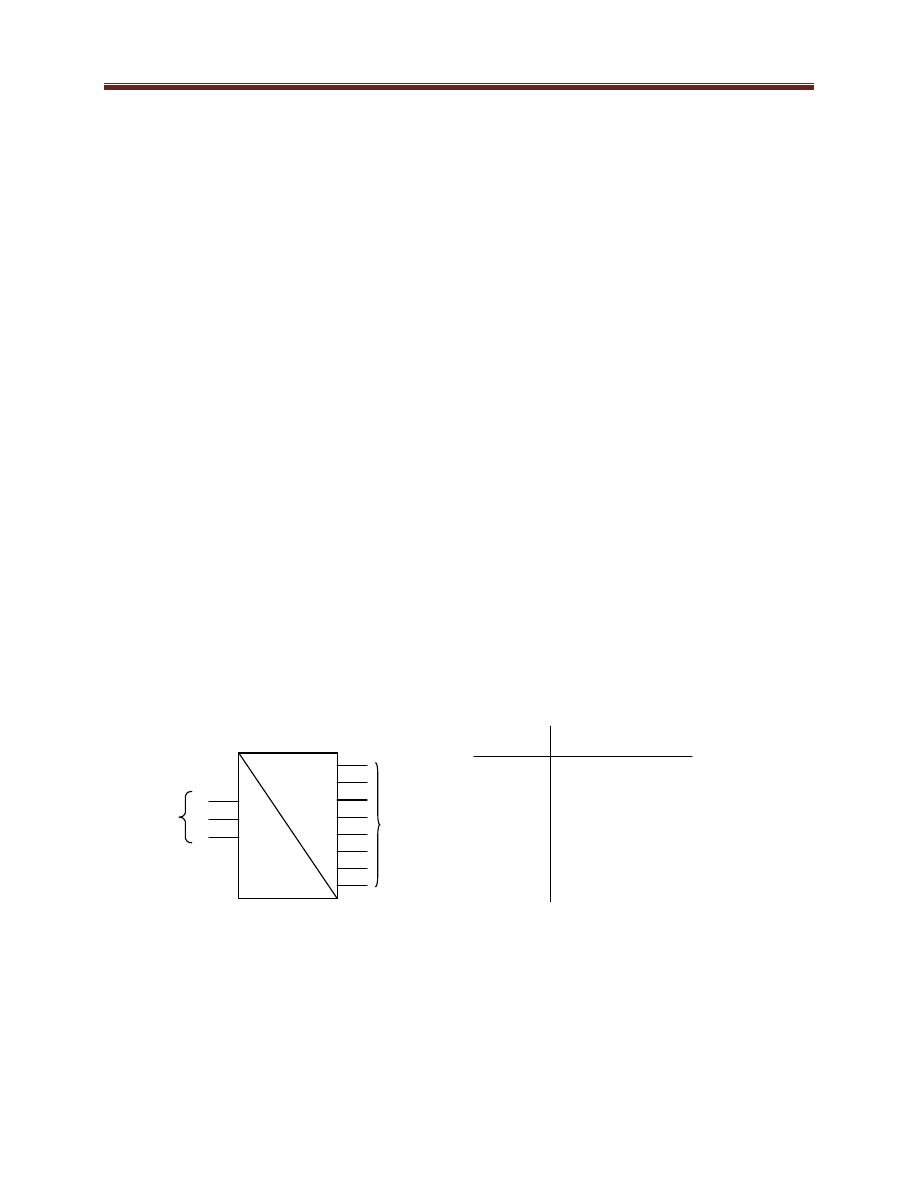

Okazuje się, że wytwarzany w technologii MSI i od dawna oferowany na rynku układ o nazwie

dekoder ma dokładnie pożądane przez nas własności. Jest to układ, który akceptuje na wejściu

zakodowaną binarnie liczbę i wytwarza jedynkę na tym wyjściu (ma ich tyle, ile możliwych do

zakodowania liczb wejściowych), którego numer odpowiada liczbie wejściowej (patrz rysunek

8.7). Jeżeli liczba wejściowa ma k bitów, to wyjść jest 2

k

. Jak widać z tabeli na rysunku 8.7

jedynka pojawia się dokładnie na jednym z nich (tzw. kod 1 z k). Np. jeżeli na wejście podamy

kombinację (101)

2

= 5

10

to jedynka pojawi się na wyjściu numer 4 (nie 5, bo liczymy od 0).

Dekoder będzie oznaczany przekreślonym ukośnie prostokątem,

wejścia

wyjścia

a b c 0 1 2 3 4 5 6 7

0

0 0 0 1 0 0 0 0 0 0 0

1

0 0 1 0 1 0 0 0 0 0 0

a

2

0 1 0 0 0 1 0 0 0 0 0

binarne b Dekoder 3

wyjścia

0 1 1 0 0 0 1 0 0 0 0

wejście c

4

1 0 0 0 0 0 0 1 0 0 0

5

1 0 1 0 0 0 0 0 1 0 0

6

1 1 0 0 0 0 0 0 0 1 0

7

1 1 1 0 0 0 0 0 0 0 1

Rysunek 8.7. Dekoder 3-bitowych liczb kodowanych w NKB.

Pierwszą grupą sygnałów, której liczność możemy w pokazany sposób zredukować są sygnały

przesyłające rozkaz do ALU. Przesyłać nimi będziemy zawsze tylko jeden rozkaz – tak więc

zamiast założonych 16 bitów możemy pamiętać tylko 4 (16 = 2

4

). Drugą taką grupą są sygnały

sterujące rejestrami. Jest ich dla 16 rejestrów 32: 16 do sterowania ich wejściem, a kolejne 16 –

wyjściem. Zauważmy, że przy dowolnych przesłaniach informacji wewnątrz procesora co

najwyżej jeden rejestr może mieć otwarte wyjścia (to z niego informacja trafia na szynę) oraz co

Układ sterujący (część 1)

8

najwyżej jeden może mieć otwarte wejścia (to on ma być załadowany informacją z szyny). Jeżeli

tak, to zakładając, że nie są możliwe bezpośrednie przesłania pomiędzy rejestrami ogólnego

przeznaczenia można numer rejestru zakodować na 4 bitach, a dwa kolejne przeznaczyć na

zapisanie czy z rejestru o podanym numerze czytamy (1 bit), czy też go ładujemy (1 bit). W

sumie zajęliśmy 6 bitów przy 32 na początku. Zysk całkowity wynosi 26 bitów (przy istotnym

założeniu uproszczającym).

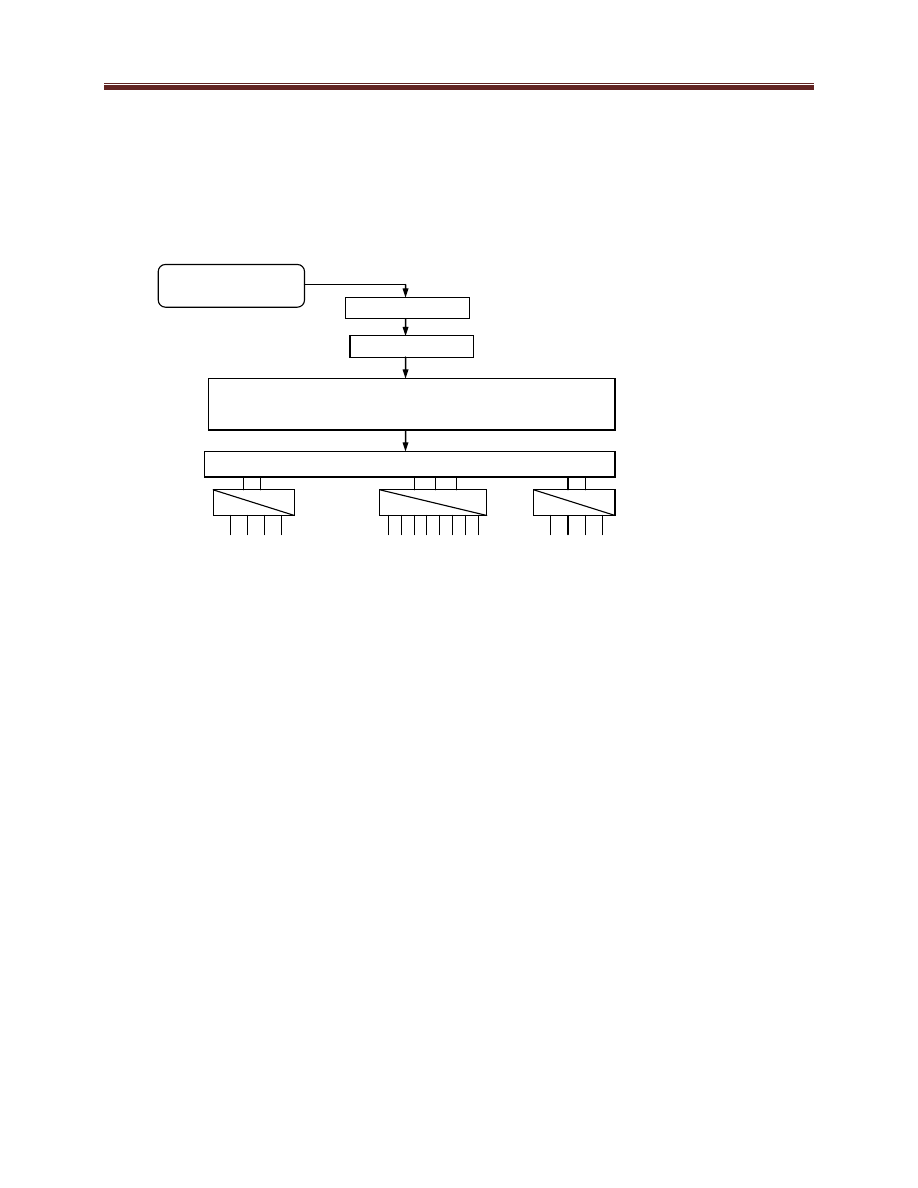

Rozkaz pobrany

z rejestru instrukcji

GAP

μPC

Pamięć

sterująca

Słowo sterujące

Dekoder

...

Dekoder

...

Dekoder

Rysunek 8.8. Układ sterujący maszyny mikroprogramowanej pionowo.

O komputerach z procesorami, w których zastosowano kodowanie podobne do opisanego

mówimy, że są maszynami mikroprogramowanymi pionowo (ang. vertical microprogrammed

machines), natomiast jeżeli mikroprogramowany układu sterujący zrealizowano bez kodowania –

to takie komputery nazywamy maszynami mikroprogramowanymi poziomo (ang. horizontal

microprogrammed machines). Ogólny schemat mikrokontrolera dla tych pierwszych jest

pokazany na rysunku 8.8 (patrz wyżej).

W praktyce stosowane są rozwiązania mieszane. Co do wydajności, to szybsze są procesory z

architekturą poziomą (sygnały mają mniej poziomów bramek do przejścia), które umożliwiają

ponadto współbieżne wykorzystywanie zasobów procesora. Są jednak (ze względu na długość

słowa) droższe od rozwiązań z architekturami pionowymi.

Przy tej okazji wprowadzenia niezwykle użytecznego (i to nie tylko w opisanym kontekście)

układu jakim jest dekoder, wprowadzimy jeszcze jeden układ pomocniczy nazywany

multiplekserem. Jest to układ, tak jak dekoder, wytwarzany w technologii MSI i również jak on

od dawna oferowany na rynku. Multiplekser realizuje funkcję wybierania jednego z wielu wejść.

Przekazuje on sygnał z wybranego wejścia na wyjście. Dokładnie: ma on n ponumerowanych

kolejno wejść sygnałowych i jedno wyjście. Ponadto ma k wejść sterujących (n = 2

k

), na które

można podać zakodowany binarnie numer wybranego wejścia sygnałowego. Podanie na te

wejścia kodu liczby i oznacza, że sygnał z wejścia o numerze i pojawi się na wyjściu

miltipleksera. Jednocześnie sygnały z pozostałych wejść będą elektrycznie odcięte od wyjścia

(patrz rysunek 8.9 niżej). Np. jeżeli sekwencja bitów sterujących s

2

s

1

s

0

= (110)

2

= 6

10

to y =

x

6

.

Układ sterujący (część 1)

9

x

0

x

1

x

2

x

3

y

x

4

x

5

x

6

x

7

s

2

s

1

s

0

Rysunek 8.9. Multiplekser o 8 wejściach sygnałowych i 3 wejściach sterujących.

Podana definicja i przykładowy miltiplekser z rysunku 8.9 odnoszą się do wyboru dokładnie

jednego z wejść. W praktyce często zachodzi konieczność wyboru grupy wejść. Np. można

rozważać sytuację wyboru jednego 32-bitowego słowa z 8 słów podanych na wejście. Taki

„słowowy” selektor ma wtedy 8*32 sygnały wejściowe i 32 sygnały wyjściowe, ale tylko 3

wejścia wybierające. Multipleksery wykorzystamy w kolejnych podrozdziałach.

Document Outline

Wyszukiwarka

Podobne podstrony:

8w Uklad sterowania 2 v04

8w Uklad sterowania 2 v04

Instrukcja do zad proj 13 Uklad sterowania schodow ruchom

Instrukcja do zad proj 19 Układ sterowania bramy garażu

Układ sterowania

Elementy bez-oczowe w elektronice- Czyli gawrych (Âci-ga), Ściągi do szkoły, Układ Sterowania i Regu

03 uklad sterowania magistrale i organizacja pamieci

Instrukcja do zad proj 17 Uklad sterowania prasy hydrauli

Jody polprzewodnikowe-sciaga, Ściągi do szkoły, Układ Sterowania i Regulacji

Układ sterowania fazowego na mikroprocesorze, elektro, 1, Podstawy Techniki Mikroprocesorowej

Gawrych2, Ściągi do szkoły, Układ Sterowania i Regulacji

Tyrystorowy układ sterownika 1 fazowego

Instrukcja do zad proj 13 Uklad sterowania schodow ruchom

Instrukcja do zad proj 19 Układ sterowania bramy garażu

Sekwencyjny układ sterowania wy¶wietlaczami LED

1997 09 Układ sterowania oświetleniem kabiny samochodu

więcej podobnych podstron