Układ sterowania, magistrale

i organizacja pamięci

Dariusz Chaberski

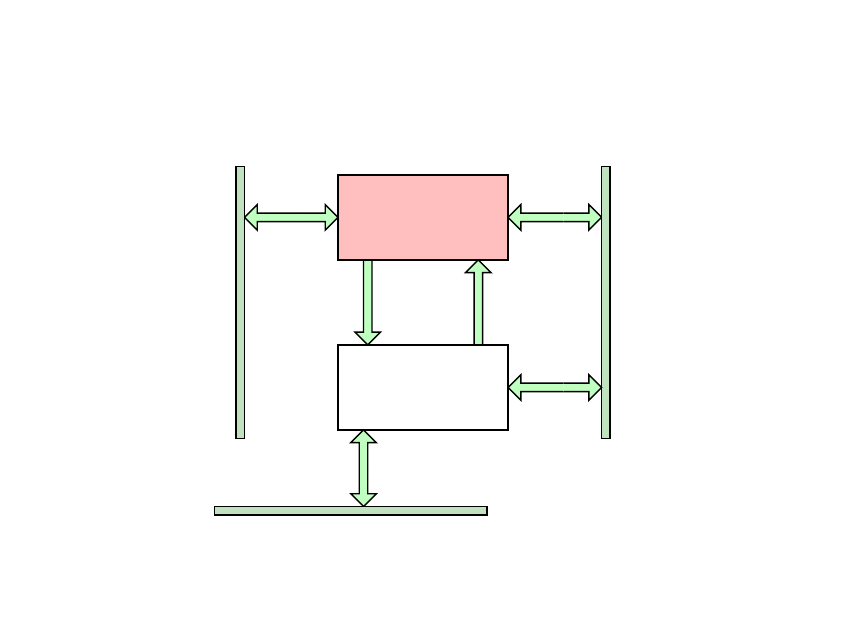

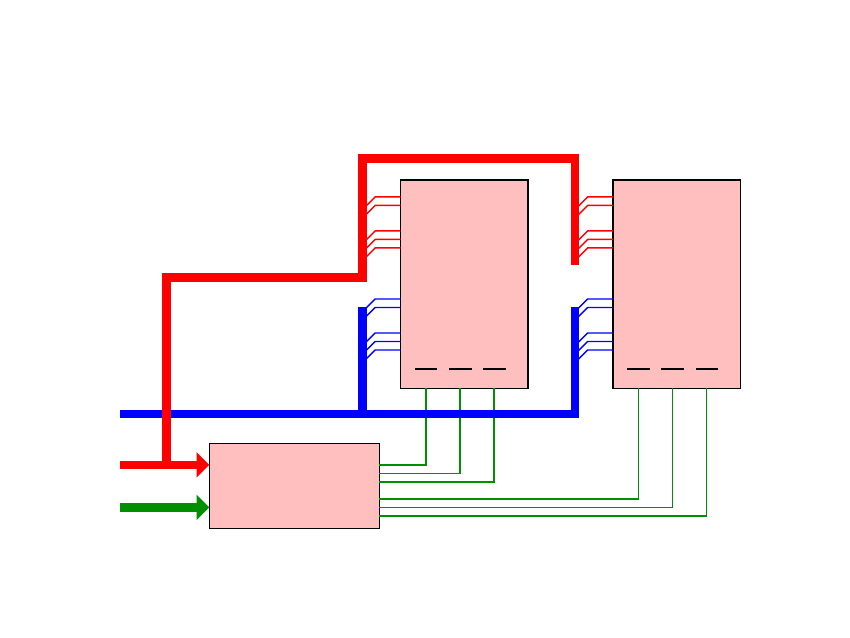

Jednostka centralna

układ

wykonawczy

układ

sterowania

sygnały

sterujące

sygnały

stanu

sz

y

n

a

sy

g

n

a

ło

w

st

er

o

w

a

n

ia

wewnętrzna

szyna adresowa

w

ew

n

ęt

rz

n

a

sz

y

n

a

d

a

n

y

ch

2

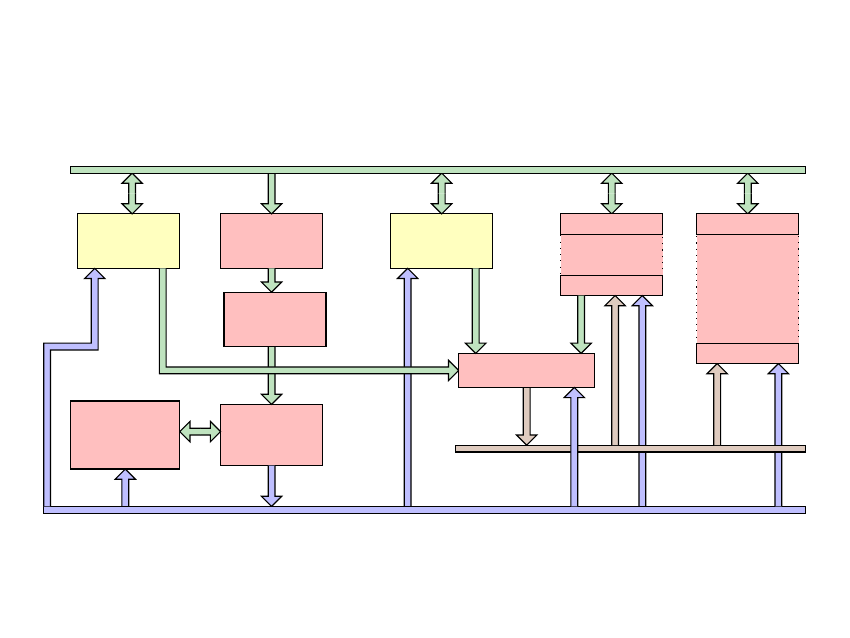

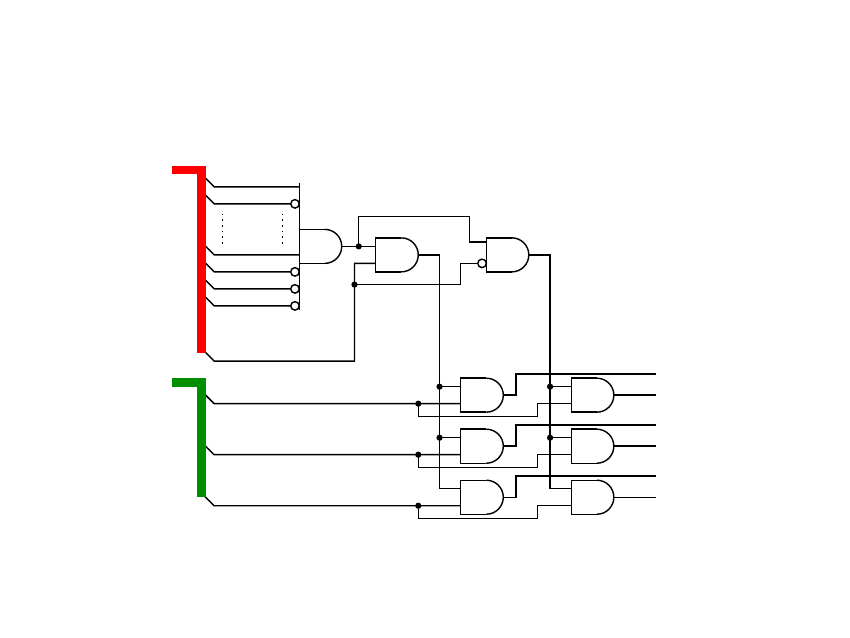

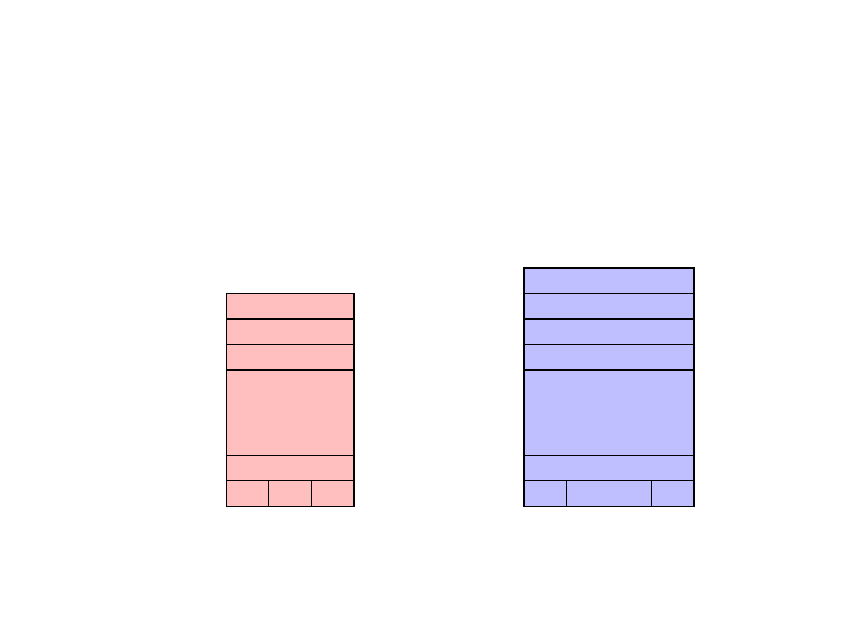

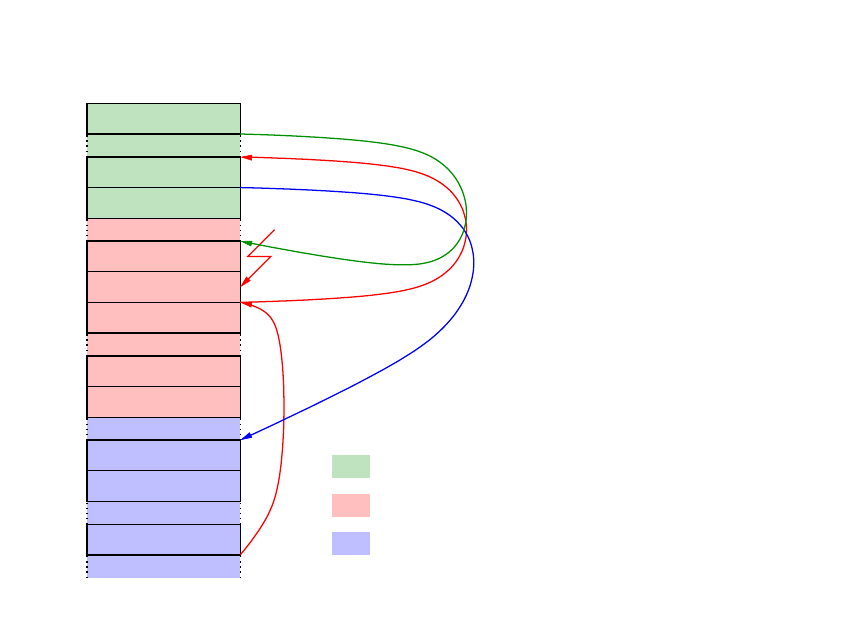

Układ sterowania

rejestr

rozkazów

generator

sygnałów

sterujących

licznik

programu

magistrala

danych

rejestry

indeksowe

magistrala

sterująca

wskaźnik

stosu

układ obsługi

sytuacji

wyjątkowych

magistrala

adresowa

rejestry

ogólnego

przeznaczenia

lub pamięć

dekoder

rozkazów

rejestr adresowy

3

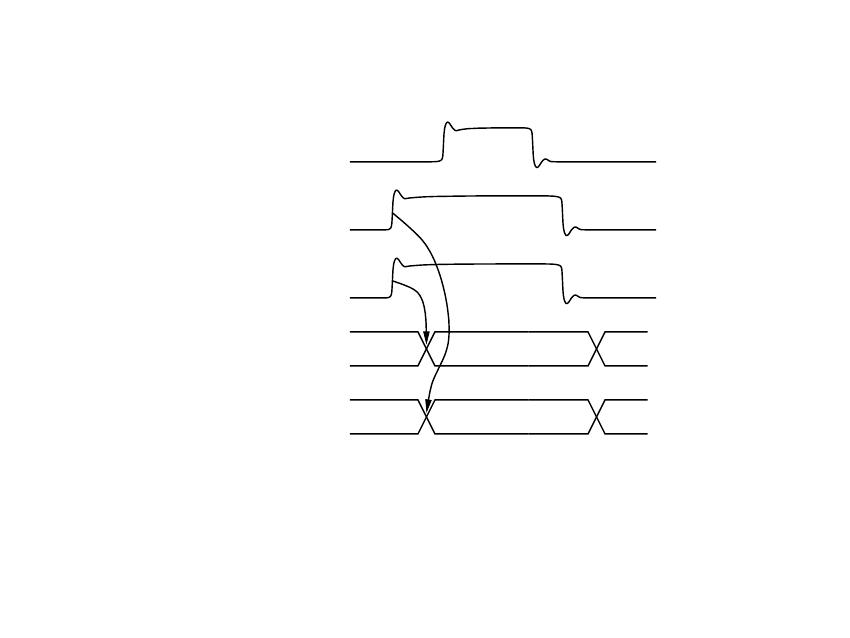

§ przykład sterowania - ochrona licznika programu PC

magistrala

danych

PC

magistrala

adresowa

SP

+1

PC

R

SP

RA

R

W

SP - wskaźnik stosu

PC

R

- odczyt licznika programu

SP

RA

- wystawienie wskaźnika stosu na magistralę adresową

R

W

- zapis magistrali danych do komórki pamięci, który znajduje się na magistrali adresowej

4

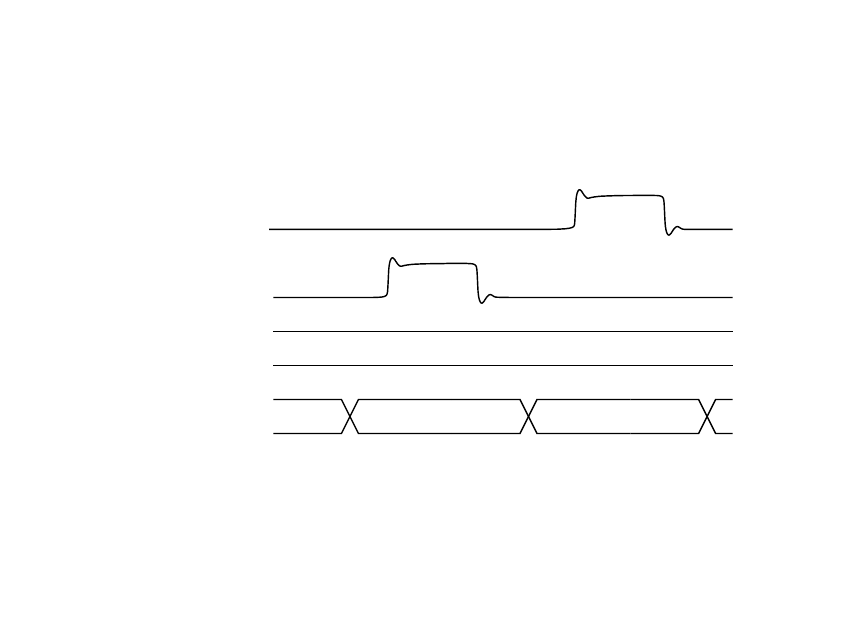

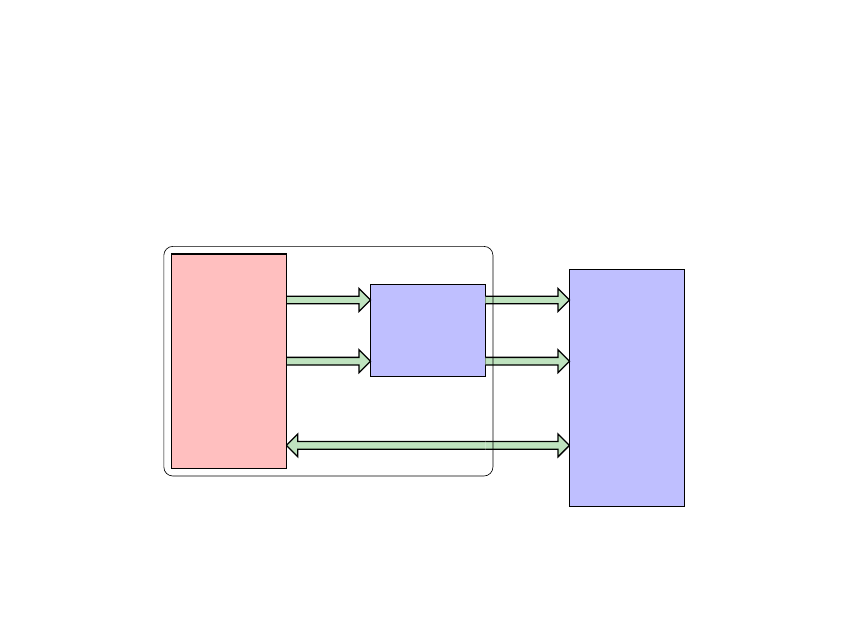

§ przykład sterowania - przesłanie pomiędzy rejestrami ogólnego przeznaczenia

magistrala

adresowa

R1

magistrala

danych

R

WS

R

WD

R2

R

WD/S

- zapis adresu rejestru przeznaczenia / źródła

R1/2 - nazwa (numer) rejestru źródła / przeznaczenia

5

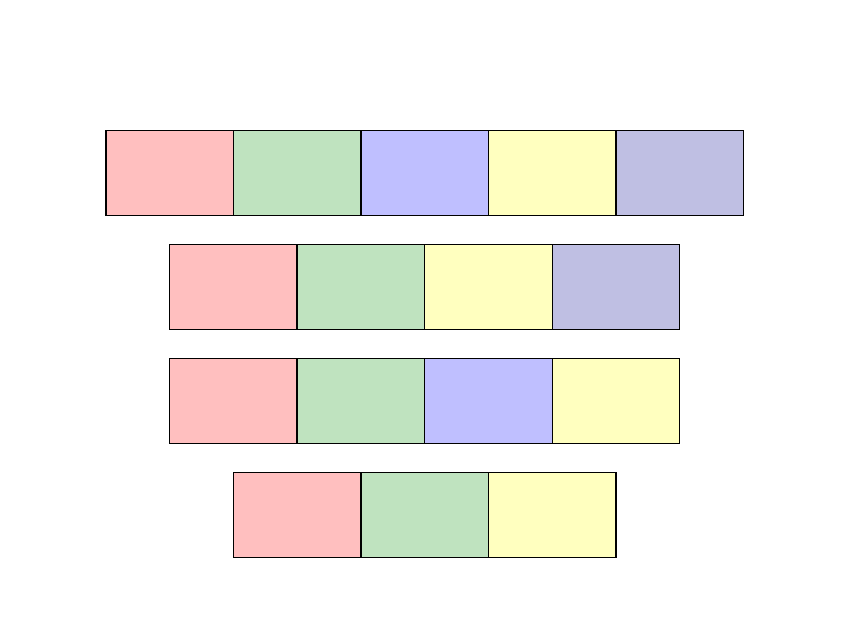

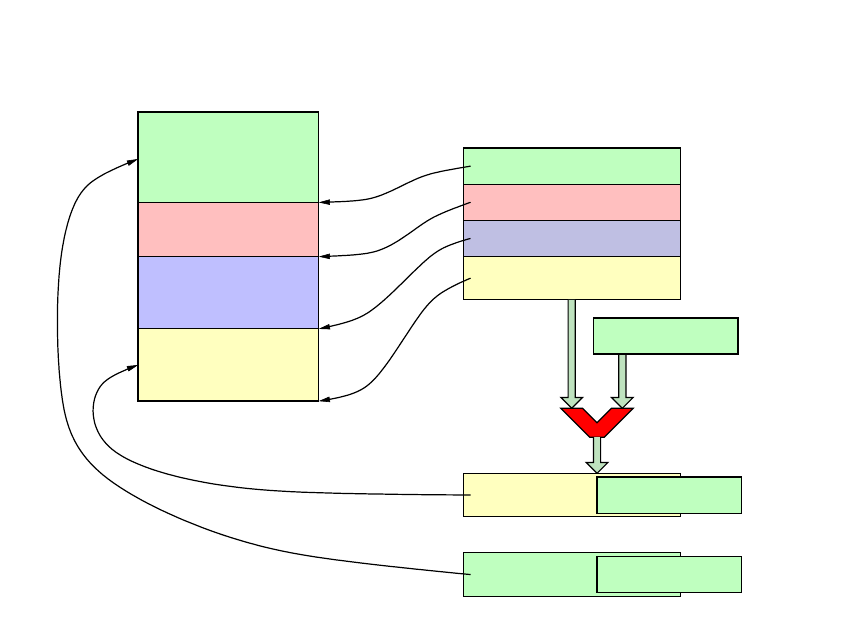

Cykl wykonywania instrukcji

dekodowanie

instrukcji

pobranie

kodu

instrukcji

odczyt

argumentów

wykonanie

instrukcji

zapisanie

wyniku

dekodowanie

instrukcji

pobranie

kodu

instrukcji

wykonanie

instrukcji

zapisanie

wyniku

dekodowanie

instrukcji

pobranie

kodu

instrukcji

odczyt

argumentów

wykonanie

instrukcji

pobranie

kodu

instrukcji

dekodowanie

instrukcji

wykonanie

instrukcji

6

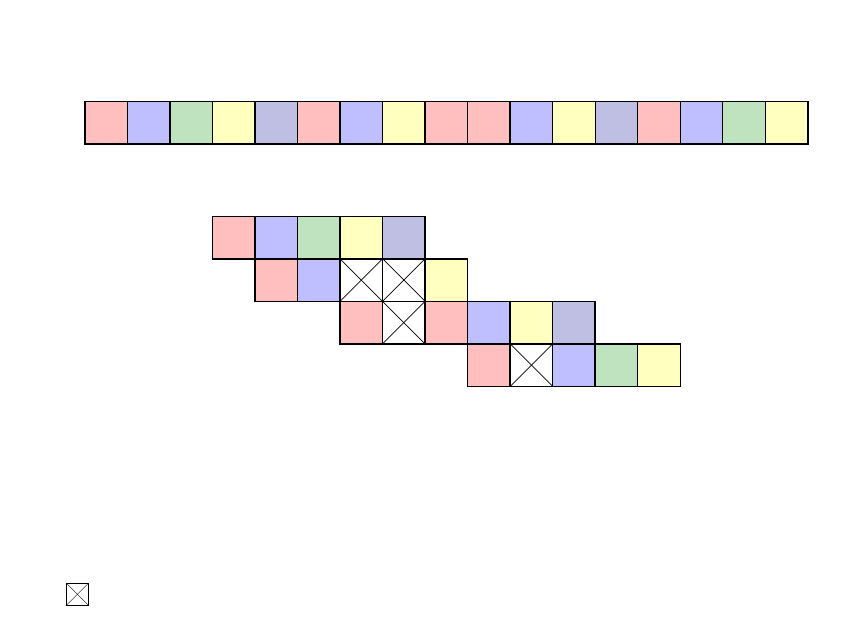

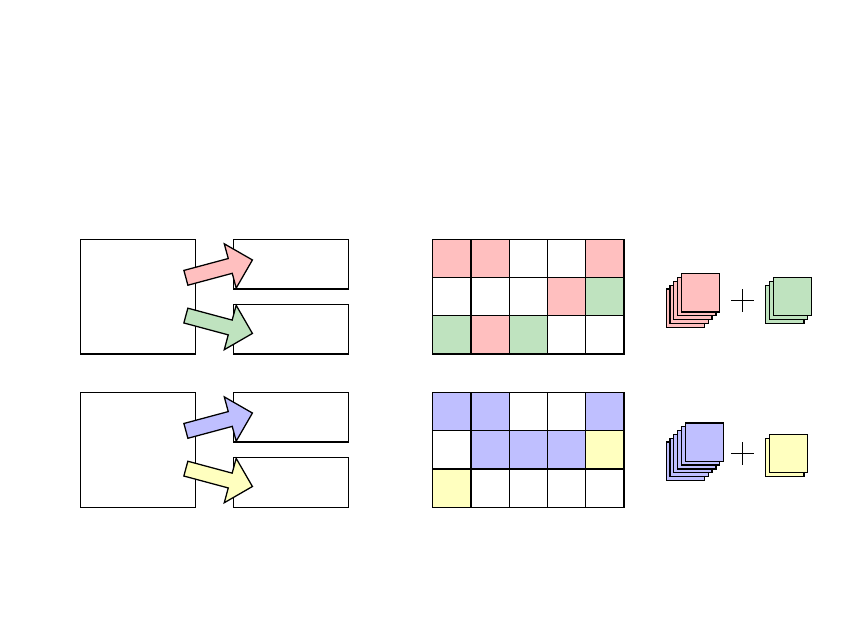

§ przetwarzanie sekwencyjne

E

W

F

D

R

F

D

E

W

F

D

R

E

D

E

F

F

§ przetwarzanie potokowe

E

W

F

E

F

D

D

E

W

F

D

R

E

R

D

F

F

F - pobranie kodu instrukcji

D - dekodowanie instrukcji

R - odczyt argumentów

E - wykonanie instrukcji

W - zapisanie wyniku

- oczekiwanie

7

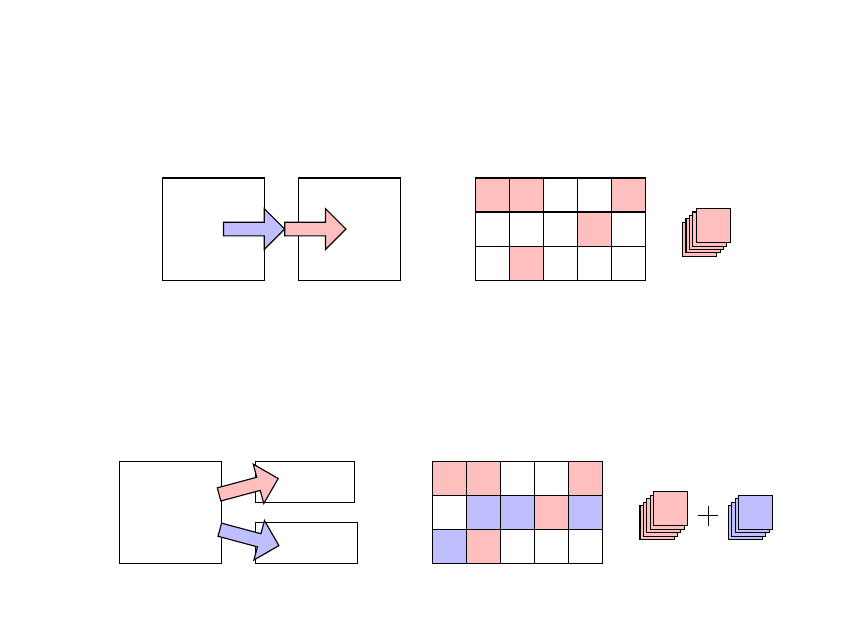

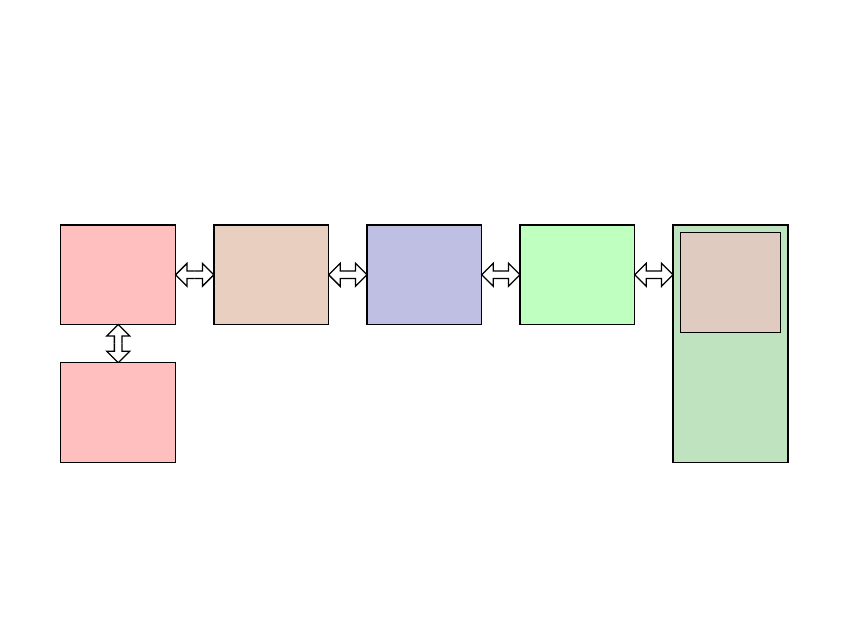

§ procesor standardowy

UW3

UW2

UW1

procesor

fizyczny

procesor

logiczny

UW1/2/3 - układy wykonawcze

§ procesor wielowątkowy -technologia HT (ang. Hyper-Threading)

UW3

UW2

UW1

procesor

fizyczny

procesor

logiczny

8

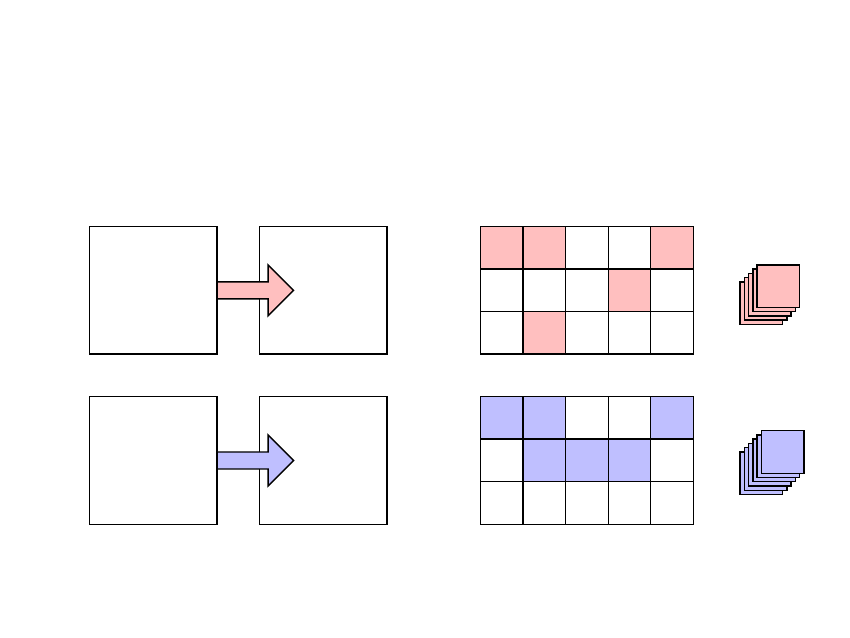

§ procesor dwurdzeniowy

procesor

fizyczny

procesor

logiczny

UW6

UW5

UW4

UW3

UW2

UW1

9

§ procesor dwurdzeniowy z technologią HT

procesor

fizyczny

procesor

logiczny

UW6

UW5

UW4

UW3

UW2

UW1

10

Magistrale

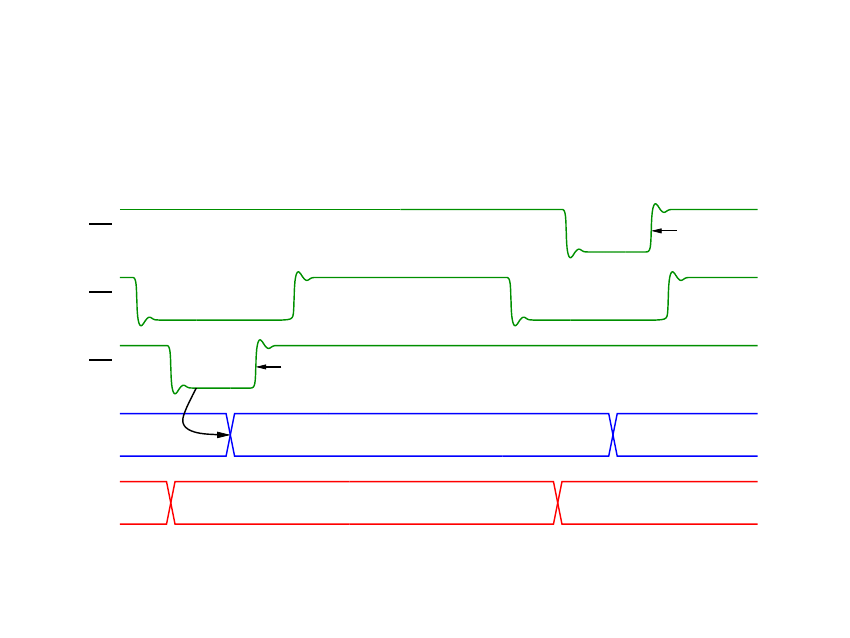

§ standard INTELA

CS

OE

WR

D

A

odczyt

zapis

11

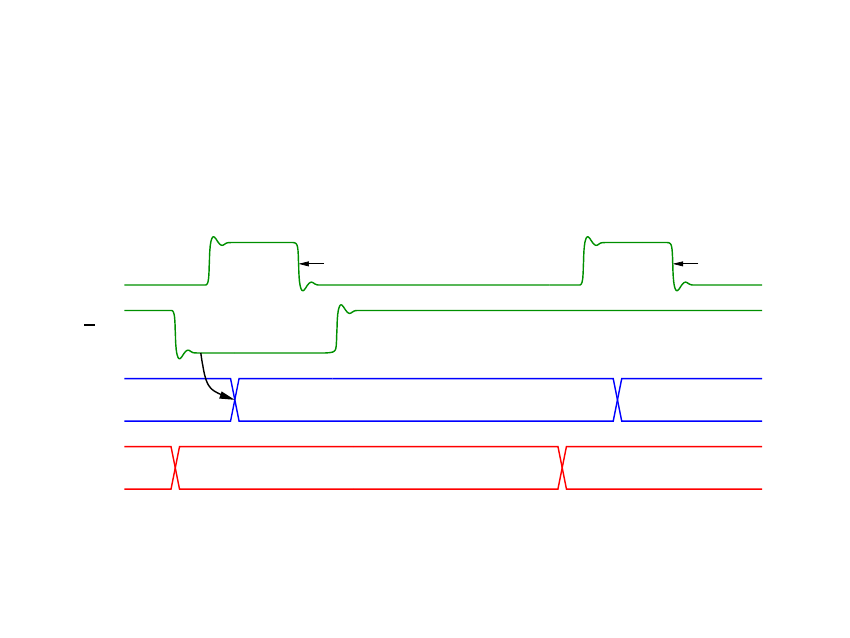

Magistrale

§ standard MOTOROLI

E

R

/W

D

A

odczyt

zapis

12

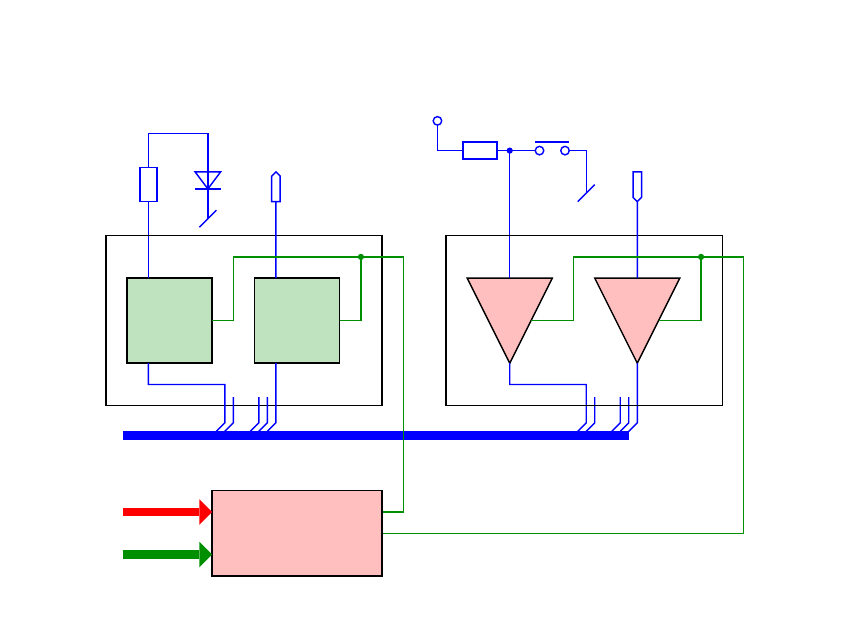

Układy wejścia wyjścia

D

D

Q

C

L

E

D

R

R

P

Q

C

IN

OUT

D

0

D

0

D

VCC

dekoder adresów

C

A

OE

OE

IN

OUT

13

Pamięć

dekoder adresów

C

A

D

A

n

−

1

A

0

D

m

−

1

D

0

A

k

−

1

A

0

D

m

−

1

D

0

OE WR CS

CS

OE WR

14

Dekoder adresów

A

z−1

A

n

A

n+1

OE1

WR1

CS1

OE2

WR2

CS2

CS

WR

OE

A

C

15

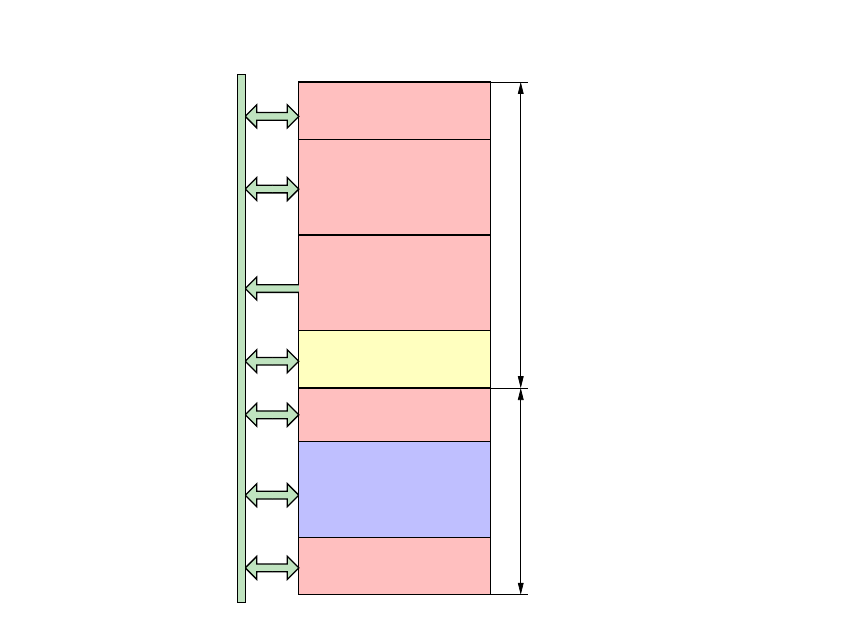

Mapa pamięci

rejestry ogólnego

przeznaczenia

układy wejścia wyjścia

rejestry indeksowe

pamięć programu

wektory przerwań

stos

pamięć danych

za

so

b

y

ze

w

n

ęt

rz

n

e

za

so

b

y

w

ew

n

ęt

rz

n

e

16

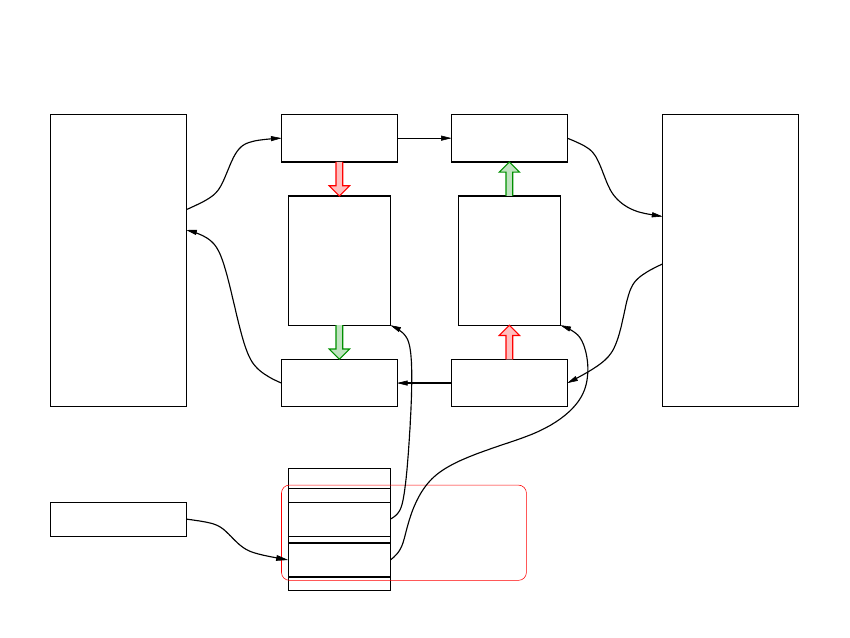

Architektury mikroprocesorów

§ według typu mapy pamięci

+ architektura Von-Neumana

pamięć

danych

b

m

−

1

b

0

0x00000

pamięć

programu

0x4ffff

0x50000

0x7ffff

17

Architektury mikroprocesorów

§ według typu mapy pamięci

+ architektura harwardzka

pamięć

programu

b

n

−

1

b

0

0x0000

0xffff

0x4ffff

pamięć

danych

b

m

−

1

b

0

0x00000

18

Segmentacja pamięci

segment programu

segment dodatkowy

rejestr segmentu danych

rejestr segmentu stosu

rejestr segmentu programu

segment danych

segment stosu

rejestr segmentu

dodatkowego

przesunięcie

adres fizyczny

adres efektywny

pamięć

19

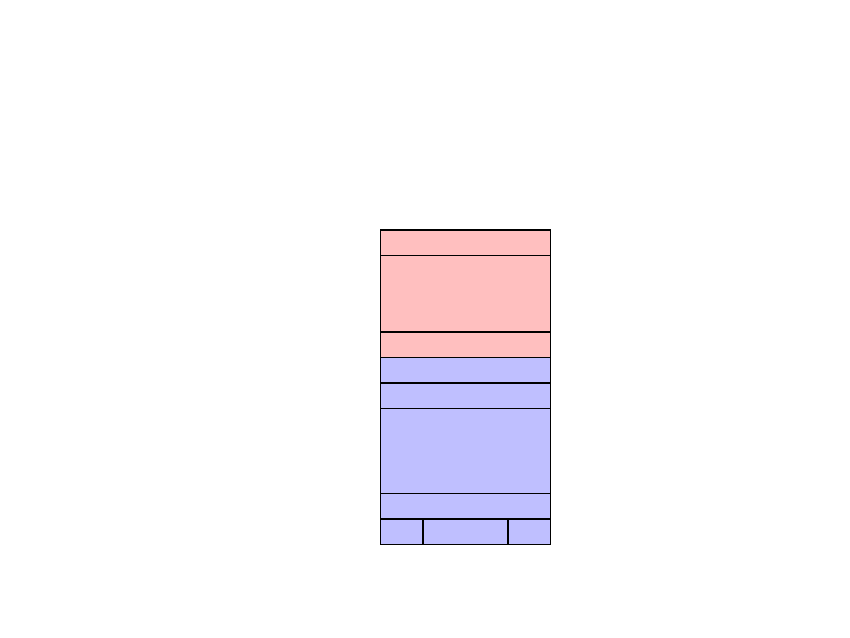

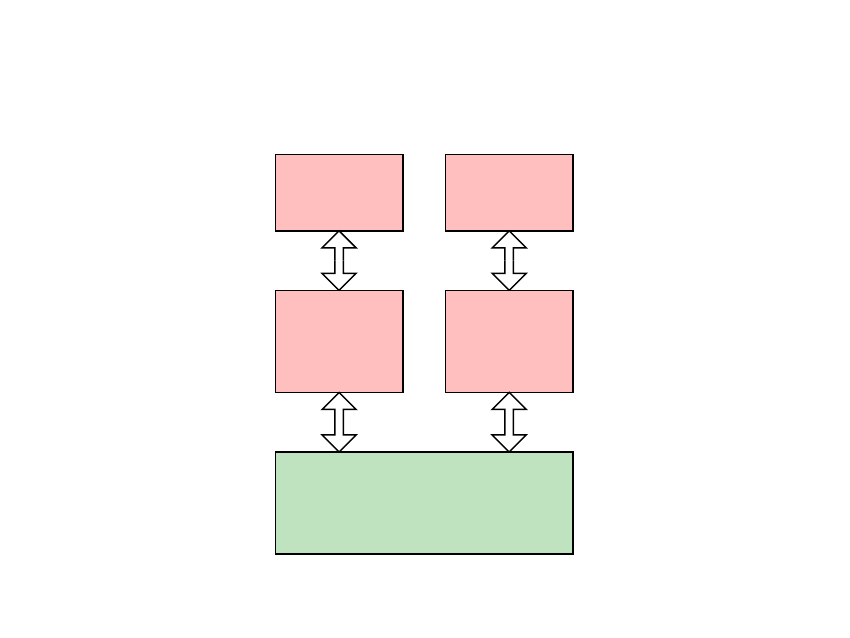

Pamięć kieszeniowa - CACHE

pamięć

CACHE

pierwszego

poziomu

pamięć

CACHE

drugiego

poziomu

pamięć RAM

16 kB

256 kB

4 GB (128 MB)

5 ns

20 ns

60 ns

rejestry

robocze

jednostki

wykonawczej

32 B

1 ns

jednostka

wykonawcza

10 ms

320 GB (160 GB)

pamięć stała

(dysk twardy,

CDROM)

pamięć

CACHE

pamięci

stałej

20

§ procesor dwurdzeniowy

rdzeń

pierwszy

rdzeń drugi

pamięć

CACHE

pierwszego

poziomu

pamięć

CACHE

pierwszego

poziomu

pamięć CACHE

drugiego poziomu

21

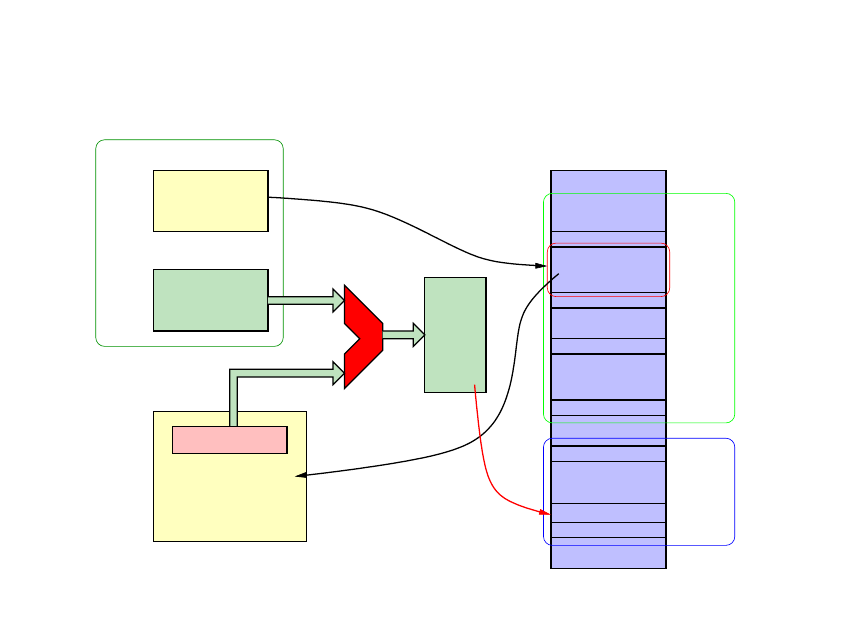

Przerwania

kod przerwanego programu

pełny kod podprogramu obsługi przerwania

podprogramy obsługi przerwań

przerwanie

skok

skok

skok

instrukcja

instrukcja

instrukcja

instrukcja

instrukcja

instrukcja

instrukcja

powrót

22

Układ zarządzania pamięcią

§ MMU (ang. Memory Management Unit)

dane

adres

wirtualny

adres

fizyczny

sygnały

sterujące

sygnały

sterujące

mikroprocesor

pamięć

fizyczna

jednostka

centralna

układ

zarządzania

pamięcią

23

§ wyznaczanie adresu fizycznego

deskryptor

segmentu

pamięć fizyczna

se

g

m

en

t

d

es

k

ry

p

to

ró

w

se

g

m

en

t

d

a

n

y

ch

rejestr

segmentowy

selektor

dana

adres

efektywny

a

d

re

s

fi

zy

cz

n

y

adres bazowy

deskryptor segmentu

a

d

re

s

w

ir

tu

a

ln

y

rozszerzenie

rejestru

segmentowego

24

Tryb Chroniony

segment

stanu

zadania 1

selektor zadania

segment

stanu

zadania 2

segment

deskryptorów

zadań

stan rejestrów

procesora

stan rejestrów

procesora

stan rejestrów

procesora

stan rejestrów

procesora

deskryptor

zadania 1

deskryptor

zadania 2

segment

deskryptorów

zadanie 1

zadanie 2

rozkaz

rozkaz

wywołanie

rozkaz

rozkaz

rozkaz

rozkaz

powrót

rozkaz

25

Wyszukiwarka

Podobne podstrony:

03 organizacja pamięciid 4188 ppt

03 UKŁAD KOSTNY

Układ limfatyczny i odporność organizmu

Instrukcja do zad proj 13 Uklad sterowania schodow ruchom

8w Uklad sterowania 2 v04

Instrukcja do zad proj 19 Układ sterowania bramy garażu

Organizacja pamięci komputerów, szkola, systemy operacyjne, klasa 1

Układ sterowania

Politechnika Białostocka 03 Układy sterowania umożliwiające zmianę parametrów ruchu tłoka

Organizacja pamięci

Elementy bez-oczowe w elektronice- Czyli gawrych (Âci-ga), Ściągi do szkoły, Układ Sterowania i Regu

03 Interakcje stosunki spoleczne organizacja struktura spoleczna, studia, wprowadzenie do socjologii

Instrukcja do zad proj 17 Uklad sterowania prasy hydrauli

Organizacja i zarzadzanie 03, PYTANIA NA EGZAMIN Z ORGANIZACJI I ZARZĄDZANIA

Jody polprzewodnikowe-sciaga, Ściągi do szkoły, Układ Sterowania i Regulacji

Rynek usług 21.03.2010, Turystyka I Rekrecja, organizacja uslug turystycznych

więcej podobnych podstron