Radioelektronik Audio-HiFi-Video 4/2002

Inteligentna sonda

logiczna wywietla

na wskaniku cyfrowym

stany logiczne 0, 1 i stan

wielkiej impedancji

High Z.

W

wiêkszoci spotykanych

w praktyce sond logicznych

jako wskaniki s¹ stosowane

diody wiec¹ce (LED), co nie

zawsze jest wygodne i mo¿e prowadziæ do

nieporozumieñ przy odczycie. Tutaj zasto-

sowano podwójny wskanik cyfrowy, na

którym wystêpuj¹ wskazania:

LO stan logiczny niski (Low _ 0)

HI stan logiczny wysoki (High _ 1)

II stan otwarcia (Infinite Impedance High Z).

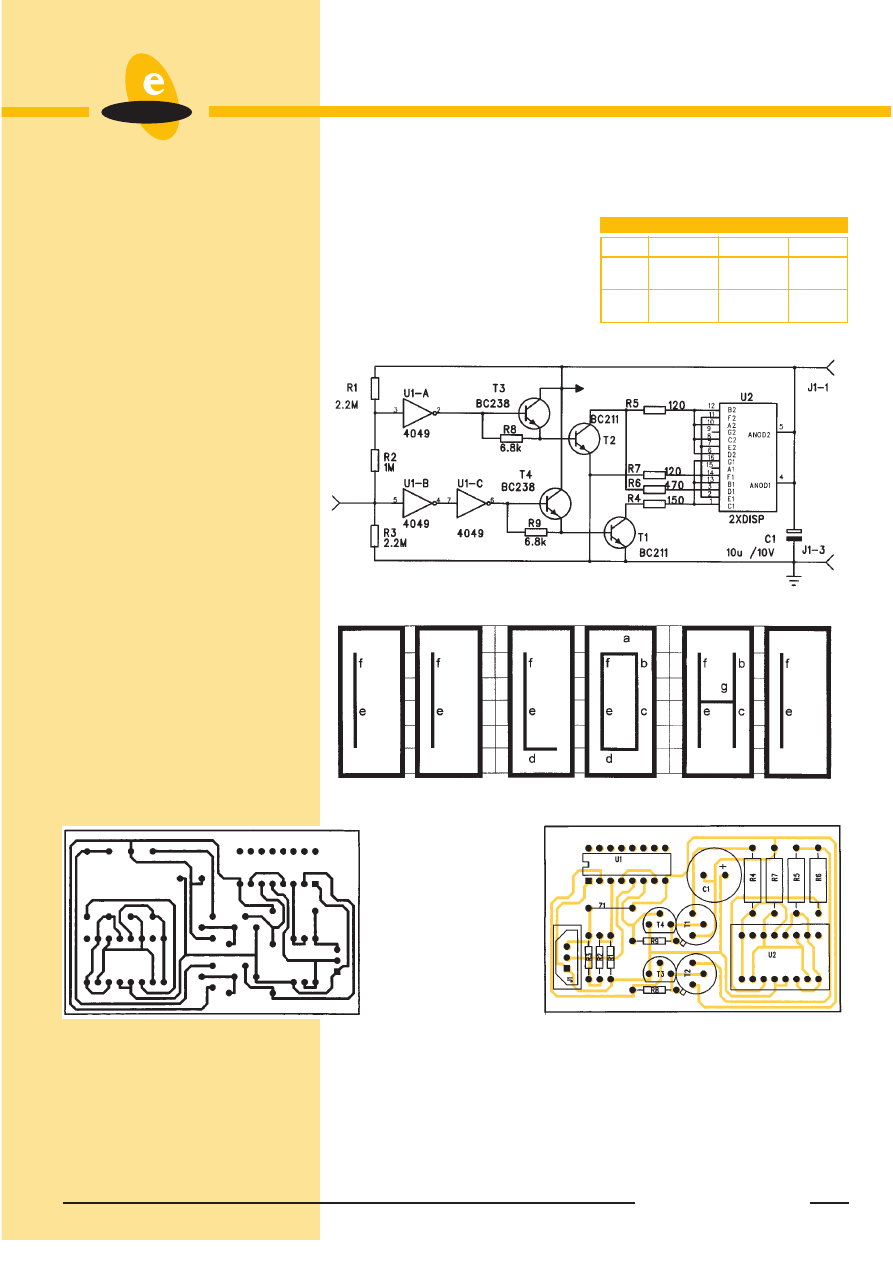

Schemat trójstanowej sondy logicznej jest

przedstawiony na rys.1. Do budowy uk³adu

zastosowano jeden uk³ad scalony CMOS ty-

pu 4049, podwójny wskanik cyfrowy ze

wspóln¹ anod¹, cztery tranzystory i kilka

rezystorów. Sposób zobrazowania poszcze-

gólnych stanów przedstawiono na rys. 2.

Wykorzystano tu mo¿liwoæ wywietlania

przez wskanik cyfrowy liter H, I, L i O. Na-

le¿y zwróciæ uwagê, ¿e segmenty e i f obu

cyfr wiec¹ siê zawsze, niezale¿nie od sta-

nu. Z tego wzglêdu wyprowadzenia E1, F1,

E2 i F2 obu wskaników s¹ po³¹czone razem

i przez rezystor R7 o rezystancji 120

Ω

po³¹-

czone z mas¹. Sonda w stanie spoczynko-

wym wywietla stan otwarcia stan wielkiej

impedancji.

TRÓJSTANOWA SONDA LOGICZNA

napiêcia zasilania jako napiêcie odpowia-

daj¹ce stanowi niskiemu, na wyjciu in-

wertera U1A pojawi siê napiêcie odpowia-

daj¹ce wysokiemu stanowi logicznemu,

a na wyjciu inwertera U1C napiêcie odpo-

wiadaj¹ce stanowi niskiemu. W rezultacie

klucz tranzystorowy z³o¿ony z tranzystorów

T3 i T2 spowoduje przep³yw pr¹du przez

segmenty D1 oraz A2, B2, C2 i D2, co

spowoduje wywietlenie liter LO.

Po do³¹czeniu wejcia sondy do punktu

o wysokim poziomie logicznym, napiêcie na

wyjciu inwertera U1C osi¹gnie wartoæ

blisk¹ napiêciu zasilania, a klucz tranzysto-

Symbol Oznaczenie Producent Uwagi

U1

4049 National

Semiconductor

U2

MAN6730 Monsanto wskanik

dwucyfrowy

Wykaz wa¿niejszych elementów

rowy z³o¿ony z T4 i T1 spowoduje przep³yw

pr¹du przez segmenty B1, C1 i G1, co

spowoduje wywietlenie liter HI.

Na rys. 3 przedstawiono p³ytkê drukowan¹

uk³adu, a na rys. 4 _ rozmieszczenie ele-

mentów na p³ytce

.

(cr)

n

J1-2

Rezystory R1, R2 i R3 tworz¹ dzielnik napiê-

cia, który powoduje, ¿e po do³¹czeniu son-

dy do punktu o napiêciu odpowiadaj¹cym

niskiemu stanowi logicznemu, napiêcie na

wejciu inwertera U1A wynosi ok. 1,5 V.

Poniewa¿ uk³ady logiczne rodziny CMOS

rozpoznaj¹ napiêcie mniejsze od po³owy

Rys. 1. Schemat trójstanowej sondy logicznej

Rys. 3.

P³ytka drukowana

trójstanowej sondy

logicznej (skala 1:1)

Rys. 4.

Rozmieszczenie

elementów na p³ytce

drukowanej

trójstanowej sondy

logicznej

Rys. 2. Sposób zobrazowania stanów logicznych

TESTER REZONATORÓW KWARCOWYCH

Uk³ad mo¿e s³u¿yæ do

sprawdzania rezonatorów

na zakres czêstotliwoci

od kilkuset kiloherców

do kilkudziesiêciu

megaherców.

S

prawdzenia dzia³ania rezonato-

ra kwarcowego mo¿na dokonaæ

w oryginalnym uk³adzie pracy,

w urz¹dzeniu lub specjalnym

uk³adzie testowym.

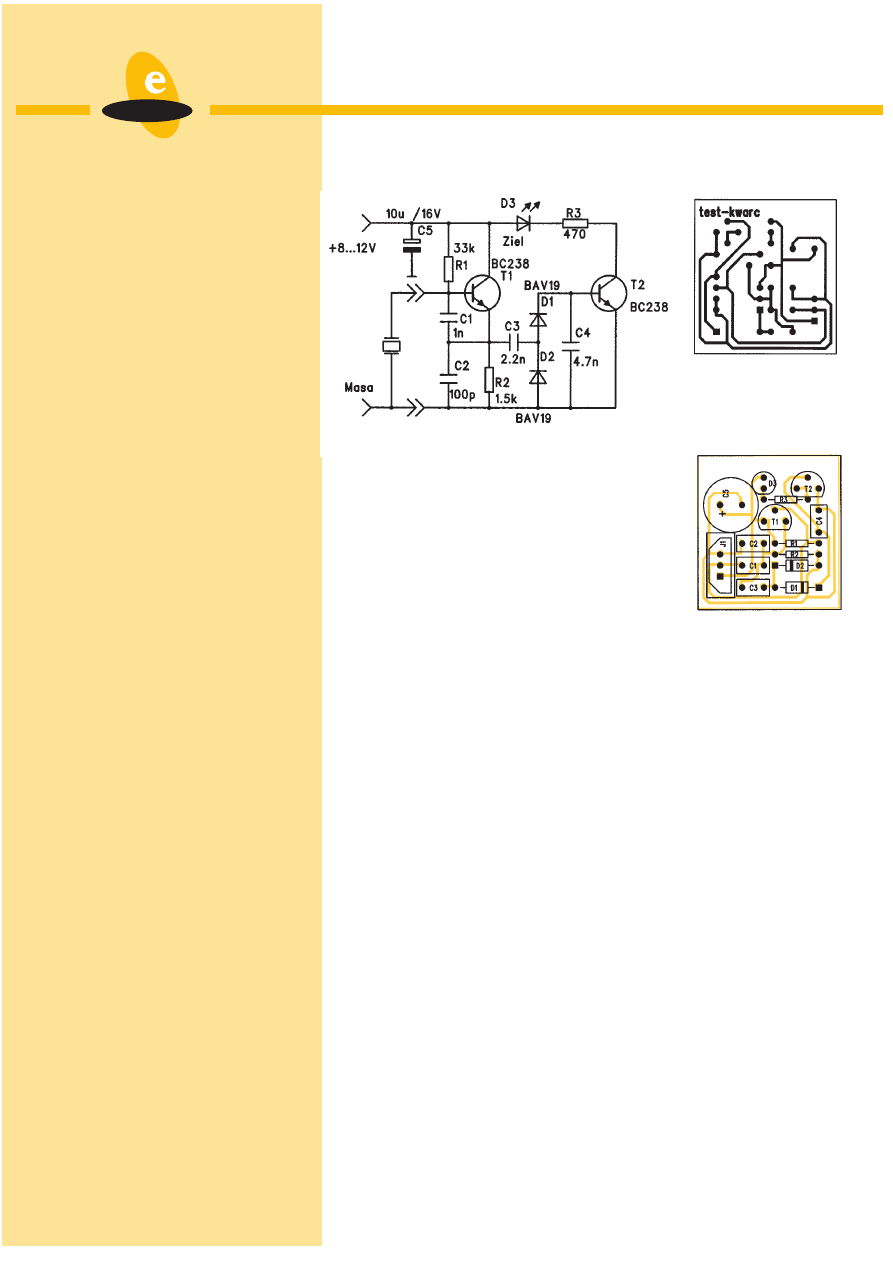

Schemat prostego testera rezonatorów

kwarcowych jest przedstawiony na rys.1.

Sk³ada siê on z nastêpuj¹cych bloków:

q

generatora badany rezonator oraz ele-

menty C1, C2, R1, R2 i T1,

q

prostownika elementy C3, C4, D1 i D2,

q

wskanika elementy D3, R3 i T2.

Do³¹czenie do zacisków wejciowych uk³a-

du rezonatora kwarcowego, a nastêpnie

w³¹czenie zasilania powoduje generacjê

przebiegu sinusoisalnego o czêstotliwoci

nominalnej rezonatora. Sygna³ wyjciowy

generatora wystêpuje na rezystorze emi-

terowym R2 Po przejciu przez prostownik

powoduje nasycenie tranzystora T2 i wie-

cenie diody D3.

Na rys. 2 przedstawiono p³ytkê drukowan¹

uk³adu, a na rys. 3 _ rozmieszczenie ele-

mentów na p³ytce.

(cr)

n

Rys. 1. Schemat testera rezonatorów kwarcowych

Rys. 2. P³ytka drukowana

testera rezonatorów

kwarcowych (skala 1:1)

Rys. 3.

Rozmieszczenie

elementów

na p³ytce

drukowanej

testera

rezonatorów

kwarcowych

Wyszukiwarka

Podobne podstrony:

04 22 PAROTITE EPIDEMICA

zestawy zadań, rrz 04 22

2002 04 41

2002 05 22

ei 01 2002 s 21 22

Siatkówka- wystawa 2002.10.22, Konspekty, Siatkówka

pg 2010 04 22

2002 04 30

Matematyka dyskretna 2002 04 Rachunek prawdopodobieństwa

2002 04 06

2002 04 34

2002 04 10

2002 04 07

2002 04 12

2002 04 28

2002 04 33

2002 04 07 wycena akcji, FCFF, FCFF, dźwignie finansowe, progi rentowności

więcej podobnych podstron