2016-05-15

1

Architektura komputerów

i systemy operacyjne

Wykład

Procesory RISC i CISC.

Architektura komputerów i systemy operacyjne

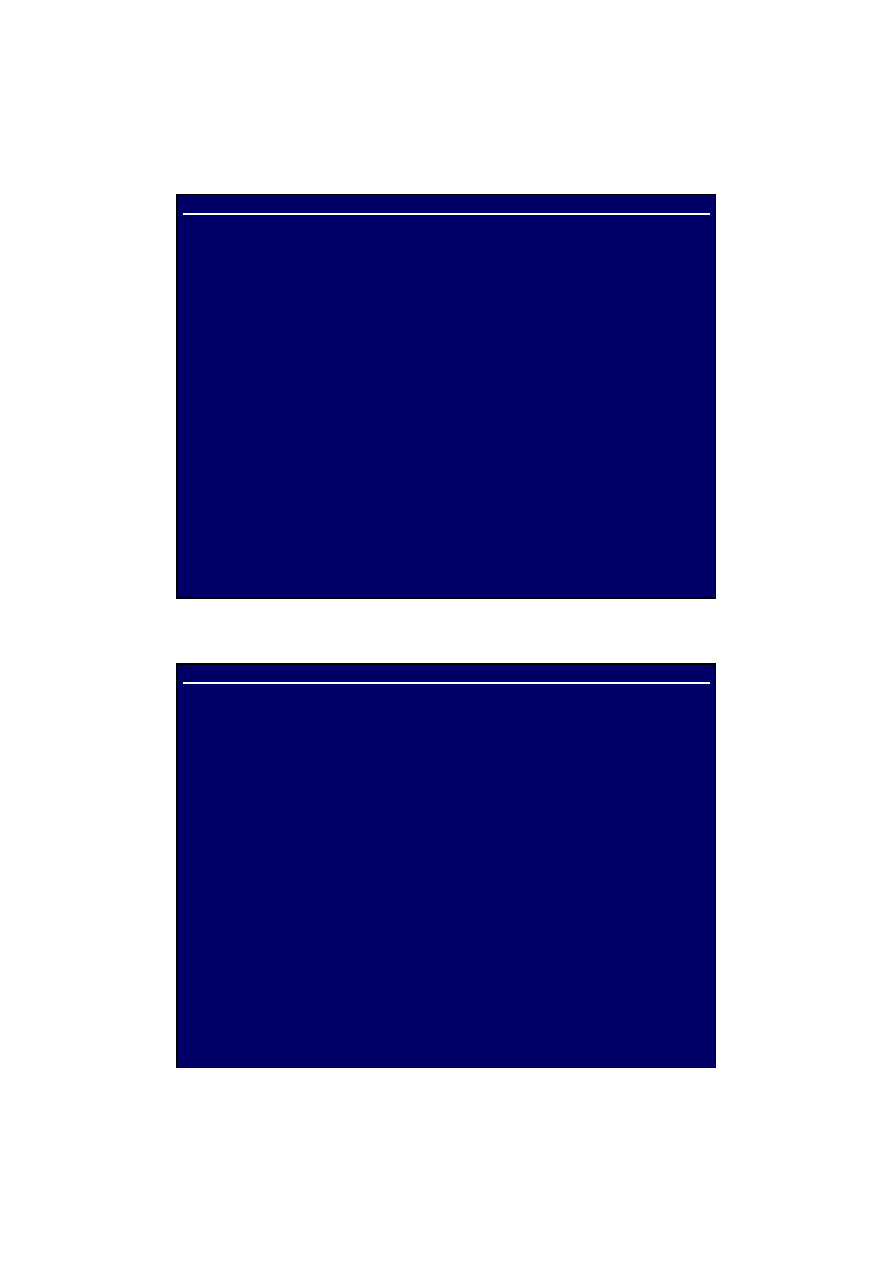

Główny podział architektur współczesnych procesorów

CISC - Complex Instruction Set Computer

RISC - Reduced Instruction Set Computer

VLIW - Very Long Instruction Word

EPIC - Explicitly Parallel Instruction Computing

2016-05-15

2

Architektura komputerów i systemy operacyjne

Architektura CISC

– procesor wykorzystujący bogaty zestaw (listę) instrukcji

– liczne sposoby adresowania argumentów

– wszystkie działania ALU wykorzystują specjalny rejestr o nazwie

„akumulator” (oznaczany jako a, A, ax, AX, acc, ACC)

– charakterystyczną cechą jest zróżnicowana długość instrukcji (w

bajtach)

– bardzo zróżnicowany czas wykonania instrukcji

– procesory mają złożoną budowę, przez co zajmują większą

powierzchnię „krzemu” i z reguły są wolniejsze

– procesory np. Pentium, x51, H8SX

Architektura komputerów i systemy operacyjne

Właściwości procesorów RISC

Cechy (RISC I)

• wszystkie instrukcje 32-bitowe w kilku formatach

• architektura typu

load-store

• duża liczba rejestrów 32-bitowych ogólnego

przeznaczenia (brak wyróżnionego akumulatora)

• prosty sprzętowy układ dekodowania instrukcji (w CISC

jest mikroukład - ROMs microcode)

• przetwarzanie potokowe (pipelining)

• wykonanie instrukcji w jednym takcie zegarowym

Początek: 1980 r., Patterson, Uniwersytet Berkeley

2016-05-15

3

Architektura komputerów i systemy operacyjne

Zalety:

- mała „powierzchnia krzemu”

- krótszy czas projektowania układu (technologiczny)

- większa wydajność

- łatwa możliwość implementacji przetwarzania potokowego

Wady:

- bardziej złożony kod instrukcji (w porównaniu z CISC)

- mała liczba trybów adresowania

- brak kompatybilności z kodem x86

- bardziej złożone kompilatory C

Zalety i wady RISC

Architektura komputerów i systemy operacyjne

Współczesne procesory RISC

• Najważniejsze procesory RISC do zastosowań typu

embedded systems:

– ARM/StrongARM (telefony komórkowe)

– MIPS Rxx00 (konsole Nintendo N64, GameCube – Dolphin, Sony

Playstation, terminale Cisco)

– Hitachi SH (produkty Hitachi, palmtopy Windows CE, konsole Sega

Saturn i Dreamcast)

– PowerPC

• Najważniejesze procesory RISC do stacji roboczych:

– SPARC, UltraSPARC I/II, SPARC 64 (Sun Microsystems, Texas

Instruments, Fujitsu)

– DEC Alpha

– Hewlett-Packard PA-RISC

Obecnie mikroprocesory (mikrokontrolery) :

8-, 16-, 32-, 64-bitowe

2016-05-15

4

Architektura komputerów i systemy operacyjne

Cechy:

- jedna instrukcja określa wiele operacji

- wszystkie jednostki wykonawcze są statyczne (co oznacza,

że podział zadań musi być rozdzielony na poziomie

kompilatora)

- statyczne jednostki wykonawcze mają prostsze sterowanie i

mogą pracować z „szybszymi” zegarami

- architektura VLIW obecnie stosowana głównie w DSP i

multimediach

Procesory VLIW

Architektura komputerów i systemy operacyjne

EPIC - przetwarzanie jawnie równoległe (kilka jednostek ALU

+ FPU + M)

•

grupowanie instrukcji i oznaczaniu ich wzajemnych relacji już na etapie

kompilacji programu

• instrukcje są grupowane w tzw. paczkach (po trzy instrukcje)

• paczki są przesyłane do procesora równocześnie

• paczka zawiera przedrostek – tj. grupę bitów informujących procesor o

tym, do których jednostek ma skierować poszczególne rozkazy

• w przedrostku znajdują się też informacje o tzw. barierach wykonań

służących do koordynacji wykonywania poszczególnych instrukcji

• jeśli pomiędzy rozkazami znajdują się bariery wykonania, to drugi ciąg

zostanie wykonany dopiero wtedy gdy znane będą wyniki działania

rozkazów z pierwszego ciągu

Architektura EPIC (Intel Itanium IA64)

Wyszukiwarka

Podobne podstrony:

AKiSO SS wykład 3 ISA

AKiSO SS wykład 8 I2C SPI 1W CAN

AKiSO SS wykład 9 syst operacyjne

AKiSO SS wykład 1

AKiSO SS wykład 2 CPU

AKiSO SS wykład 6 ZL27ARM

AKiSO SS wykład 5 cache

AKiSO SS wykład 4 potok sscalar

AKiSO SS wykład 6 CortexM3

AKiSO SS wykład 7 RS LPT FW USB

AKiSO SS wykład 0 E4x CYW wprowadzenie

AKiSO SS wykład 6 ARM wprowadzenie

AKiSO SS wykład 3 ISA

więcej podobnych podstron