2016-05-15

1

Architektura komputerów

i systemy operacyjne

Studia stacjonarne I stopnia

Wykład

Budowa i zasada działania mikrokontrolera

z rdzeniem Cortex-M3

Architektura komputerów i systemy operacyjne

1

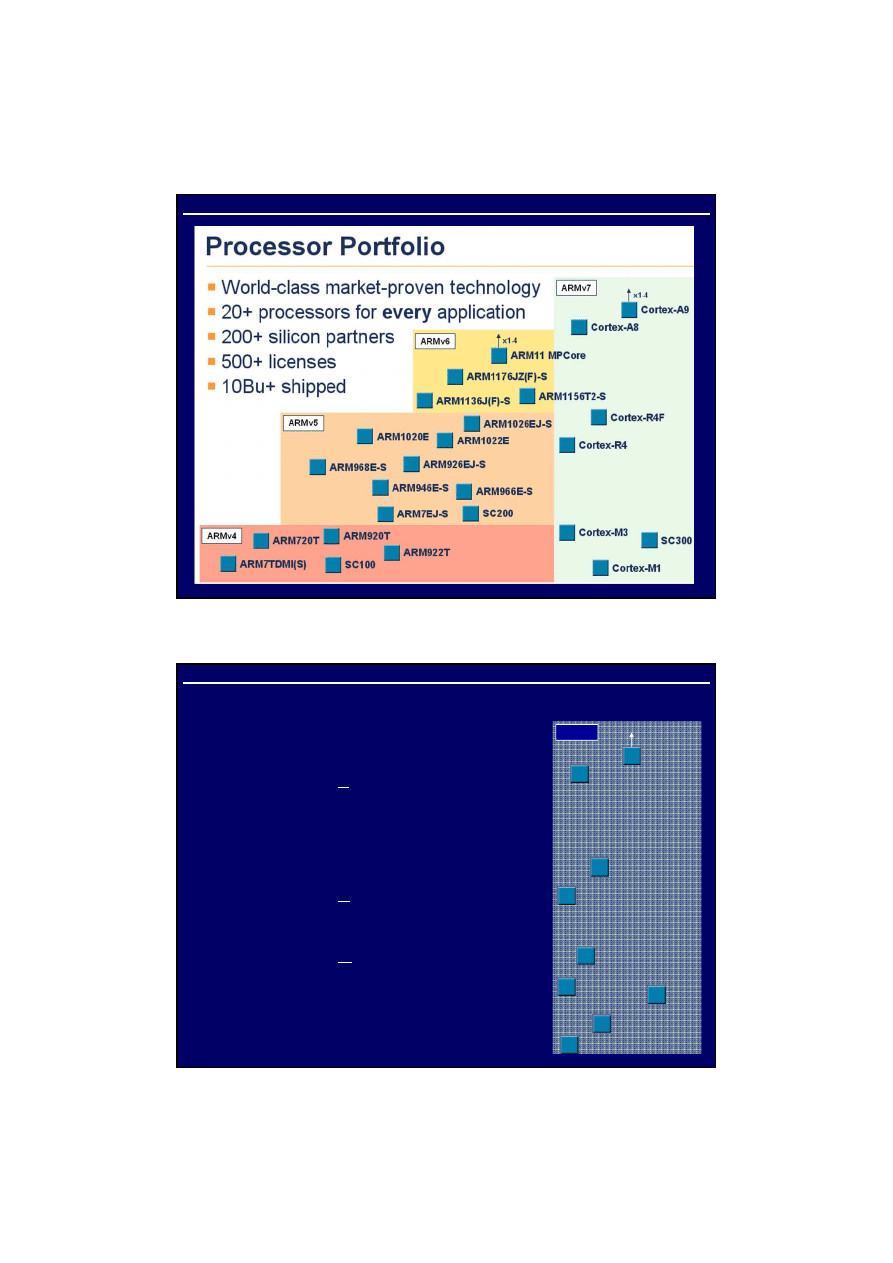

Mikroprocesory rodziny

CORTEX

2016-05-15

2

Architektura komputerów i systemy operacyjne

1

• seria ARM Cortex-A

-

aplikacje z systemami operacyjnymi tj. Symbian,

Linux, Android, Windows Embeded wymagające

dużych mocy obliczeniowych, obsługi pamięci

wirtualnej, implementacji interpreterów Javy

• seria ARM Cortex-R

- aplikacje w systemach czasu rzeczywistego

• seria ARM Cortex-M:

- aplikacje konsumenckie i przemysłowe

wymagające dużej wydajności przy niskiej cenie

Rodzina procesorów Cortex

Architektura komputerów i systemy operacyjne

1

x1-4

Cortex-A9

Cortex-A8

Cortex-R4

Cortex-M1

Cortex-M3

SC300

Cortex-R4F

ARMv7

Cortex-M4

Cortex-M0

2016-05-15

3

Cortex-Ax

Cortex-Mx

Cortex-Rx

Architektura komputerów i systemy operacyjne

2

Zastosowania procesorów Cortex

Cortex family

Cortex-A8

Architecture v7A

MMU

AXI

VFP & NEON support

Cortex-R4

Architecture v7R

MPU (optional)

AXI

Dual Issue

Cortex-M3

Architecture v7M

MPU (optional)

AHB Lite & APB

2016-05-15

4

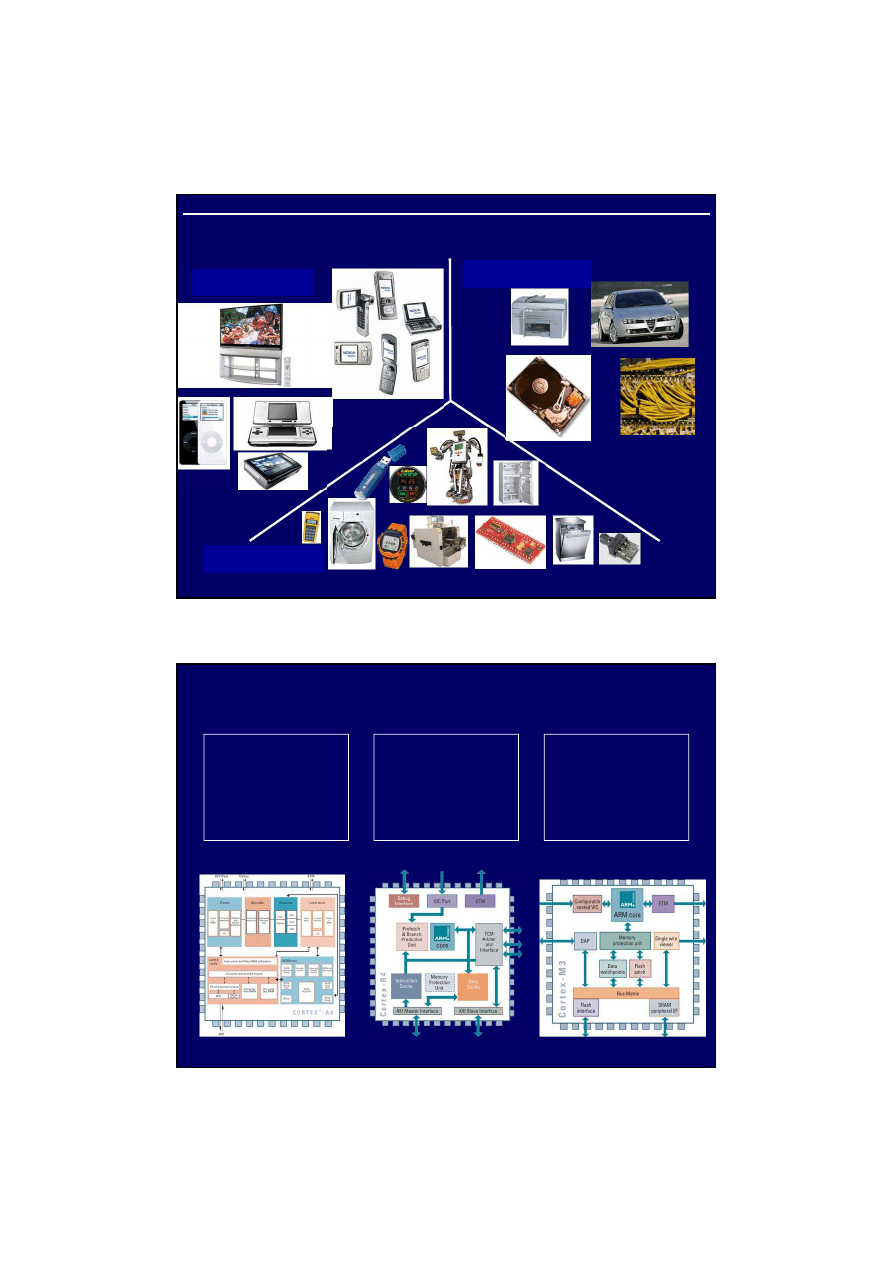

Względna wydajność procesorów ARM

*Represents attainable speeds in 130, 90, 65, or 45nm processes

Cortex-

M0

Cortex-

M3

ARM7

ARM926

ARM1026

ARM1136

ARM1176

Cortex-A8

Cortex-A9

Dual-core

Max Freq (MHz)

50

150

184

470

540

610

750

1100

2000

Min Power (mW/MHz)

0,012

0,06

0,35

0,235

0,36

0,335

0,568

0,43

0,5

0

500

1000

1500

2000

2500

M

a

x

F

re

q

u

e

n

c

y

(

M

H

z

)

Architektura komputerów i systemy operacyjne

1

Architektura

CORTEX-M3

2016-05-15

5

Cechy architektury Cortex-M3

Architektura komputerów i systemy operacyjne

3

Szybkość

wykonywania

Gęstość

upakowania kodu

100% Thumb

code

Indywidualne

zabiegi

Thumb-2

100% ARM code

- wysokiej jakości core

1.25 DMIPS/MHz

- lista instrukcji Thumb-2 i Thumb

- Architektura Harvardzka

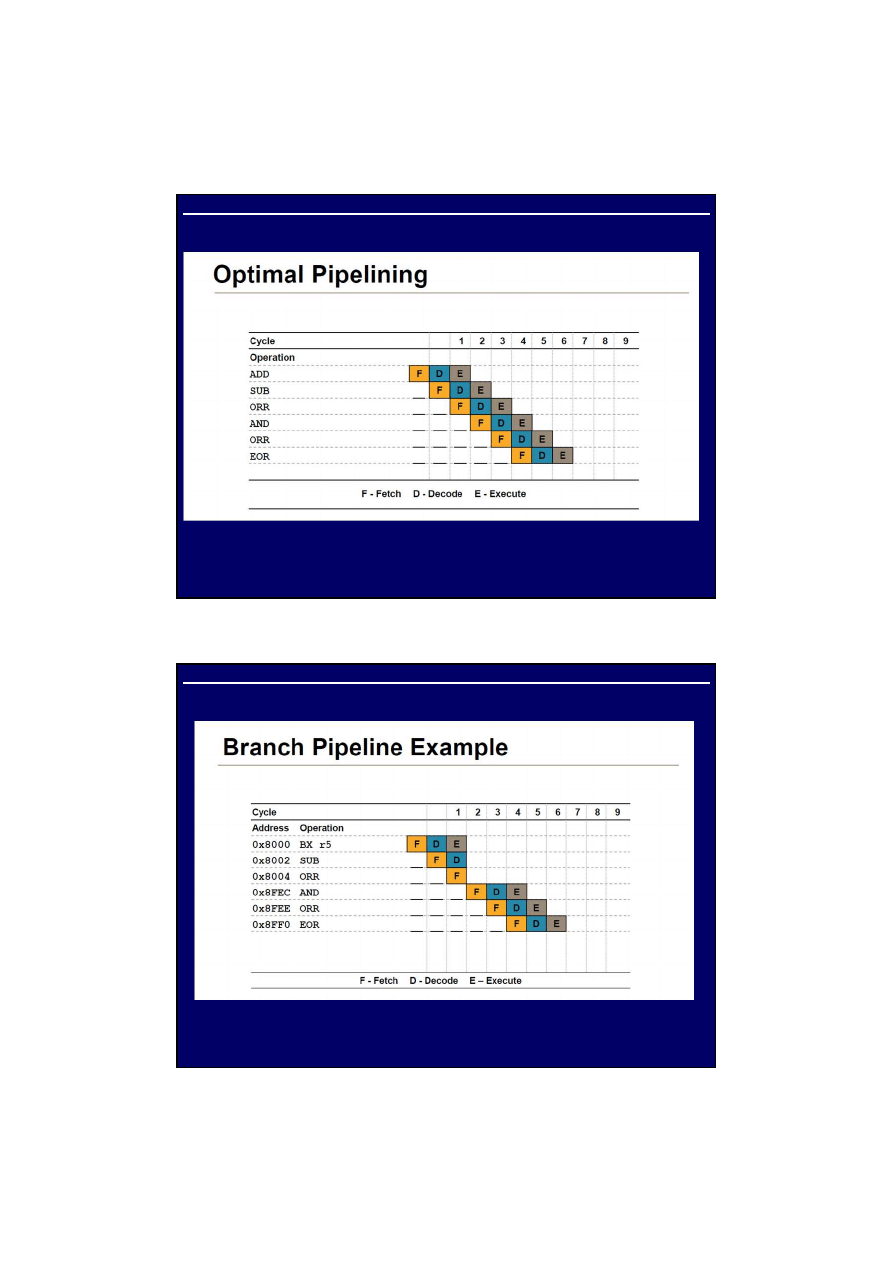

- 3-stopniowa kolejka instrukcji pipeline z rozpoznaniem rozgałęzień

- zintegrowana matryca magistral

- konfigurowalny priorytetowy kontroler przerwań wektoryzowanych (NVIC)

• do 15 przerwań systemowych (wyjątków)

• do 240 przerwań zewnętrznych

- zawansowane konfigurowalne elementy kontroli wykonywania programu (debuging)

- elementy opcjonalne:

• układ ochrony pamięci Memory Protection Unit (MPU) (seria R)

• układ śledzenia wykonywania programu Embedded Trace Macrocell (ETM)

- nieobecny w procesorach STM

Architektura komputerów i systemy operacyjne

1

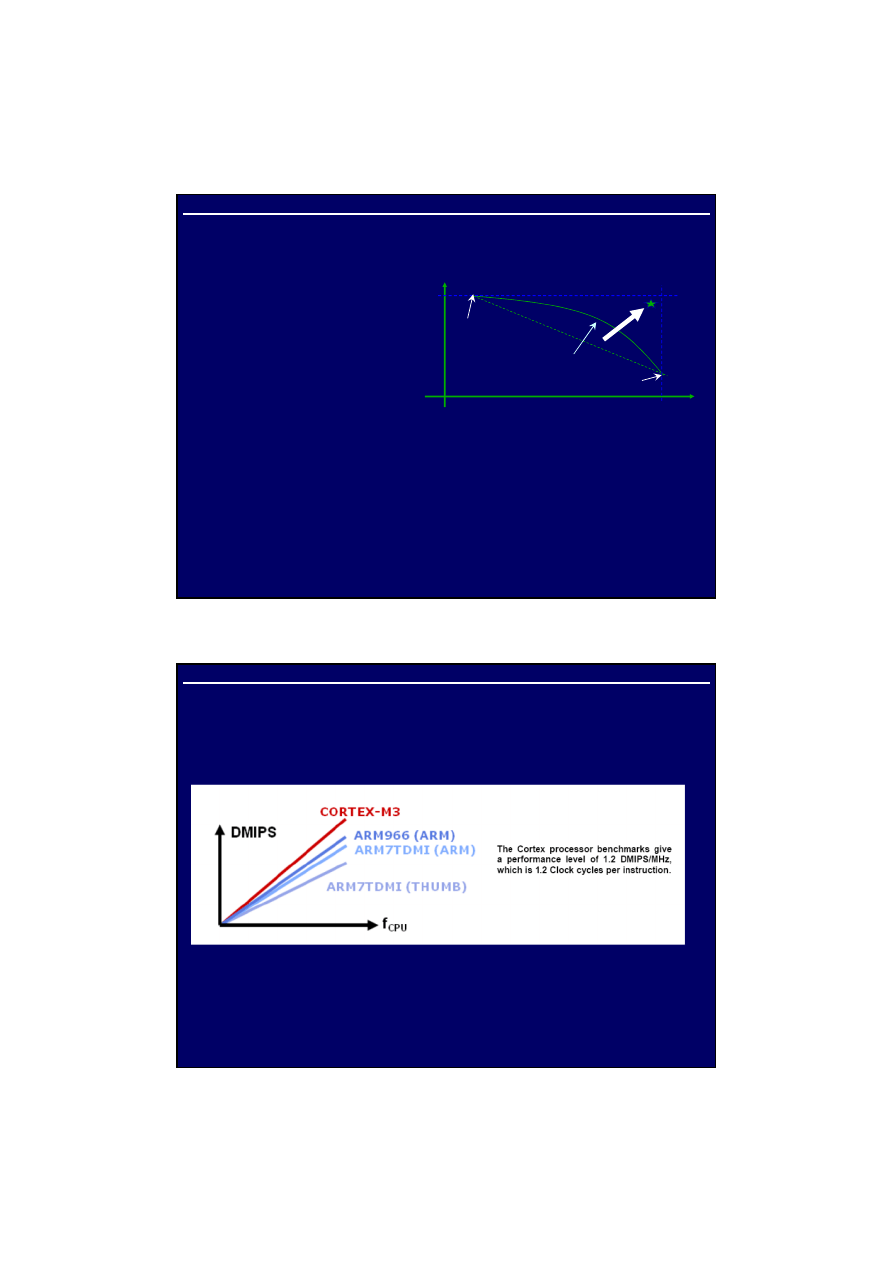

Wydajność architektury Cortex-M3 w

odniesieniu do innych rdzeni

2016-05-15

6

Architektura komputerów i systemy operacyjne

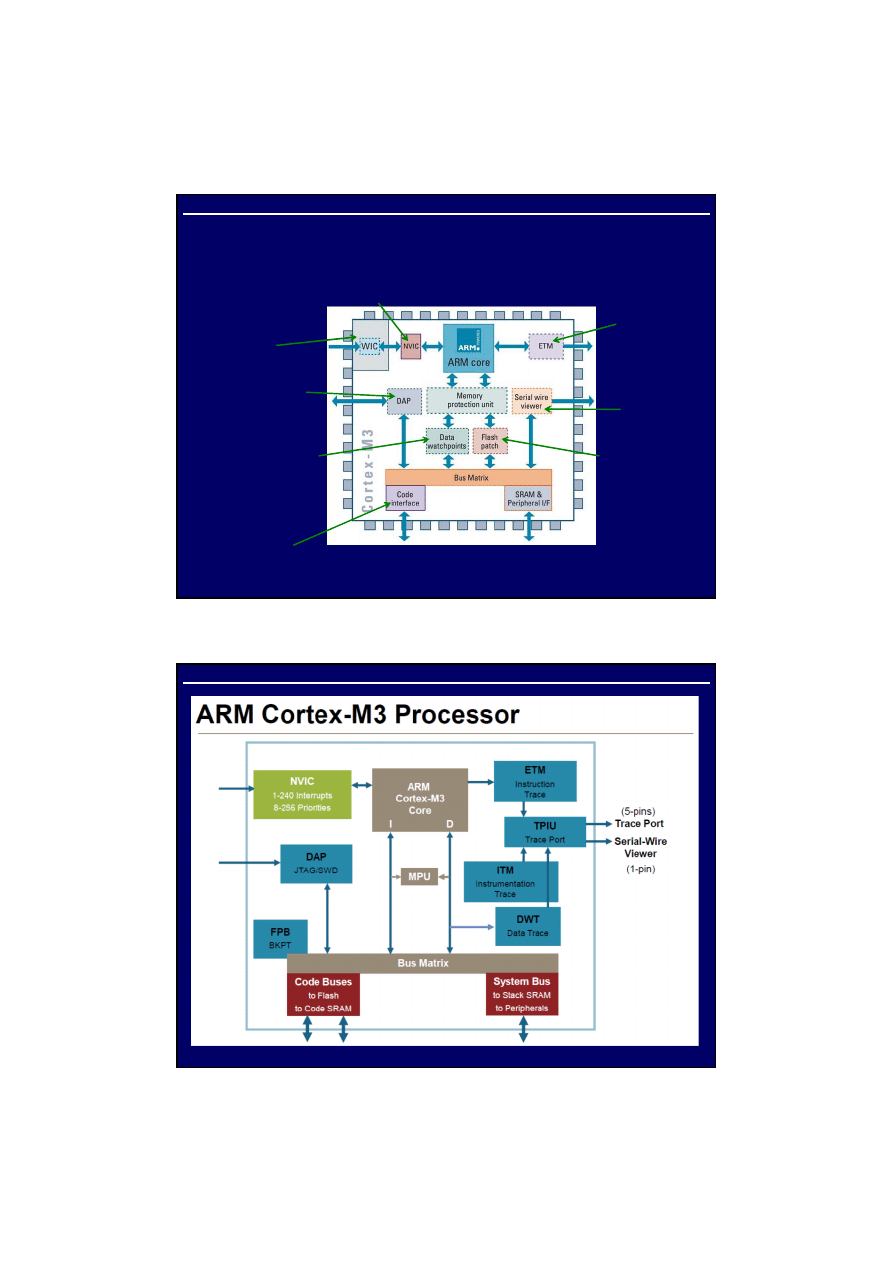

7

układ wyprowadzania

z trybu niskiego poboru

mocy (WIC)

Struktura procesora Cortex-M3

- magistrala systemowa

(SRAM i szybkie peryferia - AHB)

- magistrala wolnych peryferiów ( APB)

magistrale

program/dane/współczynniki (x2 AHB)

moduł śledzenia danych

(x4) i monitory wyjątków

interfejs portów JTAG

lub Serial Wire

(dla procesu debugowania)

moduł kontrolny

FLASH i i punktów

zatrzymań (x8)

interfeis one-wire dla

śledzenia danych

moduł śledzenia

wykonywania

programu

konfigurowalny kontroler

przerwań wektoryzowanych

Architektura komputerów i systemy operacyjne

1

2016-05-15

7

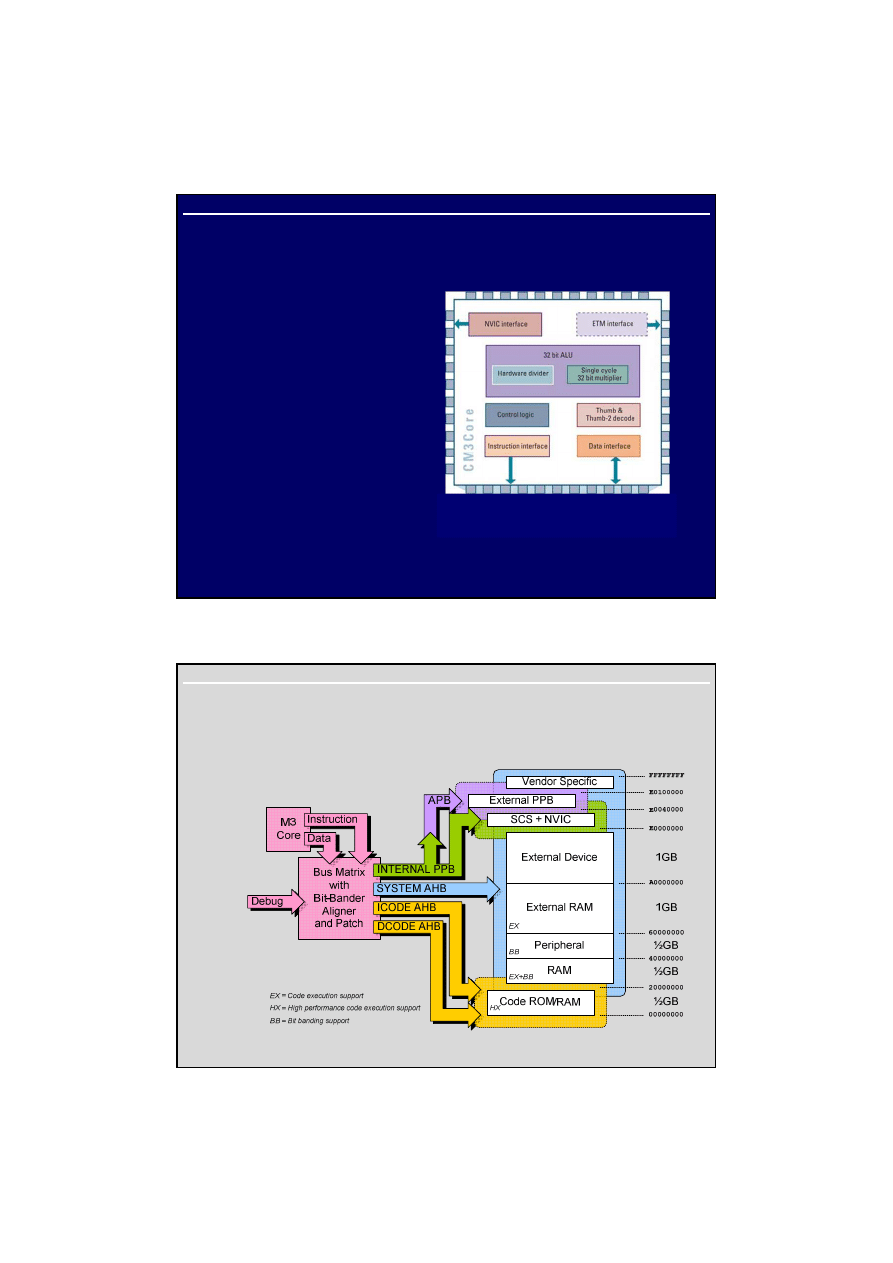

ALU zawiera:

- jednotaktowy multiplikator 32-bit

- sprzętowy dzielnik

- liczby ze znakiem i bez

- wykonywane w 2 do 12 taktach

- podlegają przerwaniu

Struktura Cortex-M3 core

Architektura komputerów i systemy operacyjne

6

Architektura komputerów i systemy operacyjne

9

Mapa pamięci

2016-05-15

8

Architektura komputerów i systemy operacyjne

10

Architektura komputerów i systemy operacyjne

5

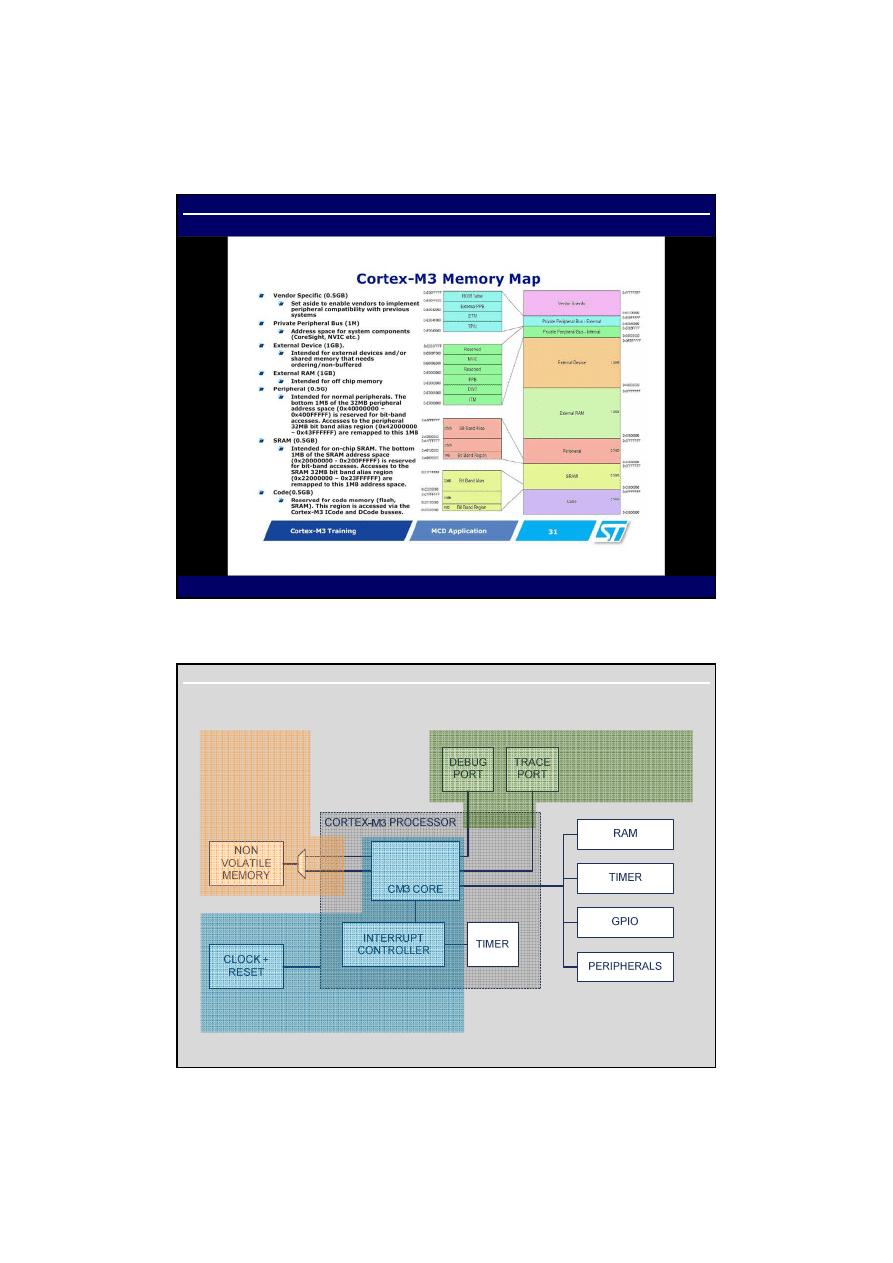

Architektura mikroprocesorów z rdzeniem Cortex-M3

niska energochłonność porównywalna z

procesorami 8/16-bitowymi

zwiększona

pojemność pamięci

FLASH dla

maksymalizacji

jakości

przetwarzania CPU

zaawansowane

możliwości

debugowania

2016-05-15

9

Architektura komputerów i systemy operacyjne

8

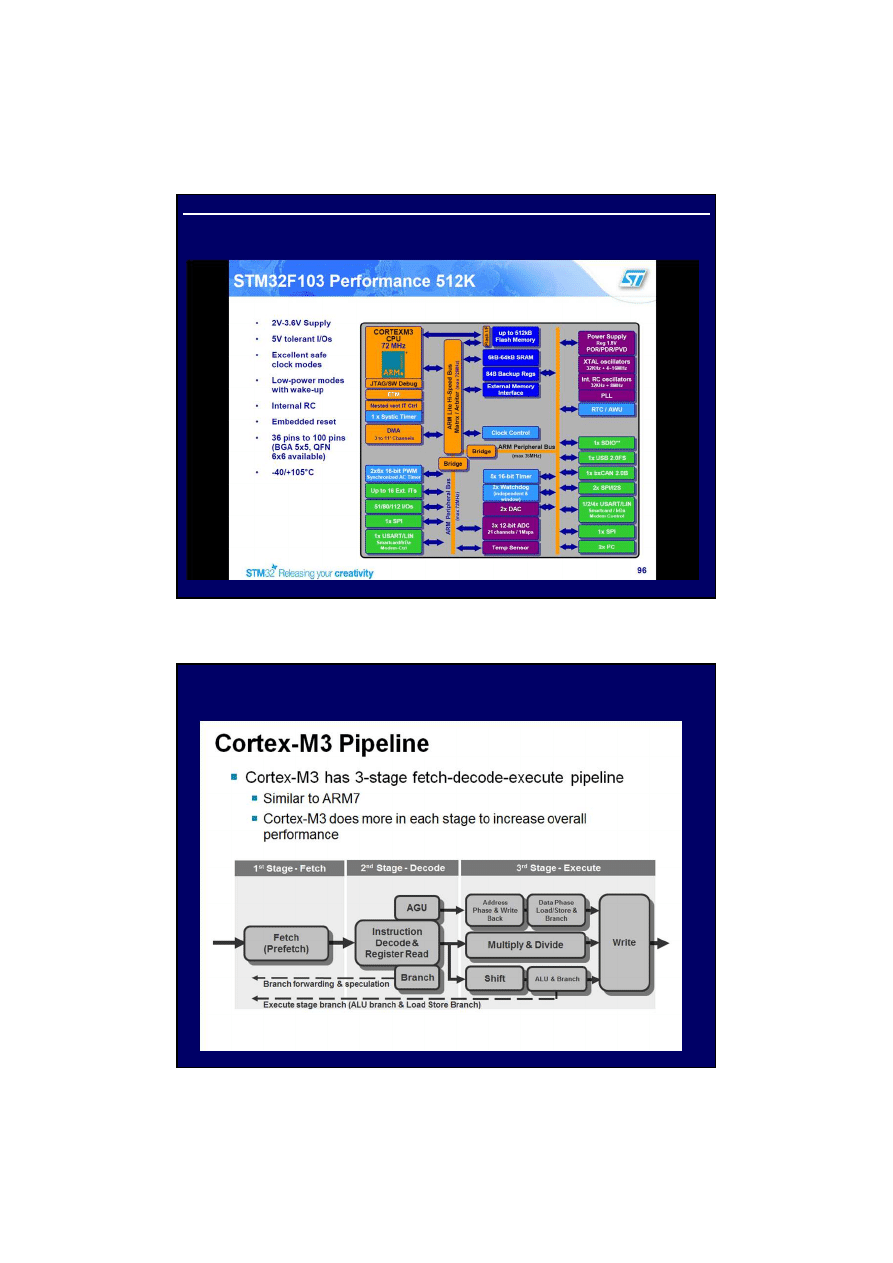

Przykład mikrokontrolera z rdzeniem Cortex-M3

Przetwarzanie potokowe w Cortex-M3

2016-05-15

10

Architektura komputerów i systemy operacyjne

1

Architektura komputerów i systemy operacyjne

1

2016-05-15

11

Architektura komputerów i systemy operacyjne

11

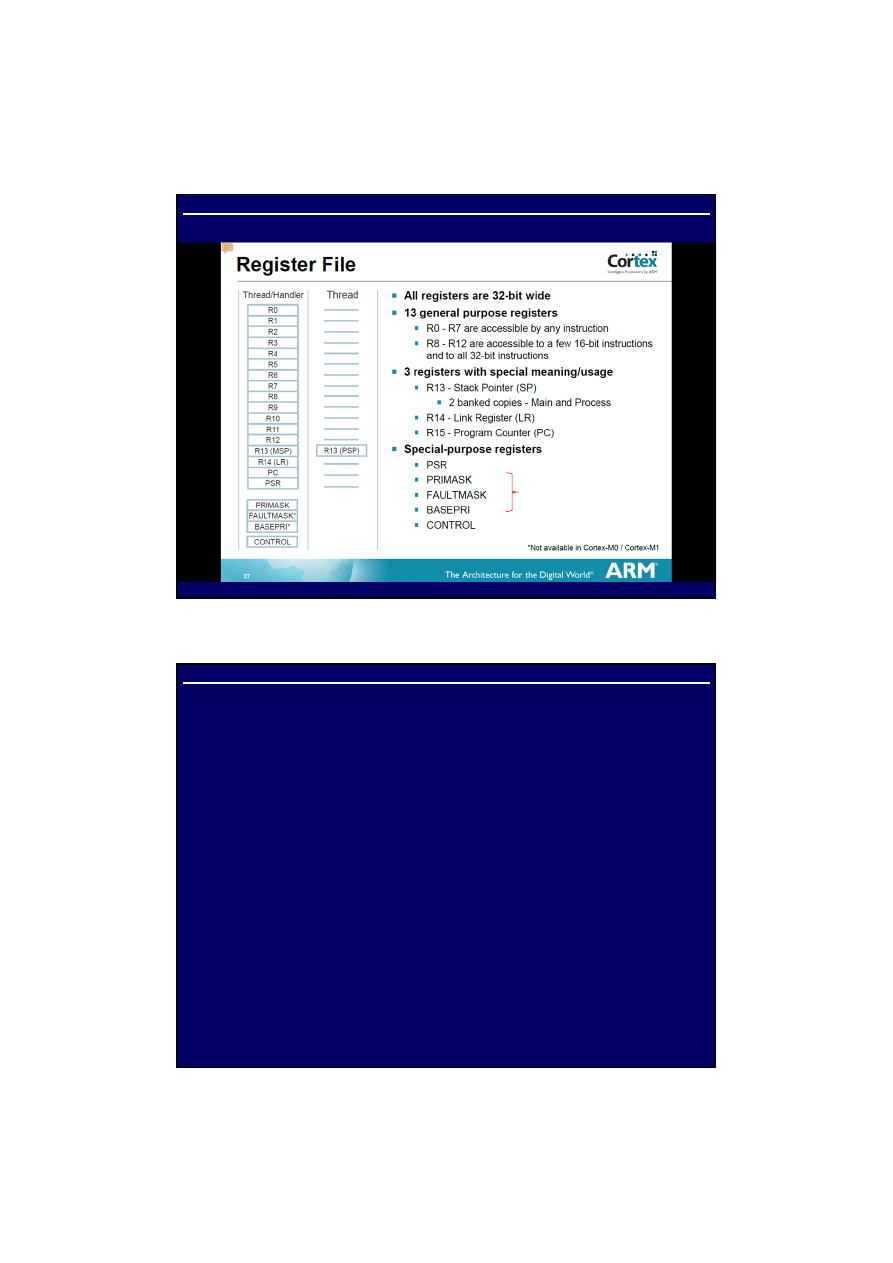

Rejestry masek wyjątków

Architektura komputerów i systemy operacyjne

1

STM32F103

2016-05-15

12

Architektura komputerów i systemy operacyjne

13

System zegarów

PLL

HSI/2

HSE/2

HSE/128

wewn. gener. LSI

(40kHz)

wewn. gener. HSI

(8MHz)

zewn. gener. HSE

(4-16MHz)

zewn. gener. LSE

(32,768kHz)

IWATCHDOGCLK

RTCCLK

SYSCLK

Architektura komputerów i systemy operacyjne

15

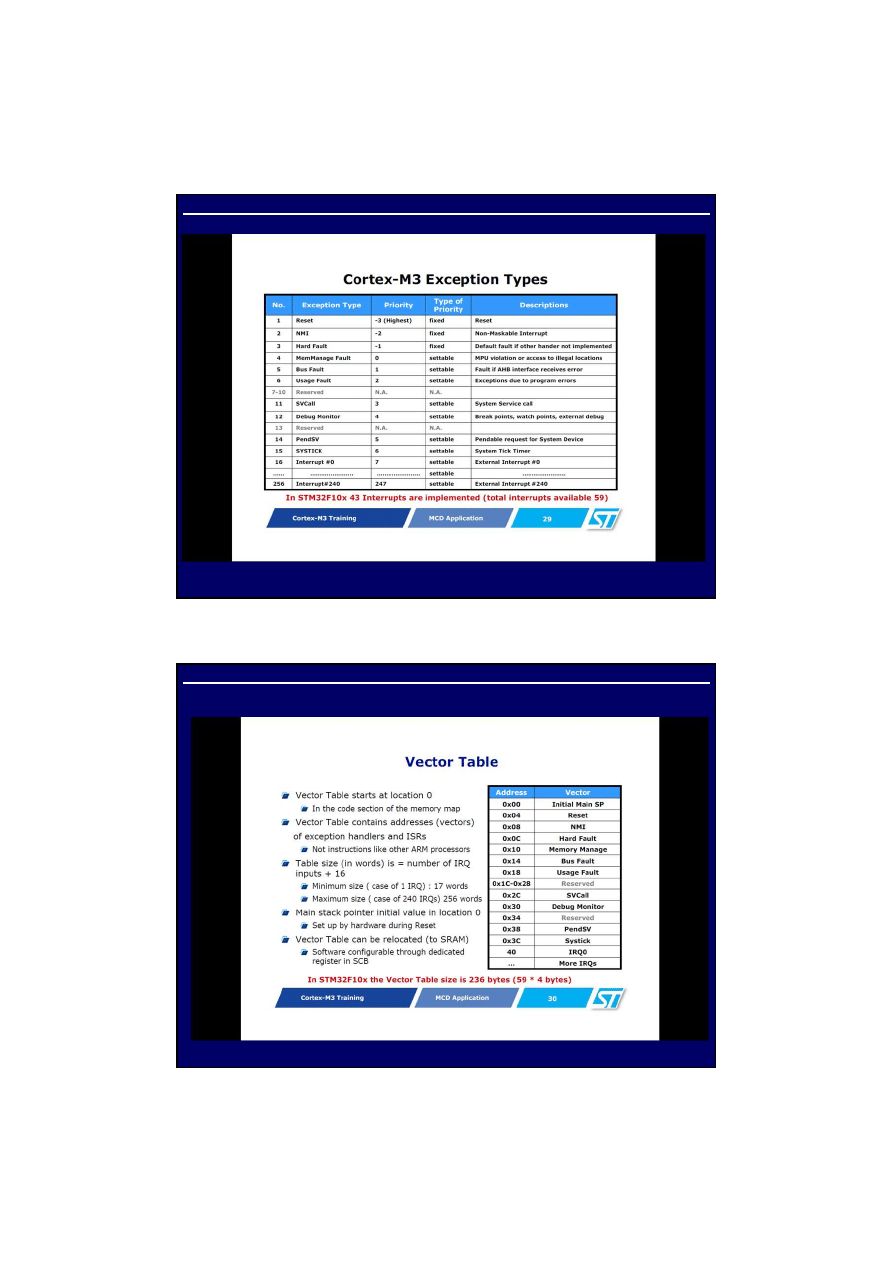

System przerwań

Oparty jest na konfigurowalnym kontrolerze przerwań wektoryzowanych NVIC

realizującym obsługę wyjątków i przerwań zewnętrznych

- wyjątki wykonywane są w uprzywilejowanym trybie

- przerywalne instrukcje LDM/STM dla zmniejszenia opóźnień obsługi przerwań

- obsługa 16 wyjątków i do 240 przerwań zewnętrznych (43 w Cortex-M3)

- 16 programowalnych poziomów priorytetu

- skrócone (do 6 taktów) opóźnienie obsługi oczekującego przerwania

- obsługa jest mikro kodowana i nie wymaga dodatkowych instrukcji

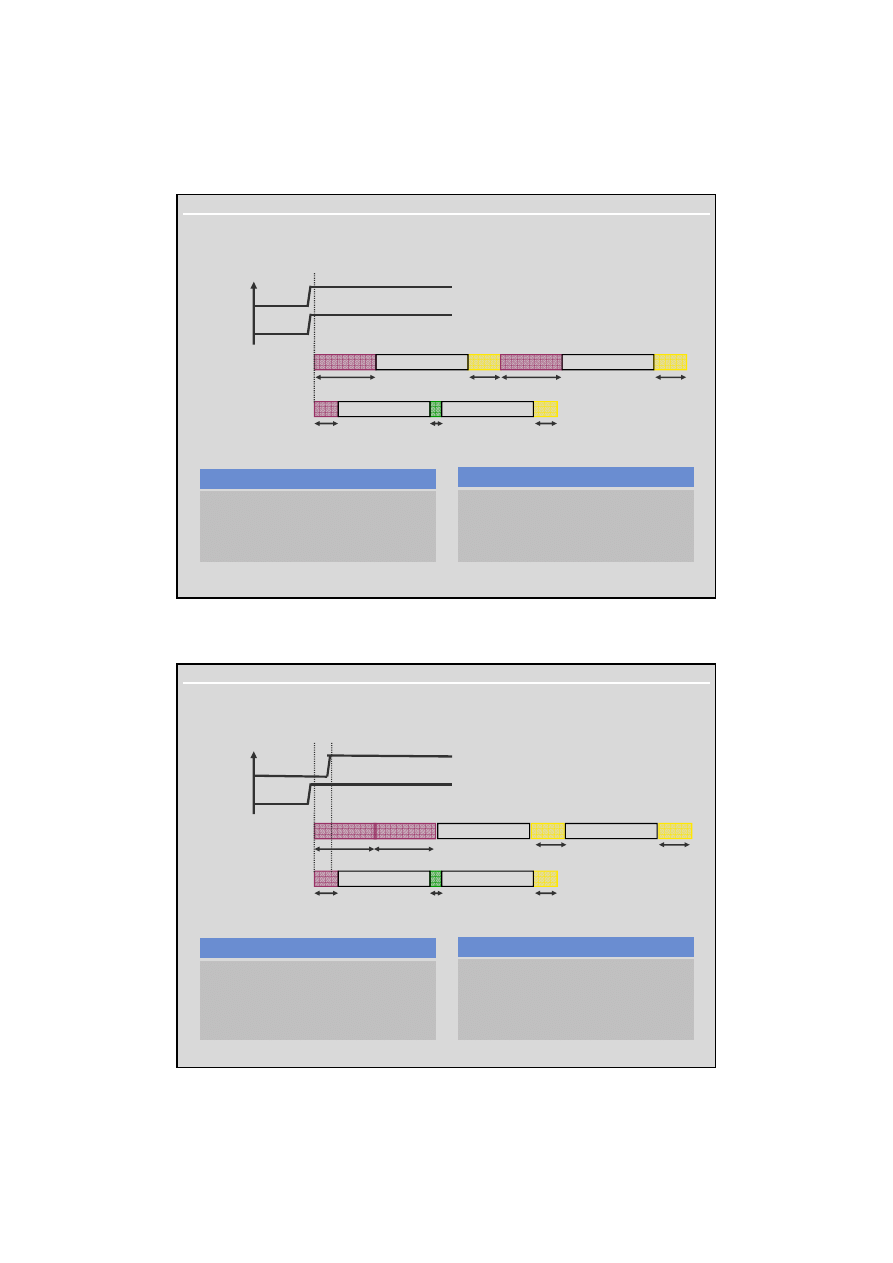

Rozpoczęcie obsługi:

- automatycznie procesor umieszcza na stosie zawartości rejestrów:

PC, xPSR, R0 – R3, R12, LR magistralą systemową AHB

- równocześnie pobierane są instrukcje obsługi przerwania (do kolejki prefetch)

magistralą Icode AHB

- oczekujące przerwanie o niższym priorytecie powstrzymuje operacje POP

Zakończenie obsługi:

- automatycznie procesor pobiera ze stosu odłożone zawartości rejestrów

- równocześnie pobierany jest przerwany ciąg instrukcji (do kolejki prefetch)

- nadchodzące przerwanie powstrzymuje operacje POP

2016-05-15

13

Architektura komputerów i systemy operacyjne

16

System przerwań T

Architektura komputerów i systemy operacyjne

17

System przerwań T

2016-05-15

14

Architektura komputerów i systemy operacyjne

18

Reakcja systemu przerwań

Push

ISR 1

Pop

Pop

ISR 2

Push

26 taktów

26 taktów

16 taktów

16 taktów

wzrost

IRQ1

IRQ2

ARM7TDMI

Obsługa przerwania

Cortex-M3

Obsługa przerwania

ISR 1

Pop

ISR 2

6 taktów

12 taktów

Push

12 taktów

Tail-Chaining

12 taktów od IRQ1 do ISR1

(przerywalne/ciągłe LSM)

6 taktów od zakończenia ISR1 do ISR2

12 taktów do powrotu z ISR2

Cortex-M3

26 taktów od IRQ1 do ISR1

(do 42 taktów w LSM)

42 takty od zakończenia ISR1 do ISR2

16 taktów do powrotu z ISR2

ARM7TDMI

Architektura komputerów i systemy operacyjne

19

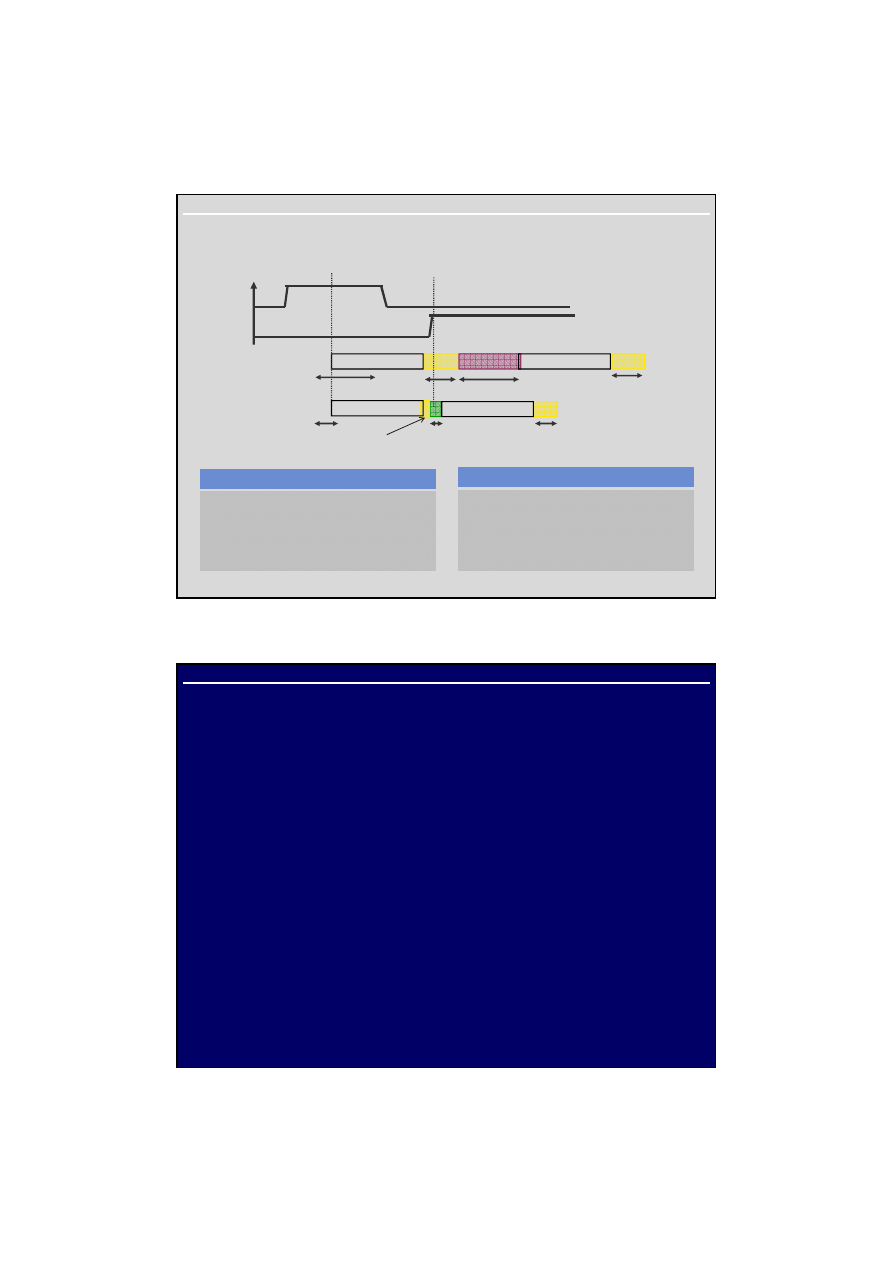

Reakcja systemu przerwań

12 taktów od IRQ do ISR:

- cykl stosowy i fetch

- cel ISR może być zmieniony aż do

ostatniego taktu, gdy IRQ1 się pojawia

Cortex-M3

26 taktów do ISR2 powiększone o do-

datkowe 26 do ISR1 po wystąpieniu IRQ1

ISR1 dołącza dodatkowe 16 taktów

powrotu do ISR2

16 taktów do powrotu z ISR2

ARM7TDMI

Push

ISR 1

Pop

Pop

ISR 2

Push

26 taktów

26 taktów

16 taktów

16 taktów

wzrost

IRQ1

IRQ2

ARM7TDMI

Obsługa przerwania

Cortex-M3

Obsługa przerwania

ISR 1

Pop

ISR 2

6 taktów

12 taktów

Push

12 taktów

Tail-Chaining

2016-05-15

15

Architektura komputerów i systemy operacyjne

20

Reakcja systemu przerwań

sprzętowo przerywany proces stosowy

POP wymaga tylko 6 taktów do ISR2

Cortex-M3

core musi dokończyć operacje stosowe

po ISR1 (pop) i ponowić je do ISR2 (push)

ARM7TDMI

ISR 1

Pop

Pop

ISR 2

Push

26 taktów

26 taktów

16 taktów

16 taktów

wzrost

IRQ1

IRQ2

ARM7TDMI

Obsługa przerwania

Cortex-M3

Obsługa przerwania

ISR 1

Pop

ISR 2

6 taktów

12 taktów

12 taktów

Tail-Chaining

przerwany Pop (1 do 12

taktów)

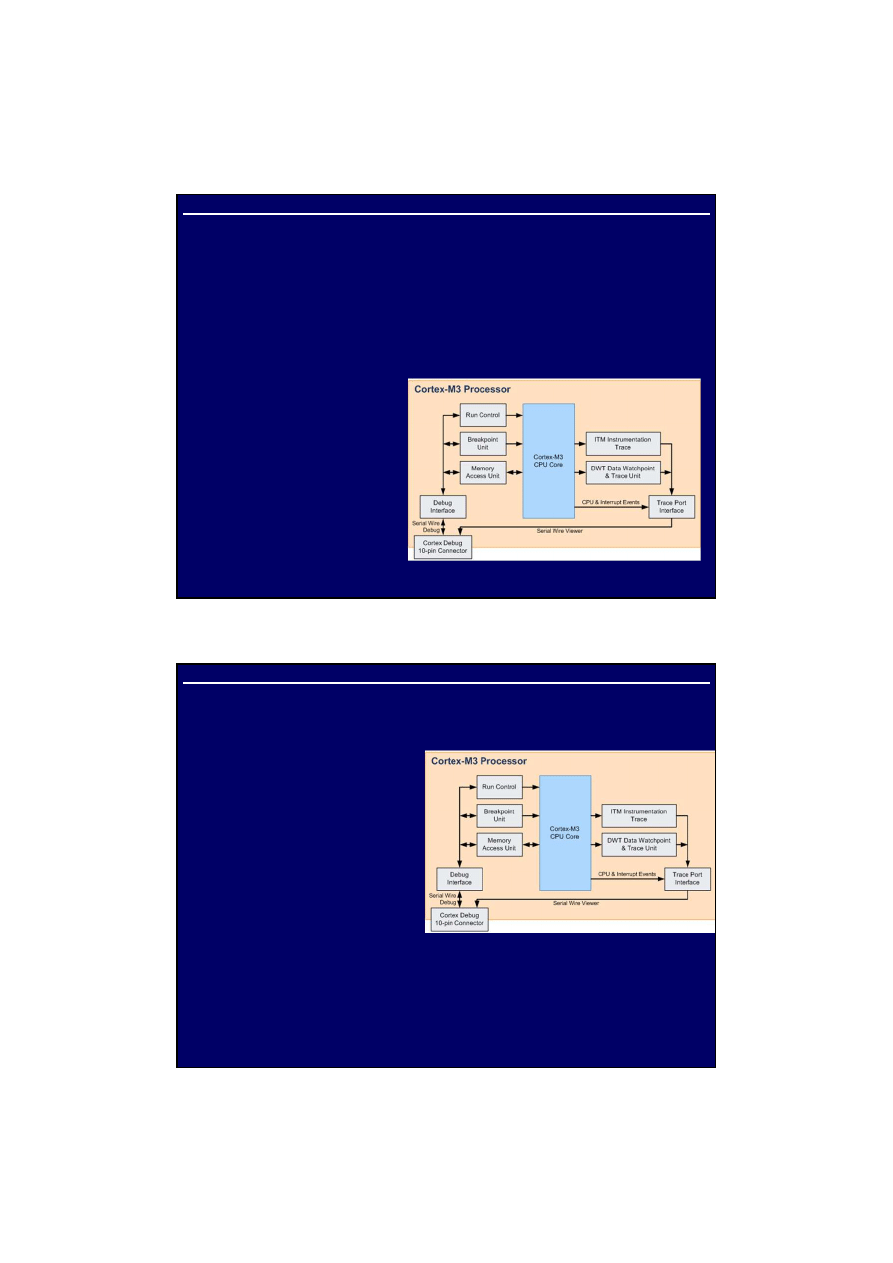

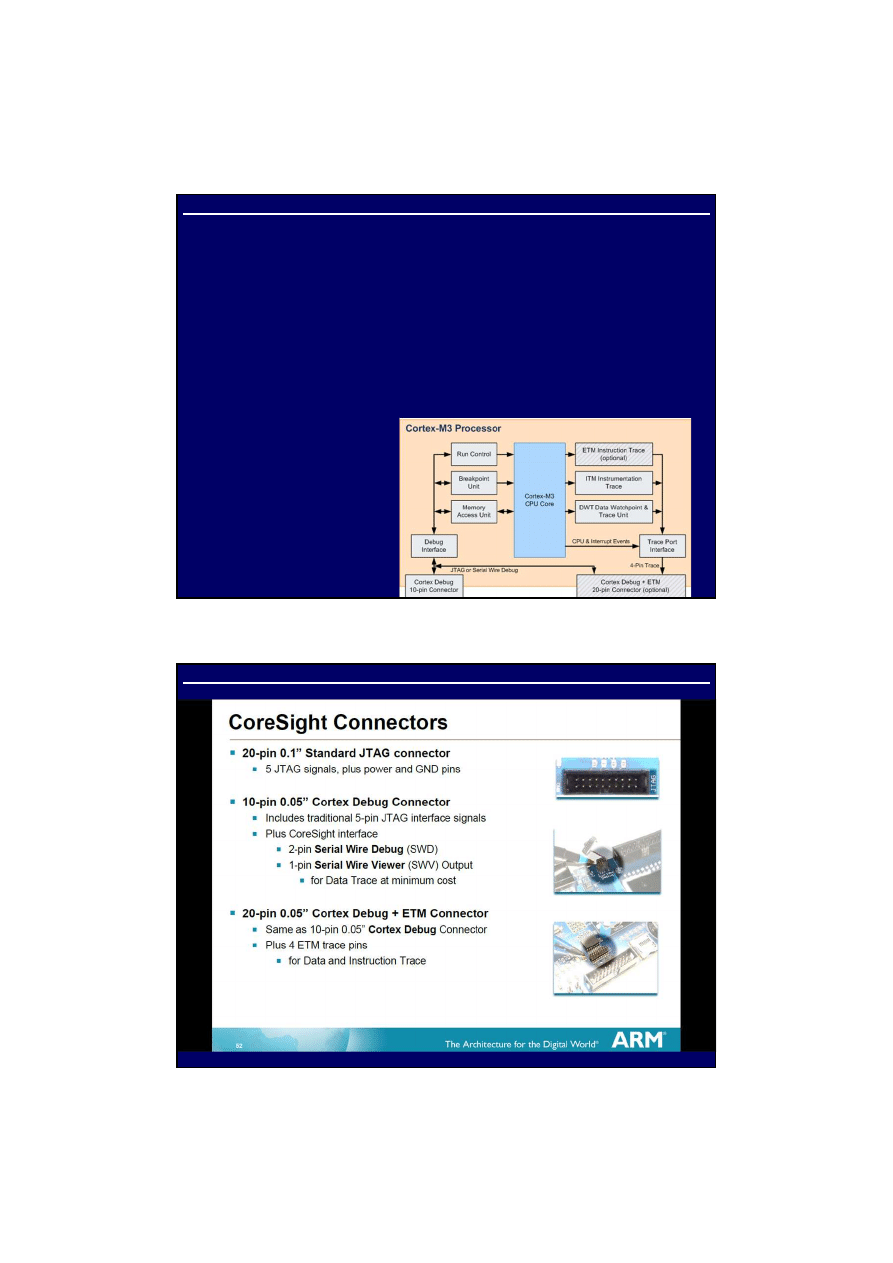

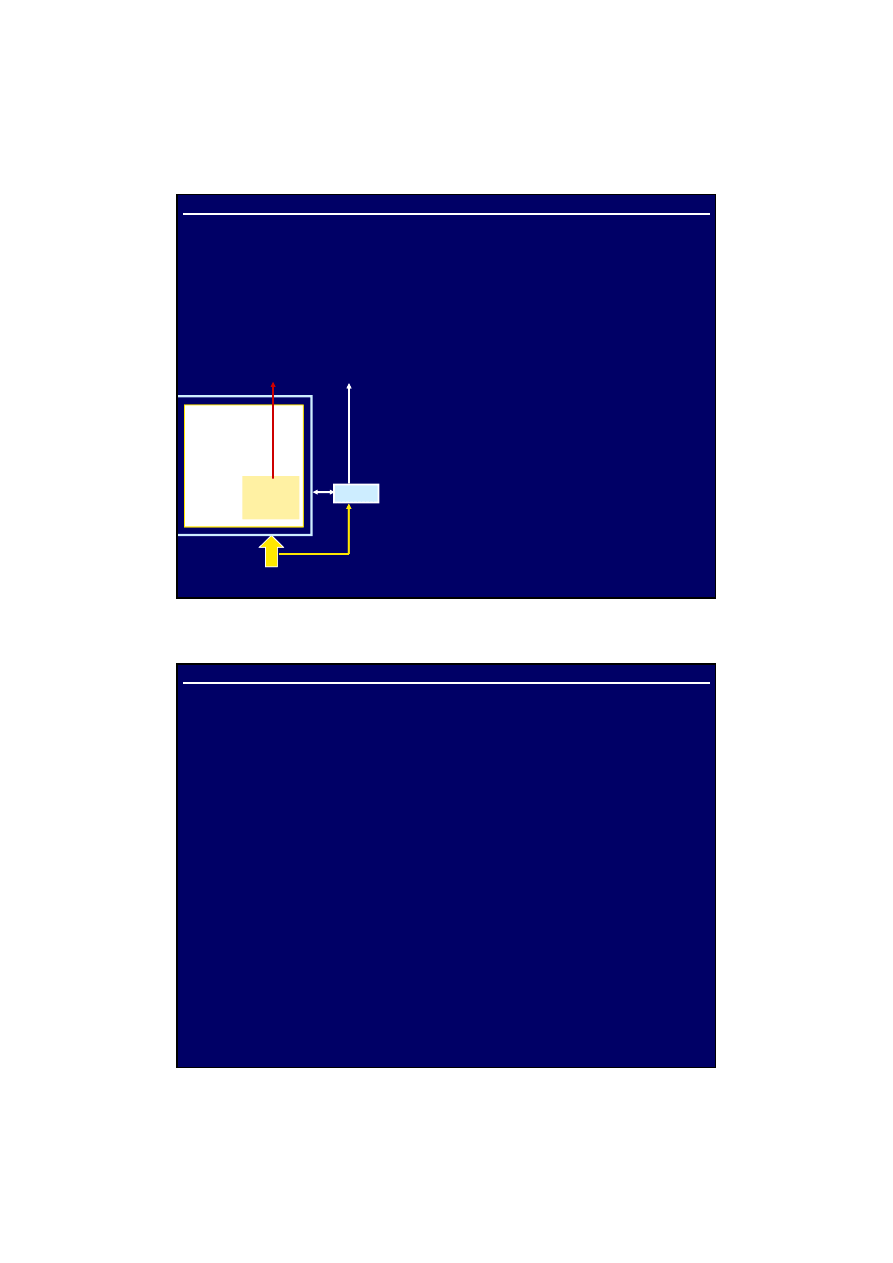

- ARM CoreSight jest pełnym wbudowanym systemem (system-on- chip) SoC

do debugowania programu i śledzenia jego wykonywania w czasie rzeczywistym

- elementy systemu mogą być konfigurowane lub nawet usuwane

- debugowanie w trakcie pracy procesora

- ustawianie punktów przerwań

- czytanie/pisanie pamięci

- bezpośredni dostęp do pamięci

- zwiększona liczba punktów przerwań i punktów obserwacji

Architektura komputerów i systemy operacyjne

33

System debugowania CoreSight

Elastyczne opcje śledzenia

- zintegrowane danych

- opcjonalne instrukcji (ETM)

Interfejsy:

- 2-pin Serial Wire Debug (SWD)

- 1-pin Serial Wire Viewer (SWV)

- Standard JTAG mode

2016-05-15

16

Architektura komputerów i systemy operacyjne

34

Proces debugowania prowadzony w czasie rzeczywistym

- blok kontroli przetwarzania RC - tryby: run, stop i krokowy

- blok pułapek sprzętowych BU - 8 breakpoints

- blok dostępu do pamięci i rejestrów MAU typu czytaj/pisz

- zapis do pamięci Flash i jej weryfikacja

CoreSight - debugowanie

Dostępne interfejsy:

- zredukowany 2-pinowy

Serial Wire Debug (SWD)

- standardowy JTAG 5-pinowy

Architektura komputerów i systemy operacyjne

35

CoreSight – śledzenie danych

Moduły:

- Instrumentation Trace Macrocell (ITM)

- Data Watchpoint and Trace unit (DWT)

Data Trace umożliwia:

- próbkowanie PC (Program Counter)

- liczniki zdarzeń rejestrujące

statystykę taktowania CPU

- realizacja wyjątków i przerwań

ze statystyką w czasie

ITM umożliwia:

- śledzenie danych użyte do analizy

czasowej lub prostego wykorzystania funkcji printf

Interfejs:

- Serial Wire Viewer (SWV) 1-pin w trybie Serial Wire

- zapewnia wyprowadzanie informacji i konfigurowanie DWT

- 4-pinowy port śledzenia + CKout

2016-05-15

17

Moduł Embedded Trace Macrocell (ETM) oferuje historię wykonania

każdej instrukcji po instrukcji.

Aktywuje:

- analizę historii wykonania instrukcji prowadzących do zdarzenia

- poszerzenie kodu programu

- analizę jakości

- optymalizację aplikacji

4-pinowy interfejs ETM

+ CKout

Architektura komputerów i systemy operacyjne

36

Moduł śledzenia wykonania programu ETM

CoreSight T

Architektura komputerów i systemy operacyjne

37

2016-05-15

18

Tryby obniżonego poboru mocy

Architektura komputerów i systemy operacyjne

38

Wake-up

External interrupts

Wake-up

sensitive

Interrupts

Power Management Unit

NVIC

Cortex-M3

WIC

Wake-up

External interrupts

Wake-up

sensitive

Interrupts

Power Management Unit

Deep

Sleep

Cechy systemu:

– aktywacja stanu ultra niskiego poboru mocy

– krytyczny dla zastosowań bateryjnych

– obecność modułu bardzo szybkiego wybudzania Wake-Up Interrupt Controller (WIC)

reagującego na krytyczny zewnętrzny wyjątek

- uśpienie

- bramkowany jest zegar do CPU

- wprowadzenie instrukcjami WFI lub WFE

- NVIC pozostaje wrażliwy na przerwania

- głębokie uśpienie

- ustawiany bit DeepSleep rejestru z.z. NVIC

- NVIC może być wprowadzany w stan

zatrzymania

- zatrzymanie

- wyłączone sygnały zegarowe i PLL

- czuwanie

- wyłączone sygnały zegarowe i PLL

- wył. stabilizator 1.8V (utrata danych RAM)

Zintegrowany licznik systemowy dla systemów czasu rzeczywistego

lub innych zadań, którego aktywne przerwanie pozwala na

przełączanie wątków:

- 24b dekrementowany

- 4 rejestry sterujące:

- CTRL - kontrolny i statusu

- LOAD - wartość przeładowana

- VAL - wartość bieżąca

- CALIB – wartość kalibracji

- nominalnie wyznacza czas 10ms

Wyjątek wektor #15

Dostępny w trybie uprzywilejowanym

- może być chroniony w aplikacji użytkownika

Timer SYSTICK (w module NVIC)

Architektura komputerów i systemy operacyjne

39

2016-05-15

19

Architektura komputerów i systemy operacyjne

21

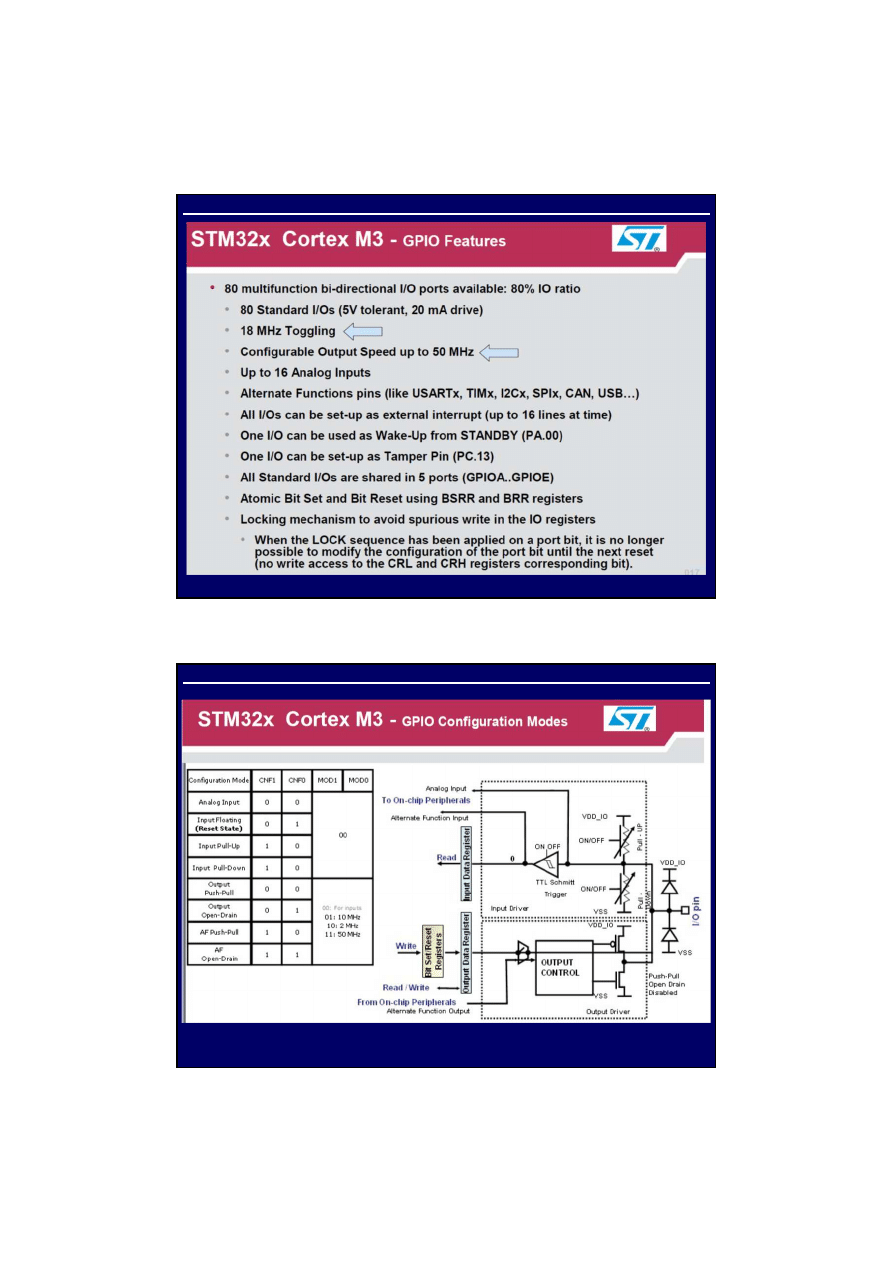

Wybrane układy peryferyjne

procesorów Cortex-M3

Architektura komputerów i systemy operacyjne

33

2016-05-15

20

Architektura komputerów i systemy operacyjne

33

Architektura komputerów i systemy operacyjne

33

2016-05-15

21

Architektura komputerów i systemy operacyjne

33

Architektura komputerów i systemy operacyjne

33

2016-05-15

22

Architektura komputerów i systemy operacyjne

33

Architektura komputerów i systemy operacyjne

33

2016-05-15

23

Architektura komputerów i systemy operacyjne

33

Architektura komputerów i systemy operacyjne

33

2016-05-15

24

Architektura komputerów i systemy operacyjne

21

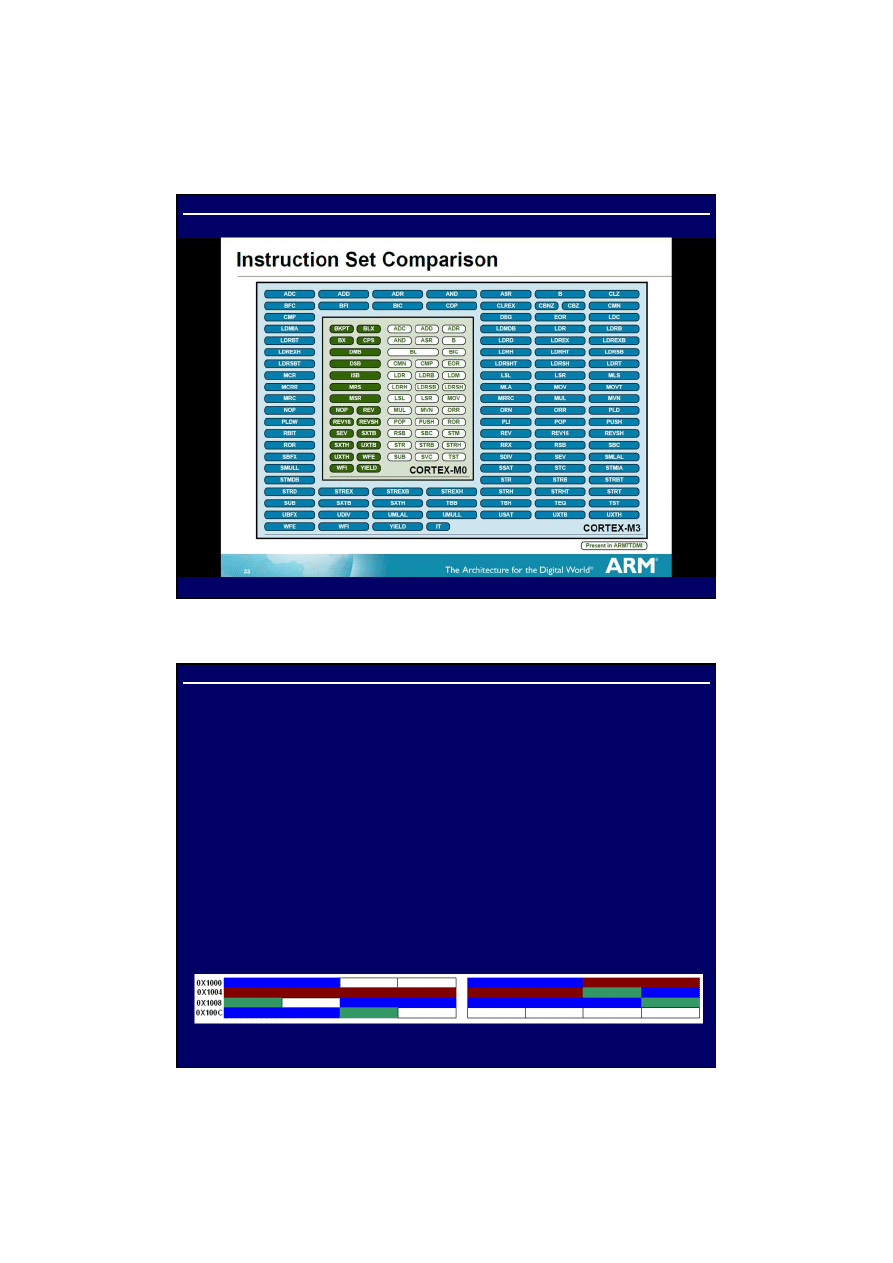

Lista instrukcji procesorów

Cortex-M3

Architektura komputerów i systemy operacyjne

21

2016-05-15

25

Architektura komputerów i systemy operacyjne

22

Architektura komputerów i systemy operacyjne

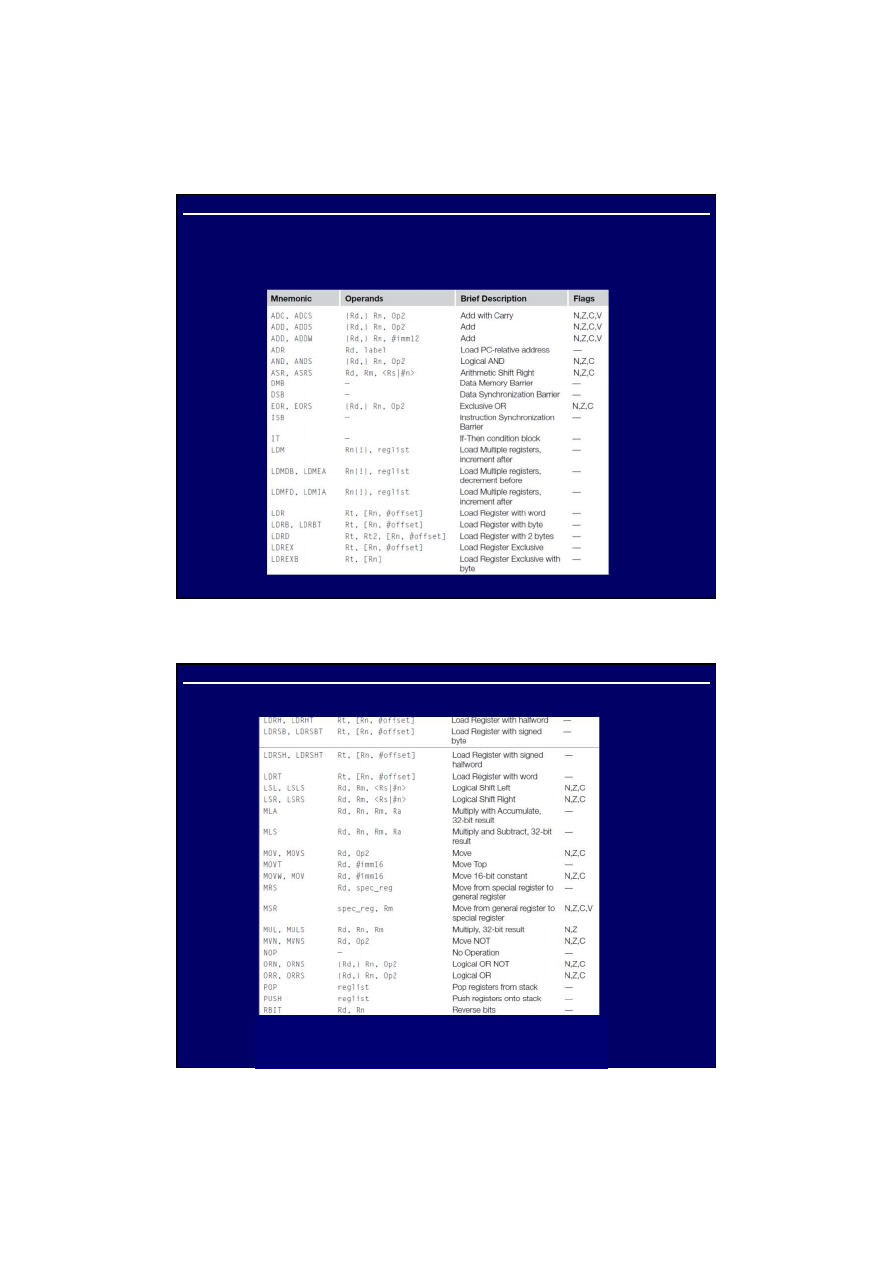

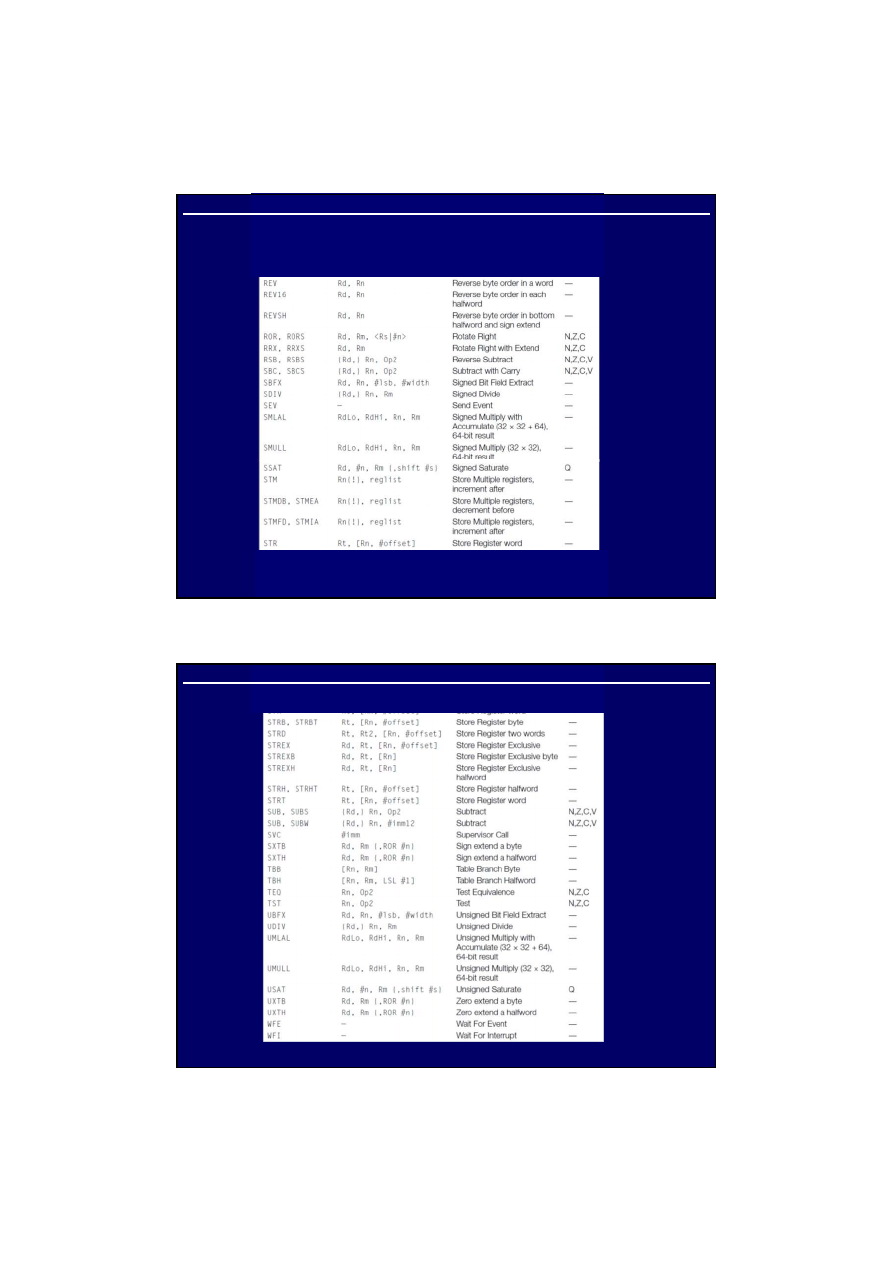

Lista instrukcji

Obejmuje rozkazy:

- przesłań (rejestrowe, blokowe)

- arytmetyczne i logiczne

- sterujące (skoki, wywołania podprogramów, pętle)

23

Aligned

Unaligned

Dane mogą być rozmieszczane w pamięci w sposób wyrównany (aligned) lub

niewyrównany (unaligned). Na rysunku każdy prostokąt stanowi bajt danych w różnych

typach tj. Long, Char i Integer

wymagających reprezentacji różnej długości. Białe

prostokąty stanowią niewykorzystaną przestrzeń pamięci. Poprzez ciągłe, wspólne

upakowanie zachodzi mniejsze zapotrzebowanie na rozmiar pamięci RAM.

2016-05-15

26

Architektura komputerów i systemy operacyjne

24

Lista instrukcji T

Na potrzeby zestawu instrukcji Thumb-2 utworzono dedykowaną odmianę asemblera

UAL (Unified Assembler Language) w celu uproszczenia wykorzystania instrukcji 16- i

32-bitowych

Architektura komputerów i systemy operacyjne

25

Lista instrukcji T

2016-05-15

27

System przerwań T

Architektura komputerów i systemy operacyjne

26

27

Architektura komputerów i systemy operacyjne

System przerwań T

Wyszukiwarka

Podobne podstrony:

AKiSO SS wykład 3 ISA

AKiSO SS wykład 8 I2C SPI 1W CAN

AKiSO SS wykład 9 syst operacyjne

AKiSO SS wykład 1

AKiSO SS wykład 2 CPU

AKiSO SS wykład 6 ZL27ARM

AKiSO SS wykład 5 cache

AKiSO SS wykład 4 potok sscalar

AKiSO SS wykład 2

AKiSO SS wykład 7 RS LPT FW USB

AKiSO SS wykład 0 E4x CYW wprowadzenie

AKiSO SS wykład 6 ARM wprowadzenie

więcej podobnych podstron