Active-HDL 6.3 SE User Guide

2

TABLE OF CONTENTS

INTRODUCTION ......................................................................................................................... 3

SYSTEM REQUIREMENTS ........................................................................................................ 3

INSTALLATION ........................................................................................................................... 3

ACTIVE-HDL 6.3 STUDENT EDITION LIMITATIONS................................................................. 9

USING THE ON-LINE DOCUMENTATION ............................................................................... 10

AUTOMATED FPGA DESIGN FLOW MANAGER..................................................................... 15

INSTALLATION – MODIFICATION OF PREVIOUS INSTALLS ................................................ 19

EXPORT/IMPORT OF ACTIVE-HDL PREFERENCES ............................................................. 19

ACTIVE-HDL PREFERENCES MANAGER OPTIONS.............................................................. 20

CONTACTING SUPPORT......................................................................................................... 21

3

INTRODUCTION

Active-HDL offers a completely integrated design entry and verification environment for HDL, C

and C++ designs. The product supports C/C++, SystemC, VHDL and Verilog designs, as well as

mixed SystemC/VHDL/Verilog and EDIF simulation. This Quick Start Guide was created to

better acquaint users with the software’s installation process, using the online help files and the

toolbars that are included within the product.

License

The Student Edition of Active-HDL 6.3, does not require any keylock or license file.

SYSTEM REQUIREMENTS

Active-HDL requires:

•

A Pentium PC or Higher/Compatible

•

128 MB Physical Memory (256 MB Recommended)

•

Microsoft Windows NT 4.0 with Service Pack 6, Windows 2000® with Service Pack 3

(recommended) or Windows XP® with Service Pack 1 (recommended)

•

Microsoft Internet Explorer™ version 4.0 or higher (see notes)

•

Hard Disk Drive with at least 360 MB of free space (for Vendor Independent Edition)

•

Monitor resolution 1280x1024 (recommended)

NOTES:

•

The amount of available physical memory limits the maximum size of the design that can be

simulated in Active-HDL.

•

If you want to install Active-HDL 6.3 on Windows NT with Service pack 6, Internet Explorer

ver. 4.0 or higher is required. Otherwise, Active-HDL will be not installed.

•

For full functionality, it is recommended to install Microsoft Internet Explorer version 5.0 or

higher. If Microsoft Internet Explorer is not available the following system components will be

no available:

- Dataflow Window

- Query window in Block Diagram

- On-line documentation

•

If you have a browser other than Internet Explorer installed on your system, you can

continue to use it without any problems. Internet Explorer can be installed as a non-default

browser and be used only by Active-HDL.

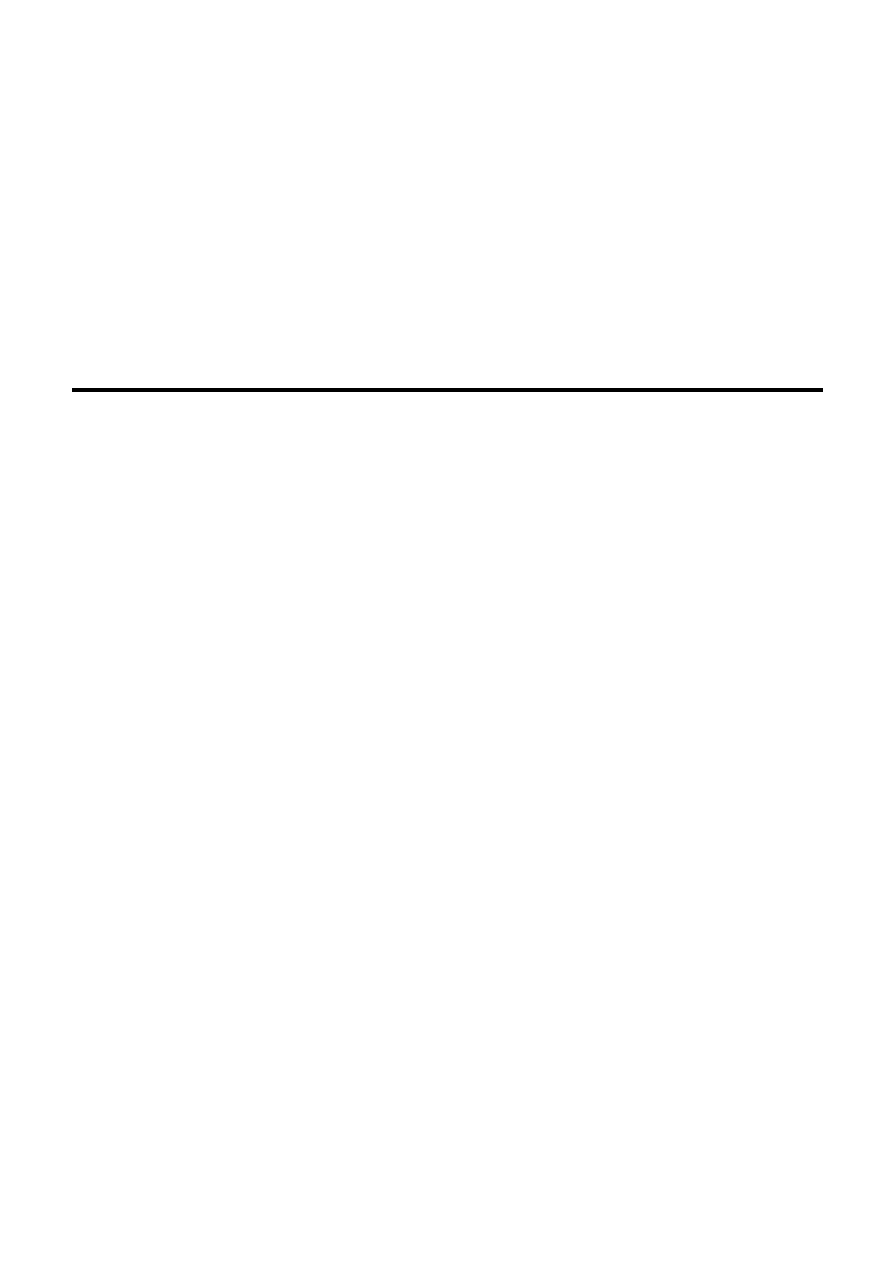

INSTALLATION

When you receive your copy of Active-HDL, insert the CD-ROM into your machine’s CD-ROM

drive. Active-HDL is equipped with an “Auto-Run” feature that will start the set-up process

without having to locate the setup.exe file. At this point you have the option to read the release

notes on the product or begin the installation process.

NOTE:

The regular version of Active-HDL 6.3 and the Student Edition cannot be installed on the

same computer. Only the latest installation will work correctly

4

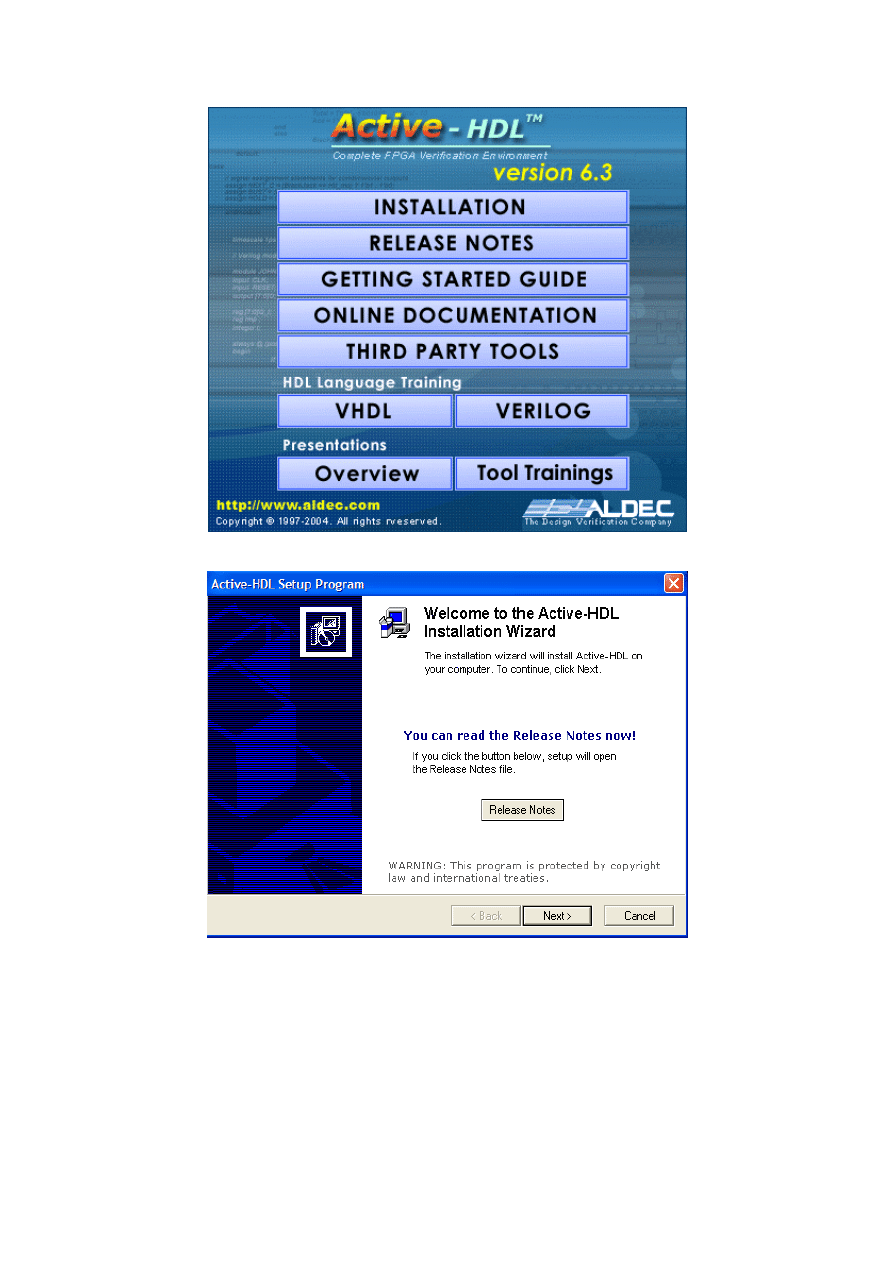

After reading the release notes or selecting the Next button, you will be asked to read the

software’s licensing agreement. Read this section carefully and when finished, choose the

Accept button.

Note: The release notes may be accessed at any time once the software is installed by opening

the on-line documentation.

5

Next, you will need to fill in the user information for the software and choose whether or not

anyone else will be allowed to access the software from the machine it is installed on. Select

Next to continue.

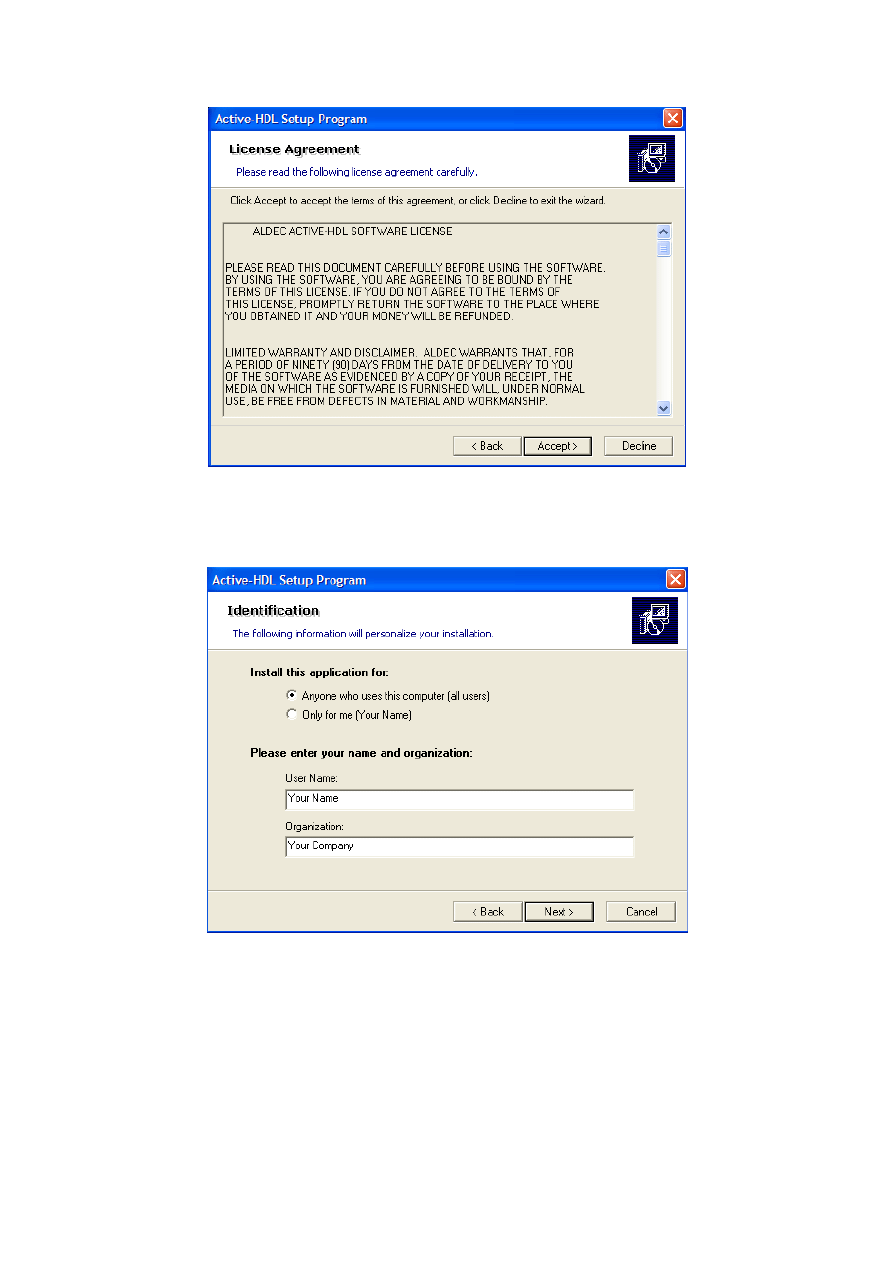

The installation program of Active-HDL Student Edition allows users to install different libraries

that are copied during the installation. Dialog below allows installing Verilog, VHDL, as well as

both types of libraries.

6

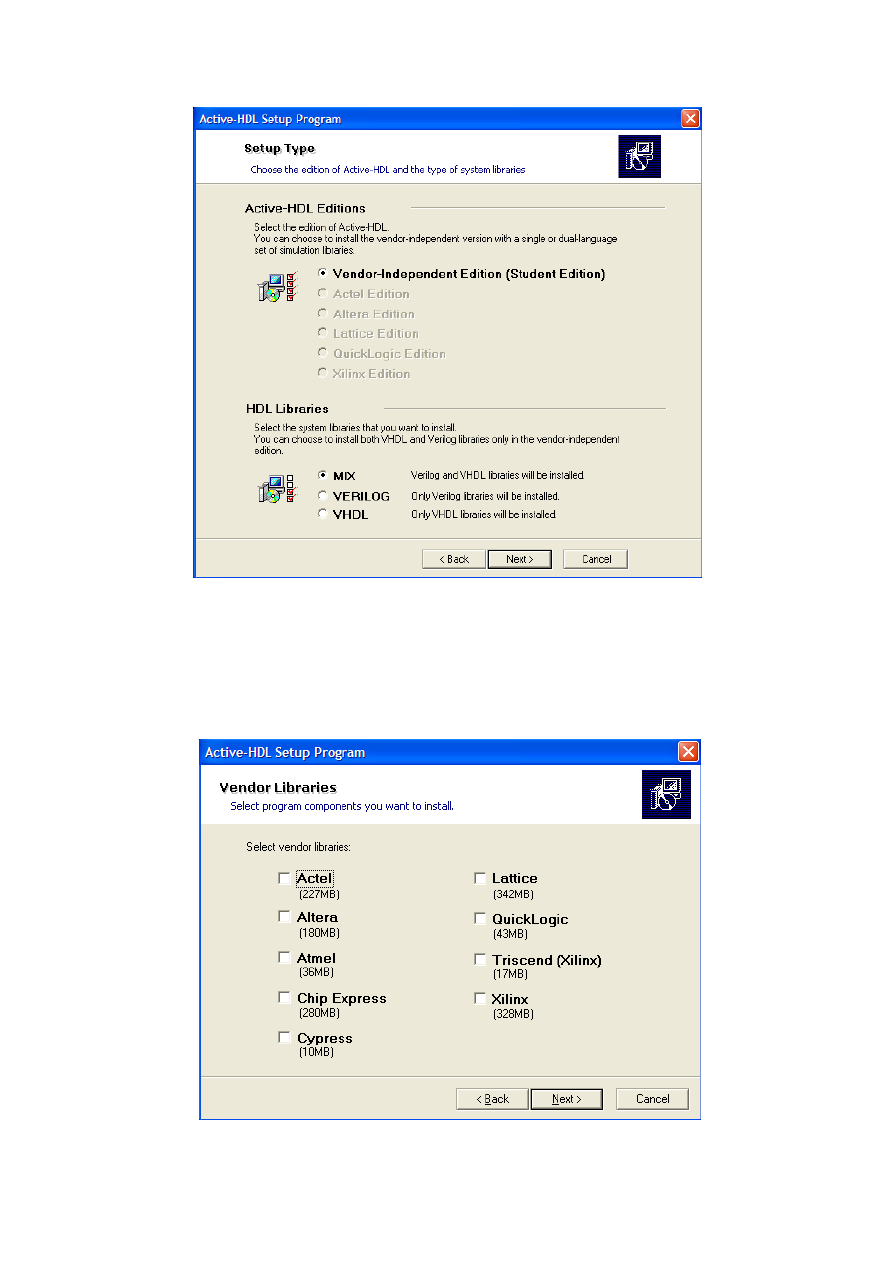

•

In the next stage of the installation process, you will need to choose which pre-installed IC

vendor libraries you will require for your designs. All libraries are based on the latest files

provided to Aldec at the time the software was produced. Please check with the appropriate IC

vendor for the latest library resources.

7

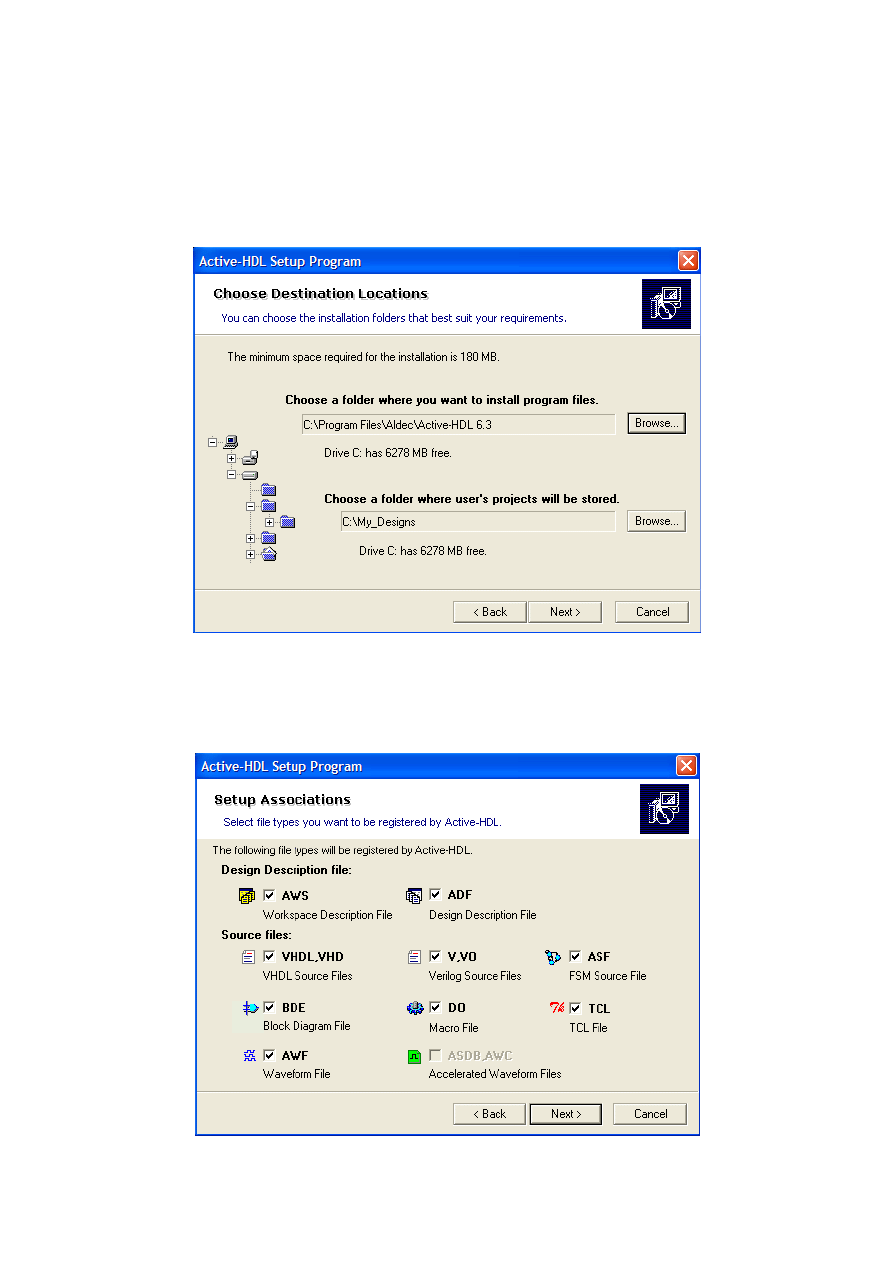

After you designate the necessary libraries and click the Next button, you must choose the

destination path for the Active-HDL software to be installed on your machine. By default, Active-

HDL already has a path selected and will create the required folders on your system’s “C” drive.

If you wish to select a new destination, choose the Browse button and locate space for both the

software’s program files as well as any projects you will create with Active-HDL.

The next step is to select the file types you wish to register to

Active-HDL. For each file selected, Active-HDL will be the default program associated when

working with these files. By default, each file is checked for use with Active-HDL. Click Next to

continue with the installation.

8

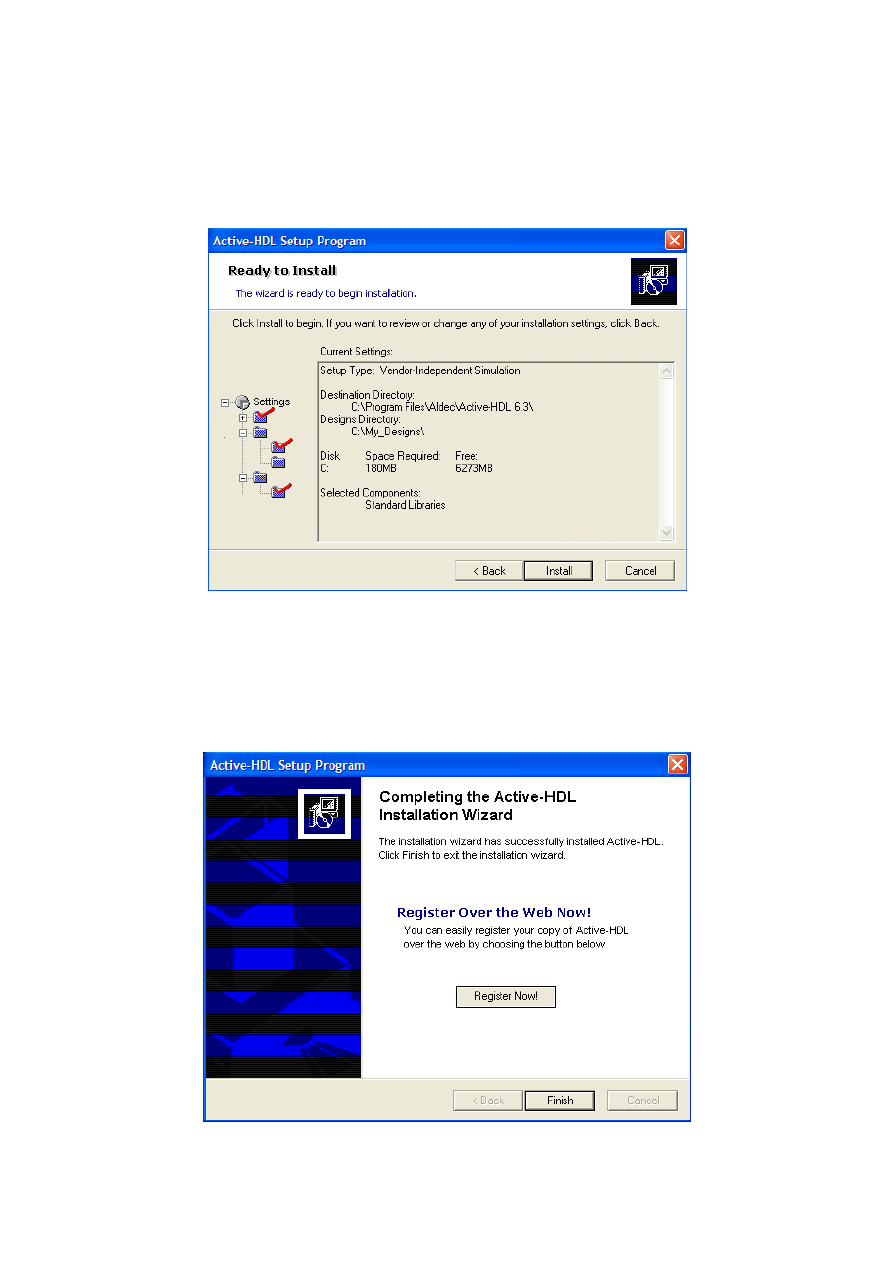

You may wish to check the information listed in this screen to verify that all paths and

associations are correct. If not, you may click the Back button to return to the appropriate stage

of the installation setup and make any changes. Choose Install when you are ready to begin

copying files to your system.

You are able to watch as files are transferred to your system. Setup is complete when all files

are copied to your designated location.

When the installation is complete, you have the option to immediately register your copy with

Aldec to ensure you receive the latest updates and product information. Choose Register Now

and fill out the simple form or click Finish to conclude the installation process.

9

ACTIVE-HDL 6.3 STUDENT EDITION LIMITATIONS

This edition provides the following limitations in comparison to the functionality of a regular

version:

•

The network installation is not available

•

The new design names are restricted to Design0 ... Design10

•

The mixed VHDL-Verilog simulation is not supported

•

The off-line simulation (Post Simulation Debug) is disabled

•

The co-simulation of SystemC modules is disabled

•

The co-simulation of Handel-C blocks is disabled

•

The maximum size of a compiled VHDL/Verilog source file is 20kB

•

The maximum amount of memory allocated during simulation is 20MB

•

The simulation of EDIF netlists is disabled

•

The compilation of Verilog sources by using the averilog command is not support

•

The Batch mode (VSimSA) is not available

•

The Edit mode is disabled in the Standard Waveform Editor window

•

The testbench generation based on standard waveform files (*.awf) is disabled

•

The testbench generation with results comparison in VHDL and Verilog is disabled

•

The testbench generation for VHDL and Verilog state machines is disabled

•

The block diagram can contain up to 20 symbols/fubs

•

The state diagram can contain up to 20 states

•

The comparison of simulation results saved in AWF files is disabled in the GUI and the

command line

•

The import of Active-CAD projects is disabled

•

The import of Viewlogic projects is disabled

•

The 'Export to HTML' option allows exporting block and state diagram that contain up to

20 symbols/fubs and 20 states as well as source files that contain up to 200 lines of a

source code.

•

Protecting and refreshing a library is disabled

•

Xilinx schematic libraries are not installed

Additionally, the following tools are not available:

•

Accelerated Waveform Viewer

•

Advanced Dataflow

•

C Code Debug

•

Code and Toggle Coverage

•

Code2Graphics Conversion Wizard

•

Design Profiler

•

Memory Viewer

•

PLI/VHPI Wizard

Third-party interfaces:

- Denali Memory Interface

- Debussy Interface

- Simulink Interface

- Cover and DVM Interface

- Source Revision Control Interface

10

- SWIFT Interface

•

VHDL Signal Agent

•

Xtrace

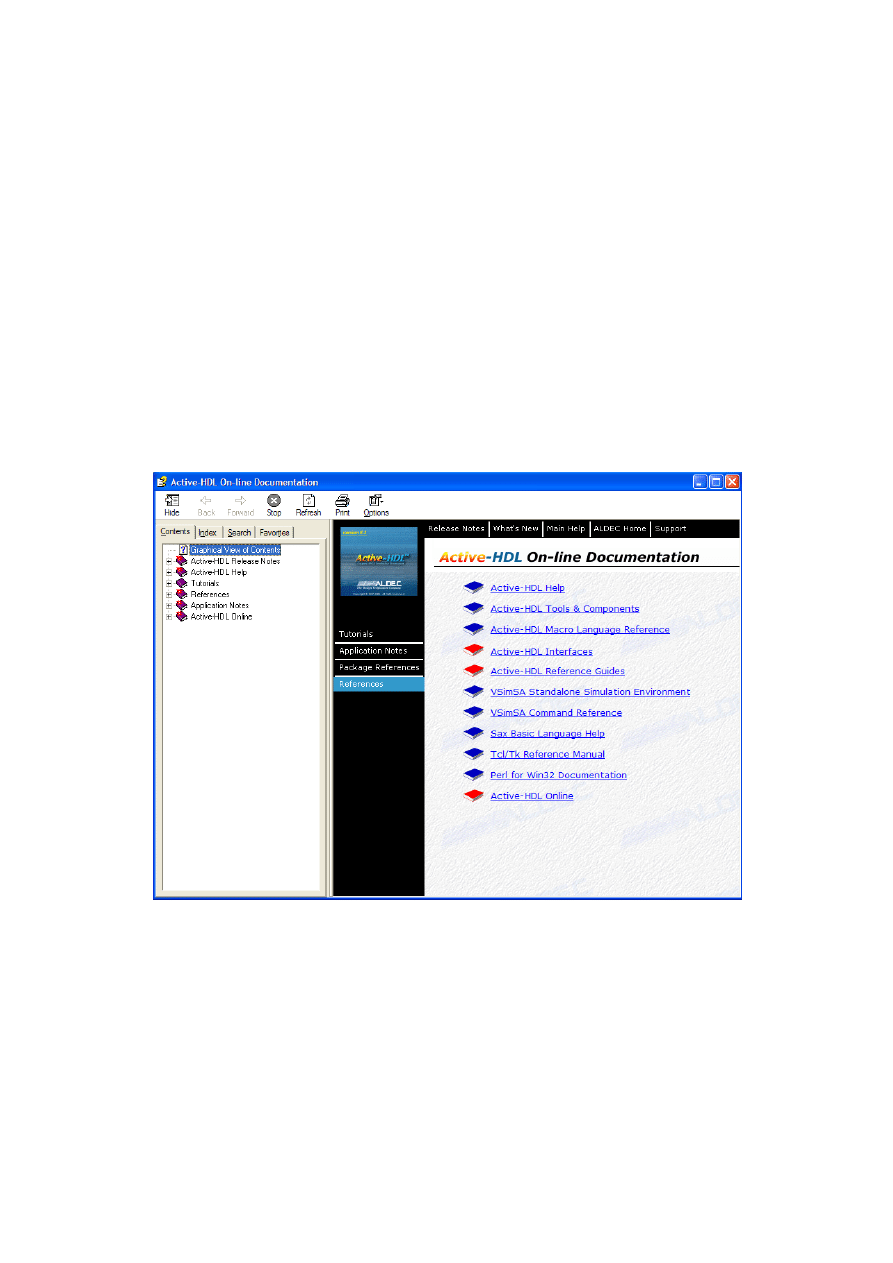

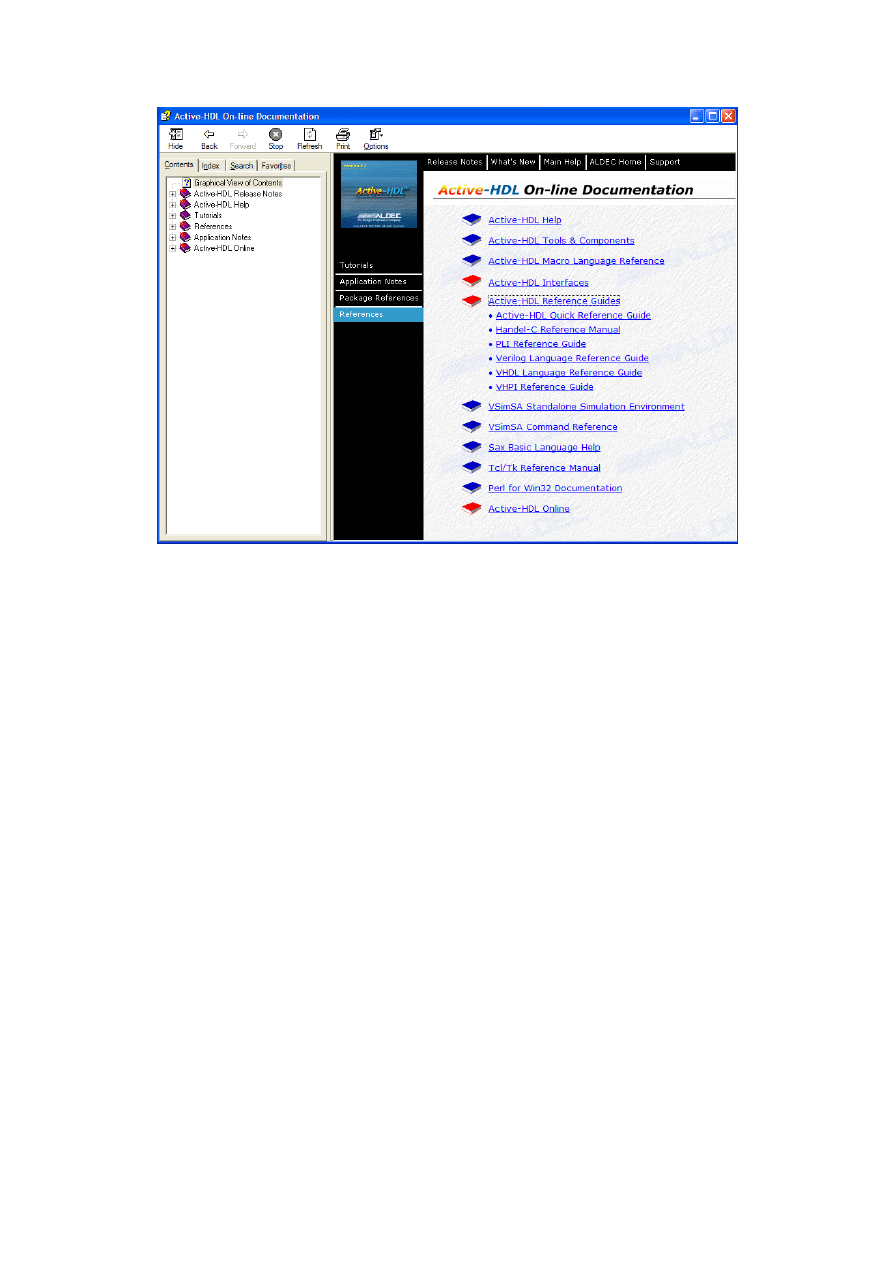

USING THE ON-LINE DOCUMENTATION

As you begin to familiarize yourself with the software, there are some useful resources available

to help use the tool effectively. Aldec has developed the in-depth on-line documentation and

tutorials for those who are new to HDL design or just new to Active-HDL.

Locating the On-line Help

From the Help menu on the tool bar of Active-HDL, select the On-line Documentation option.

This will open a new window with the complete on-line resources. It is highly recommended that

you spend some time exploring the on-line resources, as they can be very valuable tools.

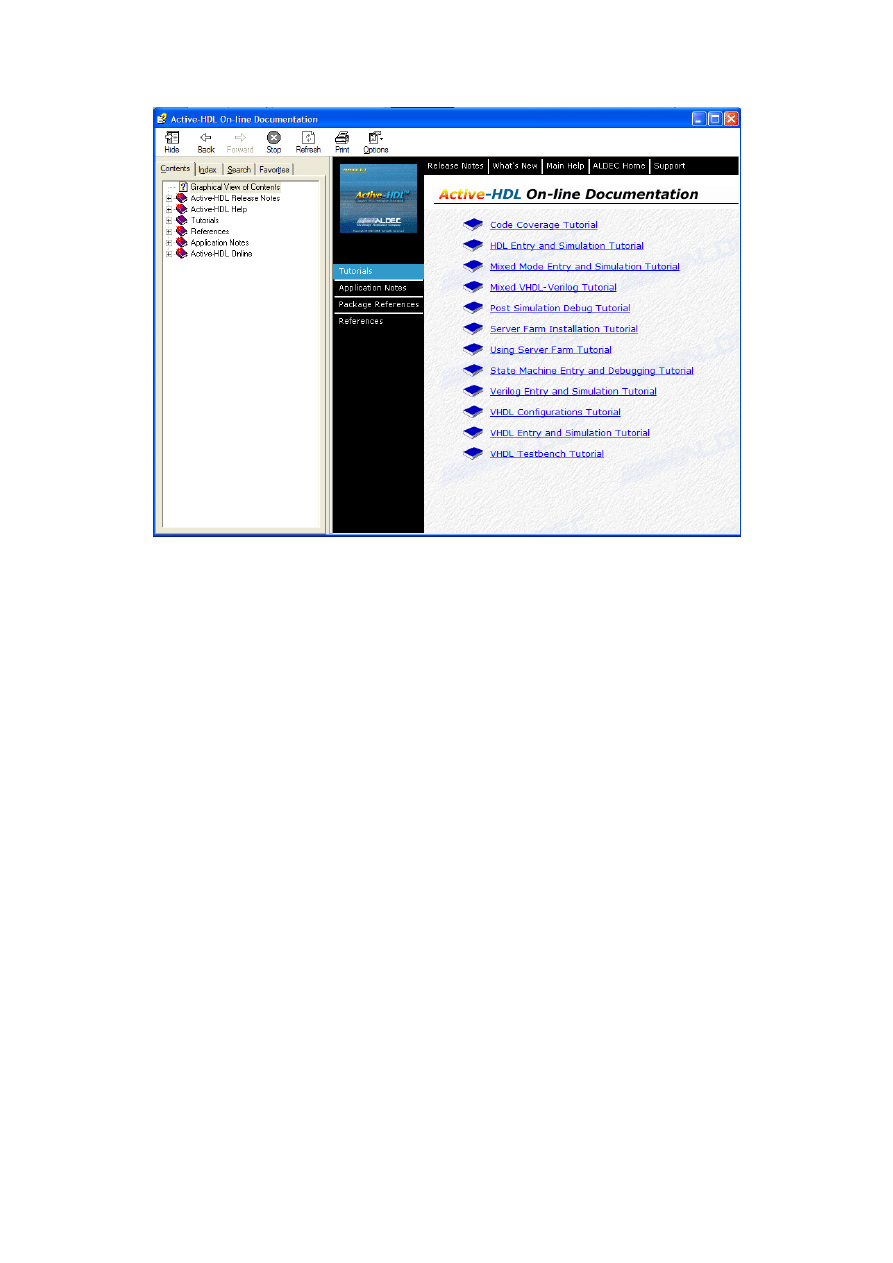

Tutorials and Reference Guides

The Tutorials located in Active-HDL’s on-line documentation include a variety of information.

From the main menu of the on-line Help, highlight the Tutorials section by left clicking once on

the appropriate button.

11

Tutorial Topics Include:

•

VHDL Entry and Simulation Tutorial

•

Verilog Entry and Simulation Tutorial

•

Mixed VHDL/Verilog Entry and Simulation

•

HDL Design Entry and Simulation Tutorial

•

State Machine Entry and Debugging Tutorial

•

Mixed VHDL/Verilog / EDIF Entry and Simulation

•

VHDL Testbench Tutorial

•

Code Coverage Tutorial

•

Post Simulation Debug Tutorial

•

Server Farm Installation Tutorial

•

Using Server Farm Tutorial

•

VHDL Configurations Tutorial

The Reference Guides are educational resources that can be accessed and used in the same

manner as the tutorials covering the following topics:

12

Reference Guide Topics Include:

•

Active-HDL Interfaces – Defines interfaces with Debussy, Denali, SWIFT, VHPI, DVM,

CoVer, Simulink®, SystemC, and SWIFT™ SmartModels Library Interface

•

VHDL Language Reference Guide – Defines terminology and gives examples of the

topics contained within the language

•

Verilog Language Reference Guide – Defines terminology and gives examples of the

topics contained within the language

•

PLI Reference Guide – Defines all components of PLI

•

VHPI Reference Guide – Defines all components of VHPI

•

Handel-C Reference Guide – Defines all components of Handel-C

•

VSIMSA – Defines internal and external commands

•

Sax Basic Language Help - The Sax Basic Language provides the core language

definition. It is Visual Basic for Applications™ compatible.

•

Tcl/Tk Reference Manual – Provides the Tool Command Language definition and

variables.

•

Perl for Win32 – Describes the Perl language and OLE and Win32 extensions

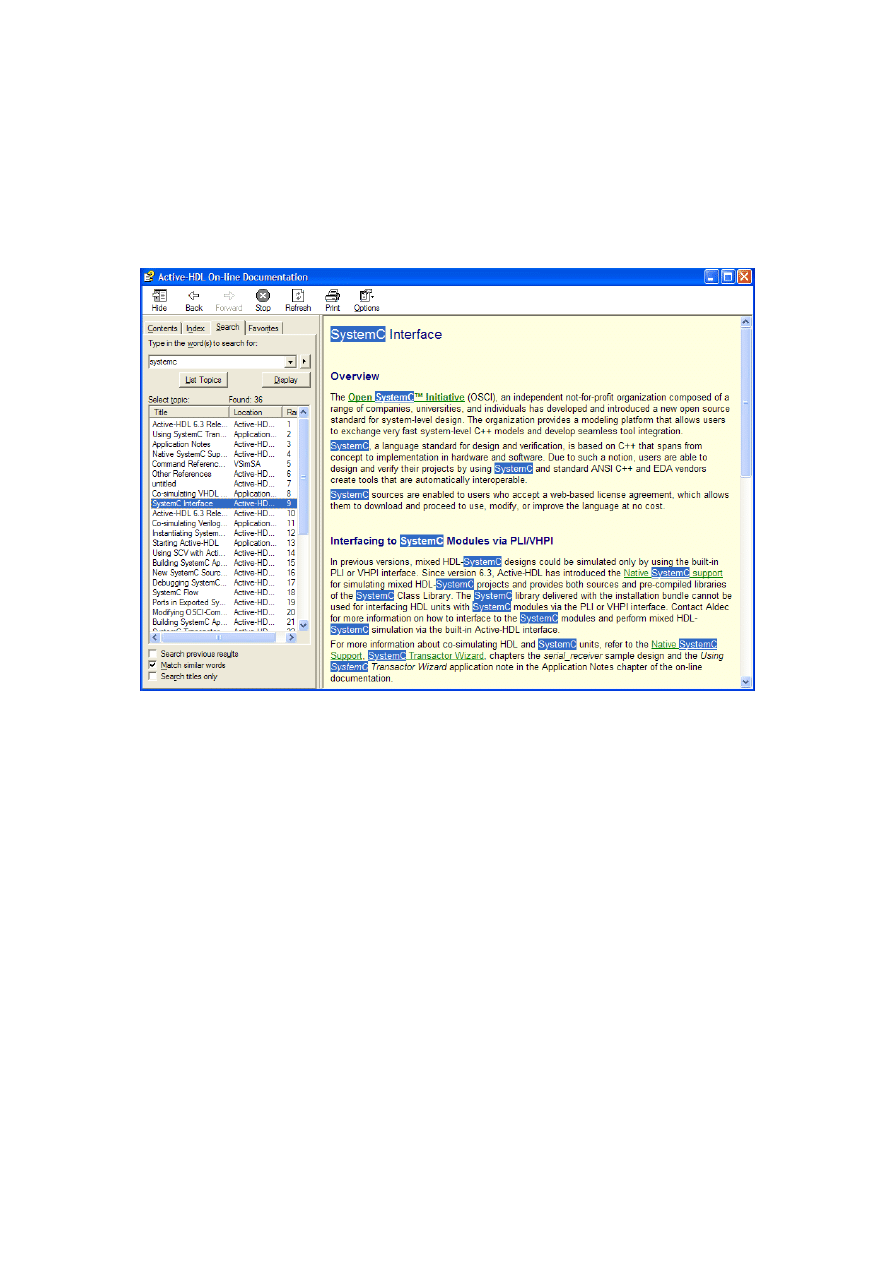

Searching for Help on a Specific Topic

Searching for help on a specific topic is easy and can be important for saving time spent

contacting Aldec support. There are multiple ways to search the on-line help:

•

Locate Help from the Contents Hierarchy

•

Find Help by Titles in the Index

•

Search for Help with Keywords

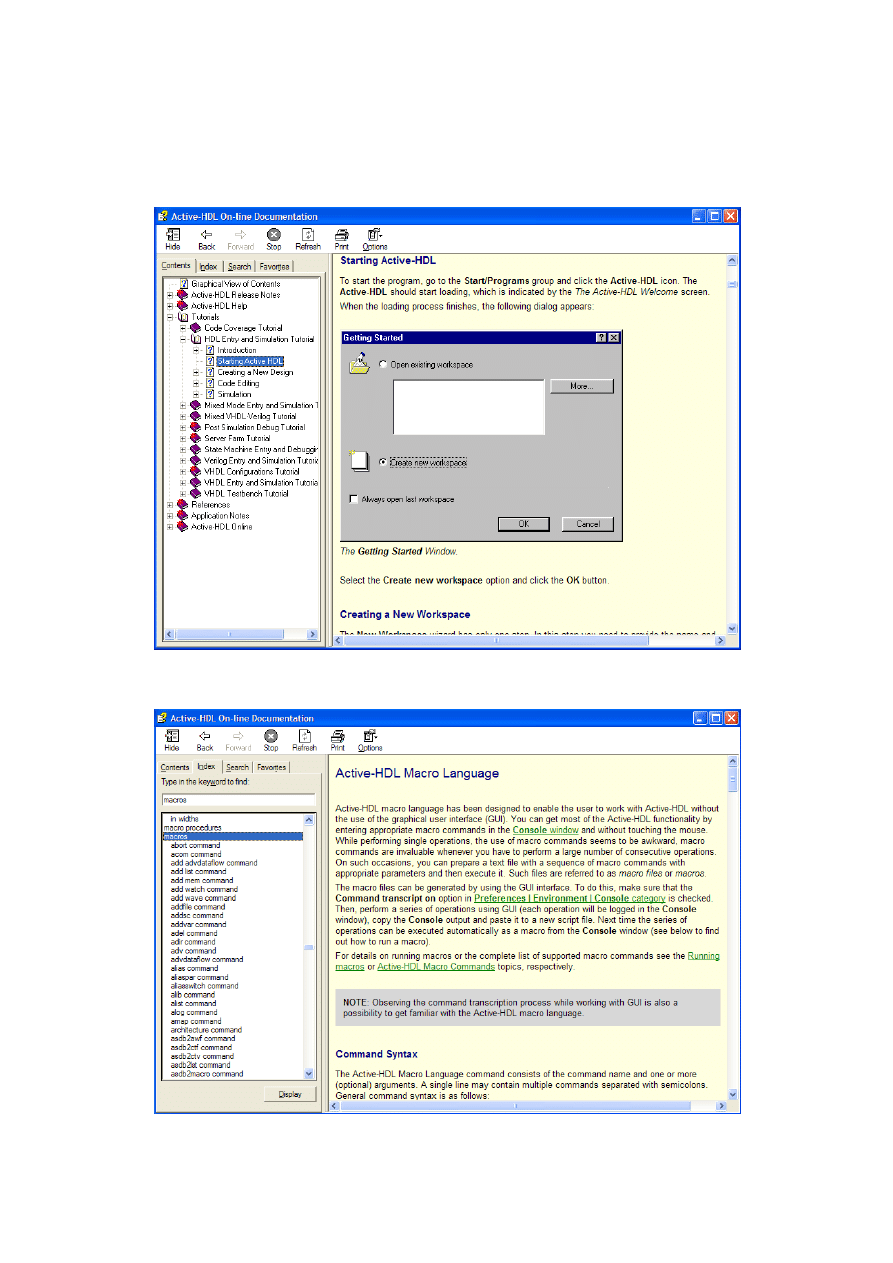

Search from Contents Hierarchy

13

Select the Contents tab on the left side of this window. Click on the hierarchy on the left of this

window; find the topic you are looking for. Click the topic to display the information in the window

on the right side.

Index Search

By typing in a few letters of a topic in the field below the Index tab, the search displays all help

14

titles starting with those letters. Double click a topic to display the information in the window on

the right side.

Search for Help by Keyword Phrase

Select the Search tab and type in the subject of the information you are seeking in the field

below the tabs. The on-line help will locate the titles matching your description by the keywords

you enter.

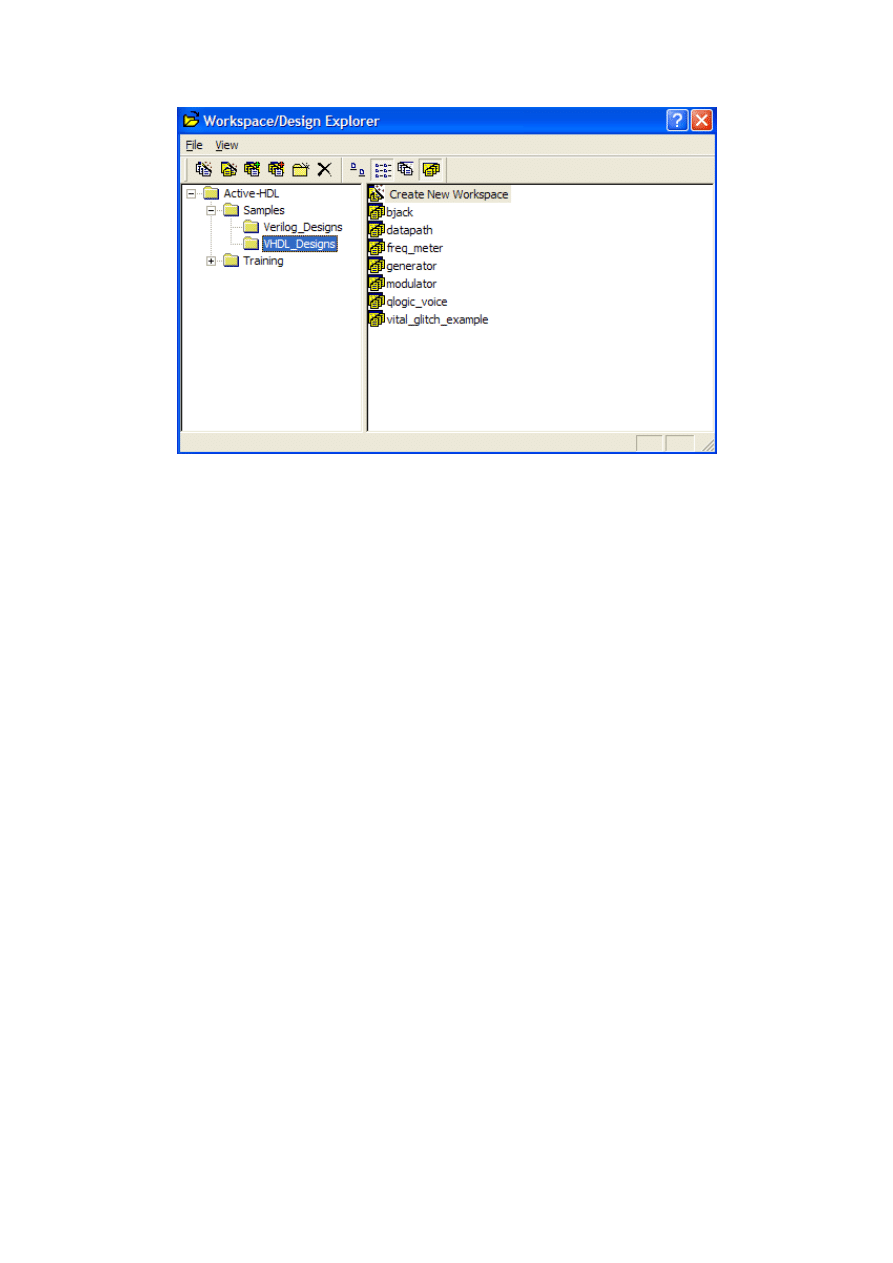

Sample Designs

Active-HDL comes with a series of sample designs that allow users to open a small design and

practice using the software on real world applications. Users are encouraged to load a sample

design and experiment with all of the tool’s features before beginning a new project.

These designs can be accessed by clicking File on the main tool bar and selecting Open

Workspace/Design Explorer.

The Workspace/Design Explorer window will then open and you can select Schematic, Verilog

or VHDL designs. When you select a folder in the left window, all sample designs in that folder

will be displayed in the window on the right.

15

Double clicking on the design will automatically open the design files in the design browser.

Note: It is recommended that you refer to the On-line Help after you have opened a design for

Tutorials and Documentation on some of the features of Active-HDL.

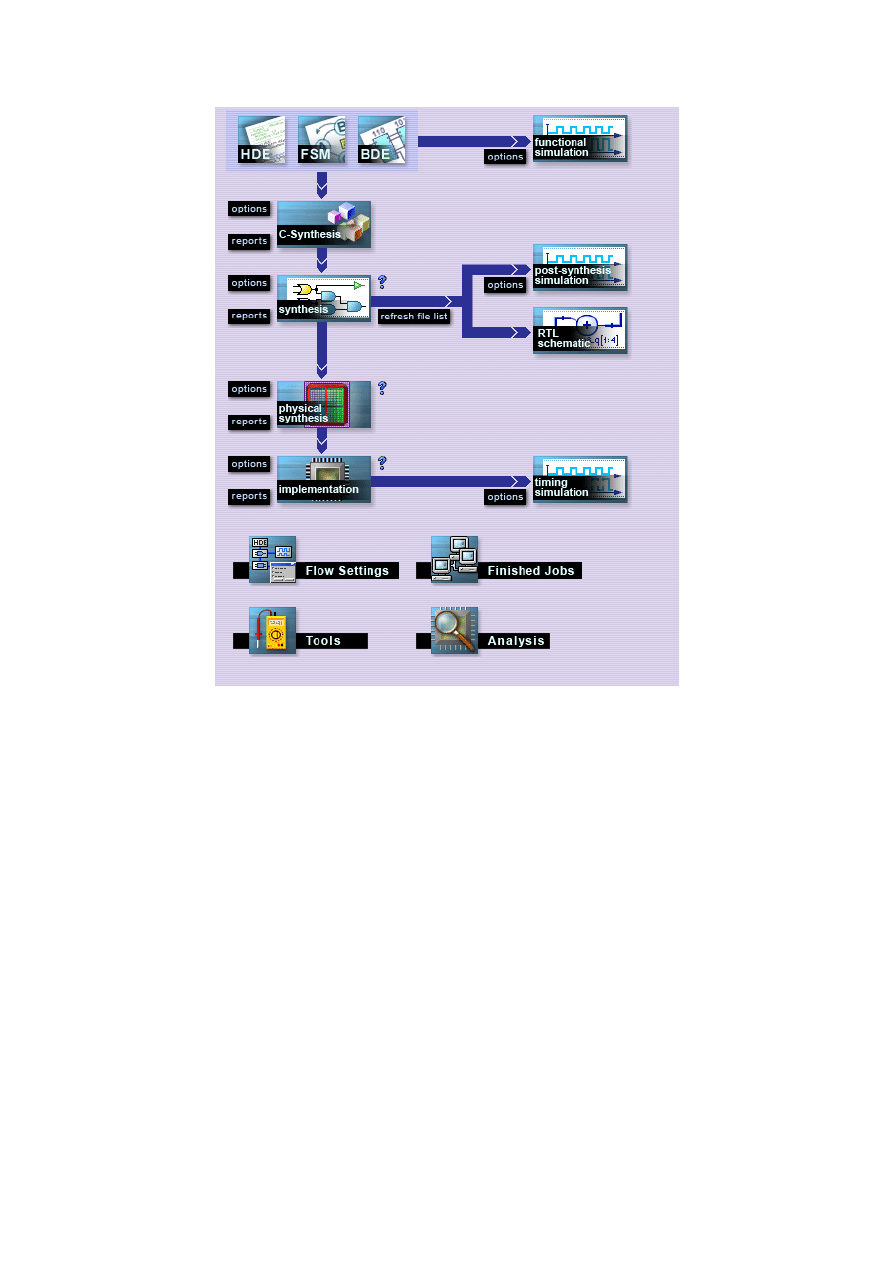

AUTOMATED FPGA DESIGN FLOW MANAGER

Active-HDL offers complete design flow integration for all leading EDA vendors with its Tcl-

based flow selection. The Design Flow Manager supports designs regardless of vendor tools or

type of chip. This independence is of most benefit to system designers because third party EDA

tools can all be invoked from a single location and designers can have one common tool to use

in all designs.

16

Synthesis Vendors Supported:

•

Altera Quartus™ II 4.1 SP2 Synthesis & Implementation

•

Celoxica™ DK3

•

Magma Palace 2.4

•

Cypress Warp® 6.3 SP1 Synthesis & Implementation

•

Exemplar Leonardo 2004a_30

•

Synopsys

FPGA Express 3.6

•

Synopsys

FPGA Compiler II 3.8.2

•

Synplicity

Synplify 7.7

•

Synplicity

Synplify Pro 7.7

•

XST VHDL/ISE 5.x XST VHDL

•

XST Verilog/ISE 5.x XST Verilog

•

XST Verilog/ISE 6.x XST VHDL/Verilog

Implementation Tools Supported:

•

Actel Designer™ R 6.0 SP1

•

Altera MAX+plusII

10.2

•

Altera Quartus™ II 4.1 SP2 (incl. Web Edition)

17

•

Atmel Figaro IDS 7.5

•

Cypress Warp

6.3 SP1

•

Lattice ispLever™ v.4.1 SP1

•

Quicklogic™ Quickworks 9.6

•

Triscend FastChip™ 3.0

•

Xilinx

Alliance 3.3/4.x

•

Xilinx

Foundation 3.3/4.x

•

Xilinx

ISE 4.x/5.x

•

Xilinx

ISE 6.x (incl. Web Edition)

•

Xilinx

Web Pack 3.3/4.x/5.x

All trademarks and registered trademarks are property of their respective owners.

If using a vendor-specific edition of Active-HDL, only those tools that support the specific silicon

will be supported in the Design Flow Manager.

Note: If you are seeking an alternate vendor flow or an updated version, check the Aldec

website at www.aldec.com or contact support@aldec.com for availability.

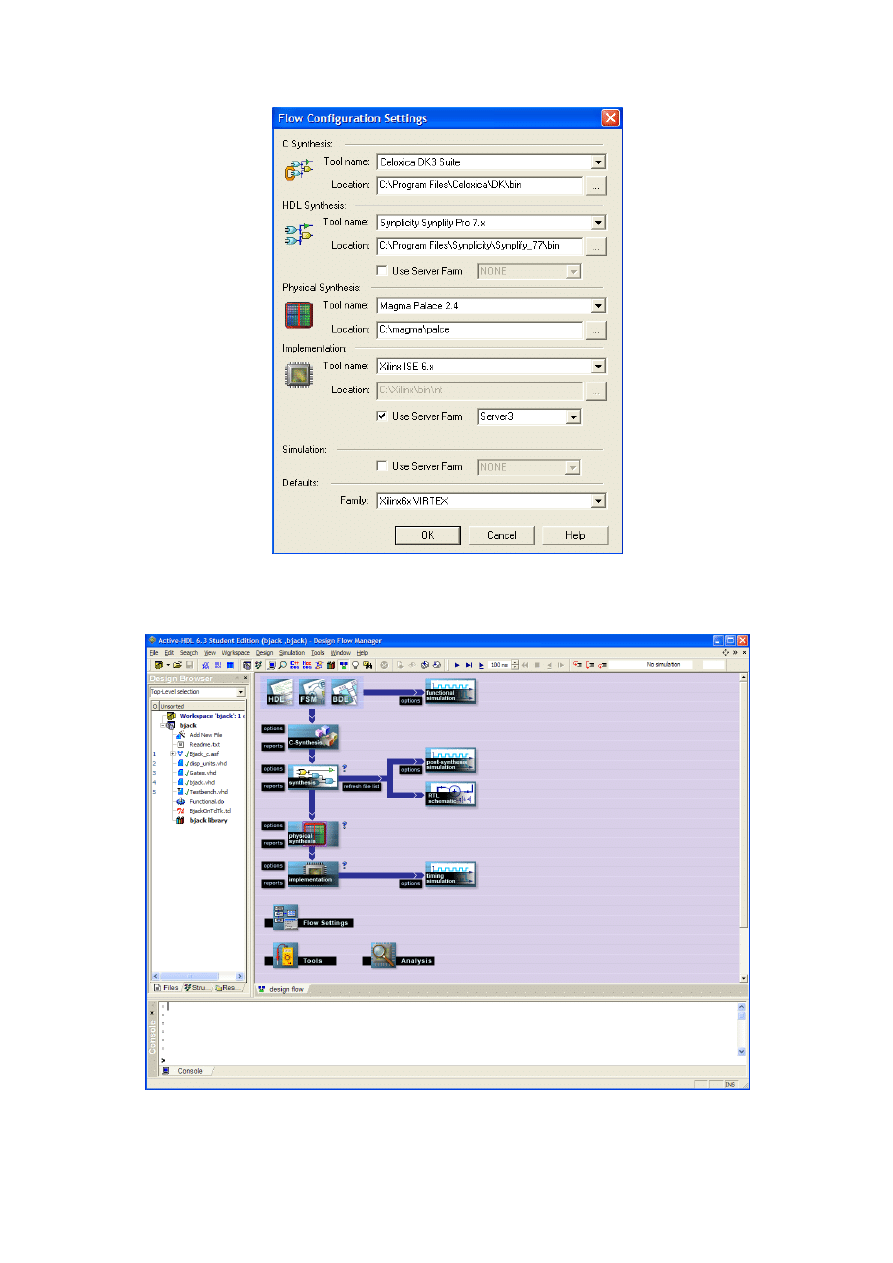

Setting the Design Flow Manager

The Design Flow Manager supports all industry-leading synthesis and implementation tools. The

Design Flow Manager is fully configurable and can be adjusted to all FPGA vendor-supplied

synthesis and implementation tools so that users can freely switch between Actel, Altera,

Cypress, Xilinx, Lattice, Quicklogic and other vendor tools.

Once The Flow Settings feature is invoked, users can specify the synthesis and implementation

tool that they will be using for this design. With the Tcl based flows, designers can customize the

flows and add additional tools that may be required during the verification process. This adds

flexibility to the design process and allows the instant addition of user-approved tools.

18

The Design Flow Manager will now invoke the specified tools and complete automation of the

FPGA design flow is now available.

19

Specifics on the Design Flow Manager

The Design Flow Manager simplifies the network configuration process for IT departments

because the end user's machine can be customized to support only those licenses and systems

that are available to that specific PC. This licensing customization feature prevents restricted

licenses of synthesis and implementation tools to be mistakenly called upon during the design

process.

The flow was made to provide maximum flexibility for the entire design process. It enables

designers to disable certain parts of the design flow so that they can concentrate on the specific

areas of the design cycle that they are currently working on. The flow also permits designers to

edit the list of tools supported so that only those that a designer uses most frequently will be

invoked.

Project Control

When synthesis and implementation are run in batch mode, the FPGA

Design Flow Manager back-annotates the results directly into the Active-HDL environment so

that system designers do not have to manually transfer the results. This allows tracking the

design progress from one centralized location. Since all files are managed through a single

project manager, the users are able to quickly run gate level and timing simulations with the

same stimuli files.

INSTALLATION – MODIFICATION OF PREVIOUS INSTALLS

With Active-HDL already installed in your computer you cannot add previously omitted

components at any time. To do this you need to run the installation software again.

Note: User projects are not removed during uninstall and will be visible in the new version of

Active-HDL.

EXPORT/IMPORT OF ACTIVE-HDL PREFERENCES

Active-HDL enables you to export the current preferences to an external file. The preferences

stored in such a file may be applied to any copy of Active-HDL that supports the import feature.

The export function as well as the import function of preferences is realized by the Active-HDL

Preferences Manager. To invoke this tool, execute the prefman.exe file located in the \Bin sub-

directory of Active-HDL installation folder. The tool may run in two modes: the command line

mode or the GUI mode.

NOTES:

•

The Active-HDL Preferences Manager cannot be used as long as any copy of Active-

HDL is running. If the tool detects a copy of Active-HDL running, it displays the error

message and shuts itself down.

•

The following settings are treated as user-specific and do not take a part in the

export/import process:

o

User name, e-mail address, company name (Tools | Preferences | Environment)

20

o

My Designs folder (Tools | Preferences | Environment)

o

Recent files/workspaces settings

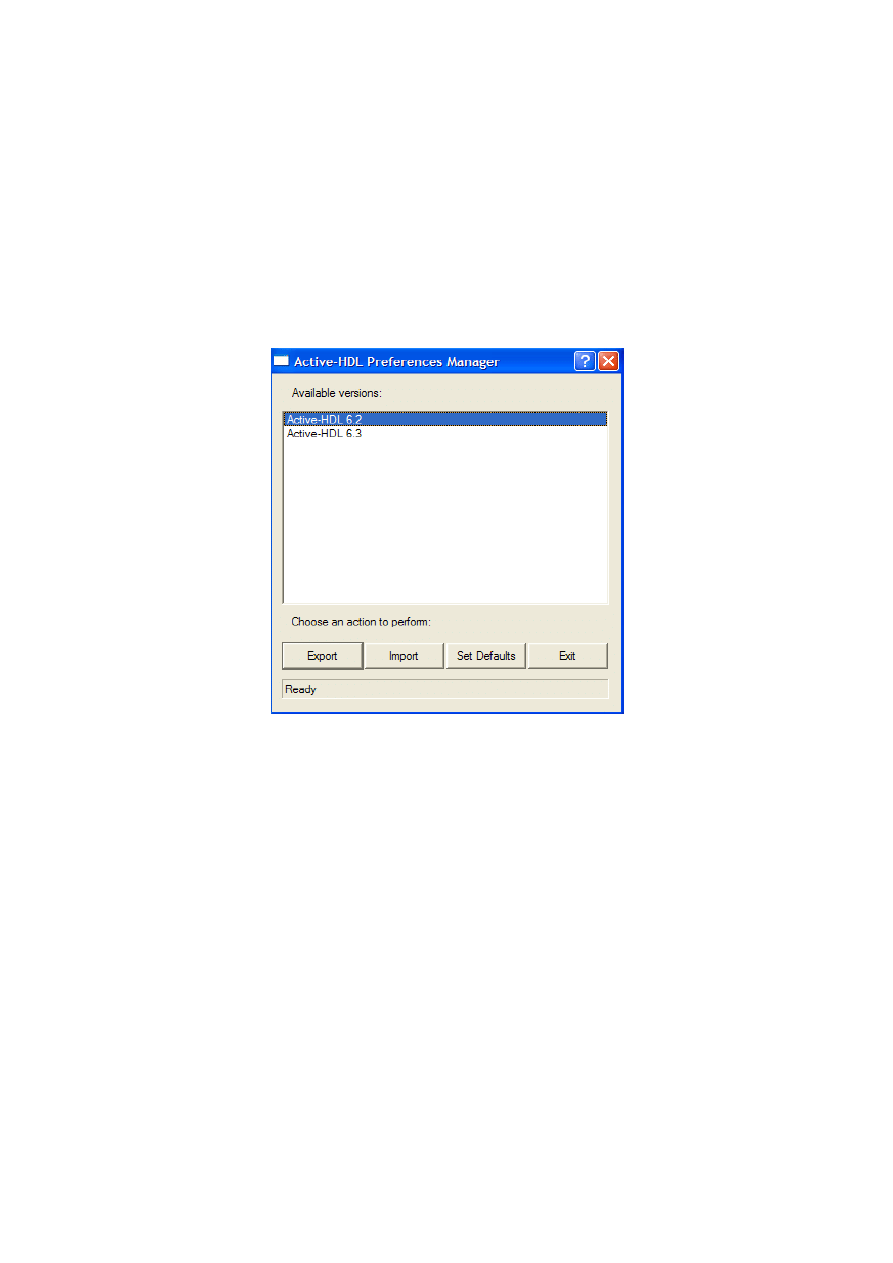

GUI mode

To run the Active-HDL Preferences Manager in the GUI mode, execute the prefman.exe

program without any additional switches (only the –v switch is allowed). As a result, the Active-

HDL Preferences Manager dialog box will start. The Active-HDL Preferences Manager running

in the GUI mode allows you to perform all the operations that are available in the command line

mode.

ACTIVE-HDL PREFERENCES MANAGER OPTIONS

Available versions

Lists Active-HDL installations available on the current computer.

Export

Starts the export of the preferences from the Active-HDL installation (specified in the Available

versions list box) by invoking the Save Active-HDL preferences dialog box. This dialog box

allows you to specify the Active-HDL preferences dump file (*.dmp) that will be used to store the

preferences.

Import

Starts the import of the preferences to the Active-HDL installation (specified in the Available

versions list box) by invoking the Apply Active-HDL preferences dialog box. This dialog box

let you specify the Active-HDL preferences dump file from which the preferences will be

imported to the specified Active-HDL installation.

Set Defaults

Restores the default settings of the Active-HDL installation specified in the

Available versions list box.

21

Exit

Closes the Active-HDL Preferences Manager.

CONTACTING SUPPORT

If you have any problems with the software or questions on the functionality, please check the

on-line help before contacting Aldec support. Many of the common questions and problems are

addressed within this structure.

If you still require assistance, you may contact the Aldec Support Team at:

Aldec Support

2260 Corporate Circle

Henderson, NV 89074

Tel: 702-990-4400

Fax: 702-990-4414

Email:

support@aldec.com

Wyszukiwarka

Podobne podstrony:

iR Shell 3 9 User Guide

FX2N 422 BD User's Guide JY992D66101

NoteWorthy Composer 2 1 User Guide

BlackBerry 8820 User Guide Manual (EN)

intel fortran user guide 2

06 User Guide for Artlantis Studio and Artlantis Render Export Add ons

Flash Lite User Guide Q6J2VKS3J Nieznany

ACCU Check compact user guide products

Proc SQL User's Guide

01 vpuml user guide

01 bpva user guide

arduino mini user guide id 6826 Nieznany (2)

cinestyle profile user guide v1 Nieznany

ANSYS LS Dyna User's Guide

AE CS3 USER GUIDE EPIC TRAILER TEMPLATE

PayPal Virtual Terminal User’s Guide

iR Shell 3 8 User Guide

CPLD I O user guide

więcej podobnych podstron