21

E

LEKTRONIKA DLA WSZYSTKICH 4/99

ELEKTOR w EdW

ELEKTOR w EdW

ELEKTOR w EdW

ELEKTOR w EdW

ELEKTOR w EdW

ELEKTOR w EdW

ELEKTOR w EdW

ELEKTOR w EdW

ELEKTOR w EdW

E

Elle

ek

kt

to

or

r w

w E

Ed

dW

W

Wskaźnik ładowania baterii z zasilacza sieciowego

C

hoćbyś był dum−

nym posiadaczem

najnowszej, auto−

matycznej ładowarki akumulato−

rów NiCd, ciągle możesz mieć

kłopot z nietypową “niekompa−

tybilną” baterią, na przykład

o rzadko spotykanym napięciu

lub wymagającą dużo większe−

go prądu ładowania niż ten, ja−

kiego może dostarczyć twoja ła−

dowarka ze sklepowej półki.

W takich przypadkach uwaga

wielu osób zwraca się w stronę

regulowanych zasilaczy siecio−

wych (o prądzie, powiedzmy,

500mA), ponieważ jest to praw−

dopodobnie najtańszy sposób

zapewnienia napięcia i prądu

stałego wymaganego do łado−

wania baterii. Taki “przyzagro−

dowy” system ładowania, choć

szybki i niezbyt wydajny, jednak

działa. Trzeba jednak pamiętać,

że podlega następującym ogra−

niczeniom:

1. Powinieneś mieć jasny

pogląd odnośnie wartości prądu

ładowania. W przypadku stoso−

wania zasilacza regulowanego,

ale niestabilizowanego, możesz

regulować prąd regulując sko−

kowo napięcie wyjściowe.

2. Musisz wiedzieć, czy prąd

rzeczywiście płynie przez bate−

rię. Tym samym wskaźnik prze−

pływu prądu jest o wiele bar−

dziej przydatny, niż wskaźnik na−

pięcia.

3. Aby zabezpieczyć cię

przed zapomnieniem o cyklu ła−

dowania, wskaźnik powinien

być widoczny tam, gdzie często

przebywasz.

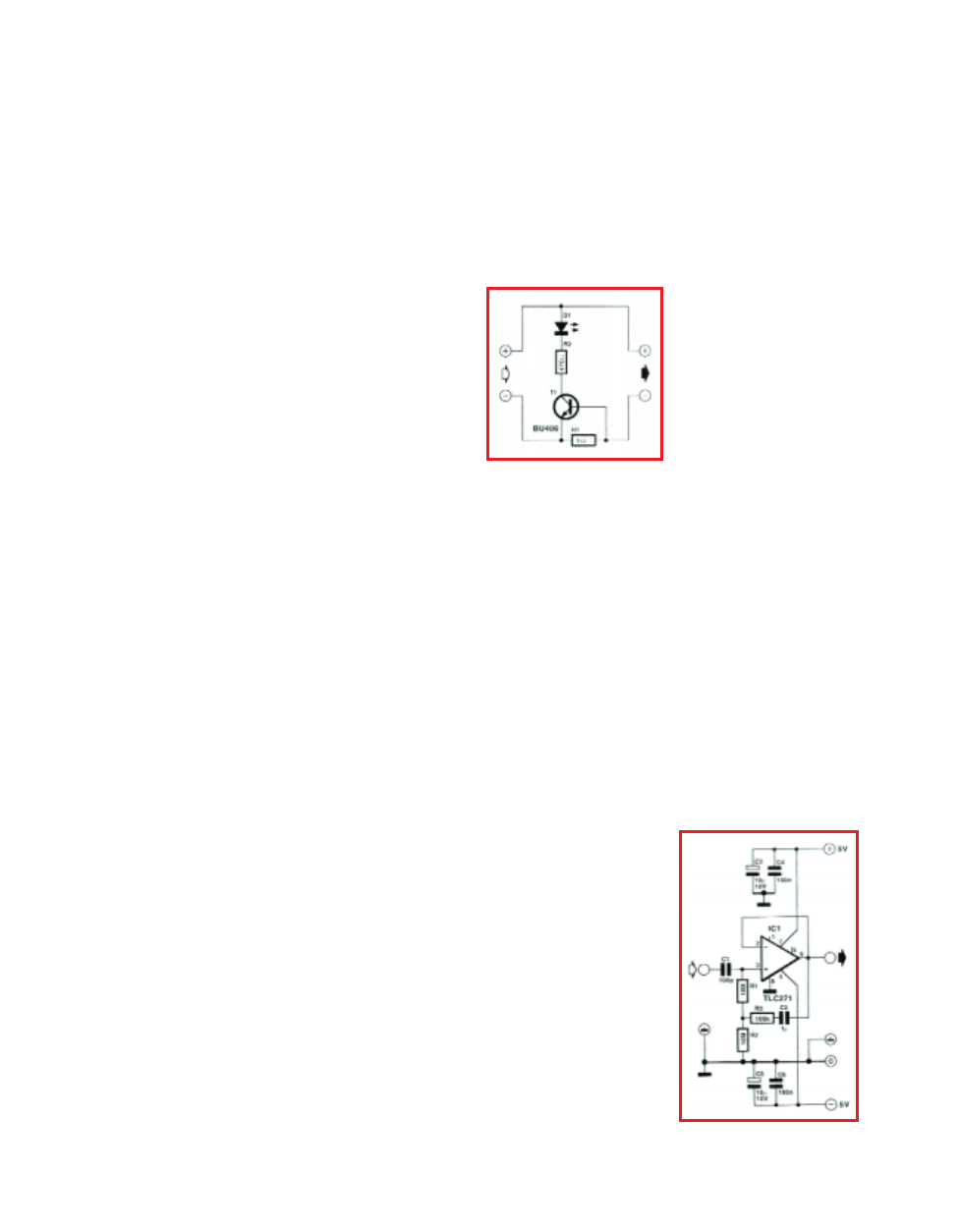

W przedstawionym tu ukła−

dzie dioda LED świeci, gdy na−

pięcie baza−emiter tranzystora

przekracza około 0,2V. Przy uży−

ciu rezystora szeregowego

o wartości 1

Ω

, jak na schema−

cie, zaświeci się przy prądzie

około 200mA, a przy około

40mA, jeśli R1 zostanie zastą−

piony przez rezystor 4,7

Ω

.

Ubytek napięcia spowodo−

wany przez ten wskaźnik nie

może nigdy przekroczyć napię−

cia baza−emiter (U

BE

) tranzysto−

ra, czyli około 0,7V. Nawet jeśli

prąd płynący przez R1 jeszcze

wzrośnie ponad poziom, przy

którym U

BE

= 0,7V, baza tranzy−

stora “wchłonie” nadmiar prą−

du. Proponowany tutaj tranzy−

stor BU406 w obudowie TO−

220 może pracować z prądem

bazy do 4A (można wykorzystać

jakikolwiek inny tranzystor dużej

mocy − przyp. red. EdW).

Przy pomocy takiego wska−

źnika ładowania możesz prze−

zwyciężyć wymienione powyżej

ograniczenia 2 i 3.

Pozostaje problem znajomo−

ści wymaganego prądu. Jak dłu−

go U

BE

pozostaje poniżej mniej

więcej 0,6V, napięcie na R1 jest

wiarygodnym wskaźnikiem prą−

du ładowania. Zamiennie mo−

żesz włączyć amperomierz, by

określić prąd ładowania przy

różnych ustawieniach napięcia

wyjściowego zasilacza. Następ−

nie powinieneś wybrać pomię−

dzy rozsądnie szybkim ładowa−

niem, powiedzmy, przez 6−7 go−

dzin prądem C/5 lub wolniej−

szym, np. przez 14 godzin prą−

dem C/10. C jest pojemnością

baterii w (mili−)amperogodzi−

nach, zazwyczaj nadrukowaną

na baterii. Ogólnie, im mniejszy

prąd ładowania, tym mniejsze

ryzyko uszkodzenia baterii, jeśli

zapomnisz wyłączyć ładowarkę.

W pewnych przypadkach bę−

dzie możliwe wbudowanie ukła−

du do zasilacza sieciowego.

Może to być jednak niebez−

pieczne z powodu obecności

napięcia sieciowego wewnątrz

obudowy zasilacza. Innym roz−

wiązaniem jest umieszczenie

układu w obudowie pilota zdal−

nego sterowania.

Układ nie jest zabezpieczony

przed odwrotną polaryzacją ba−

terii. Jeśli takie zabezpieczenie

jest niezbędne, należy wprowa−

dzić bezpiecznik bądź inny prze−

rywacz obwodu.

P

Prro

ojje

ek

ktt:: J

J.. G

Go

on

nzza

alle

ezz

R

Ry

ys

s.. 1

1..

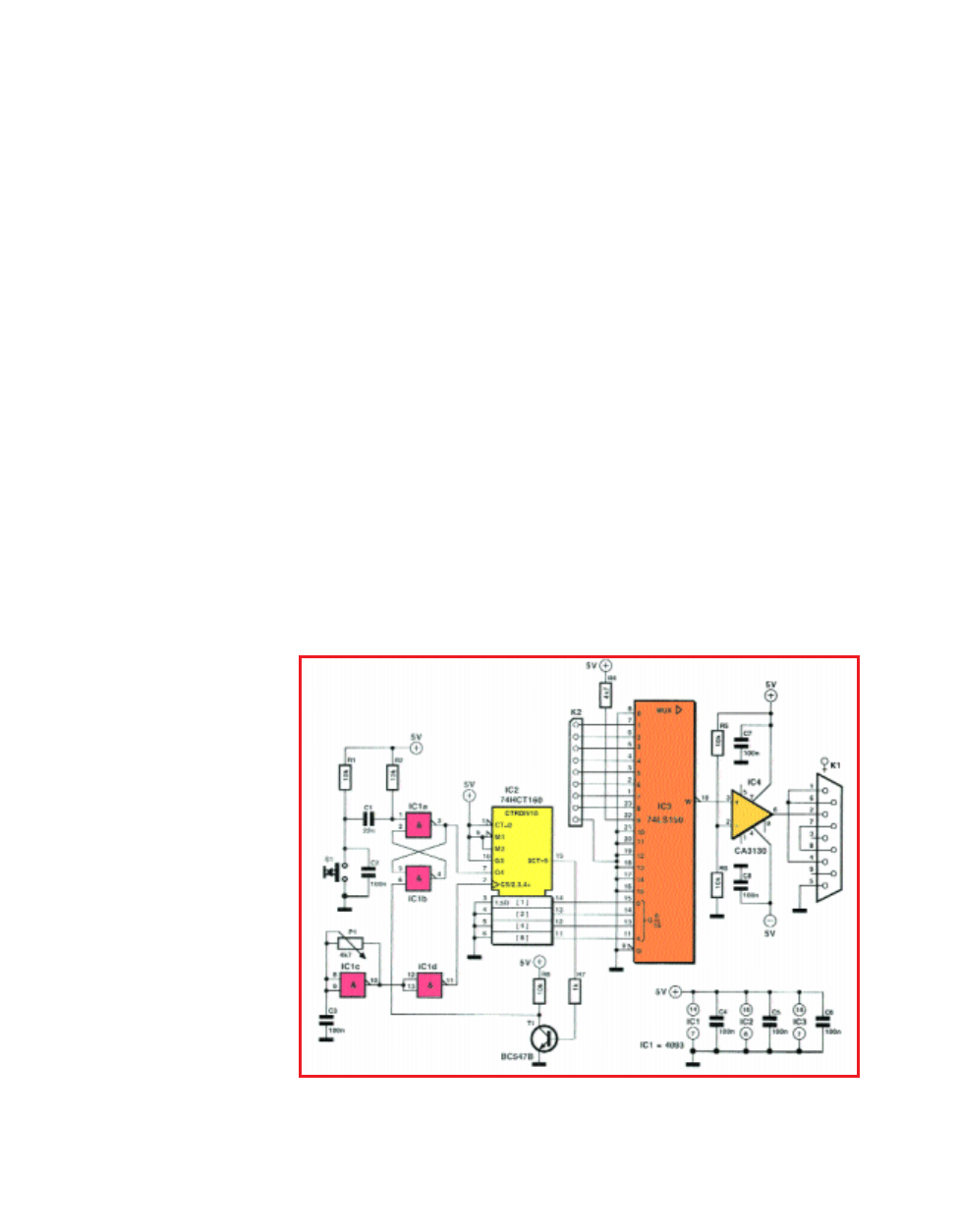

Powielacz impedancji wejściowej

I

mpedancja

wejściowa

układów

wzmacniacza

operacyjnego ze sprzęże−

niem dla prądów zmiennych nie−

mal całkowicie zależy od rezy−

stancji ustalającej stałoprądowy

punkt pracy. Jeśli stosowany

jest wzmacniacz CMOS lub FET,

impedancja wejściowa samego

układu scalonego jest bardzo

wysoka. Natomiast wypadkowa

rezystancja wejściowa układu

zależy właśnie od wartości opor−

ników zastosowanych w obwo−

dach wejściowych (lub obwo−

dach sprzężenia zwrotnego).

Ostatecznie oporność wejścio−

wa układu zbudowanego przy

użyciu współczesnego wzmac−

niacza operacyjnego może się−

gnąć 10M

Ω

. Jeśli potrzebna jest

jeszcze większa wartość, można

skorzystać z

układu “boot−

strap”, umożliwiającego pod−

wyższenie impedancji wejścio−

wej do bardzo wysokich warto−

ści. Na schemacie rezystory R1

plus R2 tworzą obwód określają−

cy stałoprądowy punkt pracy

układu wzmacniacza operacyj−

nego IC1. Bez dalszych działań,

impedancja wyjściowa wynio−

słaby około 20M

Ω

. Jednak sy−

gnał wyjściowy jest podany

zwrotnie (w fazie) na obwód

wejściowy tak, że prąd zmienny

płynący przez R1 jest radykalnie

mniejszy. Impedancja wejścio−

wa Zin dla przebiegów zmien−

nych wyniesie:

Zin =[(R2+R3)/R3](R1+R2)]

Przy wartościach elementów,

jak na schemacie, Zin ma war−

tość około 1G

Ω

.

Układ pobiera prąd około 3mA.

P

Prro

ojje

ek

ktt:: H

H.. B

Bo

on

ne

ek

ka

am

mp

p

O

Od

d R

Re

ed

d.. E

Ed

dW

W::

Układ tego typu może być

zrealizowany z użyciem dowol−

nego wzmacniacza operacyjne−

go o małym (stałym) prądzie

polaryzacji wejść np.: TL071

TL081.

R

Ry

ys

s.. 1

1..

Prezentowany układ nie

jest najnowocześniejszym su−

perszybkim przetwornikiem.

Jeśli szukasz jakiegoś rozwią−

zania superszybkiego i wyrafi−

nowanego, z czystym sumie−

niem pomiń ten artykuł. Jeśli

jednak czasem potrzebujesz

przetworzyć równoległe infor−

macje 8−bitowe na szeregowe

i przesłać je z prędkością nie

większą niż 9600 bodów, nie

przegap tego prostego układu.

Jeśli poszukujesz prostego

i niezbyt wyrafinowanego roz−

wiązania, właśnie ten układ

może się okazać najbardziej

odpowiednim blokiem.

Niniejszy artykuł pokazuje,

jak zatrudnić kilka najzwyklej−

szych układów scalonych TTL

do przetwarzania danych rów−

noległych na format szerego−

wy. Format transmisji jest

standardowy: 8 bitów danych,

jeden bit stopu i brak bitu pa−

rzystości − w praktyce usta−

wienie takie będzie odpowie−

dnie dla wszystkich, no może

z wyjątkiem najbardziej egzo−

tycznych przypadków.

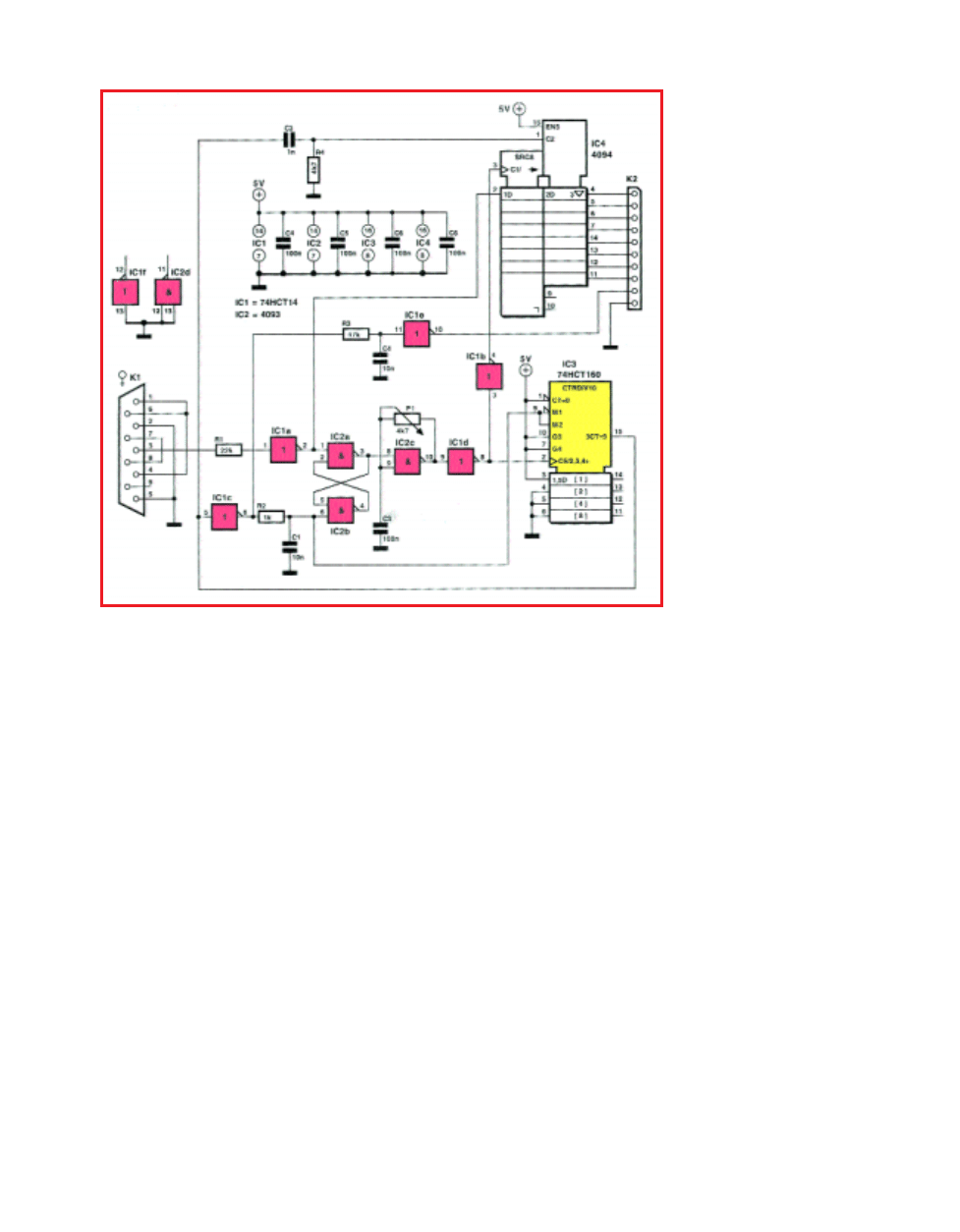

Schemat elektryczny prze−

twornika równoległo−szerego−

wego można znaleźć na rry

y−

s

su

un

nk

ku

u 1

1. Sercem układu jest

układ scalony IC3, typu

74LS150. Jest on odpowie−

dzialny za właściwe przetwa−

rzanie równoległo−szeregowe.

Osiem z szesnastu wejść te−

go multipleksera jest połączo−

nych wejściem równoległym,

czyli złączem K2. Wejście 0

(nóżka 8) układu scalonego

IC3 reprezentuje bit startu,

a wejścia 1 do 8 (nóżki 1...7

i 23) − bity danych. Na koniec,

wejście (nóżka 22) służy do

generowania bitu stopu. Wej−

ścia multipleksera 74LS150 są

kolejno uaktywniane za pośre−

dnictwem licznika BCD IC2 ty−

pu 74LS160 (74HC160). Każ−

de wciśnięcie przycisku S1

powoduje, że licznik 74LS160

liczy w górę od 0 do 9 i w ten

sposób dostarcza odpowie−

dnich kodów BCD do wejść

A − D (nóżki 11, 13...15) multi−

pleksera IC3. W wyniku dzia−

łania kondensatora C2, to sa−

mo dzieje się po włączeniu za−

silania. W rezultacie jeden bajt

zostaje przetworzony i prze−

słany.

Jeśli układ jest wykorzysty−

wany jako podzespół większe−

go urządzenia, elementy R1,

R2, C1 i S2 można pominąć,

natomiast wejście IC1a połą−

czyć z odpowiednim układem

sterującym.

E

Elle

ek

kt

to

or

r w

w E

Ed

dW

W

E

LEKTRONIKA DLA WSZYSTKICH 4/99

22

Przetwornik równolegle/szeregowo

Z ośmiu na jeden i na odwrót

K

K

a

ażżd

dy

y k

ko

om

mp

pu

utte

err m

ma

a p

prrzzy

yn

na

ajjm

mn

niie

ejj ttrrzzy

y p

po

orrtty

y::

d

dw

wa

a s

szze

erre

eg

go

ow

we

e ((o

ozzn

na

ac

czza

an

ne

e c

czzę

ęs

stto

o R

RS

S−

2

23

32

2)) ii jje

ed

de

en

n rró

ów

wn

no

olle

eg

głły

y.. Ł

Łą

ąc

czze

e s

szze

erre

eg

go

ow

we

e

R

RS

S−2

23

32

2 jje

es

stt c

ciią

ąg

glle

e b

ba

arrd

dzzo

o p

po

op

pu

ulla

arrn

ne

e ii c

ch

hę

ęttn

niie

e w

wy

y−

k

ko

orrzzy

ys

stty

yw

wa

an

ne

e.. W

W w

wiie

ellu

u w

wy

yp

pa

ad

dk

ka

ac

ch

h zza

ac

ch

ho

od

dzzii k

ko

o−

n

niie

ec

czzn

no

oś

ść

ć s

sk

ko

orrzzy

ys

stta

an

niia

a zz p

po

orrttu

u s

szze

erre

eg

go

ow

we

eg

go

o k

ko

om

m−

p

pu

utte

erra

a.. D

Da

an

ne

e zz a

allb

bo

o d

do

o k

ko

om

mp

pu

utte

erra

a m

mo

og

gą

ą b

by

yć

ć p

prrzze

e−

s

słła

an

ne

e n

na

aw

we

ett k

kiillk

ka

an

na

aś

śc

ciie

e m

me

ettrró

ów

w p

prrzze

ezz jja

ak

ką

ąk

ko

ollw

wiie

ek

k

d

dw

wu

użży

yłło

ow

wą

ą lliin

niię

ę.. Z

Za

arró

ów

wn

no

o w

w k

ko

om

mp

pu

utte

erra

ac

ch

h,, jja

ak

k

ii w

w p

prro

offe

es

sjjo

on

na

alln

ny

yc

ch

h u

urrzzą

ąd

dzze

en

niia

ac

ch

h zz n

niim

mii w

ws

sp

pó

ółłp

prra

a−

c

cu

ujją

ąc

cy

yc

ch

h b

ba

arrd

dzzo

o c

czzę

ęs

stto

o ttrrzze

eb

ba

a zza

am

miie

en

niia

ać

ć iin

nffo

orrm

ma

a−

c

cjję

ę rró

ów

wn

no

olle

eg

głłą

ą n

na

a s

szze

erre

eg

go

ow

wą

ą.. N

Na

ajjc

czzę

ęś

śc

ciie

ejj s

są

ą d

do

o tte

e−

g

go

o w

wy

yk

ko

orrzzy

ys

stty

yw

wa

an

ne

e a

allb

bo

o m

miik

krro

op

prro

oc

ce

es

so

orry

y,, a

allb

bo

o s

sp

pe

e−

c

cjja

alliizzo

ow

wa

an

ne

e u

uk

kłła

ad

dy

y s

sc

ca

allo

on

ne

e,, o

ob

be

ec

cn

niie

e c

co

orra

azz c

czzę

ęś

śc

ciie

ejj

d

do

os

sttę

ęp

pn

ne

e jja

ak

ko

o e

elle

em

me

en

ntty

y S

SM

MD

D.. P

Prrzze

ec

ciię

ęttn

ny

y h

ho

ob

bb

by

ys

stta

a

m

ma

a c

co

orra

azz m

mn

niie

ejj s

szza

an

ns

s,, b

by

y jje

e w

w p

prro

os

stty

y s

sp

po

os

só

ób

b w

wy

yk

ko

o−

rrzzy

ys

stta

ać

ć..

T

Ty

ym

mc

czza

as

se

em

m tta

ak

kżże

e h

ho

ob

bb

by

yś

śc

cii c

ch

hc

ciie

elliib

by

y w

wy

yk

ko

orrzzy

ys

stty

y−

w

wa

ać

ć p

po

orrtt s

szze

erre

eg

go

ow

wy

y k

ko

om

mp

pu

utte

erra

a zza

arró

ów

wn

no

o d

do

o zzb

biie

erra

a−

n

niia

a d

da

an

ny

yc

ch

h ((p

prrzze

es

sy

yłła

an

niie

e iin

nffo

orrm

ma

ac

cjjii d

do

o k

ko

om

mp

pu

utte

erra

a)),,

jja

ak

k ii d

do

o s

stte

erro

ow

wa

an

niia

a ((p

prrzze

es

sy

yłła

an

niie

e d

da

an

ny

yc

ch

h zz k

ko

om

mp

pu

utte

e−

rra

a d

do

o u

urrzzą

ąd

dzze

en

niia

a w

ws

sp

pó

ółłp

prra

ac

cu

ujja

ac

ce

eg

go

o)).. P

Prra

ak

ktty

yk

ka

a d

do

o−

w

wo

od

dzzii,, żże

e n

na

ajjw

wiię

ęc

ce

ejj k

kłło

op

po

ottó

ów

w s

sp

prra

aw

wiia

a b

bu

ud

do

ow

wa

a b

bllo

ok

ku

u..

R

Ro

ozzw

wiią

ązza

an

niie

e p

prrzze

ed

ds

stta

aw

wiio

on

ne

e w

w tty

ym

m a

arrtty

yk

ku

ulle

e d

do

ow

wo

o−

d

dzzii,, żże

e d

do

ob

brrą

ą a

alltte

errn

na

atty

yw

wą

ą m

mo

ożże

e b

by

yć

ć o

op

pa

arrc

ciie

e s

siię

ę n

na

a

g

ga

arrś

śc

cii p

po

oc

czzc

ciiw

wy

yc

ch

h e

elle

em

me

en

nttó

ów

w d

dy

ys

sk

krre

ettn

ny

yc

ch

h.. P

Prro

oc

ce

es

s

o

od

dw

wrro

ottn

ny

y,, zza

am

miia

an

na

a ffo

orrm

ma

attu

u s

szze

erre

eg

go

ow

we

eg

go

o n

na

a rró

ów

w−

n

no

olle

eg

głły

y,, jje

es

stt rró

ów

wn

niie

e p

prro

os

stty

y..

R

Ry

ys

s.. 1

1..S

Sc

ch

he

em

ma

att e

elle

ek

kttrry

yc

czzn

ny

y p

prrzze

ettw

wo

orrn

niik

ka

a rró

ów

wn

no

olle

eg

głło

o−s

szze

erre

eg

go

ow

we

eg

go

o.. Z

Za

a p

po

oś

śrre

ed

dn

niic

cttw

we

em

m tty

yllk

ko

o

c

czztte

erre

ec

ch

h p

prro

os

stty

yc

ch

h u

uk

kłła

ad

dó

ów

w s

sc

ca

allo

on

ny

yc

ch

h T

TT

TL

L,, d

da

an

ne

e rró

ów

wn

no

olle

eg

głłe

e zzo

os

stta

ajją

ą zza

am

miie

en

niio

on

ne

e n

na

a ffo

orrm

ma

att s

szze

e−

rre

eg

go

ow

wy

y o

o s

szzy

yb

bk

ko

oś

śc

cii ttrra

an

ns

sm

miis

sjjii d

do

o 9

96

60

00

0 b

biittó

ów

w n

na

a s

se

ek

ku

un

nd

dę

ę..

Działanie reszty układu po−

winno być zrozumiałe, ponie−

waż zastosowano naprawdę

prosty układ licznika. Przerzut−

nik

zbudowany

wokół

IC1a i IC1b może być ustawia−

ny za pośrednictwem S1 i re−

setowany przez licznik BCD za

pośrednictwem tranzystora

T1 na końcu transmisji kodu

szeregowego. Gdy przerzut−

nik jest ustawiony, licznik zli−

cza i każdy kolejny impuls ze−

garowy powoduje umieszcze−

nie następnego bitu na linii

wyjścia szeregowego. Prosty

generator RC sygnału zegaro−

wego jest zbudowany z bufo−

rami IC1c i IC1d. Został on do−

brany tak, że osiągnięto szyb−

kość transmisji 9600 bitów na

sekundę. Dokładną szybkość

ustawia się za pośrednictwem

potencjometru montażowego

P1. Przy mniejszych szybko−

ściach transmisji należy odpo−

wiednio zwiększyć kondensa−

tor C3. Na przykład, dla pręd−

kości 2400 dobrym wyborem

jest kondensator 1µF (stały,

foliowy). W ten sposób układ

może być dopasowany do nie−

mal każdej szybkości transmi−

sji, jaką zechcesz zastosować

− wszystko co musisz zrobić,

to modyfikacja oscylatora od−

powiednio do potrzeb.

RS232, krok po kroku

Zrozumiałeś, że informacje

szeregowe pojawiają się na

wyjściu W multipleksera (nóż−

ka 10). Jedynym pominiętym

dotychczas elementem jest

interfejs dopasowujący do li−

nii. Do tego celu wezwaliśmy

na pomoc zasilany symetrycz−

nie wzmacniacz operacyjny

CA3130. Wzmacniacz ten,

skonfigurowany jako kompa−

rator, zamienia sygnały o po−

ziomach TTL odbierane z mul−

tipleksera na szeregowe sy−

gnały o poziomach +5V oraz

−5V. W ten sposób staraliśmy

się spełnić wymagania elek−

tryczne określone dla interfej−

su RS232. W tym prostym

rozwiązaniu wykorzystywana

jest tylko jedna linia interfejsu

szeregowego: TxD (nadawa−

nych danych). Na złączu K1

zostały połączone ze sobą li−

nie uzgodnienia RTS (Request

To Send − żądania nadawania)

z CTS (Clear To Send − goto−

wości do nadawania), podob−

nie jak trójka DSR (Data Set

Ready − gotowości zestawu

danych), DCD (Data Carrier

Detected − wykrycia nośnej

danych) i DTR (Data Terminal

Ready − gotowości terminala

danych). W ten typowy spo−

sób port RS232 jest “uaktyw−

niony” i gotowy do komunika−

cji szeregowej. Choć w zasa−

dzie zgodnie ze standardem

poziomy napięć na linii powin−

ny być wyższe, jednak w prak−

tyce prosty zasilacz o napię−

ciach wyjściowych +5V

i

−5V jest wystarczający dla te−

go projektu.

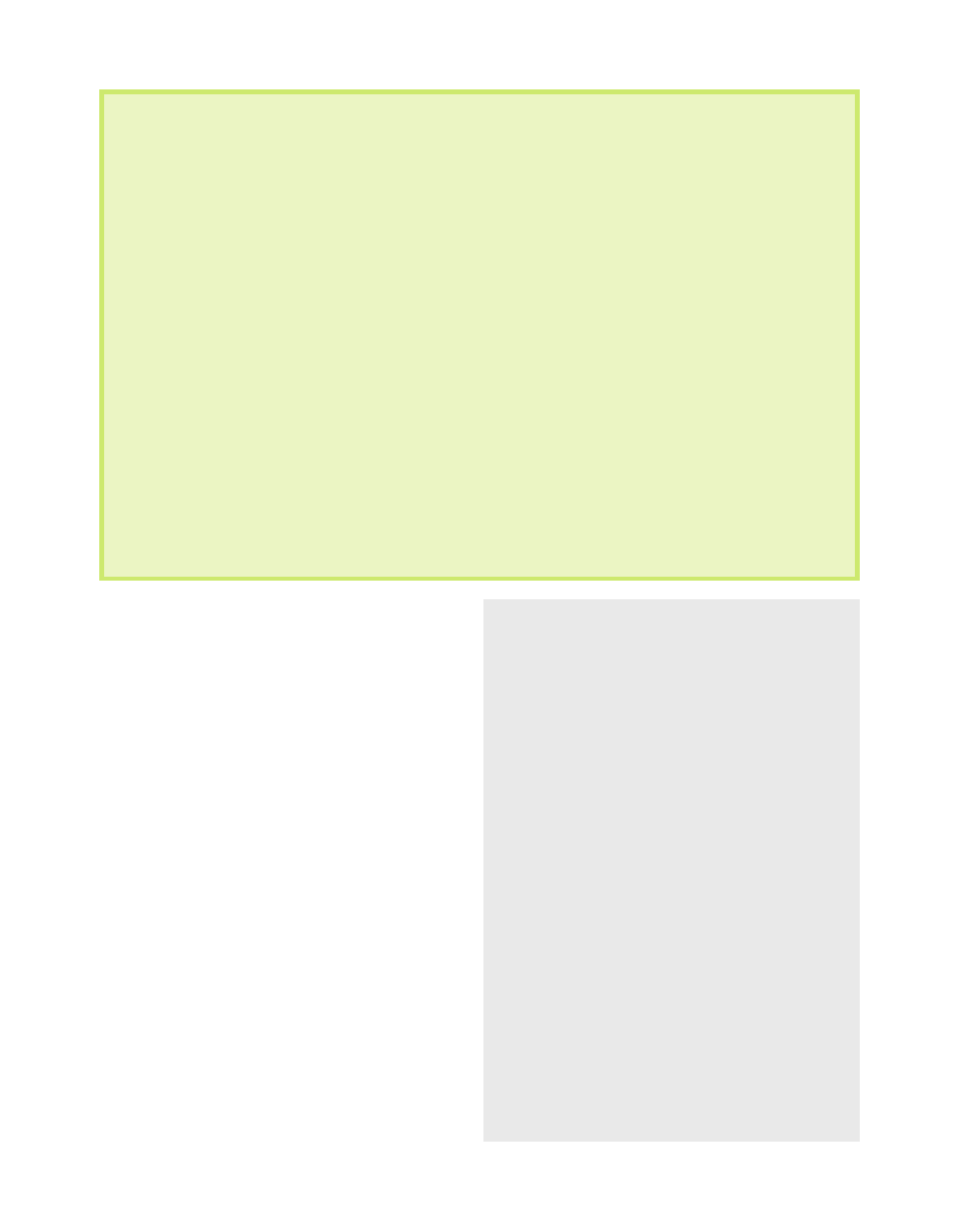

W drugą stronę

Do tej pory omawialiśmy

jedynie przetwarzanie z for−

matu równoległego do szere−

gowego. Proces odwrotny, od

formatu szeregowego do rów−

noległego również dokonuje

się w bardzo prosty sposób.

Odpowiedni układ przed−

stawia rry

ys

su

un

ne

ek

k 2

2. Złącze K1

odbiera dane szeregowe, na

przykład z portu szeregowego

komputera PC. Również i tu

niektóre piny złącza są ze so−

bą zwarte, co zresztą w tym

wypadku nie ma znaczenia.

Sygnał

szeregowy

(TxD)

z nóżki 3 złącza K1 przez rezy−

stor ochronny R1 i inwerter

IC1a jest podawany na wej−

ście 1D (nóżka 2) rejestru IC4.

IC2a i IC2b tworzą przerzutnik

RS (Set−Reset) i w połączeniu

z oscylatorem zbudowanym

z

wykorzystaniem IC2d

i

IC2c

oraz licznikiem typu

74HCT160 tworzą razem ser−

ce układu, jeśli chodzi o takto−

wanie.

Gdy dane (o poziomach

+5V i −5V) pojawią się na wej−

ściu szeregowym, zostaną

przetworzone do poziomu TTL

(R1, IC1a), a następnie dopro−

wadzone do wejścia przerzut−

nika bistabilnego RS. Przerzut−

nik ten uruchamia oscylator,

po czym impulsy zegarowe są

przesyłane do wejścia licznika

IC3 i rejestru przesuwnego

IC4. I właśnie ten rejestr prze−

suwa odebrane bity jeden za

drugim na odpowiednie pozy−

cje, skąd na koniec cyklu mo−

gą być odebrane przez złącze

K2.

Gdy oscylator IC2c wytwo−

rzy dziewięć impulsów zega−

rowych, przerzutnik RS jest

ponownie zerowany za pośre−

dnictwem sygnału na wyjściu

3CT=9 układu IC3 (nóżka 15),

po

zanegowaniu

przez

IC1c.Obwód RC złożony z R2

i C1 wydłuża ostatni impuls.

Gdyby to nie zostało zapew−

nione, istniałaby poważna

obawa, że rejestr przesuwny

zgubi ostatni impuls, głównie

dlatego, że IC4 (jako układ

CMOS) jest nie tak szybki, jak

IC3 (układ HCT). Obwód RC,

złożony z C3 i R4, dostarcza

impulsów

strobujących,

umożliwiających wczytanie

danych do rejestru wyjścio−

wego IC4. Sygnał ten pocho−

dzi z tego samego wyjścia

układu IC3. Odebrane dane

pozostaną na wyjściu (złączu

E

Elle

ek

kt

to

or

r w

w E

Ed

dW

W

23

E

LEKTRONIKA DLA WSZYSTKICH 4/99

R

Ry

ys

s.. 2

2.. P

Prrzze

ettw

wa

arrzza

an

niie

e w

w o

od

dw

wrro

ottn

ny

ym

m k

kiie

erru

un

nk

ku

u rró

ów

wn

niie

eżż n

niie

e jje

es

stt p

prro

ob

blle

em

me

em

m.. T

Te

en

n p

prro

os

stty

y u

uk

kłła

ad

d zza

a−

m

miie

en

niia

a iin

nffo

orrm

ma

ac

cjje

e s

szze

erre

eg

go

ow

we

e n

na

a rró

ów

wn

no

olle

eg

głłe

e..

K2) tak długo, aż pojawi się

następny impuls strobujący,

czyli

do

skompletowania

następnego bajtu danych.

Jest

to

możliwe

dzięki

podwójnemu

buforowaniu

w kostce IC4. Urządzenie pe−

ryferyjne, odbierające dane

z portu K2, otrzymuje impuls

informujący

o

odebraniu

i skompletowaniu następnego

bajtu danych za pośrednic−

twem R3, C4 i negatora IC1e.

Wartości elementów ukła−

du (głównie oscylatora) są od−

powiednie dla sygnałów sze−

regowych przesyłanych z czę−

stotliwością 9600 bitów na

sekundę. Poprzez zwiększe−

nie C2 do 470nF można obni−

żyć częstotliwość bitów do

2400. Potencjometr montażo−

wy umożliwia dokładną regu−

lację częstotliwości. Niestety,

regulacja oscylatora zegara

nie jest tak łatwa, jak byśmy

sobie życzyli. Problem polega

na tym, że oscylator jest ak−

tywny tylko wtedy, gdy są

odbierane dane szeregowe.

W celu dostrojenia układu,

można rozwiązać ten “pro−

blem” poprzez wymuszenie

ciągłej pracy oscylatora, na

przykład przez chwilowe połą−

c z e n i e

w y p r o w a d z e n i a

8 IC2c z linią +5V (tj. chwilo−

we przecięcie połączenia po−

między

wyprowadzeniami

3 IC2a i 8 IC2c). Następnie

można zmierzyć częstotli−

wość zegara na wyprowadze−

niu 8 IC1d (2400Hz dla 2400

bitów/s lub 9600Hz dla 9600

bitów/s).

O

Od

d R

Re

ed

da

ak

kc

cjjii E

Ed

dW

W:

Układy rodzin 74LS, 74HC

i 74HCT w opisanych ukła−

dach mogą być stosowane

wymiennie. Wzmacniacz ope−

racyjny

CA3130

można

spróbować zastąpić innym,

nawet popularnym uA741.

Aby zapewnić dostateczną

stabilność częstotliwości, na−

pięcie zasilające 5V powinno

być stabilizowane, a w oscyla−

torach (z bramkami odpowie−

dnio IC1C, IC2c) należy stoso−

wać kondensatory foliowe,

nie ceramiczne, przy czym po−

tencjometry P1 powinny być

typu helitrim.

E

Elle

ek

kt

to

or

r w

w E

Ed

dW

W

E

LEKTRONIKA DLA WSZYSTKICH 4/99

24

Programy

Programy

Port szeregowy RS232 w komputerze PC musi być usta−

wiony (lub “skonfigurowany”) dla zapewnienia, że znajduje

się w odpowiednim trybie (a nie nastroju) do odbioru danych.

W tym celu należy użyć DOS−owej komendy

mode com2:9600,n,8,1

przez co konfigurujemy port COM2 (zakładając, że COM1

obsługuje myszkę).

Aby przetestować przetwornik równoległo−szeregowy,

trzeba dołączyć do portu COM2 komputera układ z rysunku

1.

Następnie do odczytu danych przychodzących do kompu−

tera można zatrudnić prosty program. Poniższy program, na−

pisany w QBASIC−u daje taką mozliwość.

Po podaniu danych równoległych (liczby 8−bitowej) na

układ z rysunku 1 i naciśnięciu przycisku S1, na ekranie kom−

putera powinna się pojawić nowa wartość, odpowiadająca

tej liczbie.

start:

IF INP(&H2FD)>96 THEN PRINT INP(&H2F8)

GOTO start:

Zazwyczaj adresem portu COM2 jest właśnie liczba szes−

nastkowa 2F8, a adres 2FD wskazuje rejestru stanu, który

będzie odczytywany dla sprawdzenia, czy są tam nowe da−

ne. Jeśli wykorzystujesz inny port COM, należy odpowiednio

zmienić adresy.

Przetwornik szeregowo−równoległy jest również łatwy do

testowania. Program zamieszczony poniżej w sposób ciągły

przesyła sekwencje liczb od 0 do 255 do portu równoległego

i dalej do układu z rysunku 2:

FOR X = 0 TO 255

OUT &H2F8,X

FOR Y = 1 TO 1000: NEXT Y

NEXT X

Wiersz

FOR Y = 1 TO 1000: NEXT Y

został wprowadzony dla zmniejszenia częstotliwości wpi−

sywania do bufora portu komputera nowych danych, co jest

wręcz konieczne, gdy korzystasz z szybkiego komputera.

Dzięki temu ustawieniu (i opóźnieniu) możesz nawet zoba−

czyć, że nowa wartość jest przesyłana za każdym powtórze−

niem tej pętli programowej.

Obydwa programy wykorzystują port COM2 o adresie

2F8. Jeśli masz zamiar korzystać z innego portu COM, nale−

ży odpowiednio zmodyfikować adres.

Wyszukiwarka

Podobne podstrony:

2015 08 20 08 31 40 01

2015 08 20 08 14 40 01

2015 08 20 07 52 40 01

2015 08 20 07 53 40 01

2014 03 02 11 53 40 01

2015 08 20 08 14 40 01

2014 03 02 11 53 40 01

Wb 40 01

2015 08 20 07 53 40 01

2015 08 20 08 31 40 01

2015 08 20 07 52 40 01

40 01

40 0610 013 05 01 7 General arrangement

2002 01 40

01 40

Ćw nr 40, 40,,,, Chowaniec Aleksander

2003 01 40

więcej podobnych podstron