Prezentowany układ jest rozwinięciem wcześ-

niejszego projektu Autora pt. Generator sygna-

łowy DDS, opublikowanego w EdW 7, 8/2008.

DDS to całkowicie cyfrowa metoda bez-

pośredniej syntezy przebiegów analogowych

o częstotliwości od DC do kilkuset mega-

herców. Metoda ta zapewnia bardzo wysoką

stabilność generowanej częstotliwości (taką

jak stabilność generatora wzorcowego) oraz

przestrajanie z dokładnością do ułamków Hz.

Scalone układy syntezy DDS są w pełni pro-

gramowalne, zatem częstotliwość, amplituda

oraz faza generowanego sygnału mogą być

dowolnie zmieniane poprzez układy sterujące

np. mikroprocesor.

Układy DDS integrujące w swojej struk-

turze wszystkie bloki niezbędne do generacji

sygnałów stały się alternatywą dla analogowych

syntezerów opartych o pętle synchronizacji fa-

zowej, zapewniając bardzo szybkie przestraja-

nie w bardzo szerokim zakresie częstotliwości,

w pełni cyfrową regulację amplitudy, fazy oraz

częstotliwości generowanego sygnału. Układy te

nie wymagają kalibracji, strojenia oraz są znacz-

nie mniej wrażliwe na zmiany temperatury niż

standardowe analogowe rozwiązania. Wszystkie

syntezy DDS umieszczone są w miniaturowych

obudowach SMD zajmując tym samym mało

miejsca na płytkach drukowanych. Układy te

mogą także pełnić funkcję źródeł sygnałów ze-

garowych. Wiele syntezerów DDS posiada wbu-

dowany wewnętrzny szybki komparator, który

może służyć do generacji sygnału prostokątnego

z sygnału sinusoidalnego.

Obecnie największym producentem ukła-

dów DDS jest fi rma Analog-Devices posia-

dająca w swojej ofercie kil-

kanaście typów syntez DDS

(www.analog.com).

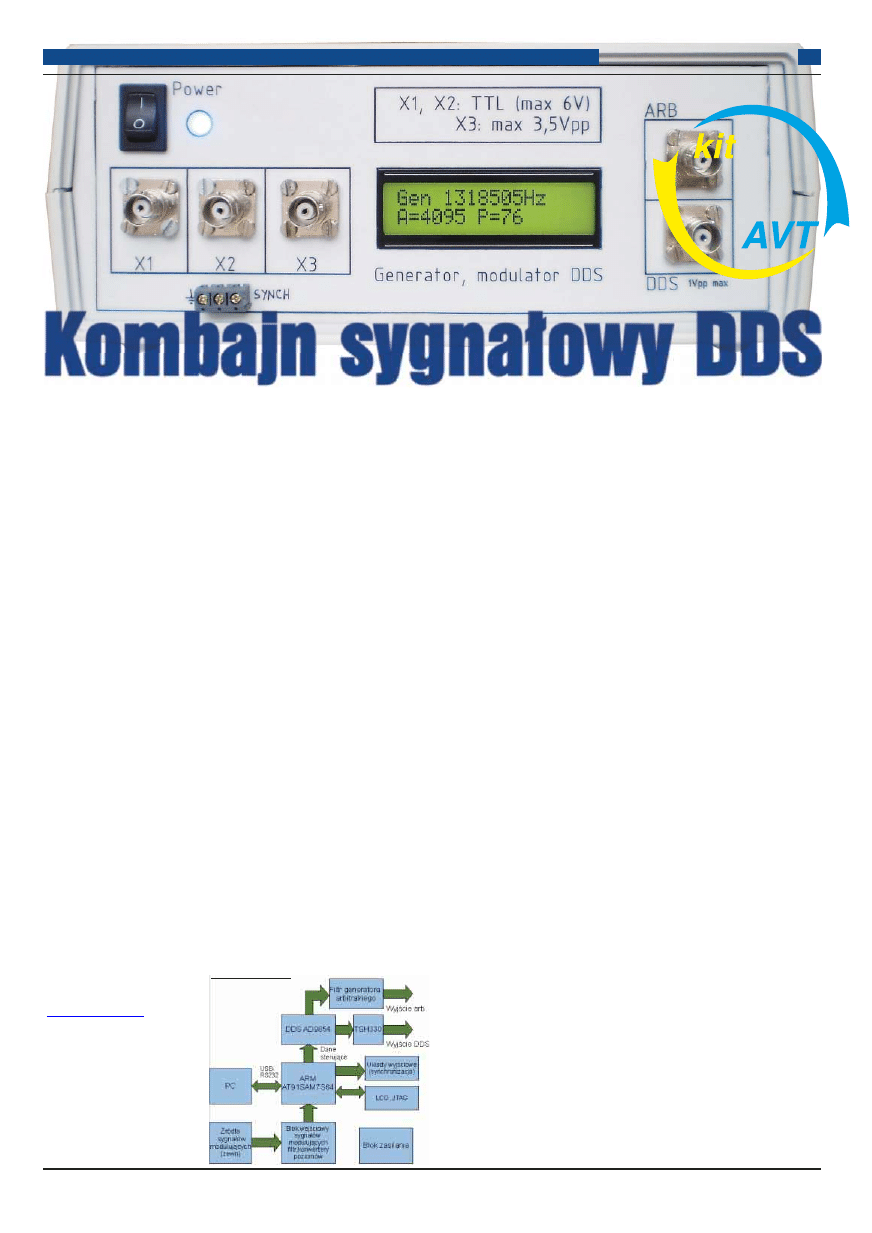

Koncepcję praktycznej re-

alizacji modulatora oraz gene-

ratora przedstawia rysunek 1.

Konstrukcja modułowa

zapewniła łatwiejsze urucha-

mianie modelu. Dodatkowo

błędy bądź uszkodzenie da-

nego bloku funkcjonalnego

nie pociąga za sobą konieczności wymiany

całej elektroniki, a tylko określonego frag-

mentu. Dwa główne bloki urządzenia to układ

syntezy DDS, oparty na układzie AD9854

oraz układ sterowania wykorzystujący proce-

sor ARM AT91SAM7S64.

Układ AD9854 jest układem bezpośred-

niej syntezy cyfrowej DDS zawierającym

wszystkie niezbędne bloki do generacji syg-

nału aproksymującego sinusoidę. Maksy-

malna częstotliwość taktowania układu wy-

nosi 300MHz dla wersji w obudowie TQFP

thermal slug. Obudowa ta wyposażona jest

we wkładkę radiatorową, którą należy przy-

lutować do pola masy na płytce drukowanej.

Druga wersja tego samego układu nie zawie-

ra wkładki radiatorowej, co ogranicza moc

strat układu oraz częstotliwość taktowania do

200MHz. Układ AD9854 ma dwa zintegro-

wane przetworniki DAC o rozdzielczości 12

bitów każdy (kanał I oraz Q w przypadku wy-

korzystania układu jako generatora kwadratu-

rowego). Kanał Q może zostać odłączony od

rdzenia DDS a wartość prądu wyjściowego

tego kanału będzie zależna od zawartości re-

jestru o adresie 0x0B. Umożliwia to generację

innych sygnałów poprzez sekwencyjne wpi-

sywanie do tego rejestru wartości próbek syg-

nału. W modelu zostało to wykorzystane do

generowania sygnałów arbitralnych, których

przebieg jest opisany funkcją matematyczną.

Układ wymaga zasilania napięciem 3,3V o

wydajności prądowej minimum 800mA.

Programowanie może odbywać się w

trybie równoległym oraz szeregowym. Tryb

równoległy umożliwia transfer danych do

syntezy z szybkością

do 100MHz, tryb sze-

regowy maksymalnie

10MHz. Wybór try-

bu pracy następuje

poprzez pin 70 (S/P

SELECT). Połączenie

tego pinu z napięciem

VDD włącza tryb rów-

noległy, połączenie

z masą – tryb szere-

gowy. Inne szczegóły dotyczące tego układu

można znaleźć w Internecie.

Mikroprocesor wykorzystany do stero-

wania układem to AT91SAM7S64. Jest to

procesor z rdzeniem ARM 7-TDMI. Wybór

tego układu był podyktowany chęcią uzyska-

nia możliwie dużej szybkości pracy (56MHz)

oraz liczby pamięci programu (64kB). Także

znacznie większa, w stosunku do procesorów

AVR, szybkość przetworników ADC układu

pozwoliła na sprzętową realizację modulacji

analogowych o paśmie częstotliwości sięgają-

cym kilku kHz. Początkowo układ wyposażo-

ny był w mikroprocesor AVR ATmega8. Nie-

stety, szybkość działania przetworników ADC

nie była wystarczająca do uzyskania sensow-

nego pasma przenoszenia toru analogowego.

Procesor wymaga dołączenia minimal-

nej liczby komponentów związanych z jego

działaniem, głównie kondensatorów fi ltrują-

cych zasilanie. Dodatkowymi elementami są

rezonator kwarcowy oraz kondensatory bocz-

nikujące rezonator. Rezonator ustala częstotli-

wość wewnętrznego oscylatora, która następ-

nie może zostać powielona w wewnętrznym

układzie PLL. Do pinu 39 (NRST) można

dołączyć scalony układ resetu (supervisor).

Pin 55 umożliwia wykasowanie wewnętrznej

pamięci programu. Do pinu 63 (PLLRC) nale-

ży dołączyć fi ltr PLL składający się z dwóch

rezystorów oraz kondensatora. Wartości tych

elementów powinny być dostosowane do czę-

stotliwości pracy układu oraz czasu potrzeb-

nym do zsynchronizowania się pętli (start-up

time). Producent na stronie internetowej udo-

stępnia gotowy plik Excela (xls), który służy

do obliczeń wartości tych elementów. Układ

umieszczony jest w obudowie LQFP oraz

QFN z 64 wyprowadzeniami.

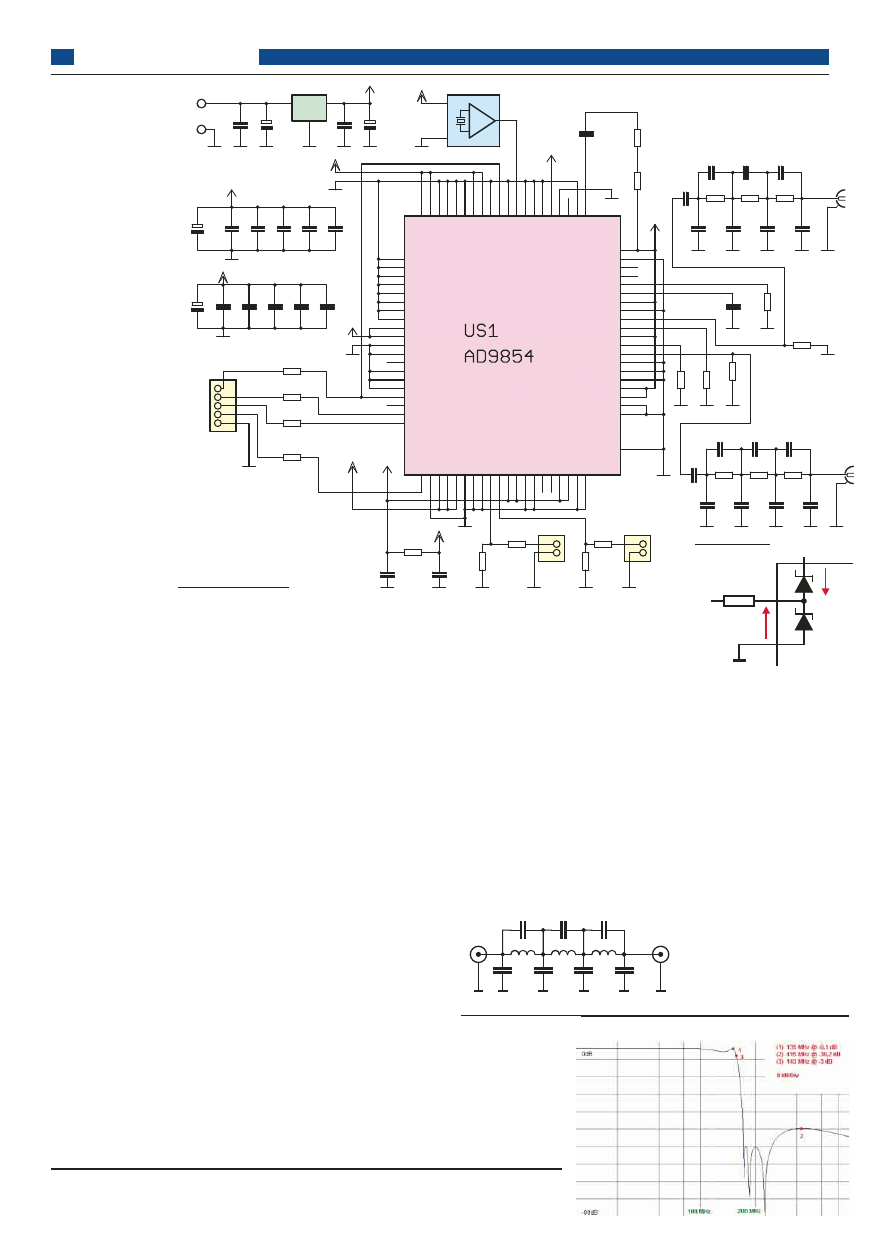

Blok syntezy DDS. Schemat układu syntezy

DDS przedstawia rysunek 2. Układ AD9854

to układ scalony syntezy DDS, generujący

przebieg sinusoidalny oraz arbitralny. Przebieg

aproksymujący sinusoidę występuje na wyjściu

Iout1 oraz Iout1B (piny 48 i 49). Wyjścia te są

komplementarne i oba wymagają rezystorów

zamykających (R8, R11). Przebieg arbitralny

15

Elektronika dla Wszystkich

Maj 2010

Maj 2010

Projekty AVT

#

#

#

#

#

#

#

#

#

2941

2941

Kombajn sygnałowy DDS

Kombajn sygnałowy DDS

Rys. 1

występuje na wyjściu

Iout2 oraz Iout2B.

Także przebiegi wy-

stępujące na tych pi-

nach są przesunięte o

180 stopni i wymagają

rezystorów zamykają-

cych (R9, R10).

Do obu wyjść syn-

tezy dołączone są fi ltry

eliptyczne 7. rzędu,

zbudowane na ele-

mentach L2-L7 oraz

C17-C32. Źródłem

sygnału zegarowego

jest generator kwar-

cowy QG1 o często-

tliwości 28,322MHz.

Częstotliwość ta zosta-

je powielona w bloku

pętli PLL układu US1.

Stopień powielenia zo-

stał zaprogramowany

na 11 razy, zatem czę-

stotliwość taktowania

układu US1 wynosi

311,542MHz. Jest to

więcej niż zalecana

przez producenta czę-

stotliwość taktowania.

Skutkiem przetakto-

wania jest większe grzanie się układu (pobór

prądu i moc strat są silnie zależne od częstotli-

wości taktowania oraz częstotliwości sygnału

wyjściowego). Nie powoduje to nieprawidłowo-

ści w działaniu syntezy DDS, a umożliwia gene-

rację przebiegów o większych częstotliwościach

(w modelu ponad 120MHz). Warto zaznaczyć,

że od jakości sygnału zegarowego (stabilność

długo- i krótkoterminowa, szumy fazowe, jitter)

zależy jakość sygnału wyjściowego syntezy.

Gniazda oznaczone jako FSK oraz S-K

służą do modulacji binarnej sygnału genero-

wanego poprzez syntezę DDS. Gniazdo FSK

umożliwia modulację dwuwartościową FSK

(z rampą lub bez) oraz modulację BPSK.

Gniazdo S-K umożliwia realizację modula-

cji OOK z rampą. W obu przypadkach czas

narastania rampy (czyli liniowej zmiany czę-

stotliwości dla FSK lub amplitudy dla OOK)

jest kontrolowany poprzez oprogramowanie.

Oba wejścia przystosowane są do pracy z syg-

nałami TTL dzięki dzielnikom R1–R2 oraz

R3–R4. Sygnały przekraczające dwukrotnie

poziom napięcia zasilania (tj. 6,6V) nie spo-

wodują uszkodzenia układu, ale powodują

przewodzenie diod ochrony ESD układu US1,

praca w takich warunkach nie jest zalecana.

Nie powinno się zatem przekraczać napięcia

6Vpp na tych gniazdach. Sygnał ten oczywi-

ście powinien być unipolarny.

Gniazdo CON łączy płytkę syntezy DDS

z mikroprocesorowym układem sterowania.

Początkowo układ sterowania oparty był o

mikroprocesor AVR zasilany napięciem 5V,

stąd obecność rezystorów R12–R15. Ich zada-

niem była konwersja napięcia 5V na napięcie

ok 3,6V. Ideę konwersji przedstawia rysunek

3. Tego typu sposób nie jest zalecany, ale czę-

sto stosowany ze względu na prostotę wyko-

nania.

Układ programowany jest oczywiście w

sposób szeregowy z wykorzystaniem sygnału

zegara (WRB/SCLK, pin 21) oraz synchro-

nicznymi danymi (A0/SDIO, pin 19). Piny

danych interfejsu równoległego zostały dołą-

czone do masy (piny od 1 do 8). Elementy R6,

R7, C4 tworzą fi ltr wewnętrznej pętli PLL.

Rezystor R5 wyznacza prąd referencyjny

wewnętrznych przetworników DAC. Dalsze

szczegóły można znaleźć w nocie katalogo-

wej układu AD9854. Kondensator C3 popra-

wia współczynnik SFDR, można go nie mon-

tować, godząc się na większe zniekształcenia

sygnału (gorszy SFDR).

Część cyfrowa ukła-

du zasilana jest z napięcia

+3V3, ale odseparowana

jest od części analogowej

poprzez dławik 100μH

L1. Dodatkowo duża

liczba kondensatorów

SMD o pojemnościach od 100nF do 2,2nF

ma zapewnić skuteczną fi ltrację składowej

zmiennej z szyn zasilania w szerokim zakre-

sie częstotliwości. Jest to niezmiernie ważne

w przypadku cyfrowych układów pracujących

przy dużych częstotliwościach. Układ IC1 jest

stabilizatorem napięcia LDO (o niskim spad-

ku napięcia). Na-

pięcie wyjściowe

tego stabilizatora to

3,3V, maksymalny

prąd obciążenia to

800mA. Układ syntezy wymaga zasilania w

granicach 4V–6V (maksymalne napięcie pra-

cy IC1). Wydajność prądowa układu zasilania

nie powinna być mniejsza od 1A, ze względu

na znaczny pobór prądu przez pracującą syn-

tezę DDS (ok. 800mA, zależnie od częstotli-

wości wyjściowej).

Filtr eliptyczny. Ma on za zadanie stłumić

wyższe harmoniczne sygnału generowanego

przez syntezę DDS. Schemat zastosowane-

go fi ltru eliptycznego przedstawia rysunek

4. Filtr ten jest fi ltrem dolnoprzepustowym

siódmego rzędu, dopasowanym obustronnie

do impedancji 50Ω. Charakterystyka amplitu-

dowa tego fi ltru pokazana

jest na rysunku 5.

Filtr został zaprojekto-

wany i przeanalizowany w

programie RFSim. Proce-

dura projektowania zakła-

Rys. 5

16

Projekty AVT

Maj 2010

Maj 2010

100u

+

3

V

3

V

D

D

10n

10n

+

3

V

3

V

D

D

V

D

D

+

3

V

3

+

3

V

3

33k

3

3

k

33k

3

3

k

10n

4

.7

k

1

k

2

2

0

10n

V

D

D

V

D

D

+

3

V

3

10n

10n

10n

10n

2.2n

2.2n

100n 100n

100n 100n

47u

47u

5

1

51

5

1

5

1

4

,7

u

3

2

0

n

47nH

47nH

47nH

47nH

47nH

47nH

22p

22p

22p

22p

22p

22p

22p

22p

4

.7

p

6

.8

p

1

0

p

4

.7

p

6

.8

p

1

0

p

100n 220u

100n 47u

+

3

V

3

2.2k

2.2k

2.2k

2.2k

D7

1

D6

2

D5

3

D4

4

D3

5

D2

6

D1

7

D0

8

DVDD0

9

DVDD1

10

DGND0

11

DGND1

12

(NC1)

13

A5

14

A4

15

A3

16

A2/IO-RESET

17

A1/SDO

18

A0/SDIO

19

I/O-UD-CLK

20

W

R

B

/S

C

LK

2

1

R

D

B

/C

S

B

2

2

D

V

D

D

2

2

3

D

V

D

D

3

2

4

D

V

D

D

4

2

5

D

G

N

D

2

2

6

D

G

N

D

3

2

7

D

G

N

D

4

2

8

FS

K

/B

P

S

K

/H

O

LD

2

9

S

H

A

P

E

D

-K

E

YI

N

G

3

0

AV

D

D

0

3

1

AV

D

D

1

3

2

A

G

N

D

0

3

3

A

G

N

D

1

3

4

(N

C

2)

3

5

V

O

U

T

3

6

AV

D

D

2

3

7

AV

D

D

3

3

8

A

G

N

D

2

3

9

A

G

N

D

3

4

0

AGND4

41

VIN-POS

42

VIN-NEG

43

AVDD4

44

AGND5

45

AGND6

46

AGND7

47

IOUT1

48

IOUT1B

49

AVDD5

50

IOUT2B

51

IOUT2

52

AGND8

53

AVDD6

54

DACBP

55

DAC-R-SET

56

(NC3)

57

(NC4)

58

AGND9

59

AVDD7

60

P

LL

-F

LT

6

1

A

G

N

D

10

6

2

(N

C

5)

6

3

D

IF

F-

C

LK

-E

N

6

4

AV

D

D

8

6

5

A

G

N

D

11

6

6

A

G

N

D

12

6

7

R

E

FC

LK

B

6

8

R

E

FC

LK

6

9

S

/P

-S

E

LE

C

T

7

0

M

A

S

TE

R

-R

E

S

E

T

7

1

D

G

N

D

5

7

2

D

V

D

D

5

7

3

D

V

D

D

6

7

4

D

G

N

D

7

7

5

D

G

N

D

8

7

6

D

G

N

D

9

7

7

D

G

N

D

10

7

8

D

V

D

D

7

7

9

D

V

D

D

8

8

0

EP

P$1

L1

C1

C2

1

2

FSK

R1

R

2

1

2

S-K

R3

R

4

C3

R

5

R

6

R

7

C4

7

14

8

QG1

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

R

8

R9

R

1

0

R

11

C

1

7

C

1

8

L2

L3

L4

L5

L6

L7

C19

C20

C21

C22

C23

C24

C25

C26

C

2

7

C

2

8

C

2

9

C

3

0

C

3

1

C

3

2

1

2

3

4

5

CON

X1-1

X1-2

IC1

GND

IN

OUT

C33

C34

C35

C36

R12

R13

R14

R15

X2

X3

GND

VCC

OUT

+

+

+

+

TC1264 3,3V

TC1264 3,3V

D1

D2

0,3V

3,6V

AD9854

R

3,3V

5V

47nH

22pF

10pF

47nH

22pF

16,8pF

47nH

22pF

20pF

22pF

50R

50R

Rys. 2

Rys. 3

Rys. 4

dała stałe wartości dławików i takie dobranie

kondensatorów (lub ich równoległego połącze-

nia), aby uzyskać optymalną charakterystykę.

Dobór elementów fi ltru powinien umożliwić

możliwie największą stromość charakterysty-

ki przy zachowaniu małego zafalowania w pa-

śmie przepustowym oraz dobrego tłumienia w

paśmie zaporowym. Jako że sygnały lustrzane

sygnału wyjściowego syntezy DDS powyżej

częstotliwości próbkowania (311,542MHz)

maleją wraz ze wzrostem częstotliwości, fi ltr

powyżej tej częstotliwości ma tłumienie tylko

38dB (81 razy), co jest zupełnie wystarczają-

ce, aczkolwiek w precyzyjnych urządzeniach

pomiarowych zawierających syntezę DDS na-

leży tak dobrać fi ltr, aby tłumienie w zakresie

wyższych częstotliwości było zdecydowanie

lepsze. Największy poziom sygnałów lustrza-

nych występuje w zakresie częstotliwości Ny-

quista – częstotliwość próbkowania (155MHz

–311,542MHz) i w tym zakresie fi ltr powinien

wykazywać największe tłumienie. W zakresie

163MHz–260MHz tłumienie fi ltru nie jest

gorsze niż 48dB.

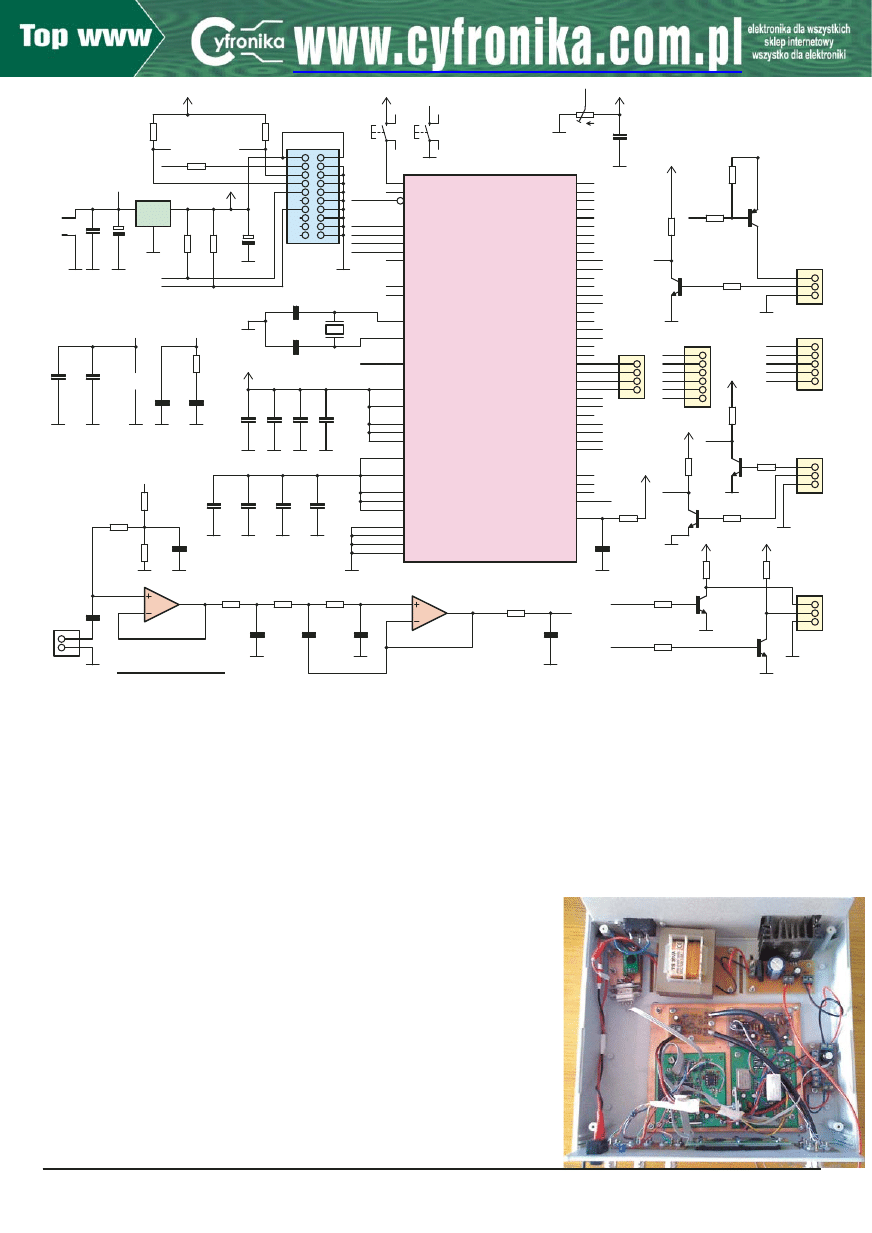

Blok układu sterowania. Układ sterowania

został zrealizowany na mikroprocesorze z

rdzeniem ARM7 TDMI. Sercem układu jest

mikroprocesor AT91SAM7S64. Schemat

układu przedstawiony jest na rysunku 6.

Układ taktowany jest częstotliwością 16MHz,

która generowana jest poprzez wewnętrzny

oscylator mikroprocesora z dołączonym ze-

wnętrznym rezonatorem kwarcowym Q1. Na-

stępnie częstotliwość ta ulega powieleniu w

układzie PLL do częstotliwości 56,177MHz.

Układ odbiera dane sterujące poprzez in-

terfejs RS232 z komputera PC i odpowiednio

konfi guruje syntezę DDS. Moduł mikropro-

cesorowy składa się z 5 podbloków, mianowi-

cie: układu zasilania, układu fi ltru dolnoprze-

pustowego, bloku konwerterów poziomów,

układu programowania JTAG oraz wyświet-

lacza alfanumerycznego LCD 2x16 znaków.

Blok zasilania składa się ze stabilizatora

napięcia 3,3V (IC2) oraz kondensatorów włą-

czonych pomiędzy szyny zasilania oraz masę.

Warto zaznaczyć, że rdzeń procesora wymaga

napięcia zasilania 1,8V. Napięcie to wytwa-

rzane jest przez sam układ AT91SAM7S64 i

jest dostępne na pinie 8 (VDDOUT). Pin ten

połączony jest z pinami zasilającymi rdzeń

mikroprocesora oraz układ wewnętrznej pętli

PLL. Stąd dodatkowe kondensatory fi ltrujące

to napięcie zasilania (C1–C4). Jak już wspo-

mniano przy omawianiu syntezy DDS fi ltracja

napięcia zasilającego w przypadku szybkich

układów cyfrowych jest bardzo ważna, stąd

zastosowanie elementów SMD oraz konden-

satorów o różnych wartościach pojemności

umieszczonych blisko układu scalonego (po-

cząwszy od najmniejszych pojemności). Brak

dobrej fi ltracji może objawiać się dziwnym

zachowaniem mikroprocesora, trudnym do

zdiagnozowania. Do układu zasilania dołą-

czone są także elementy fi ltrujące napięcie

odniesienia układu przetwornika analogowo-

cyfrowego: L1, C12, także te elementy powin-

ny być umieszczone możliwie jak najbliżej

układu scalonego. Kolejnym blokiem jest fi ltr

dolnoprzepustowy 4. rzędu z wielokrotnym

sprzężeniem zwrotnym (MFB). Układ składa

17

17

Elektronika dla Wszystkich

Maj 2010

Maj 2010

AT91SAM7S64

100n

100n

10n

V

C

C

100n

10n

1

6

M

H

z

1

0

p

1

0

p

V

C

C

220u

47u

100n

zas

V

C

C

1u

1u

10n

1n

4

7

k

4

7

k

4

7

k

4

7

k

V

C

C

BC547B

BC557

V

C

C

1

.5

k

4

.7

k

1.5k

1.5k

100u

100n

V

C

C

10k

V

C

C

NE5532

NE5532

22k

10k

4.7k

4.7k

10n

4.7n

4.7n

1n

4

7

k

4

7

k

100n

47k

100n

470

BC547B

BC547B

GND

4

.7

k

4

.7

k

V

C

C

V

C

C

10k

10k

BC547B

BC547B

10k

10k

1

.5

k

1

.5

k

V

C

C

V

C

C

100n

100n

100n

10n

4

7

0

VDDIN

7

VDDFLASH

59

VDDIO

18

VDDIO

45

VDDIO

58

VDDOUT

8

VDDPLL

64

VDDCORE

12

VDDCORE

24

VDDCORE

54

GND

2

GND

17

GND

46

GND

60

XIN

62

XOUT

61

PLLRC

63

DDP

57

DDM

56

ERASE

55

TST

40

/NRST

39

JTAGSEL

50

TCK

53

TDI

33

TMS

51

TDO

49

ADVREF

1

AD4

3

AD5

4

AD6

5

AD7

6

PA0/PWM0/TIOA0

48

PA1/PWM1/TIOB0

47

PA2/PWM2/SCK0

44

PA3/TWD/NPCS3

43

PA4/TWCK/TLCK0

36

PA5/RXD0/NPCS3

35

PA6/TXD0/PCK0

34

PA7/RTS0/PWM3

32

PA8/CTS0/ADTRG

31

PA9/DRXD/NPCS1

30

PA10/DTXD/NPCS2

29

PA11/NPCS0/PWM0

28

PA12/MISO/PWM1

27

PA13/MOSI/PWM2

22

PA14/SPCK/PWM3

21

PA15/TF/TIOA1

20

PA16/TK/TIOB1

19

PA17/TD/PCK1/AD0

9

PA18/RD/PCK2/AD1

10

PA19/RK/FIQ

13

PA20/RF/IRQ0/AD3

16

PA21/RXD1/PCK1

11

PA22/TXD1/NPCS3

14

PA23/SCK1/PWM0

15

PA24/RTS1/PWM1

23

PA25/CTS1/PWM2

25

PA26/DCD1/TIOA2

26

PA27/DTR1/TIOB2

37

PA28/DSR1/TCLK1

38

PA29/RI1/TCLK2

41

PA30/IRQ1/NPCS2

42

PA31/NPCS1/PCK2

52

C1

C2

C4

C6

C8

2

1

Q

1

C

9

C

1

0

IC2

GND

IN

OUT

C13

C14

C15

X1-1

X1-3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

JTAG

3

1

2

4

S

1

C3

C5

C7

C11

R

2

R

3

R

4

R

5

T1

T2

R

1

R

6

R7

R8

1

2

3

RS232

L1

C12

1

2

3

4

DATA

1

2

3

4

5

6

CTRL

1

3

2

3

2

R9

2

3

1

IC3A

6

5

7

IC3B

8

4

R10

R11

R12

R13

C16

C17

C18

C19

R

1

4

R

1

5

C20

R16

C21

1

2

MODIN

R17

3

1

2

4

S

2

T3

T4

R

1

8

R

1

9

R20

R21

1

2

3

D_IN

1

2

3

4

5

DDS

T5

T6

R22

R23

R

2

4

R

2

5

1

2

3

D_OUT

C22

C23

C24

C25

R

2

6

GND

GND

GND

TMS

TMS

TDI

TDI

TCK

TCK

TDO

TDO

PLL

PLL

NRST

NRST

N

R

S

T

TX1

TX1

RX1

RX1

CT

C

T

RW

RW

EN

EN

+5V

+5V

+5V

+5V

+5V

ADC

ADC

DCLK

DCLK

DAT

DAT

SCLK

SCLK

IOUP

IOUP

SDIO

SDIO

RESET

RESET

OCLK

OCLK

ODAT

ODAT

+

+

TC1264 3,3V

TC1264 3,3V

IC1

Rys. 6

się z jednego podwójnego wzmacniacza ope-

racyjnego NE5532. Pierwszy wzmacniacz,

IC3A, to wtórnik napięciowy, który separuje

od reszty układu sygnał wejściowy podawany

na wejście MODIN. Zapobiega także uszko-

dzeniu mikroprocesora w przypadku zbyt

dużej amplitudy sygnału wejściowego. Ele-

menty R14, R15, R16 wytwarzają napięcie

sztucznej masy na poziomie 2,5V, C20 fi ltruje

to napięcie. Po wtórniku napięciowym sygnał

trafi a na fi ltr dolnoprzepustowy zbudowany

na wzmacniaczu IC3B oraz elementach R12–

C17, R11–C18, R10–C19. Na wyjściu układu

IC3B znajduje się jeszcze jeden stopień fi ltra-

cji R13–C16. Następnie sygnał trafi a na prze-

twornik ADC mikroprocesora.

Konwertery poziomów mają za zadanie

dopasowanie sygnałów o różnych napięciach

do napięć akceptowalnych przez układ mi-

kroprocesora. Jednym z takich bloków jest

konwerter RS232 zbudowany na tranzysto-

rach T1 oraz T2. Układ odznacza się dużą

prostotą, zamiast tych tranzystorów można

użyć dedykowanego konwertera RS232-TTL

np. MAX232. Z układem jak na schemacie nie

było żadnych problemów, pracuje poprawnie

na szybkości 115200b/s. Tranzystory T5 oraz

T6 zapewnią wyprowadzenie sygnałów wyj-

ściowych do układów pomiarowych np. oscy-

loskopu, w celu synchronizacji danych modu-

lujących oraz przebiegu zmodulowanego wy-

twarzanego przez syntezę DDS. Tranzystory

T3, T4 służą do wprowadzania danych wej-

ściowych (modulujących). Programowanie

mikroprocesora odbywa się poprzez interfejs

JTAG. Złącze oznaczone jako JTAG służy do

podpięcia programatora (WIGGLER). Rezy-

story R2–R5 podciągają piny interfejsu JTAG

do dodatniej szyny zasilania. Rezystor R17

nie został zamontowany (reset programowy

stwarzał problemy podczas testowania ukła-

du), resetowanie układu odbywa się ręcznie za

pomocą przycisku S2 lub poprzez włączenie

i wyłączenie układu. Dodatkowo wewnętrzną

pamięć FLASH można skasować za pomocą

przycisku S1. Szczegóły dotyczące tej proce-

dury zawarte są w nocie katalogowej układu

AT91SAM7S64. Ostatnim ele-

mentem jest wyświetlacz LCD.

Wyświetlacz składa się z dwóch

linii po 16 znaków. Zawiera

włączone podświetlanie w celu

zapewnienia wygodnego od-

czytu w różnych warunkach

oświetleniowych. Potencjometr

R9 służy do regulacji kontrastu

wyświetlacza.

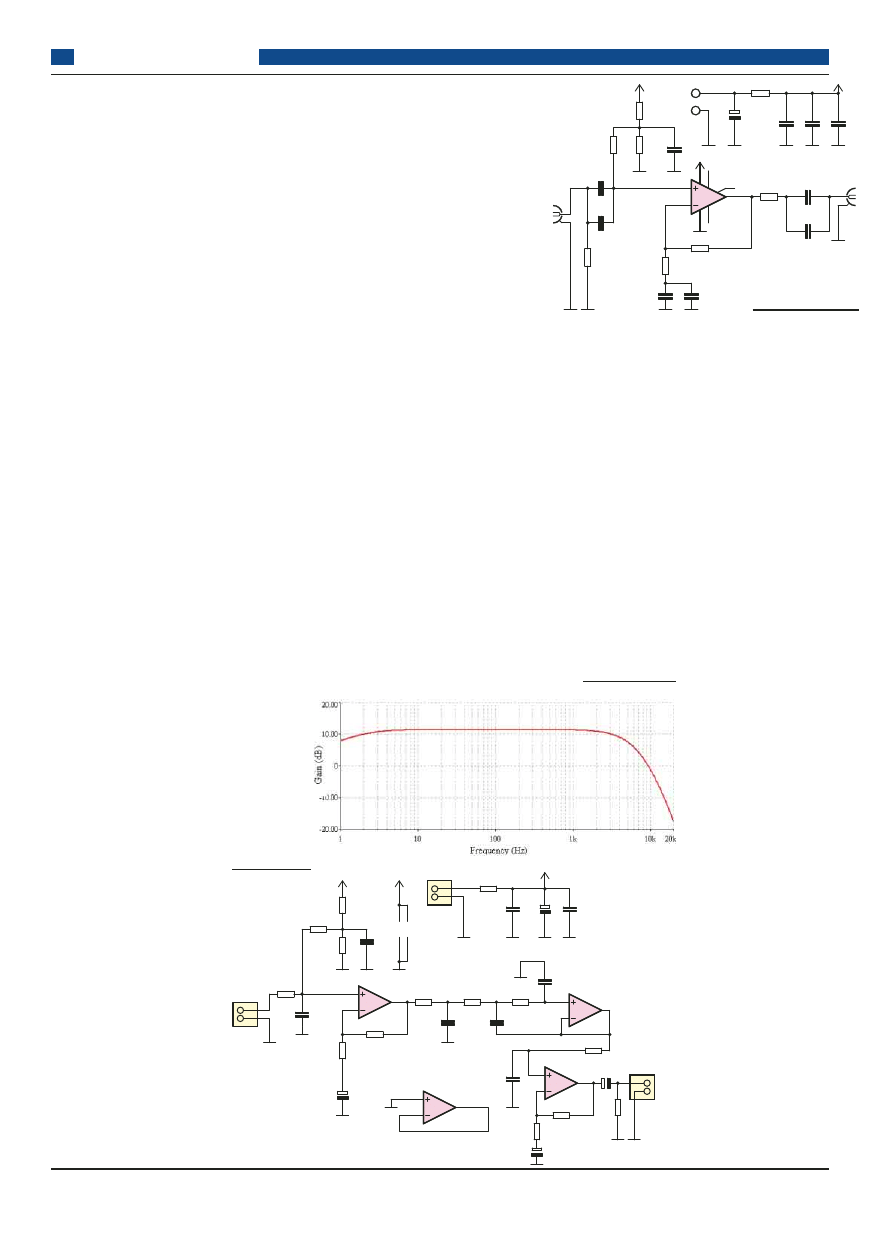

Blok fi

ltru generatora arbi-

tralnego. Schemat układu fi ltru

generatora arbitralnego przed-

stawiony jest na rysunku 7.

Układ jest fi ltrem aktywnym

zbudowanym w oparciu o dwa

wzmacniacze operacyjne typu

NE5532. Składa się on z 3

bloków: wzmacniacz wejściowy, które-

go celem jest wzmocnienie sygnału oraz

odseparowanie płytki syntezy DDS od

układu fi ltrującego, układ fi ltru dolnoprze-

pustowego 5. rzędu oraz wzmacniacz wyj-

ściowy zapewniający niską impedancję

wyjściową. Wzmacniacz wejściowy został

zbudowany na wzmacniaczu IC1A oraz

elementach C6, R8, R9. Wzmocnienie

tego stopnia wynosi +2. Układ rezystorów

R1, R2, R3 wytwarza napięcie sztucznej

masy na poziomie VCC/2. Kondensator

C1 usuwa składową zmienną z tego na-

pięcia. Napięcie to jest konieczne do po-

prawnej pracy wzmacniaczy operacyjnych

zasilanych napięciem unipolarnym. Blok ten

nie zawiera kondensatora fi ltrującego skła-

dową stałą na wejściu, gdyż taki kondensator

znajduje się na bloku syntezy DDS (C17). Na

blok fi ltru dolnoprzepustowego składają się

elementy R5–C3, R6–C4, R7–C5, R10–C7

oraz w bloku wejściowym R4–C2. Jest to za-

tem fi ltr piątego rzędu. Układ IC1B pracuje w

układzie fi ltru MFB (z wielokrotnym sprzę-

żeniem zwrotnym). Po bloku fi ltracji sygnał

trafi a na wzmacniacz wyjściowy. Wzmac-

niacz wyjściowy ma za zadanie odseparowa-

nie fi ltru dolnoprzepustowego od obciążenia

dołączonego do układu. Wzmacniacz IC2A

wraz z elementami R11, R12, C8 tworzy

nieodwracający wzmacniacz o wzmocnieniu

+2. Elementy C9, R13 odcinają składową

stałą, pozostawiając tylko przebieg zmienny.

Niewykorzystany wzmacniacz IC2B został

połączony w konfi guracji minimalizującej

samowzbudzenie. Charakterystyka całego

modułu fi ltru przedstawiona jest na rysunku

8. Dolna częstotliwość graniczna wyznaczona

jest przez pojemności C17 (na płytce syntezy

DDS) oraz C6, C8 i C9 i wynosi ona ok. 2 Hz

(–3dB). Górna częstotliwość graniczna (–3dB)

wynosi 4,4kHz. Elementy L1, C10, C11, C12

służą do fi ltracji napięcia zasilającego. Napię-

cie zasilania może mieścić się w granicach 4V

– 16V (maksymalne napięcie zastosowanych

kondensatorów elektrolitycznych).

Stopień wyjściowy syntezy DDS. W celu od-

separowania syntezy DDS od obciążenia, a

przez to także w celu ochrony układu scalo-

nego, zastosowano wyjściowy bufor szeroko-

pasmowy. Schemat układu pokazany jest na

rysunku 9. Układ opiera się o wzmacniacz

operacyjny ze sprzężeniem prądowym –

TSH330. Parametry tego wzmacniacza można

znaleźć w Internecie.

Sygnał wyjściowy z syntezy DDS (gniaz-

do X3 na płytce syntezy DDS) trafi a na wej-

ście modułu bufora – gniazdo X1. Rezystor

R3 dopasowuje linię transmisyjną zbudowa-

ną z układu przetwornika

DAC, układu AD9854

– fi ltr eliptyczny – prze-

wód 50Ω RG58U – blok

bufora. Jest on konieczny

ze względu na duże często-

tliwości transmitowanego

sygnału, bez niego w linii

pojawiają się odbicia, co

powoduje zniekształcenia

sygnału oraz generację za-

kłóceń. Kondensatory C3

oraz C11 (niezamontowany)

odcinają składową stałą wy-

twarzaną przez obwód sztucz-

nej masy. Obwód sztucznej

masy składa się z rezystorów

R4, R5 oraz R6. Kondensator

C4 fi ltruje napięcie sztucznej

masy i zapobiega przenikaniu

zakłóceń z szyn zasilających

na wejście nieodwracające

wzmacniacza.

Wzmacniacz IC1 jest

wzmacniaczem ze sprzę-

żeniem prądowym. Dobór

rezystorów ustalających

wzmocnienie opierało się o

dane katalogowe, gdyż tyl-

18

Projekty AVT

Elektronika dla Wszystkich

Maj 2010

Maj 2010

NE5532N

NE5532N

NE5532N

NE5532N

1

0

k

1

0

k

100k

V

C

C

100n

6.8k

2.2n

6.8k

10k

100k

2.2n

470p

100p

GND

2,2k

2

.2

k

10u

6.8k

1n

10k

1

0

k

10u

1

0

u

1

0

0

k

V

C

C

100n

47u

100u

V

C

C

100n

2

3

1

IC1A

6

5

7

IC1B

8

4

2

3

1

IC2A

6

5

7

IC2B

8

4

R

1

R

2

R3

C1

R4

C2

R5

R6

R7

C3

C4

C5

R8

R

9

C6

R10

C7

R11

R

1

2

C8

1

2

JP1

1

2

JP2

C

9

R

1

3

1

2

ZAS

C10

C11

L1

C12

+

+

+

+

Rys. 7

THS330

V

C

C

220

1

0

0

1u

10n

5

1

4

7

0

4

7

0

1

.5

k

V

C

C

1

0

0

n

100n

51

1

0

0

n

*

47u

100u

100n

10n

1n

VCC

*

5

1

5

1

2

3

6

8

6

8

IC1

7

IC1

7

4

R1

R

2

C1

C2

R

3

R

4

R

5

R

6

C

3

C4

X1

R7

C

5

C

6

X2-1

X2-2

C7

L1

C8

C9

C10

X3

C

11

+

Rys. 9

Rys. 8

ko przy poprawnym dobraniu rezystora R1

układ jest stabilny, a pasmo przenoszenia nie

zależy od wzmocnienia. Wzmocnienie moż-

na regulować, zmieniając wartość rezystora

R2. Wzmocnienie układu wynosi 6,2 raza.

Obecność elementów C1 oraz C2 uniemoż-

liwia wzmacniaczowi wzmacnianie napięcia

niezrównoważenia oraz napięcia sztucznej

masy. Dla składowej stałej wzmacniacz ma

wzmocnienie równe jeden. C1 został dodat-

kowo zbocznikowany kondensatorem C2 o

znacznie mniejszej pojemności w celu rów-

nomiernego rozkładu wzmocnienia w funk-

cji częstotliwości. Moduł impedancji C2 jest

znacznie mniejszy przy wyższych częstotli-

wościach niż dużego kondensatora C1. W

podobnym celu zostawiono miejsce na płytce

na elementy C6 i C11, jednak współpracujące

z nimi kondensatory 100nF dobrze pracują w

szerokim zakresie częstotliwości. Po testach

modułu konieczne okazało się dodanie obwo-

du R8, C12, który kompensuje spadek ampli-

tudy syntezy DDS w zakresie najwyższych

generowanych częstotliwości. Elementy te

nie są uwzględnione na płytce PCB i należy

je przylutować od strony druku. Filtracja zasi-

lania została zrealizowana na elementach C7,

L1, C8, C9, C10. Różne wartości pojemności

służą zapewnieniu minimalnej impedancji

całego bloku kondensatorów w możliwie naj-

szerszym zakresie częstotliwości. Rezystor

R7 zapewnia dopasowanie do linii zasilającej

obciążenie 50Ω (kanał wejściowy oscylosko-

pu lub analizatora widma z wejściem 50Ω).

Blok zasilacza. Składa się on z dwóch płytek,

jednej odpowiedzialnej za wyprostowanie na-

pięcia z transformatora, jego wygładzenie oraz

stabilizowanie na poziomie 5V oraz drugiej

– odpowiedzialnej za rozdzielenie napięcia

na poszczególne moduły oraz jego dokładną

fi ltrację. Dodatkowo na płytce zamocowano

gniazdo do podłączenia wentylatora. Schemat

pierwszego obwodu można zobaczyć na ry-

sunku 10. Mostek B1 przystosowany jest do

pracy z prądami do 2A. Kondensatory C1 i C2

fi ltrują napięcie zasilające stabilizator. Napię-

cie 5V dostępne jest na wyjściu – gniazdo X-

-2. Stabilizator jest typu 7805 o maksymalnym

prądzie 1A. Uzwojenie wtórne transformatora

podłączone jest z płytką za pomocą gniazda

X-1. Zastosowano transformator o napięciu

12V oraz mocy 12VA. Drugi element układu

zasilania stanowi płytka fi ltrów oraz rozdzie-

lenia napięcia na poszczególne bloki syntezy.

Schemat układu można zobaczyć na rysunku

11. Największy prąd pobiera układ syntezy.

Tor zasilania syntezy składa się z dławika L1

oraz kondensatorów C2, C3, C6. Dławik L1

separuje syntezę DDS od pozostałych bloków,

składowa zmienna generowana przez pracują-

cą syntezę nie powinna się przedostawać do

torów zasilania innych bloków, szczególnie

wzmacniaczy wyjściowych. Przed dławi-

kiem znajdują się elementy fi ltrujące napięcie

zasilania do modułów mikroprocesora oraz

wzmacniaczy wyjściowych. Procesor został

podpięty bezpośrednio pod dodatnią szynę

zasilania. Wzmacniacz wyjściowy TSH330

oraz wzmacniacz – fi ltr generatora arbitral-

nego zostały wpięte poprzez 100μH dławiki.

Kondensator elektrolityczny C4 to kondensa-

tor typu LOW ESR. Dławik L1 ma indukcyj-

ność 250μH i może pracować z prądami do

1A, rezystancja jego uzwojeń jest pomijalna.

Rezystor R1 ogranicza prąd niebieskiej diody

LED, która jest sygnalizatorem występowania

napięcia zasilającego.

Oprogramowanie

Oprogramowanie urządzenia składa się z

dwóch programów, jeden instalowany jest

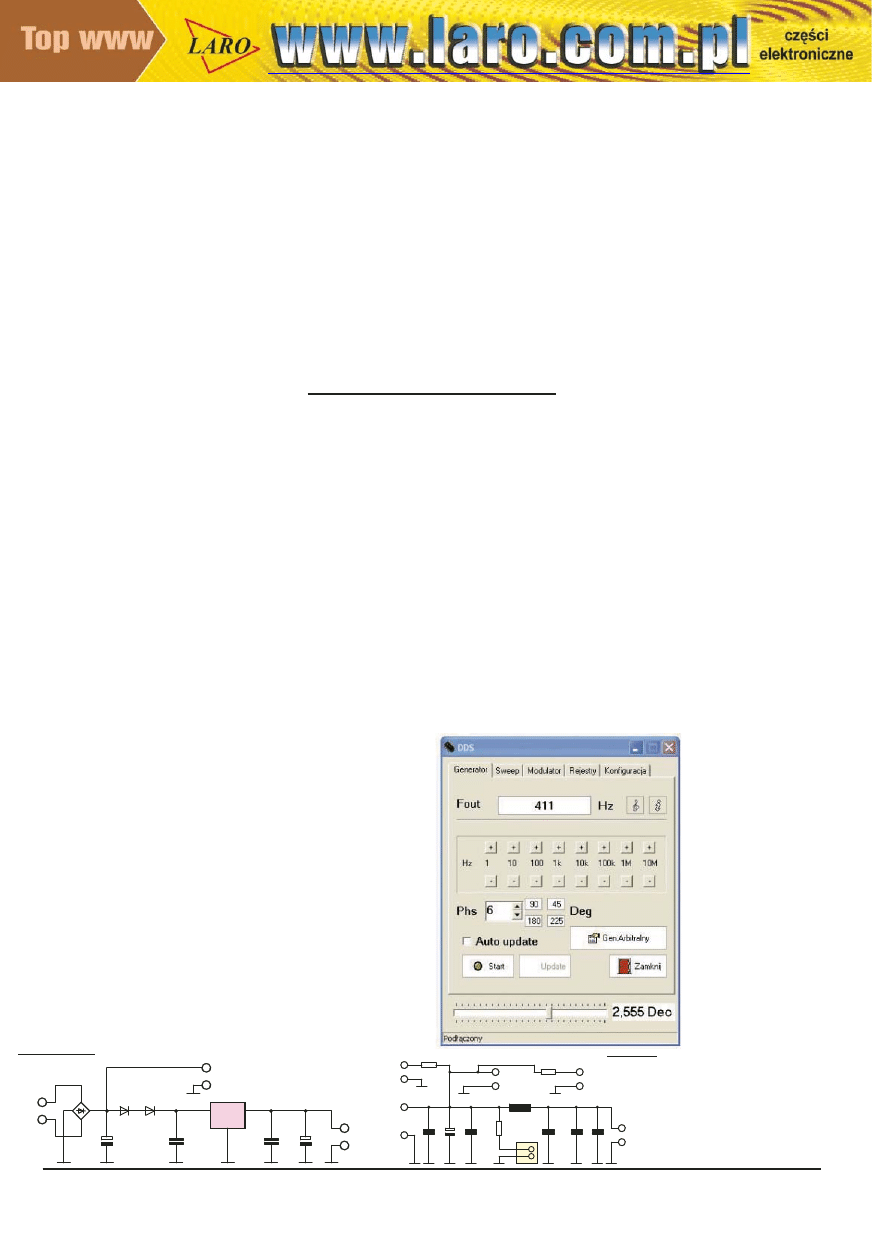

na komputerze klasy PC (oprogramowanie

użytkownika), drugi jest zawarty w pamięci

programu mikroprocesora sterującego synte-

zą DDS. Oprogramowanie na PC zapewnia

pełną kontrolę nad urządzeniem. Oprogramo-

wanie użytkownika zostało napisane w pakie-

cie Borland Delphi 6.0. Program składa się z

kilku zakładek służących do sterowania ukła-

dem. Do podstawowych opcji należą:

1. Generator sinusoidalny przestrajany.

2. Wobulator.

3. Modulator (cyfrowy, analogowy).

4. Bezpośredni dostęp do rejestrów syntezy.

5. Generator arbitralny.

Generator. Zakładka ta pozwala regulować

częstotliwość, amplitudę oraz fazę sygnału si-

nusoidalnego generowanego przez syntezę. Ze

względu na znaczny

zakres przestrajania

wprowadzono sekcję

przycisków służącą

do łatwego zadawa-

nia częstotliwości.

Można także włączyć

oraz wyłączyć auto-

matyczne wysyłanie

nowych danych do

syntezy DDS (opcja

auto update). Poni-

żej sekcji przycisków

znajduje się regulacja

fazy. Dodatkowe czte-

ry przyciski pozwala-

ją na szybką zmianę

fazy. Ręczny zakres

wynosi od 0˚ do 359˚

z krokiem 1˚. Obok

znajduje się przycisk włączający panel ge-

neratora arbitralnego oraz przycisk zamknię-

cia programu. Na samym dole umieszczono

suwak regulacji amplitudy. Zakres regulacji

wynosi 0–4095 dec wartości próbki z krokiem

5 dec.

Wobulator. Zakładka „SWEEP” pozwala na

liniowe przemiatanie częstotliwości w pełnym

zakresie pracy syntezy z dowolnym krokiem i

z dowolnym czasem na krok. Tego typu opcja

bywa przydatna w badaniu pasma przenosze-

nia fi ltrów itp.

Modulator. Zakładka „Modulator” służy do

wyboru jednej z wielu modulacji zaaplikowa-

nych w układzie. Modulacje te zostały podzie-

lone na 3 kategorie:

1. Programowe – w których parametry fali noś-

nej oraz sygnały modulujące są generowane

przez oprogramowanie użytkownika (jak np.

dane do wysłania) lub program mikroproce-

sora (analogowe sygnały modulujące).

2. Analogowe – sprzętowe, modulacje analo-

gowe, których sygnał modulujący podawany

jest na wejście analogowe urządzenia (X3).

3. Cyfrowe – sprzętowe, modulacje impulsowe

(z kluczowaniem), których dane wejściowe

podawane są na jedno z gniazd X1 lub X2.

Ze względu na dużą złożoność obliczeń mo-

dulacje programowe (szczególnie analogowe)

nie mają szerokiego pasma. Zdecydowanie

najszybsze są modulacje cyfrowe sprzętowe.

Tryb rejestrowy. Umożliwia bezpośredni do-

stęp do rejestrów syntezy. Program użytkowni-

ka emuluje wygląd rejestrów syntezy i umoż-

liwia ich ręczną konfi gurację. Nie wszystkie

rejestry są dostępne, nie jest to konieczne do

konfi guracji syntezy. W razie pomyłki lub

dziwnego zachowania się syntezy, spowodo-

wanego błędną konfi guracją, dwa przyciski

na panelu umożliwiają

zresetowanie syntezy i

jej ponowną domyślną

inicjalizację.

Generator arbitralny.

Jest to podprogram słu-

żący do generacji do-

wolnej funkcji napięcia

opisanej matematyczną

funkcją jednej zmien-

nej (drugą zmienną jest

czas). W skład panelu

generatora arbitralnego

wchodzą przyciski z na-

zwami funkcji matema-

tycznych, wartości licz-

bowe oraz możliwość

dodania szumu.

Równanie można

także wpisać ręcznie w

okienku nad panelem

z przyciskami. Dodatkowo

możliwe jest powiększenie

fragmentu przebiegu, obcię-

cie go do pełnego okresu (ma-

nualne oraz automatyczne)

19

19

Elektronika dla Wszystkich

Maj 2010

Maj 2010

2200u

100n

7805

100n

220u

5V

Went

D1, D2 1N4007

A

C

1

A

C

2

-

+

B1

X1-1

X1-2

C1

C2

IC1

GND

IN OUT

C3

C4

X2-1

X2-2

X3-1

X3-2

D1

D2

+

+

Rys. 10

100nF

10n

470p

220u

250u

100nF

4

7

0

10n

100u

100u

X1-1

X1-2

C1

C2

C3

C4

L1

C6

1

2

LED

R

1

DDS-1

DDS-2

C5

ARM-1

ARM-2

TSH-1

TSH-2

L2

ARB-1

ARB-2

L3

+

Rys. 11

tak, aby zachować ciągłość fazy, oraz zmiana

ustawień długości rekordu danych. Wysła-

nie danych do syntezy trwa ok. 2 sekund, po

czym na gnieździe ARB występuje zadany

przebieg.

Konfi guracja programu. Program przed

pierwszym uruchomieniem wymaga skonfi -

gurowania. Najważniejsze jest skonfi guro-

wanie portu COM, który zostanie użyty do

transmisji danych. Port ten tworzony jest wir-

tualnie na komputerze użytkownika poprzez

przejściówkę USB-RS232, więc mimo że wy-

korzystuje się od strony systemu procedury

obsługi portu COM, to urządzenie połączone

jest z komputerem poprzez złącze USB. Moż-

liwa jest konfi guracja ręczna – poprzez wpisa-

nie portu COM oraz konfi guracja automatycz-

na – program wyszuka aktywne porty COM.

Jeśli nie ma innych urządzeń korzystających z

portów szeregowych, to wyświetlony port jest

portem urządzenia. Dodatkowo istnieje moż-

liwość wyłączenia powielacza częstotliwości

taktowania (PLL). Umożliwia to zaobserwo-

wanie przebiegu generowanego przez syntezę

z obejściem fi ltru, którego częstotliwość od-

cięcia jest znacznie większa niż częstotliwość

uzyskiwanych sygnałów. Częstotliwość tak-

towania wynosi wtedy 28,322MHz, a często-

tliwość fi ltru 143MHz (–3dB). Ogranicza to

maksymalną częstotliwość wyjściową prze-

biegu do 14MHz.

W modelu wykorzystano przejściówkę

USB-RS232, która od strony systemu ope-

racyjnego widziana jest jako wirtualny port

COM. Przejściówki takie kosztują kilkanaście

złotych i można je łatwo kupić np. na Allegro.

Przejściówka jest opcjonalna, układ może wy-

korzystywać interfejs RS232, z pominięciem

przejściówki.

Montaż i uruchomienie

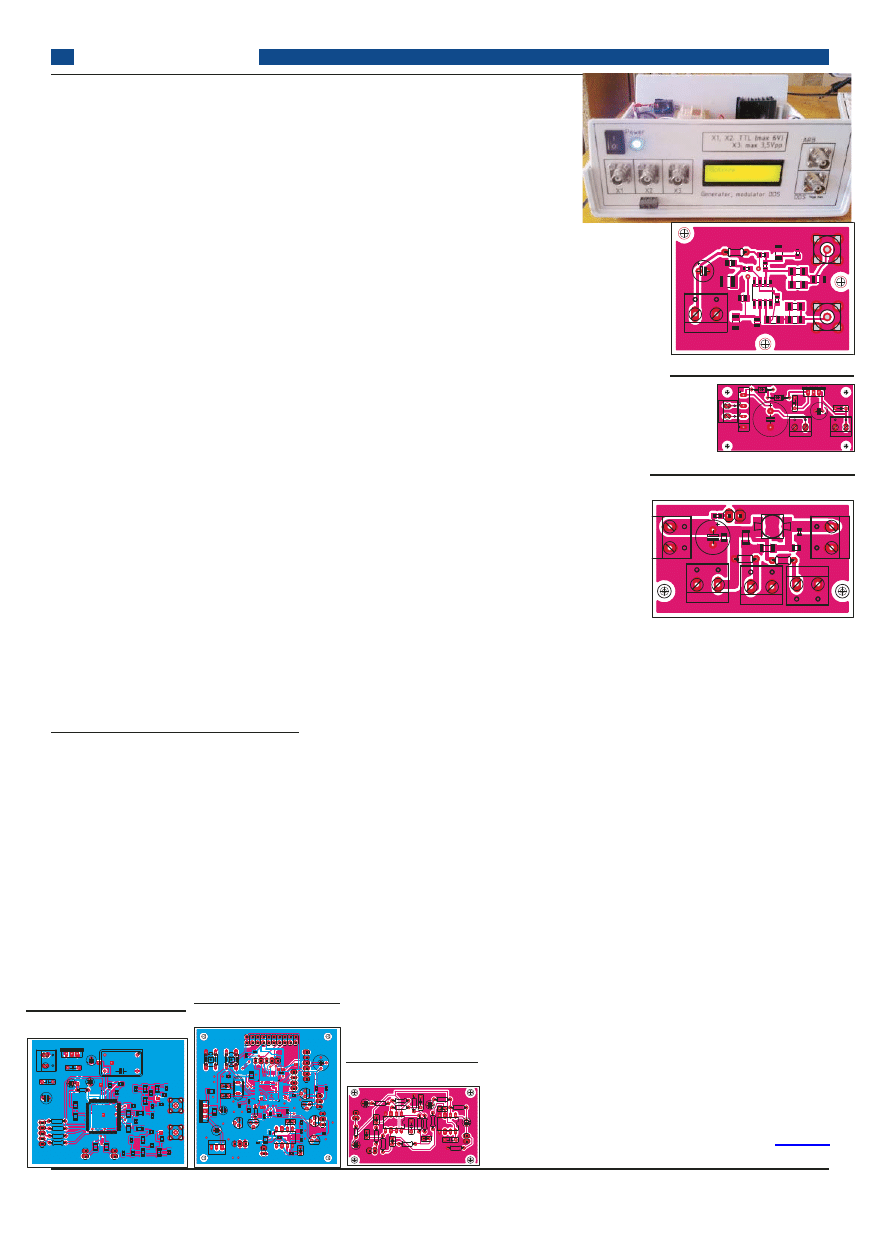

Blok syntezy DDS został zmontowany na

płytce pokazanej na rysunku 12. Płytka zo-

stała wykonana w programie Eagle. Ze wzglę-

du na dużą liczbę połączeń oraz elementów

SMD płytka zawiera dwie warstwy. Takie roz-

wiązanie jest także korzystniejsze ze względu

na możliwość umieszczenia kondensatorów

fi ltrujących zasilanie możliwie blisko układu

AD9854. Niweluje się przez to indukcyjno-

ści doprowadzeń, co ma oczywiście wpływ

na efektywność fi ltracji napięcia zasilającego

układ. Sam układ syntezy DDS występuje w

obudowie TQFP80. Został on przylutowany

z wykorzystaniem pasty lutowniczej oraz lu-

townicy kolbowej.

Większość elementów zastosowanych do

budowy układu to elementy do montażu po-

wierzchniowego. Użycie tej technologii pro-

dukcji elementów było podyktowane dużą

częstotliwością pracy układu. Zastosowanie

elementów przewlekanych w tego typu ukła-

dach nie jest zalecane ze względu na parame-

try szczątkowe, głównie indukcyjności do-

prowadzeń kondensatorów oraz rezystorów.

W miejsce kondensatorów elektrolitycznych

można zastosować kondensatory tantalowe,

ewentualnie kondensatory elektrolityczne o

niskiej rezystancji ekwiwalentnej ESR. Nie

jest to bezwzględnie konieczne ze względu

na to, iż typowe kondensatory elektrolityczne

pracują poprawnie do kilkudziesięciu kHz (w

zależności od producenta oraz pojemności).

Powyżej tej częstotliwości fi ltrację przejmują

kondensatory stałe.

Podczas pracy w zakresie najwyższych

częstotliwości (100MHz–120MHz) układ

AD9854 grzeje się dość mocno. W celu po-

prawienia chłodzenia tego elementu zastoso-

wano dodatkowy mały radiator aluminiowy

doklejony do obudowy. Radiator został także

zamontowany na stabilizatorze napięcia LDO.

Moc strat wydzielana na tym elemencie w naj-

gorszym przypadku wynosi ok. 1,5W.

Gniazda FSK oraz S-K zostały umiesz-

czone na przednim panelu urządzenia. Wy-

korzystano wygodne i trwałe gniazda typu

BNC, które umożliwiają podpięcie generatora

sygnałowego i innych urządzeń. Gniazda X2

oraz X3 na płytce syntezy DDS zostały zapro-

jektowane jako gniazda SMA, ale ze względu

na wysoki koszt tych gniazd oraz konieczność

stosowania przewodów połączeniowych z

wtykami SMA zrezygnowano z ich montażu

i połączenia wykonano przewodem koncen-

trycznym oraz skrętką. Gniazdo X3 zostało

połączone przewodem koncentrycznym BNC

50Ω z płytką wzmacniacza-bufora wyjścio-

wego syntezy DDS. Gniazdo X2 (wyjście

przebiegu generatora arbitralnego) zostało po-

łączone parą skręconych przewodów z płytką

fi ltru i wzmacniacza wyjściowego. Gniazdo

X1 służy do podłączenia napięcia zasilania.

Jest to typowe gniazdo śrubowe ARK. Całą

płytka została przykręcona do większej płyt-

ki laminatu miedziowego w celu zapewnienia

stabilnej konstrukcji mechanicznej.

Moduł z mikroprocesorem zmontowany zo-

stał na płytce pokazanej na rysunku 13. Gniaz-

do opisane jako DDS służy do połączenia syg-

nałów sterujących z płytką syntezy DDS. Po-

łączenie to wykonano przewodem taśmowym.

Podobnie połączono wyświetlacz LCD

(złącza CTRL oraz DATA). Sterowanie

odbywa się w trybie 4-bitowym, dlatego

linia danych

(DATA) ma

tylko 4 prze-

wody. Gniaz-

do JTAG to

dwie listwy

goldpin 1x10.

P o z o s t a ł e

gniazda zostały

wyprowadzone

na panel czoło-

wy urządzenia,

wejście sygna-

łu modulują-

cego MODIN

jako gniazdo

BNC, służące

do podłączenia źródła

sygnału modulującego;

wejście i wyjście da-

nych cyfrowych (D_IN,

D _ O U T )

jako złącza

ś r u b o w e

A R K 3 .

Cała płyt-

ka została

p r z y k r ę -

cona do

w i ę k s z e j

płytki lami-

natu miedziowego w celu zapewnienia stabilnej

konstrukcji mechanicznej.

Filtr generatora arbitralnego. Układ zmon-

towano na płytce pokazanej na rysunku 14.

Wszystkie zastosowane elementy to elementy

do montażu przewlekanego (w układzie nie

występują częstotliwości wyższe niż 30kHz).

Ze względu na prosty układ oraz niewielką

liczbę połączeń płytka została wykonana jako

jednowarstwowa, metodą termotransferu z

warstwą opisową po stronie elementów. Po

lutowaniu strona lutowania została pokryta

warstwą lakieru izolującego w celu minima-

lizacji utleniania się miedzi. Gniazdo JP2 to

gniazdo wejściowe fi ltru, zostało ono połączo-

ne z gniazdem wyjściowym X2 płytki synte-

zy DDS za pomocą skrętki. Gniazdo JP1 to

gniazdo wyjściowe. Na jego wyjściu wystę-

puje odfi ltrowany przebieg podany na wejście

JP2. Gniazdo to zostało wyprowadzone na

panel czołowy jako gniazdo BNC. Połączenie

między płytką a tym gniazdem wykonano za

pomocą skrętki. Gniazdo ZAS służy do podłą-

czenia napięcia zasilania.

Bufor TSH330. Układ zmontowano na płytce

pokazanej na rysunku 15. Płytka modelowa

została wykonana metodą termotransferu.

Kondensatory fi

ltrujące zasilanie zostały

umieszczone możliwie najbliżej układu sca-

lonego IC1 (efektywność fi ltracji napięcia

zasilania).

Rys. 12 Skala 50%

20

Projekty AVT

Elektronika dla Wszystkich

Maj 2010

Maj 2010

C1

C2

R2

R4

C5

C6

C7

C8

C9

C10

C13

C14

R10

R1

1

1

1

2

-

I

O

US1

L1

FSK

R1

S-K

R3

C3

R5

R6 R7

C4

QG1

C1

1

C12

C15

C16

R8

R9

C17

C18

L2

L3

L4

L5

L6

L7

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

CO

N

X1

IC1

C33

C34

C35

C36

R12

R13

R14

R15

X2

X3

Rys. 13 Skala 50%

100n

100n

10n

10n

1u

1u

47k

100n

4.

7k

10n

100n

470

10k

10k

10k

100n

100n

47

0

C1

C2

C4

C8

C3

C5

R3

C12

R13

C16

C21

R17

R20

R21

R23

C23

C24

R26

-

IO

1

2

34

2

3

1

1

2

3

1

2

3

4

2 3

1

2

31

2

31

2 3

1

IC1

C6

Q1

C9

C10

IC2

C13

C14

C15

X1

JTAG

S1

C7

C1

1

R2

R4

R5

T1

T2

R1

R6

R7

R8

RS232

L1

DA

TA

CTRL

R9

IC

3

R10

R1

1

R12

C17

C18

C19

R14

R15

C20

R16

MO

D

IN

S2

T3

T4

R18

R19

D_IN

DDS

T5

T6

R22

R24

R25

D_O

UT

C22

C25

AT91SAM7S64

100n

16M

Hz

10p

10p

220u

47u

100n

zas

10n

1n

47k

47k

47k

BC547B

BC557

1.

5k

4.7k

1.

5k

1.5k

100u

10k

NE5534

22k

10k

4.7k

4.

7n

4.7n

1n

47k

47k

100n

47k

BC547B

BC547B

4.

7k

4.

7k

BC547B

BC547B

10k

1.

5k

1.

5k

100n

10n

IC

1

IC

2

R1

R2

R3

C1

R4

C2

R5

R6

R7

C3

C4

C5

R8

R9

C6

R10

C7

R11

R12

C8

JP1

JP2

C9

R13

ZAS

C10

C11

L1

C12

NE5532N

NE5532N

10k

10k

100k

100n

6.

8k

2.

2n

6.

8k

10k

100k

2.2n

470p

100p

2,2k

2.2k

10u

6.

8k

1n

10k

10k

10u

10u

100k

100n

47u

100u

100n

Rys. 14 Skala 50%

THS330

220

100

1u

10n

51

470

470

1.

5k

100n

100n

51

100n

*

100n

10n

1n

*

IC

1

R1

R2

C1

C2

R3

R4

R5

R6

C3

C4

R7

C5

C6

C8 C9

C10

C1 1

1

2

X1

X2

C7

L1

X3

47u

100u

Rys. 15 Skala 100%

1

2

1

2

12

-

I

O

B1

X1

C1

C2

IC1

C3

C4

X2

X3

D1

D2

2200u

100n

7805

100n

220u

5V

Went

100nF

10n

470p

250u

100nF

470

10n

C1

C2

C3

L1

C6

R1

C5

1

2

12

1

2

1

2

1

2

X1

C4

LED

DDS

ARM

TSH

L2

ARB

L3

220u

100u

100u

Rys. 16 Skala 50%

Rys. 17 Skala 100%

stotliwość rezonansowa, a tym samym pobie-

rany prąd, będzie ulegał niewielkiej zmianie.

Przedstawiona nagrzewnica była zasilana

z autotransformatora o mocy maksymalnej

1kW i taką moc udało mi się wykorzystać.

Tranzystory sterujące przy takim chłodzeniu

nie grzały się mocno, co świadczy o możli-

wości dalszego zwiększenia mocy. Niestety,

ponieważ nie posiadam autotransformatora o

większej mocy, nie mogłem tego sprawdzić

w praktyce.

Warto podkreślić, że niezalecane jest

uruchamianie nagrzewnicy bezpośrednio z

sieci, przy pominięciu auto-

transformatora. Podczas jej

włączenia następuje silny

impuls prądowy, który przy

podaniu napięcia 230V może

uszkodzić tranzystory steru-

jące. Stopniowe zwiększa-

nie napięcia wyjściowego

pozwala na bieżąco kontro-

lować pobierany prąd i eli-

minuje ryzyko uszkodzenia

urządzenia.

Na załączonych fotogra-

fiach zaprezentowano przykła-

dy nagrzewanych przedmio-

tów. Nawet tak duże elementy

jak śruby o średnicy 20mm

rozgrzewają się do czerwoności w przecią-

gu jedynie kilku sekund. Niektóre ze zdjęć

przedstawiają pierwszą wersje nagrzewnicy w

innej obudowie i ze spiralą wykonaną z drutu

miedzianego.

Na zakończenie chciałbym ostrzec wszyst-

kich, którzy zechcą zbudować taką nagrzew-

nicę. Urządzenie jest zasilanie bez separacji

galwanicznej od sieci, co stwarza niebez-

pieczeństwo porażenia. Z tego względu

zarówno przy budowie, jak i uruchamianiu

należy zachować szczególną ostrożność.

Łukasz Plis

23

23

Projekty AVT

Elektronika dla Wszystkich

Maj 2010

Maj 2010

Uwaga! Podczas uruchamiania i użyt-

kowania układu w jego obwodach wystę-

pują napięcia groźne dla życia i zdrowia.

Osoby niedoświadczone i niepełnoletnie

mogą wykonać je wyłącznie pod kierun-

kiem wykwalifikowanego opiekuna, na

przykład nauczyciela.

Rezystory

R1 . . . . . . . . . . . . . . . . . . . . . . . 18kΩ

R2,R3 . . . . . . . . . . . . . . . . . . . . .15Ω

R4 . . . . . . . . . . . . . . . . . . . . . . 1,5kΩ

R5,R6 . . . . . . . . . . . . . . . . . 10Ω/5W

R7 . . . . . . . . . . . . . . . . . . . . . . . 47kΩ

PR1 . . . . . . . . . . . . . . . . . . . . . 100kΩ

Kondensatory

C1 . . . . . . . . . . . . . . . . . . 10μF/400V

C2 . . . . . . . . . . . . . . . . . . . . . . 100μF

C3,C4 . . . . . . . . . . . . . . . . 2,2nF/2kV

C5,C6 . . . . . . . . . . . . . . . . 4μF/400V

C7 . . . . . . . . . . . . . . . . . . . . 1000μFV

Półprzewodniki

D1 . . . . . . . . . . . . . . . . . . . . . UF4001

D2,D3 . . . . . . . . . . . . . . . . . . . . . LED

D4 . . . . . . . . . . . . . . . . . . . . . 1N4148

M1. . . . . . . . . . . . . . . . . . mostek 50A

T1,T2. . . . . . . . . . . . . . . IFRPS40N60

U2 . . . . . . . . . . . . . . . . . . . . . .IR2153

Pozostałe

C,L,L1 . . . . . . . . . . . . . .* - patrz tekst

Z1,Z2. . . . . . . . . . . . . . . . . . . . . ARK2

Z6 . . . . . . . . . . . . . . . . . . . ARK2 mały

Wykaz elementów

Płytka drukowana jest do stęp na

w sie ci han dlo wej AVT ja ko kit szkol ny AVT-2940.

Wszystkie elementy poza

gniazdem śrubowym ARK2,

kondensatorem elektroli-

tycznym C7 oraz dławikiem

L1 to elementy SMD, co

jest oczywiście zrozumi-

ale ze względu na zakres

częstotliwości, w jakich

pracuje ten układ. Blok bu-

fora został połączony z płytką

syntezy przewodem kon-

centrycznym 50Ω RG58U.

Połączenie z gniazdem BNC

X3 także wykonano tym

samym przewodem. Każdą

linię transmisyjną pomiędzy

buforem a obciążeniem (rezystor 50Ω kanału

wejściowego oscyloskopu lub analizatora

widma) powinno się wykonywać stosownym

przewodem o impedancji 50Ω. Układ zasilany

jest napięciem 5V, podawanym na złącze X2,

pobór prądu wynosi ok. 20mA. Płytka została

przykręcona trzema śrubami M3 do większej

płytki laminatu miedziowego.

Układy zasilania. Oba układy zostały za-

montowane na płytkach pokazanych na

rysunkach 16 i 17. Jedynie dioda LED została

wyprowadzona na przedni panel za pomocą

dwużyłowego przewodu. Ścieżki zasilające są

odpowiednio grube, aby zapewnić możliwie

niski spadek napięcia na ich rezystancji

oraz zminimalizować przenikanie tętnień z

sąsiednich modułów. Duża liczba konden-

satorów stałych oraz elektrolitycznych ma

zapewnić napięcie zasilania pozbawione jakie-

jkolwiek składowej zmiennej, która mogłaby

pogorszyć parametry układu. Poszczególne

bloki podpięte są w następujący sposób:

Gniazdo DDS – blok syntezy DDS.

Gniazdo ARM – blok sterownika mikroproce-

sorowego.

Gniazdo TSH – blok wzmacniacza

wyjściowego dla syntezy DDS.

Gniazdo ARB – blok fi ltru i wzmacniacza

generatora arbitralnego.

Na początku montażu warto zmontować tylko

układ sterowania oraz blok syntezy DDS.

Umożliwi to od razu sprawdzenie poprawności

działania obu płytek. Następnie można

zmontować zasilacz, stopień wyjściowy z

układem TSH330 oraz fi ltr generatora arbi-

tralnego. Do uruchomienia układu niezbędny

będzie oscyloskop oraz generator funk-

cyjny. Testowanie należy przeprowadzić od

sprawdzenia poprawności pracy samego gen-

eratora, poprzez modulacje cyfrowe, z wyko-

rzystaniem przebiegu prostokątnego TTL po-

dawanego na wejścia FSK, S-K, kończąc na

modulacjach analogowych (przebieg sinusoi-

dalny, muzyka itp.) – złącze MODIN.

Test zmontowanego urządzenia przeprowadza

się poprzez sprawdzenie obecności zadanych

sygnałów na wyjściach urządzenia. Do syn-

chronizacji oscyloskopu z urządzeniem można

wykorzystać złącze oznaczone jako D_OUT,

pozwoli ono zaobserwować skomplikowane

sygnały np. 16-QAM. Oscyloskop powin-

ien wtedy pracować w trybie single-trigger z

wyzwalaniem ze złącza D_OUT.

Rafał Stępień

Moduł DDS

R1-R4 . . . . . . .33kΩ 1206

R5 . . . . . . . . . 4,7kΩ 0805

R6 . . . . . . . . . . .1kΩ 0805

R7 . . . . . . . . . 220Ω 0805

R8-R11 . . . . . . 51Ω 1206

R12-R15 . . . . . . . . .2,2kΩ

C1-C8 . . . . . . . 10nF 0805

C9,C10 . . . . . .2,2nF 0603

C11-C14 . . . . 100nF 1206

C15,C16,C36. . . . .47μF/16V

C17 . . . . . . . . 4,7μF 1206

C18 . . . 220nF+100nF 1206

C19-C26 . . . . . 22pF 0805

C27,C30 . . . . .4,7pF 0805

C28,C31 . . . . .6,8pF 0805

C29,C32 . . . . . 10pF 0805

C33,C35 . . . . . . . . .100nF

C34 . . . . . . . . . 220μF/16V

IC1 . . . . . . . TC1264 3.3V

US1. . . . . . . . . . . AD9854

L1 . . . . . . . . . . . . . 100μH

L2 . . . . . . . . . . . . . . 47nH

QG1. . . . .gen. 28,322MHz

S-K,CON,FSK. . . . . . .goldpin

X1 . . . . . . . . . złącze ARK

X2,X3. . . . . . nie montować

Filtr ARB

R1,R2,R6,R11,R12 . . . 10kΩ

R3,R7,R13. . . . . . . 100kΩ

R4,R5 . . . . . . . . . . .6,8kΩ

R8,R9 . . . . . . . . . . .2,2kΩ

R10 . . . . . . . . . . . . .6,8kΩ

C1,C10,C12. . . . . . .100nF

C2,C3 . . . . . . . . . . . 2,2nF

C4 . . . . . . . . . . . . . .470pF

C5 . . . . . . . . . . . . . .100pF

C6,C8,C9. . . . . . . . . 10μF

C7 . . . . . . . . . . . . . . . .1nF

C11 . . . . . . . . . . . . . 47μF

IC1, IC2. . . . . . . . NE5532

L1 . . . . . . . . dławik 100μH

JP1,JP2,ZAS . . . . . goldpin

Moduł procesora

R1,R7,R8,R24,R25 . . . . . .

. . . . . . . . . . . .1,5kΩ 0603

R2-R5,R14-R16. . 47kΩ 0603

R6,R12,R13,R18,R19. . . . .

. . . . . . . . . . . 4,7kΩ 0603

R9,R20-R23. . .10kΩ 0603

R10 . . . . . . . . .22kΩ 0603

R26 . . . . . . . . 470Ω 0603

C1,C2,C6,C12 100nF 1206

C15,C20-C24 . .100nF 1206

C3,C5 . . . . . . . . 1μF 1210

C4,C7,C8,C25 . . 10nF 0805

C9,C10 . . . . . . . . . . .10pF

C11,C19 . . . . . . 1nF 0603

C13 . . . . . . . . . . 220μF/16

C14 . . . . . . . . . . . 47μF/16

C17,C18 . . . . . . . . . 4,7nF

IC1 . . . . . . AT91SAM7S64

IC2 . . . . . . . TC1264 3.3V

T1,T3-T6 . . . . . . . . BC547

T2 . . . . . . . . . . . . . BC557

Q1 . . . . . .rezonator 16MHz

L1 . . . . . . . . dławik 100μH

S1,S2 . . . . . . mikroswitch

Rs232,MODIN,D_IN,D_

OUT,CTRL,DDS,

DATA,JTAG . . . . . . goldpin

X1 . . . . . . . . . złącze ARK2

Rozdzielacz

R1 . . . . . . . . . 470Ω 0603

C1,C6 . . . . . . 100nF 1206

C2,C5 . . . . . . . 10nF 0805

C3 . . . . . . . . . 470pF 0603

C4 . . . . . . . . . . . . . 220μF

L1 . . . . . . . . . . . . . 250μH

L2,L3. . . . . . . . . . . 100μH

LED . . . . . dioda LED niebieska

TSH,X1,ARM,ARB,DDS . . .

. . . . . . . . . . . złącze ARK2

TSH330

R1 . . . . . . . . . 220Ω 0603

R2 . . . . . . . . . 100Ω 0603

R3,R7 . . . . . . . 51Ω 1206

R4,R5 . . . . . . 470Ω 0603

C1 . . . . . . . . . . . 1μF 1210

C2,C9 . . . . . . . 10nF 0805

C3-C5,C8 . . . 100nF 1206

C6,C11 . . . . nie montować

C7 . . . . . . . . . . . . . . 47μF

X1,X3. . . . . .opis w tekście

X2 . . . . . . . . złącze ARK2

Zasilacz

C1 . . . . . . . . .2200μF/25V

C2,C3 . . . . . . . . . . .100nF

C4 . . . . . . . . . . . . . 220μF

D1,D2 . . . . . . . . . 1N4007

IC1 . . . . . . . . . . . . . .7805

X1-X3 . . . . . . złącza ARK2

Wykaz elementów

Płytka drukowana jest do stęp na

w sie ci han dlo wej AVT ja ko kit szkol ny AVT-2941.

Wyszukiwarka

Podobne podstrony:

2010 05 Ćwiczenie 4 Wzmacnianie sygnałów zmiennych

2010 05 R odp

2010 05 Analizator widma 70MHz część 2

2010 05 04

SERWIS 2010.05.08

2010 05 Nagrzewnica indukcyjna 1kW

2010 05 Szkoła konstruktorów klasa III

2010 05 R

2010 05 P

2010.05.31 matematyka finansowa

05.2010-05-05

2010-05-17, bezpieczeństwo publiczne

21 Wiek 2010 05 spis tresci

CERTO 2010 05 20 Standardowy

2010 05 Płytki drukowane domowa soldermaska

więcej podobnych podstron