Z jednostką centralna mikrokontrolera współpracuje układ przerwań. W mikrokontrolerach

rodziny 8051 stosuje się jeden standardowy mechanizm obsługi przerwań. Źródłem przerwań

są wydarzenia w wewnętrznych urządzeniach peryferyjnych (np. przepełnienie układu

czasowego) lub w zewnętrznym otoczeniu mikrokontrolera (zmiana stanu logicznego na

określonym wyprowadzeniu). Takie wydarzenie prowadzi do zaprzestania wykonywania

bieżącego programu i skoku do określonego miejsca w przestrzeni adresowej. Licznik

przerwań zależy od liczby i stopnia komplikacji wewnętrznych urządzeń peryferyjnych.

Nie w każdym przypadku wystąpienie przyczyny przerwania musi doprowadzić natychmiast

do przerwania bieżącego programu. Istnieją bowiem dwa warunki przejścia do obsługi

przerwania:

- przerwanie musi być dopuszczone, bowiem programista może każde przerwanie

indywidualnie dopuścić lub zablokować,

- nie jest aktualnie obsługiwane przerwanie o wyższym priorytecie.

Nadawanie priorytetów przerwaniom przez programistę w przypadku 8051 jest ograniczone i

polega tylko na możliwości zadeklarowania każdego przerwania na jednym z dwóch

poziomów priorytetów.

Różnice między układami 8051 i 80166 w zakresie normalnych przerwań:

- 80166 posiada znacznie więcej źródeł przerwań, tj. 32,

- bardziej rozbudowane możliwości ustalania przez użytkownika priorytetów przerwań,

- obsługa przerwań może nastąpić szybciej, bowiem w układzie 80166 od razu precyzyjnie

wiadomo, co jest źródłem przerwania,

Możliwa jest obsługa przerwań za pomocą zupełnie innego mechanizmu – kanałów PEC

(Peripherial Event Controler – kontroler zdarzeń peryferyjnych)

Rozwój wewnętrznych układów peryferyjnych mikrokontrolerów jest jednym

z podstawowych kierunków ich rozwoju. W strukturach pierwszych mikrokontrolerów

umieszczane były tylko podstawowe urządzenia peryferyjne: porty, łącze komunikacji

szeregowej oraz proste układy czasowe. Od tego czasu do chwili obecnej nastąpił znaczny

postęp rozwoju wewnętrznych urządzeń peryferyjnych mikrokontrolerów:

- w

strukturze

mikrokontrolera integrowano więcej urządzeń peryferyjnych,

- są to urządzenia bardziej „inteligentne”, tzn. są wstanie samoczynnie

realizować złożone funkcje bez ingerencji jednostki centralnej,

- są bardziej wyspecjalizowane.

Urządzenia peryferyjne współczesnych mikrokontrolerów można podzielić na kreślone grupy

funkcyjne.

Układy peryferyjne mikrokontrolerów

Łącza

równoległe

Ports

PCIAMCIA

Sterowniki

komunikacji

szeregowej

UART

SCC

I

2

B

CAN

Układy

czasowe

Timers

Counters

PWM

CAPCOM

RTC

Układy

nadzorujące

Watchdog

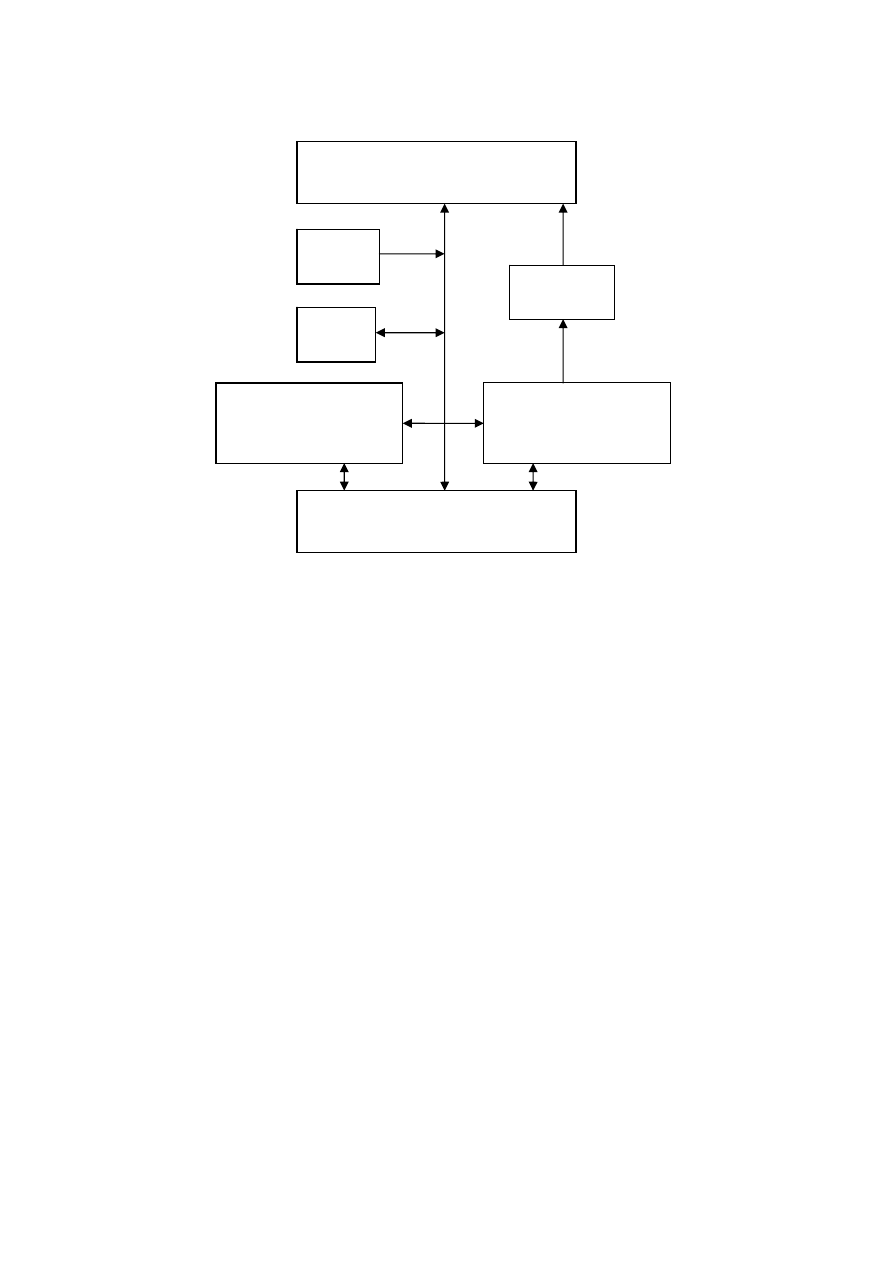

8051

Jednostka centralna 8051:

- architektura typu CISC,

- architektura akumulatorowa – tzn. niektóre rozkazy, m. in. operacje arytmetyczne,

muszą wykorzystywać jeden wyróżniony rejestr wewnętrzny o nazwie akumulator,

- możliwość wykonywania operacji na pojedynczych bitach,

- model pamięci typu Harvard (rozdzielona przestrzeń adresowa dla pamięci programu

i pamięci danych).

Wewnętrzne szyny

systemowe

jednostka centralna

pamięć

ROM

pamięć

RAM

układ

przerwań

sterownik

zewnętrznych szyn

systemowych

wewnętrzne

urządzenia

peryferyjne

porty

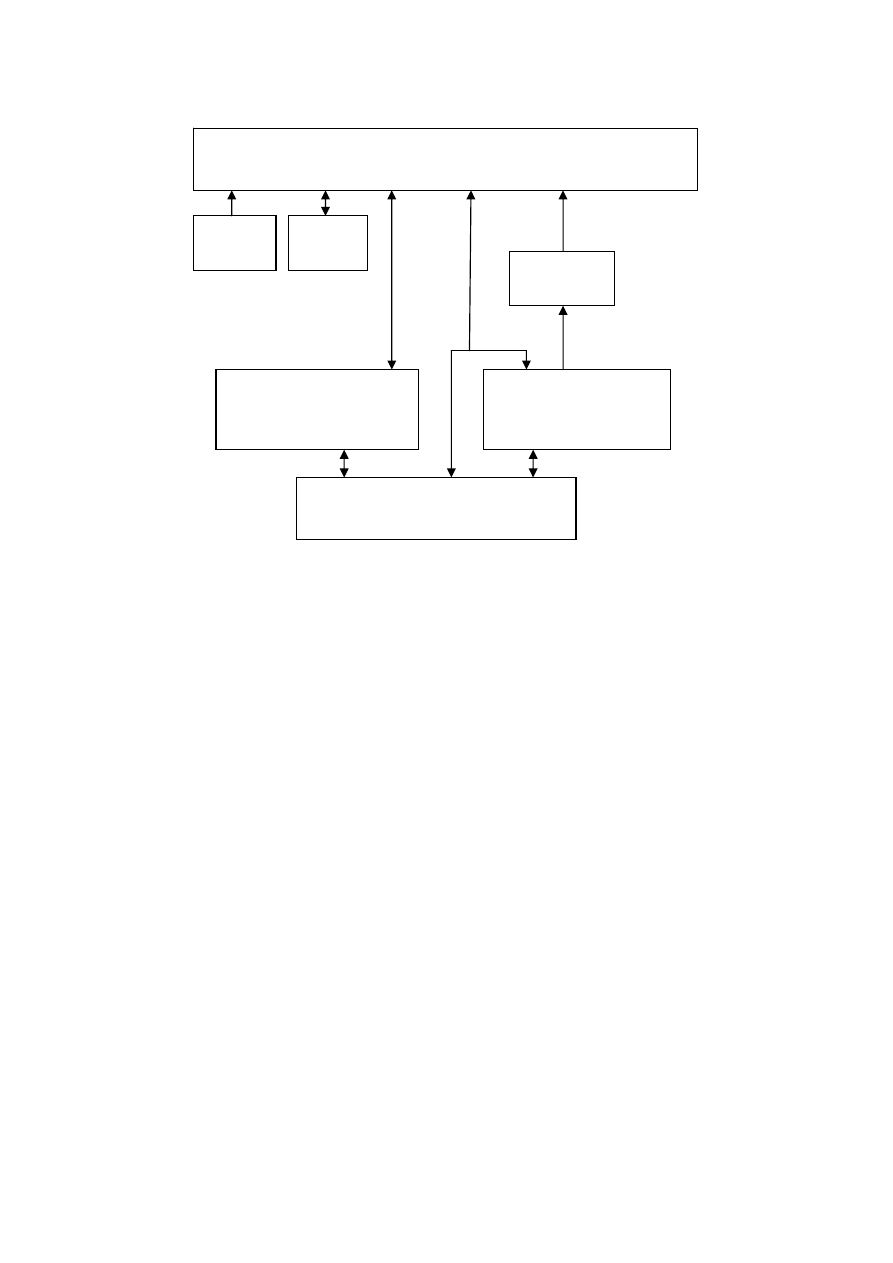

80166

Jednostka centralna 80166:

- architektura typu RISC,

- czteropoziomowa struktura potokowa,

- brak akumulatora.

Wewnętrzne szyny

systemowe

jednostka centralna

pamięć

ROM

pamięć

RAM

układ

przerwań

sterownik zewnętrznych

szyn systemowych

wewnętrzne

urządzenia

peryferyjne

porty

Wyszukiwarka

Podobne podstrony:

13 programowalny kontroler przerwan 8259

Dz Urz KGP Nr 16

CW 06 B przerw

ADA wyjatki przerw3

CHRAPEK,podstawy robotyki, Urz dzenia chwytaj ce i g owice technologiczne robotów przemys owych cz 2

Instr. kontr.urz.gaszącego, Instrukcje w wersji elektronicznej

Twórczość Kazimierza Przerwy -Tetmajera, Szkoła, Język polski, Wypracowania

Jak przerwać wykonywanie pętli (for, PHP Skrypty

projektowanie stron na urz%c4%85dzenia mobilne

przerwa

przerwan

Eksploatacja maszyn i urz dze WICHA

111-4, materiały studia, 111. WYZNACZANIE SZEROKOŚCI PRZERWY ENERGETYCZNEJ W PÓŁPRZEWODNIKU METODĄ T

kospekt12, Elektrotechnika AGH, Semestr II letni 2012-2013, Fizyka II - Laboratorium, 12 Wyznaczanie

więcej podobnych podstron