W.2_VLSI FABRICATION

TECHNOLOGY

UKŁADY

SCALONE

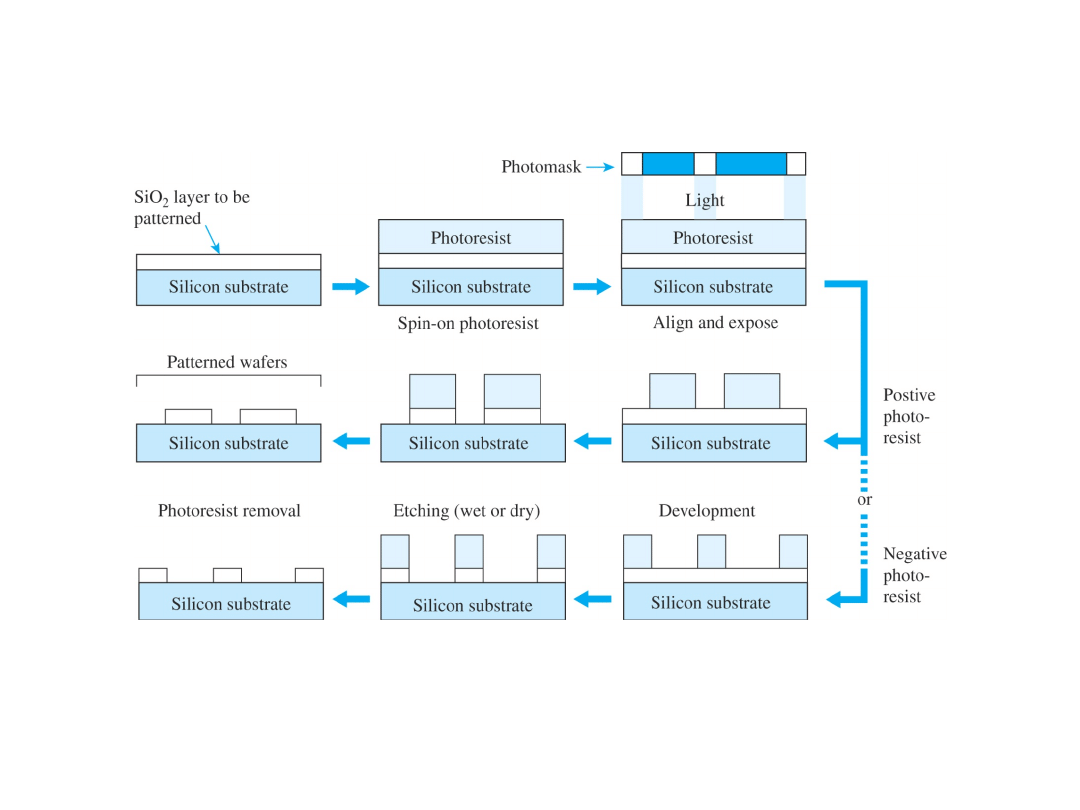

Fig.1 Photolithography using positive or negative photoresist.

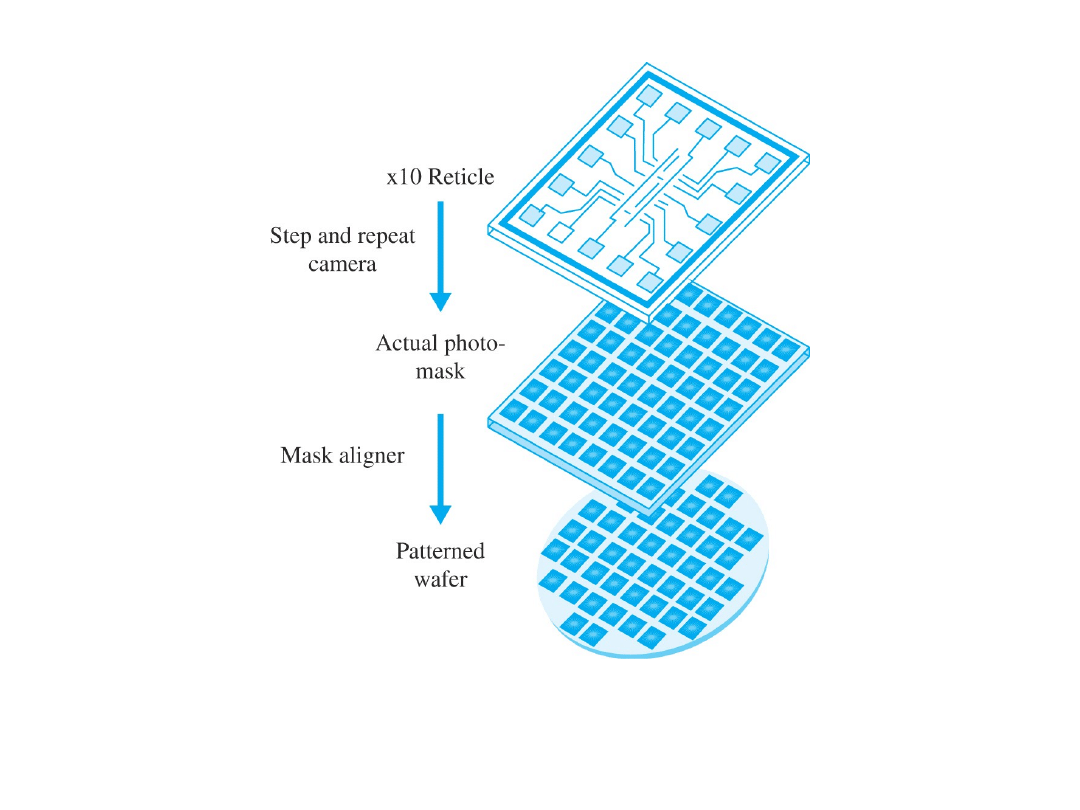

Fig.2 Conceptual illustration of a step-and-repeat reduction

technique to facilitate the mass production of integrated circuits.

Maska

pozycjonowana

w osi pionowej

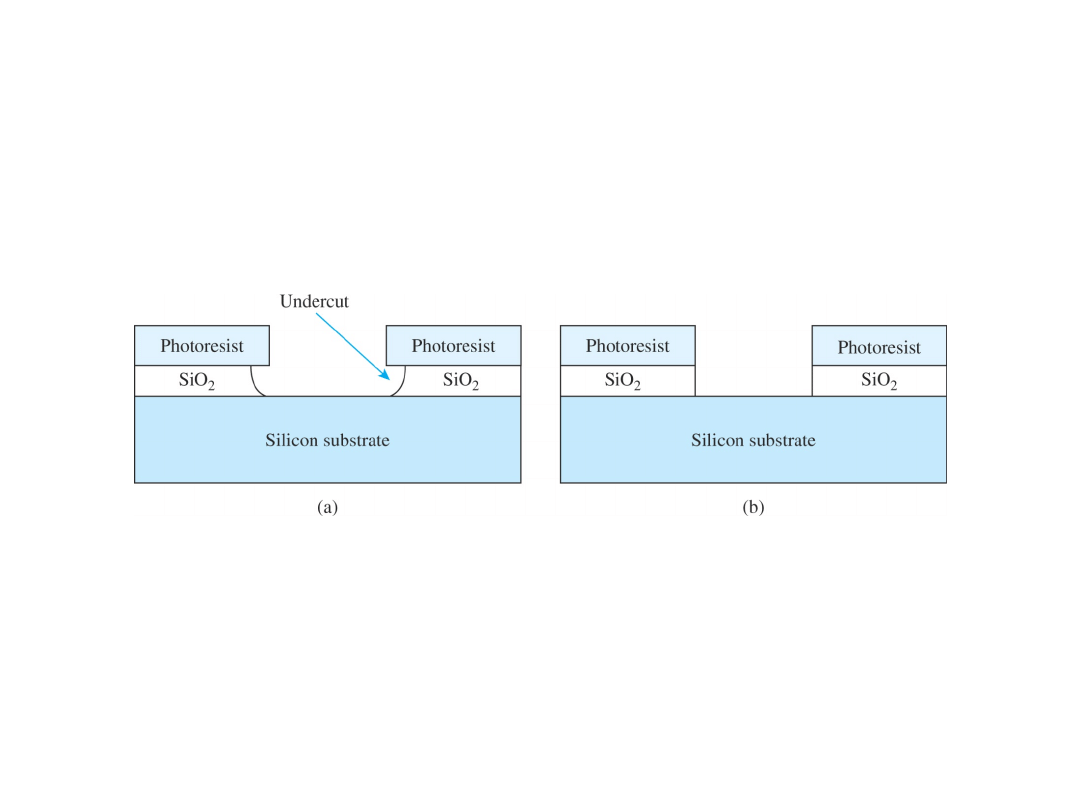

Fig.3 (a) Cross-sectional view of an isotropic oxide etch with severe

undercut beneath the photoresist layer. (b) Anisotropic etching,

which usually produces a cross section with no undercut.

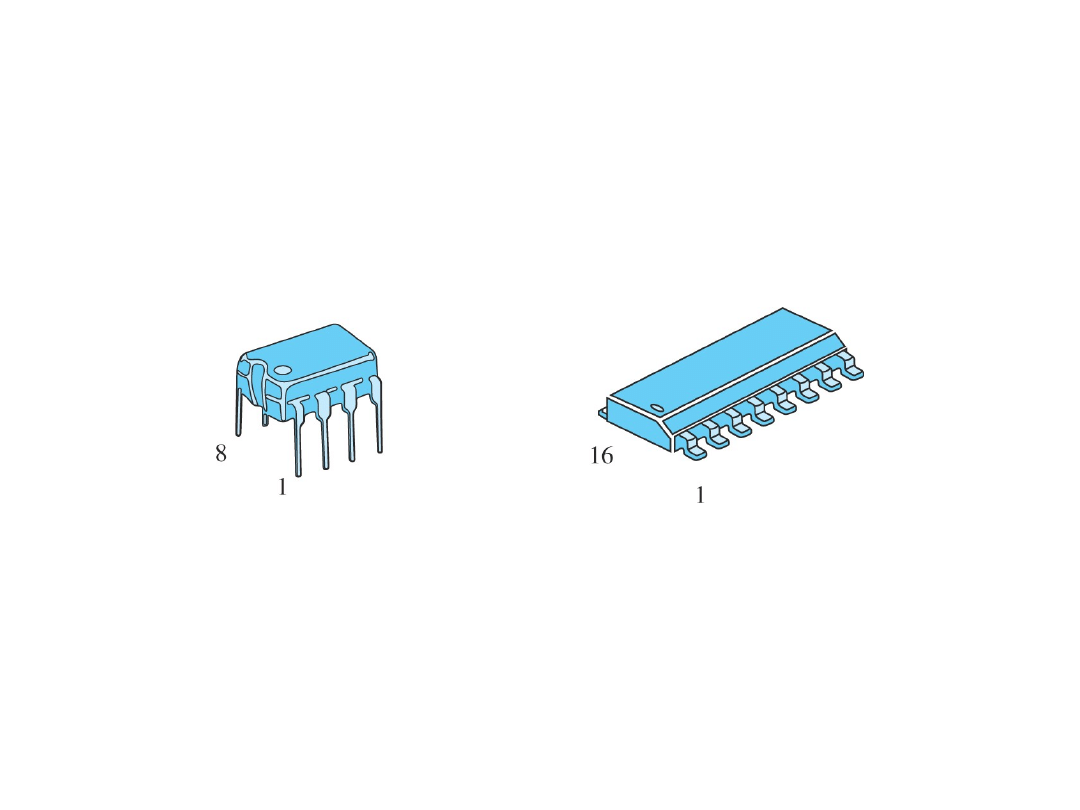

Fig.4. Examples of an 8-pin plastic dual-in-line IC package and a

16-pin surface-mount package.

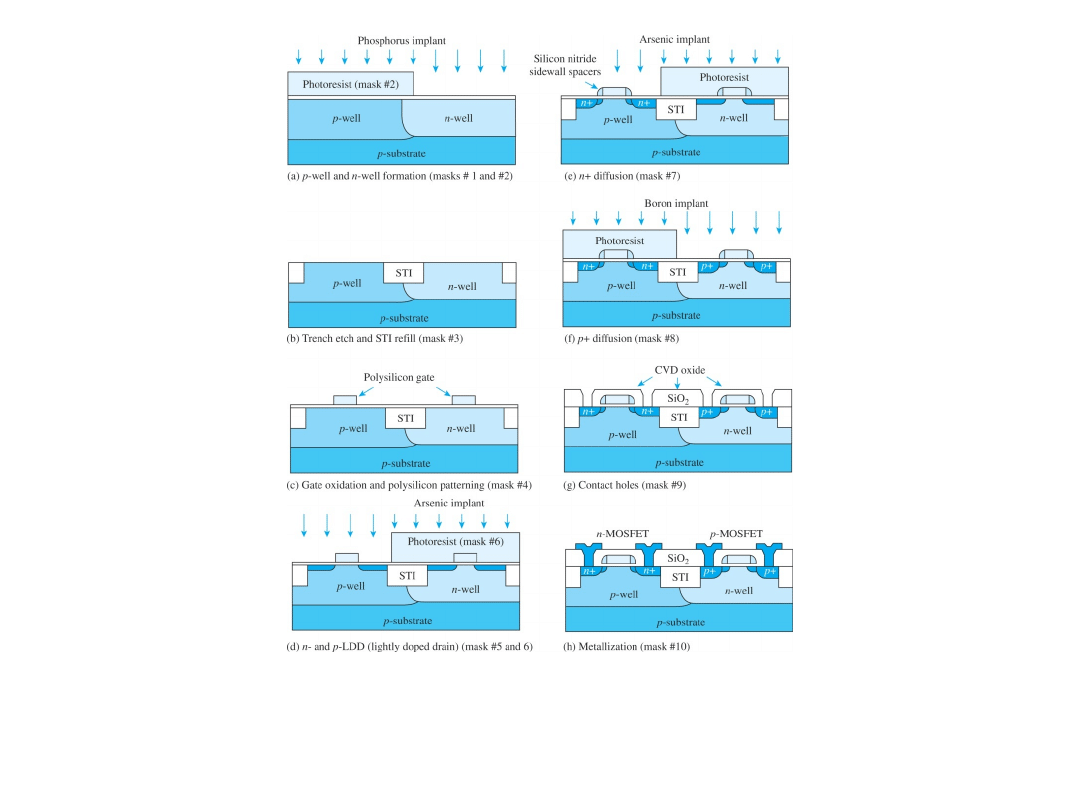

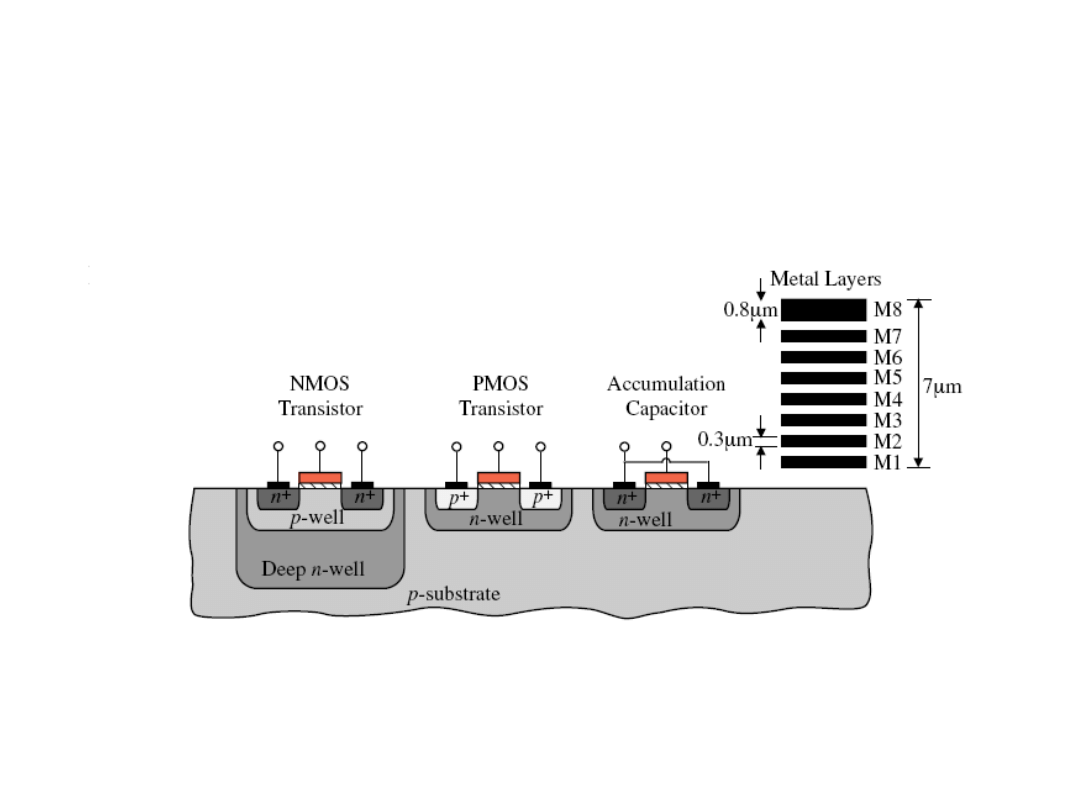

Fig.5 A modern twin-well CMOS process flow with shallow trench

isolation (STI).

Implantacja

wysokoenergetyczna

Implantacja

niskoenergetyczna

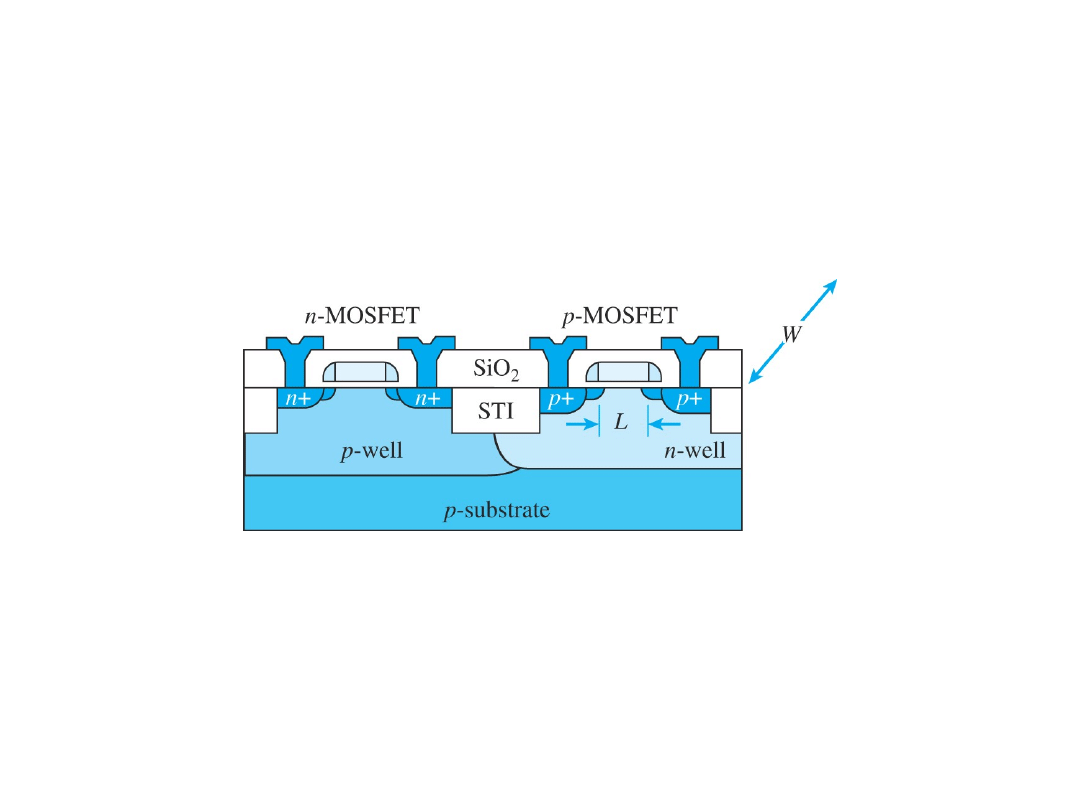

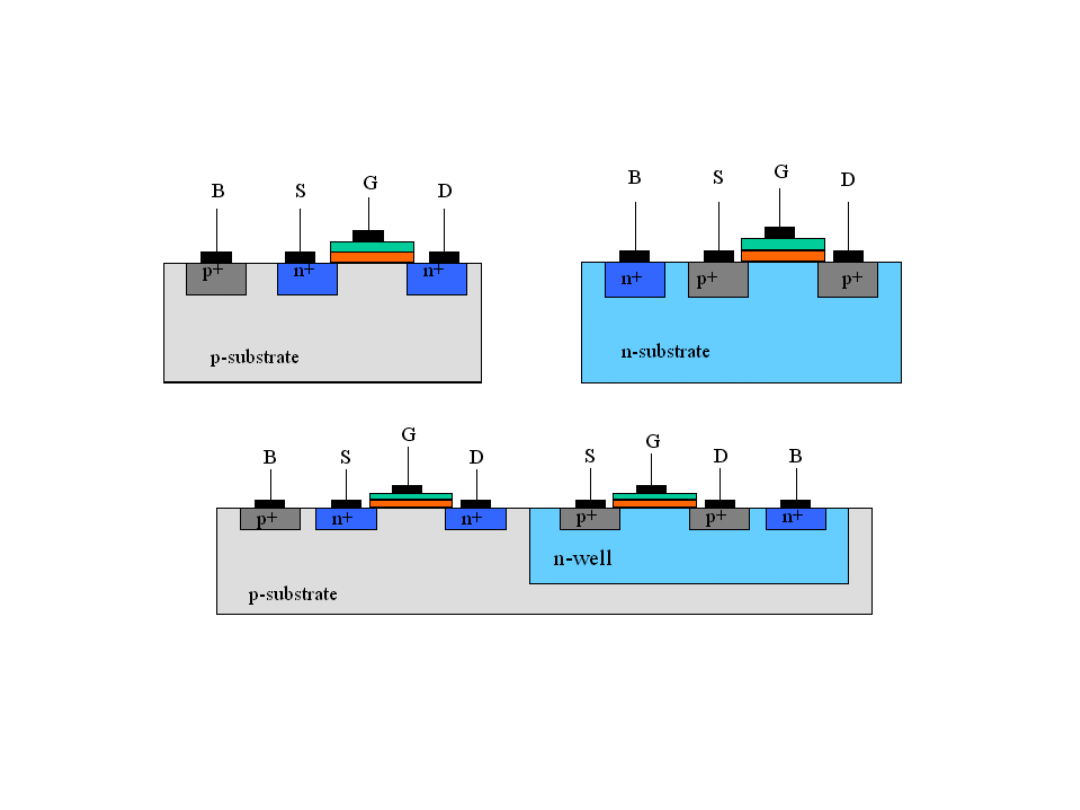

Fig.6 Cross-sectional diagram of n- and p-MOSFETs.

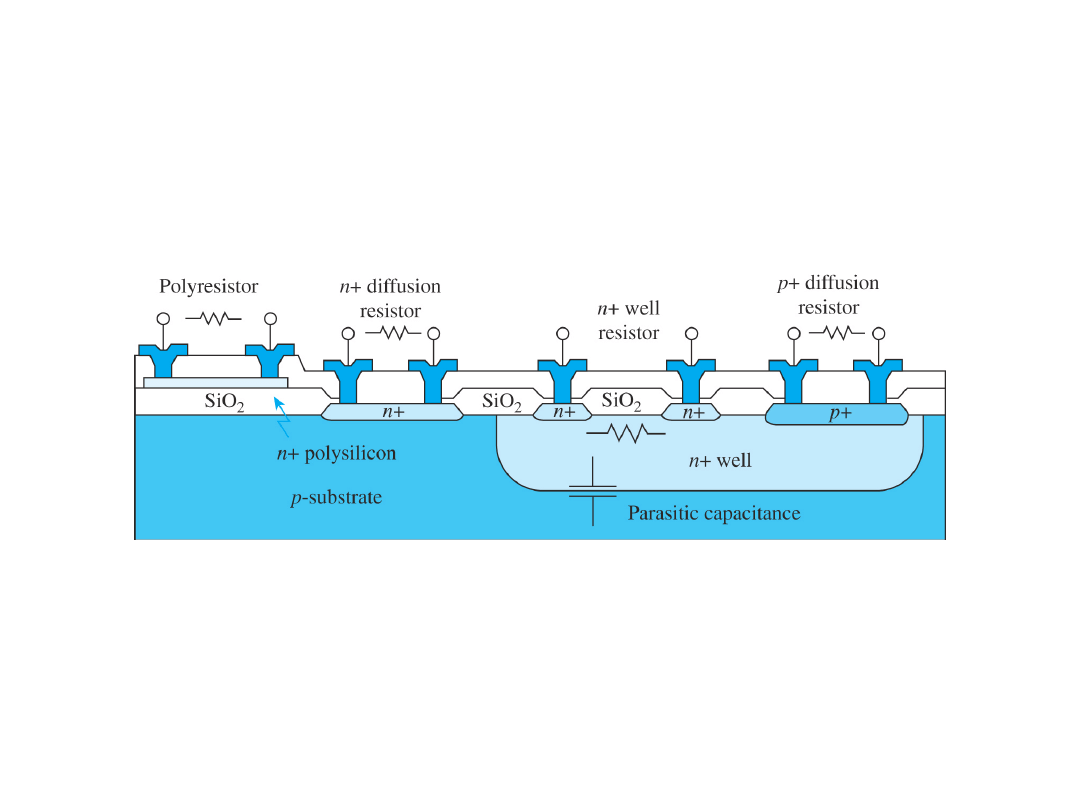

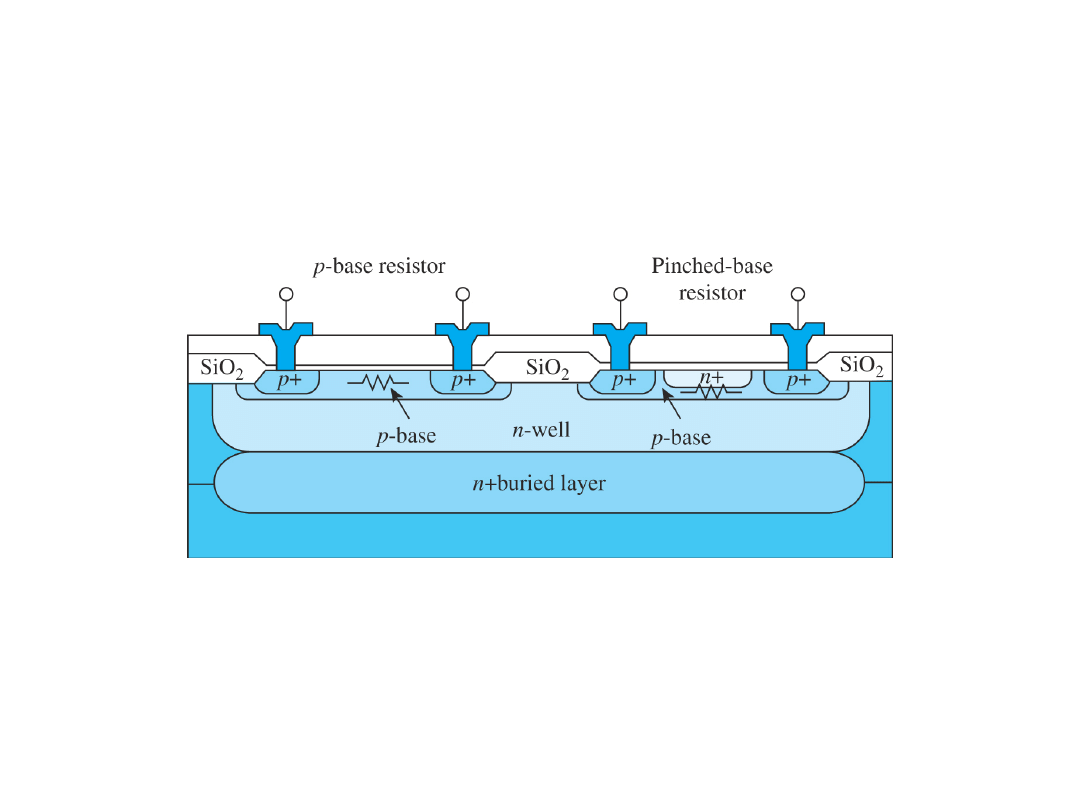

Fig.7 Cross sections of various resistor types available from a

typical

n-well CMOS process.

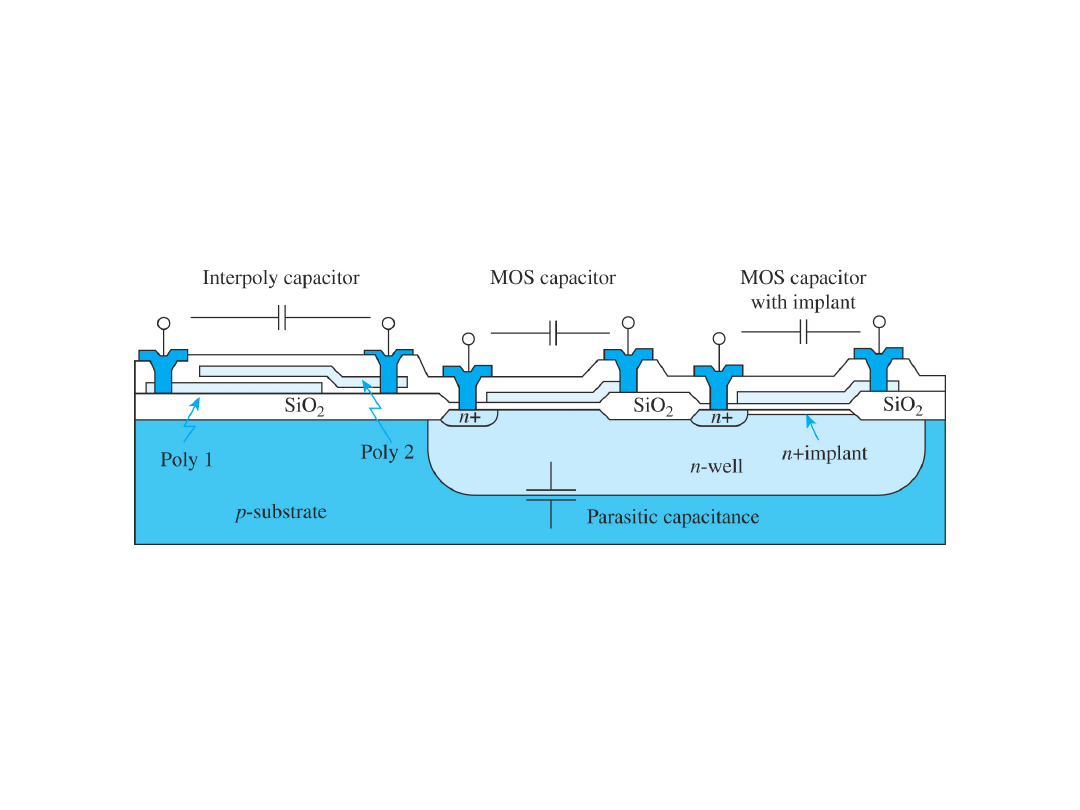

Fig.8 Interpoly and MOS capacitors in an n-well CMOS process.

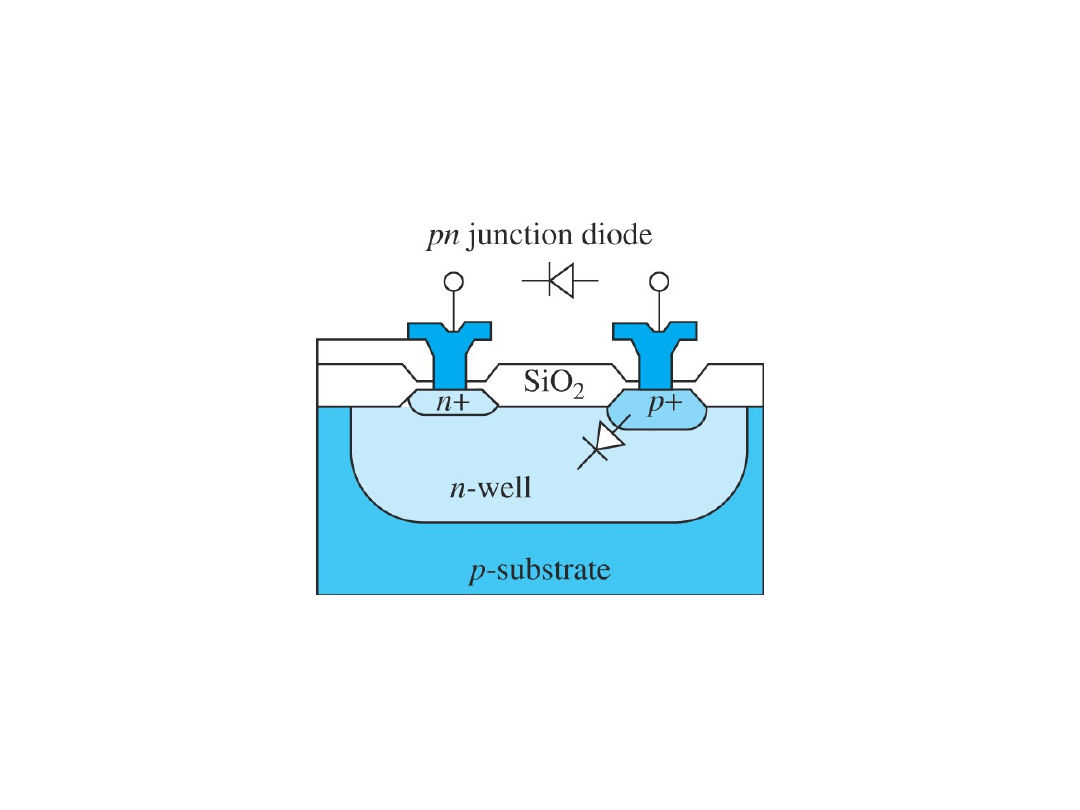

Fig.9 A pn junction diode in an n-well CMOS process.

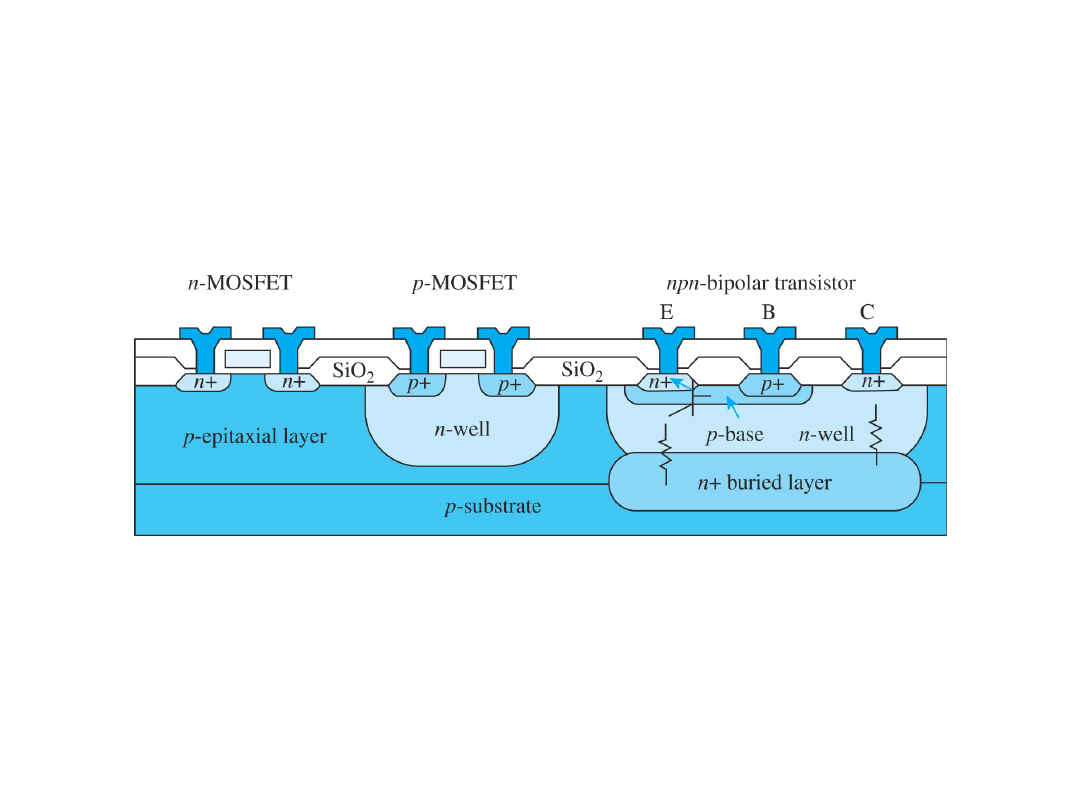

Fig.10 Cross-sectional diagram of a BiCMOS process.

Fig.11 Lateral pnp transistor.

Fig.12 p-base and pinched p-base resistors.

spłaszczony

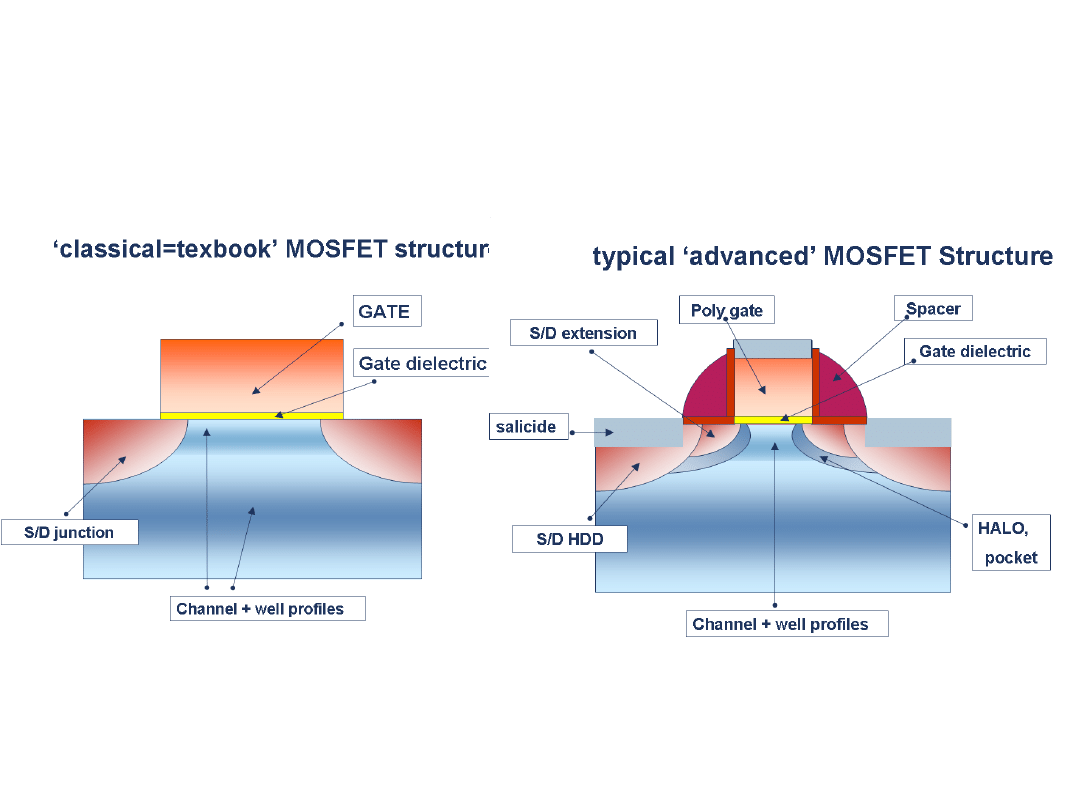

Struktury tranzystorów MOSFET:

a) z długim kanałem, b) z krótkim kanałem

Podstawowa technologia cyfrowa

Elementy we współczesnych

technologiach CMOS

Wielkosygnałowy model

tranzystora MOS

Wielkosygnałowy model Schichmana – Hodgesa

MOSFET

I

W

L

C

U

U U

U

D

ox

GS

T

DS

DS

2

2

dla U

GS

> U

T

i 0 < U

DS

< U

GS

- U

T

DS

T

GS

Dsat

U

U

U

L

W

K

I

1

2

2

'

dla U

GS

> U

T

i U

DS

> U

GS

-U

T

f

BS

f

T

T

U

U

U

2

2

0

I

I

U

BD

s

BD

T

exp

1

I

I

U

BS

s

BS

T

exp

1

I

D

K’ =

Cox - parametr transkonduktancyjny,

U

T0

- napięcie progowe przy napięciu podłoże-źródło

U

BS

=0,

- współczynnik objętościowy napięcia progowego,

- współczynnik modulacji długości kanału w [V

-

0,5

],

- potencjał powierzchniowy przy silnej inwersji

półprzewodnika

f

2

const

przy

)

(

GS

DS

D

u

u

f

i

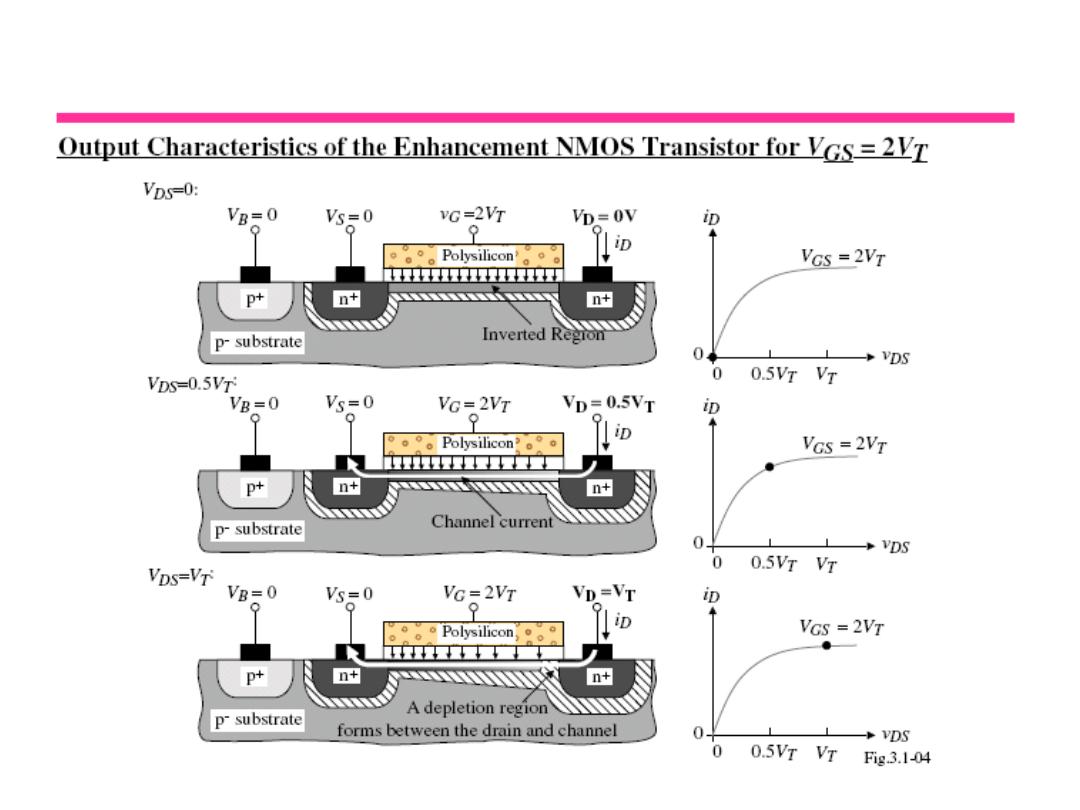

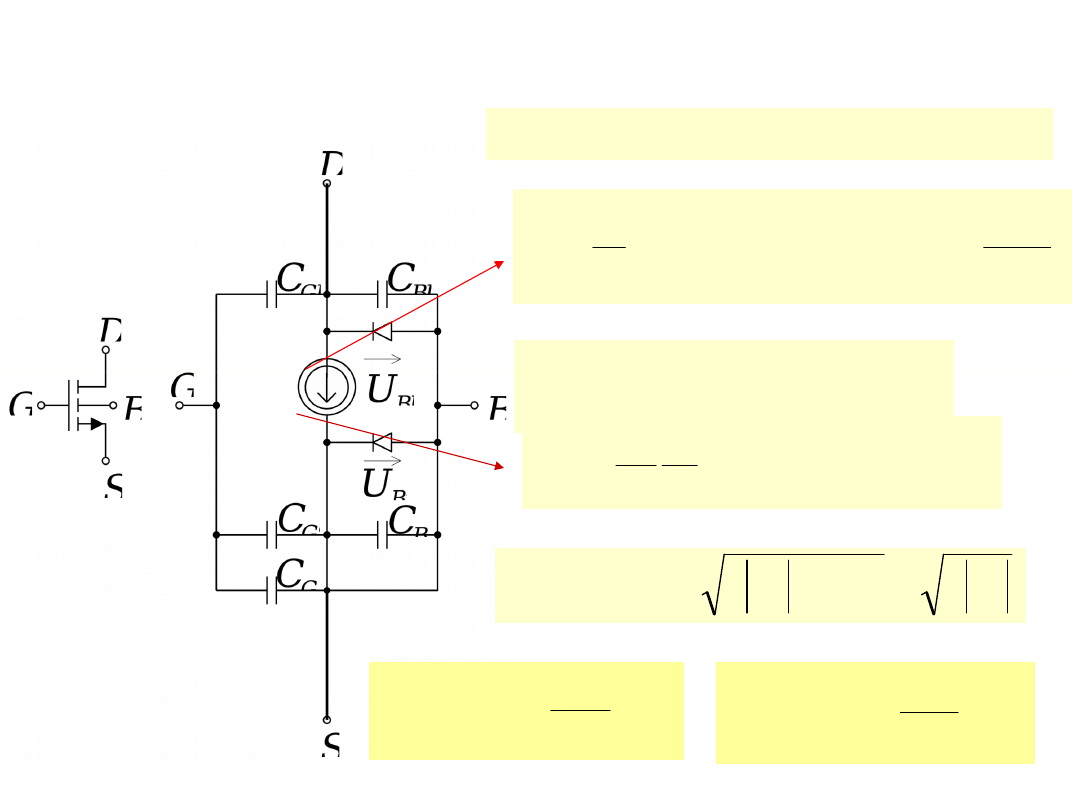

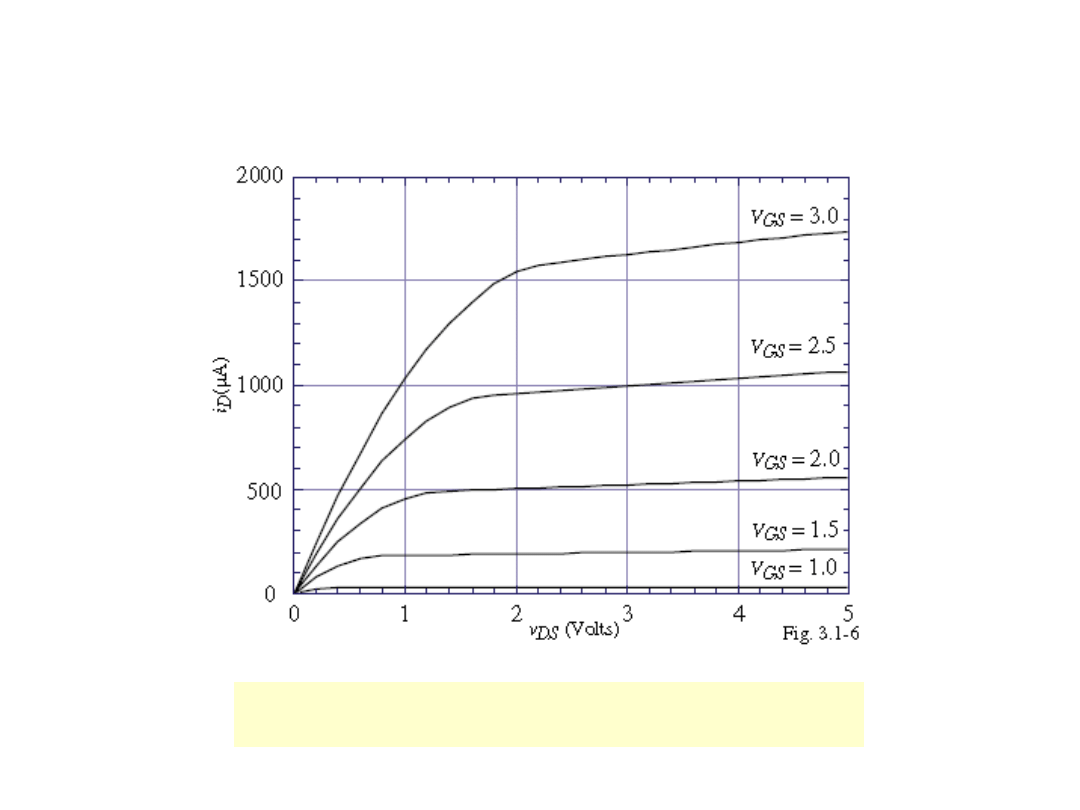

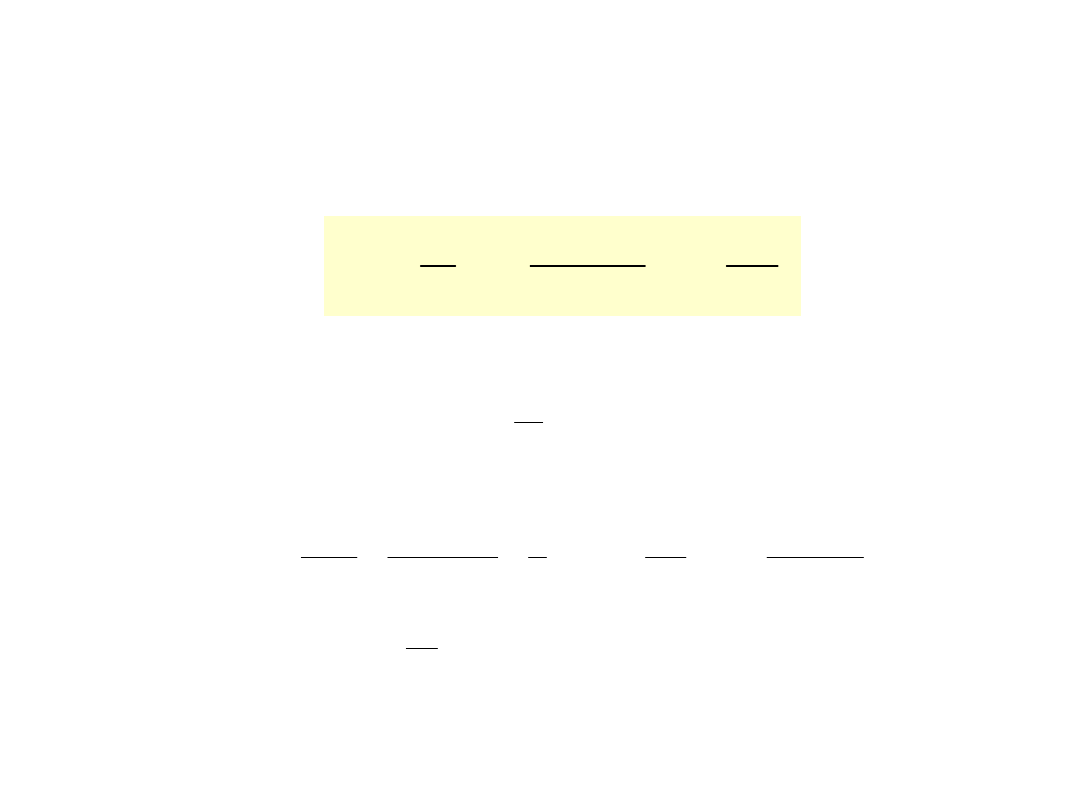

CHARAKTERYSTYKI WYJŚCIOWE

const

przy

)

(

DS

GS

D

u

u

f

i

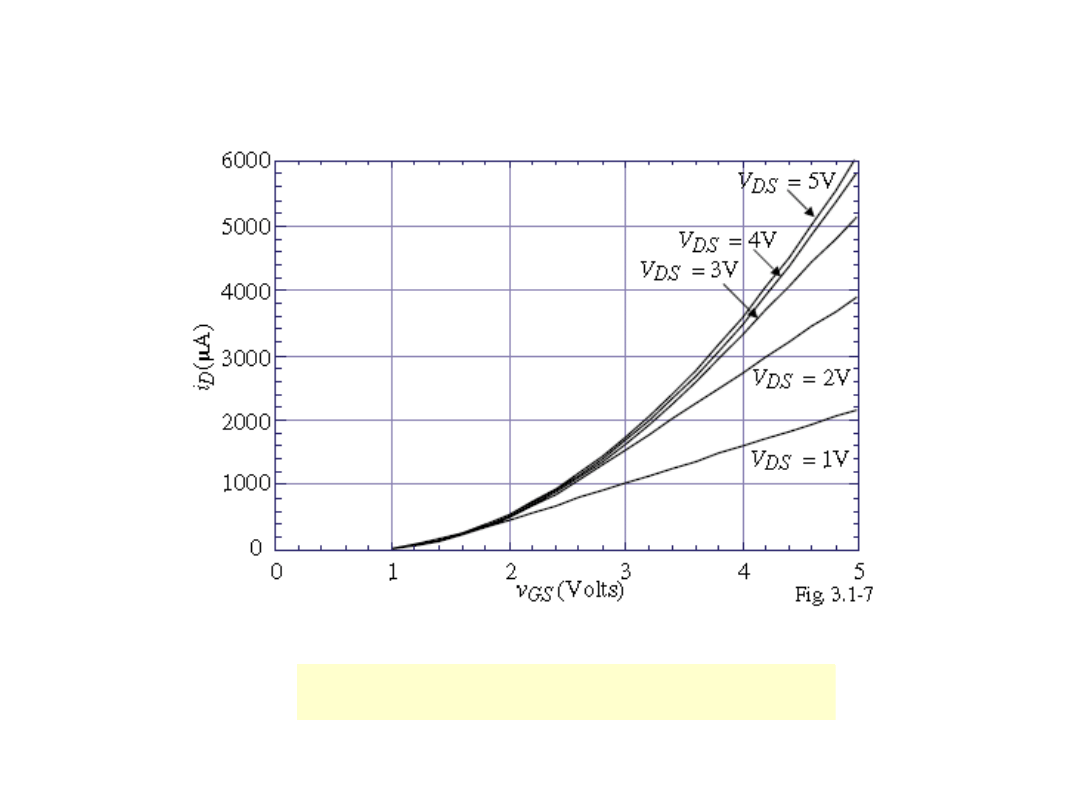

CHARAKTERYSTYKI PRZEJŚCIOWE

const

przy

)

(

BS

GS

D

u

u

f

i

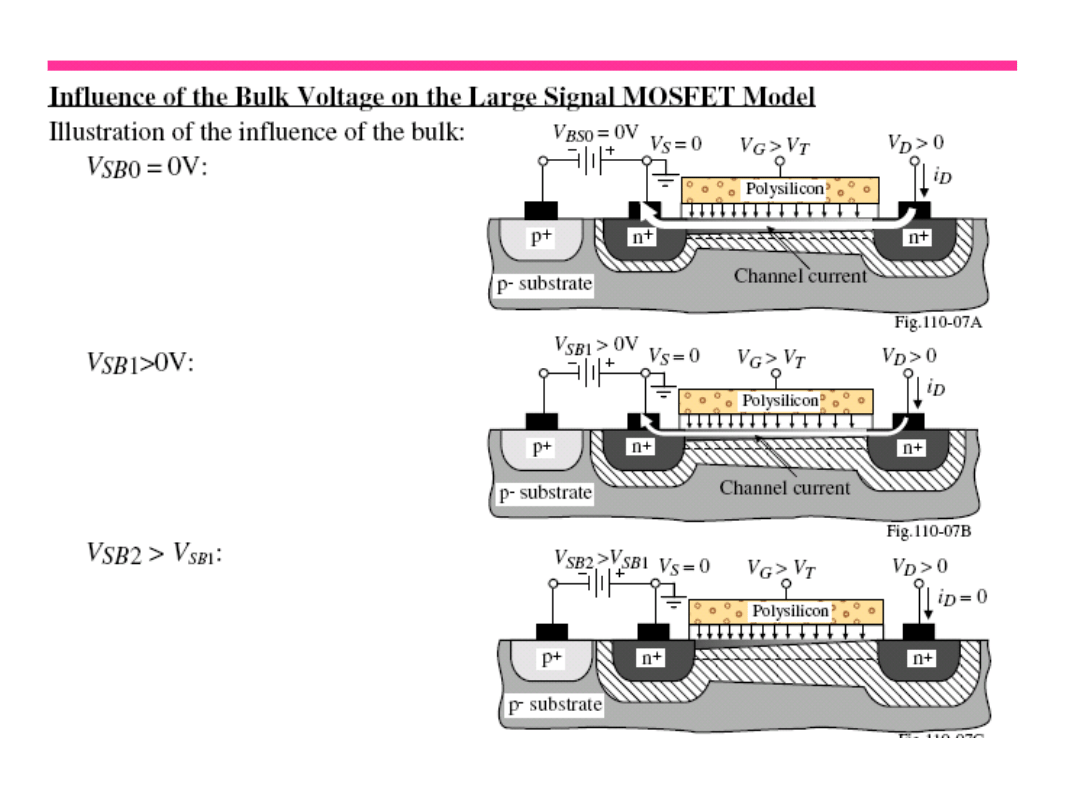

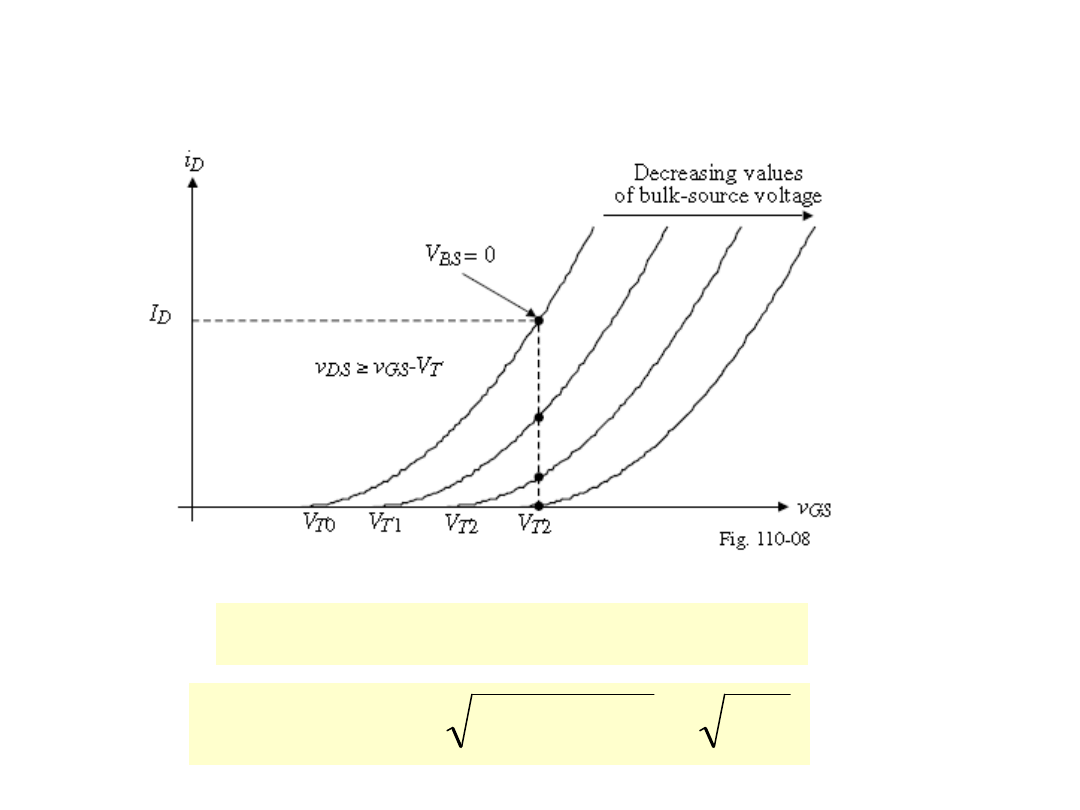

WPŁYW NAPIĘCIA PODŁOŻE – ŹRÓDŁO NA

PRĄD DRENU

U

U

U

T

T

si

BS

si

0

Charakterystyki małosygnałowe

BS

const

U

U

BS

D

DS

const

U

U

DS

D

GS

const

U

U

GS

D

D

U

U

I

U

U

I

U

U

I

I

DS

GS

BS

GS

DS

DS

;

;

;

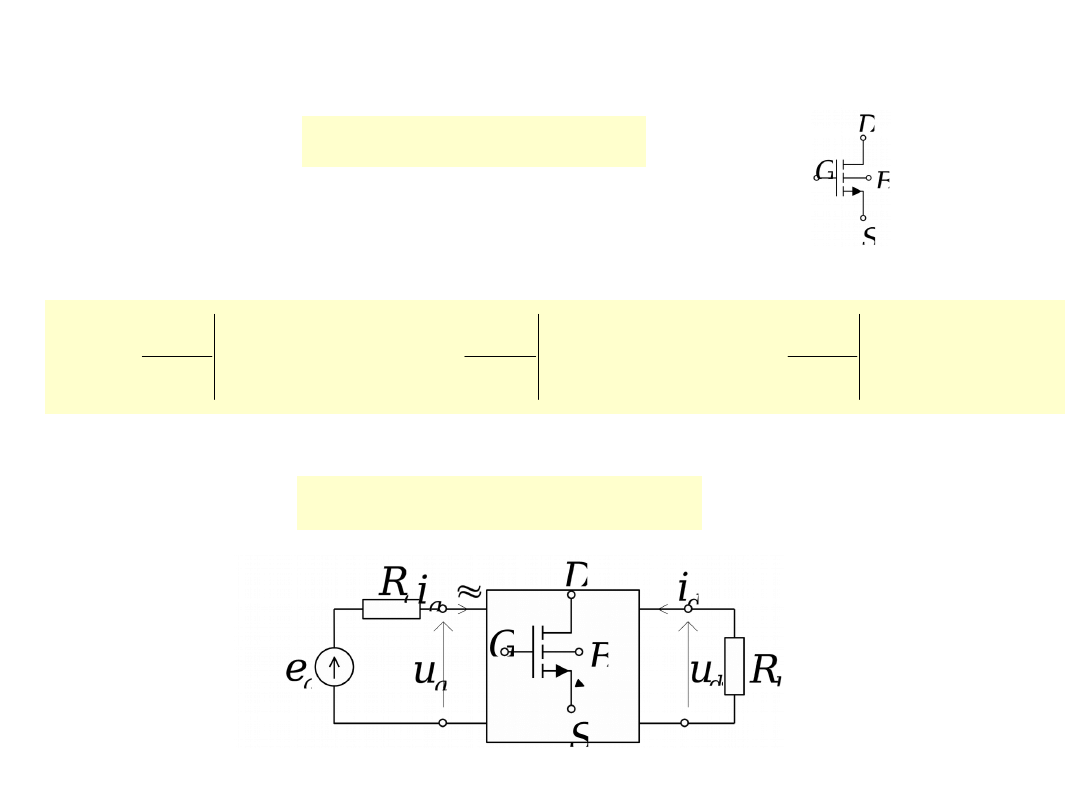

Tranzystor jako czwórnik aktywny

)

,

,

(

DS

DS

GS

D

U

U

U

f

I

Dla układu

OS:

bs

mb

ds

ds

gs

m

d

u

g

u

g

u

g

i

Małosygnałowy model tranzystora MOSFET

const

,

BS

DS

U

U

GS

D

m

U

I

g

const

,

BS

GS

U

U

DS

D

ds

U

I

g

const

,

GS

DS

U

U

BS

D

mb

U

I

g

Transkonduktancja:

Konduktancja wyjściowa:

Transkonduktancję

wynikającą z wpływu

napięcia U

BS :

g

K

W

L

I

K W

L

U

U

m

Dsat

GS

T

2 '

'

g

I

U

I

U

U

U

mb

D

BS

D

T

T

BS

m

BS

si

m

mb

g

U

g

g

2

ds

mb

m

g

g

g

100

10

g

I

ds

D

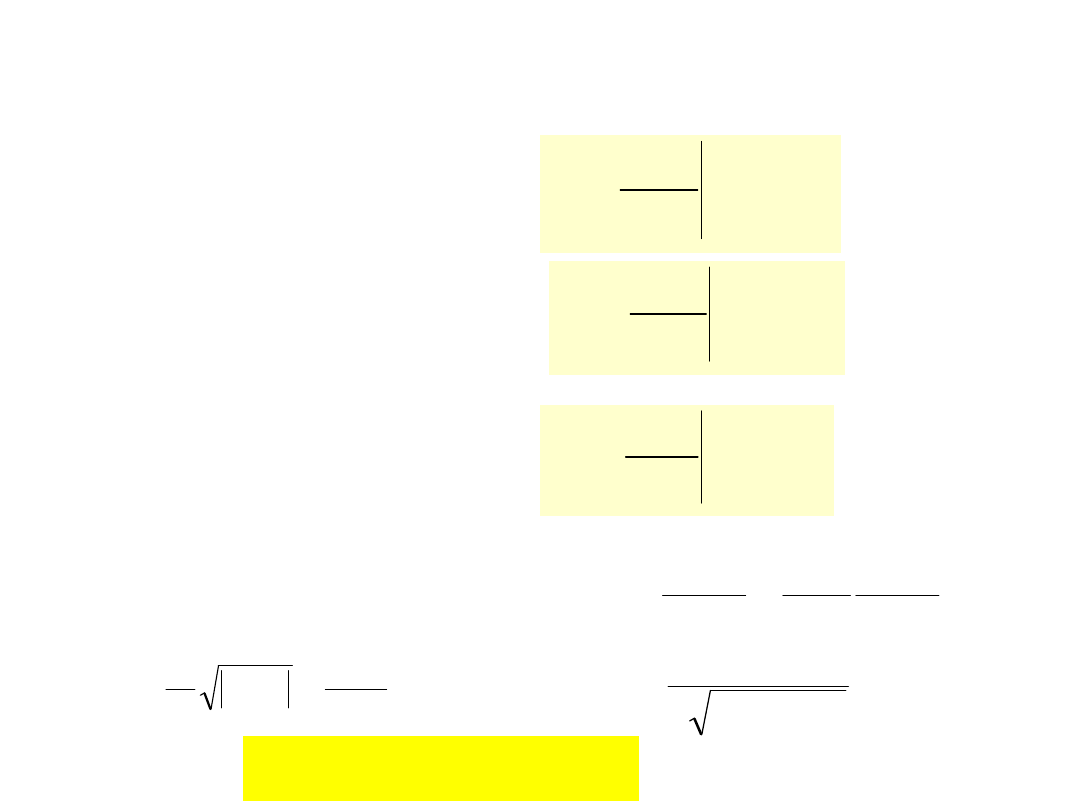

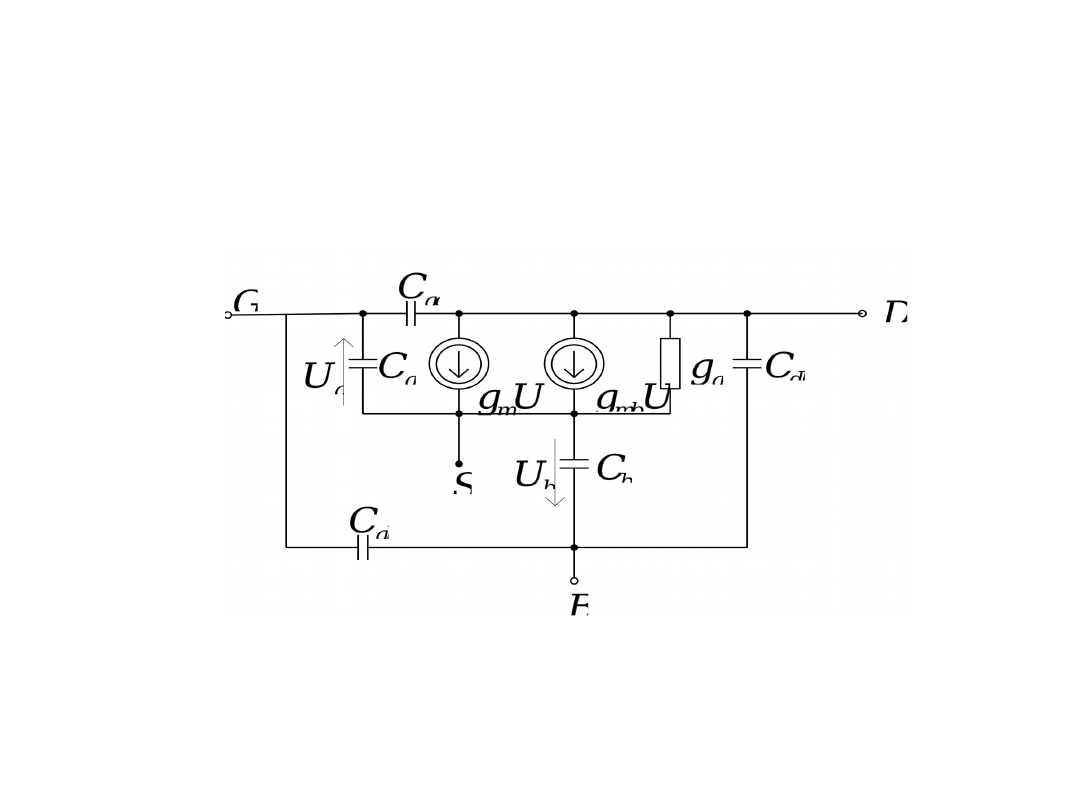

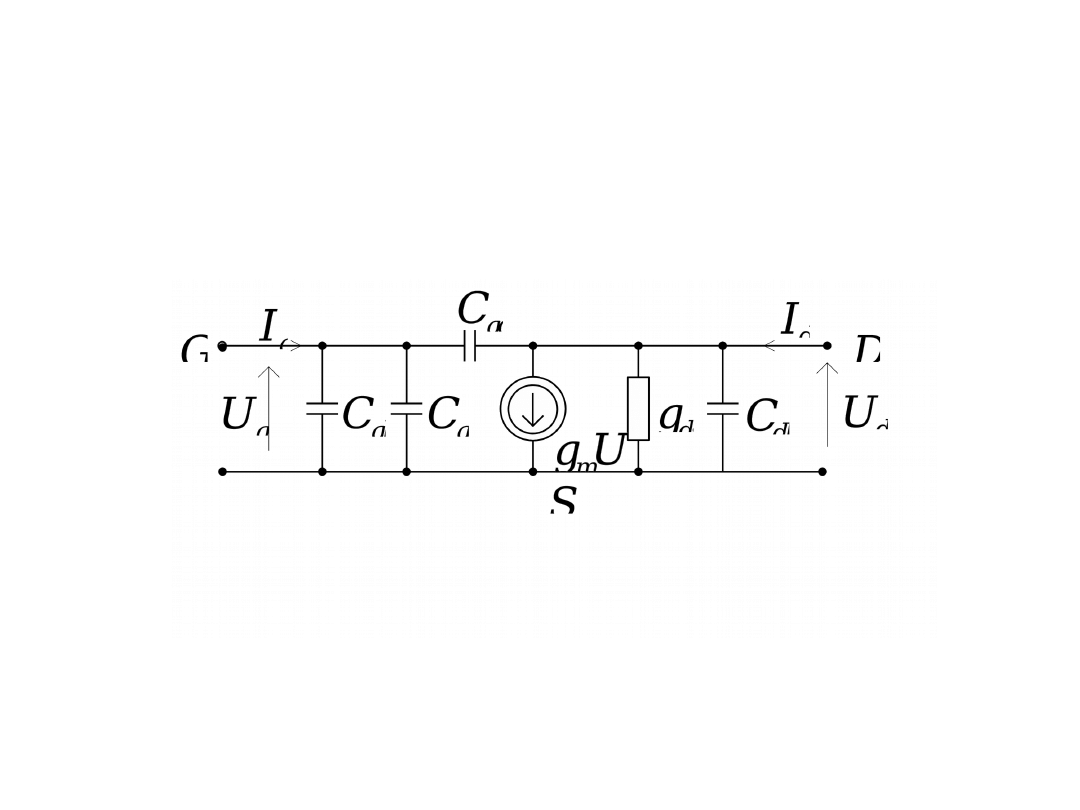

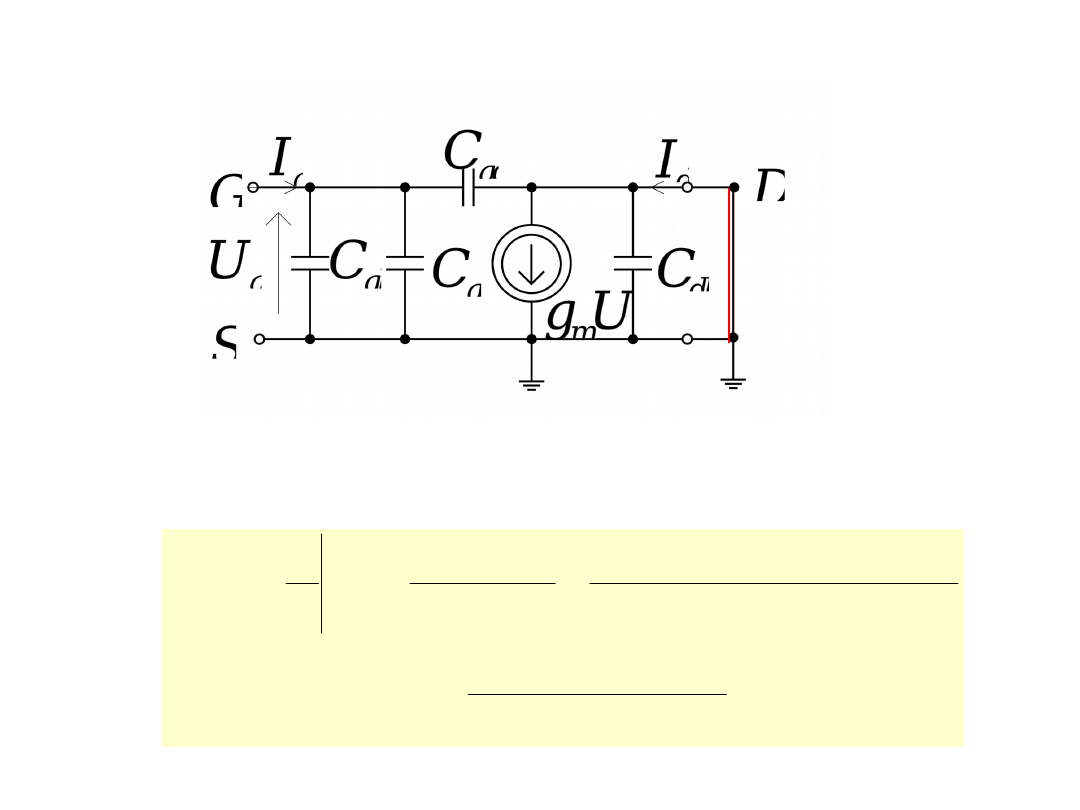

MAŁOSYGNAŁOWY MODEL TRANZYSTORA

MOSFET

Z UWZGLĘDNIENIEM EFEKTU PODŁOŻA

Małosygnałowy model tranzystora MOSFET

w zakresie wielkich częstotliwości,

bez uwzględnienia efektu podłoża

Częstotliwość odcięcia f

T

jest częstotliwością przy której prąd

wejściowy I

g

jest równy prądowi źródła sterowanego g

m

U

gs

tranzystora przy zwartym wyjściu.

Częstotliwość graniczna f

T

tranzystora

MOSFET

gb

gd

gs

m

T

i

gd

gb

gs

gs

gs

m

g

gs

m

U

g

d

i

C

C

C

g

f

j

k

C

C

C

j

j

U

j

U

g

j

I

j

U

g

I

I

j

k

ds

2

dla

1

0

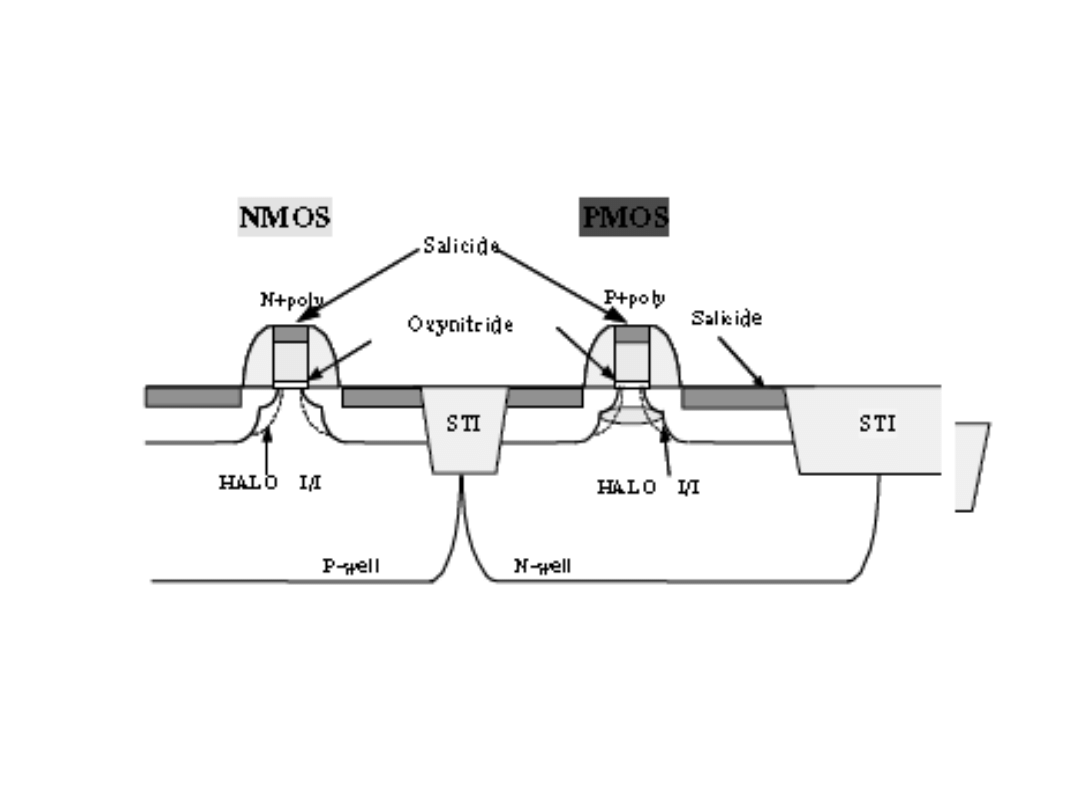

Przekrój poprzeczny tranzystorów NMOS i PMOS z krótkim

kanałem wykonanych w zaawansowanej technologii z płytką

izolacją rowkową STI

(

Shallow Trench Isolation)

Warstwy „salicide” (niskorezystywne

warstwy krzemianów: np. TiSi2, W Si2, W

Si2, TaSi2)

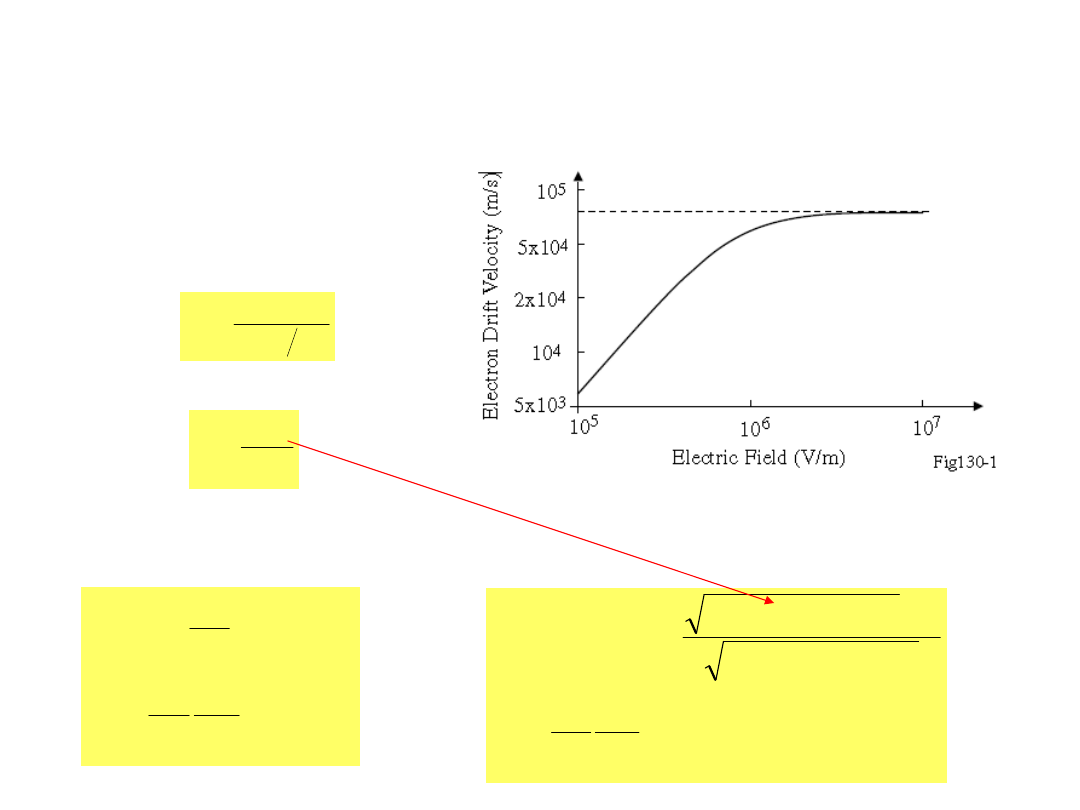

Tranzystory MOS z krótkim kanałem

c

n

d

E

E

E

v

1

2

'

2

1

2

L

C

g

f

V

V

L

W

K

g

gs

m

T

T

GS

m

1

2

1

2

1

1

2

1

L

C

g

f

V

V

V

V

E

WC

g

gs

m

T

T

GS

T

GS

c

o

ox

m

Prędkość poruszania się

elektronów:

Nie ma nasycenia ruchliwości

nośników

Występuje nasycenia ruchliwości nośników

c

LE

1

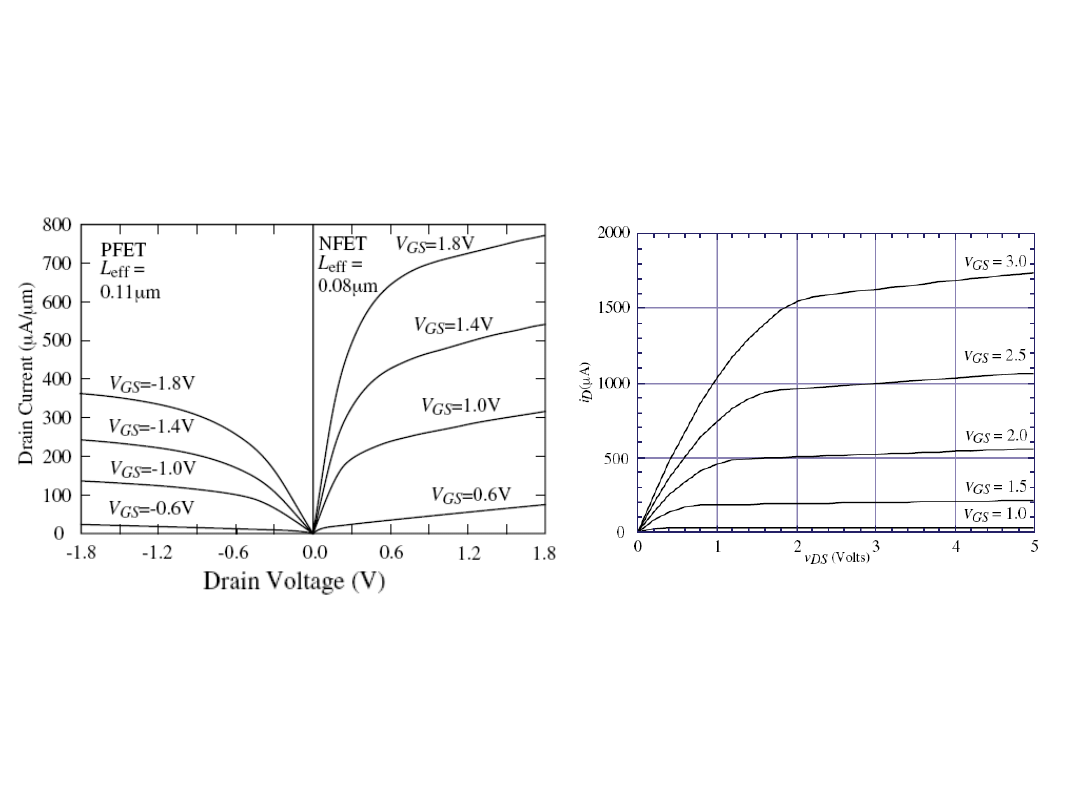

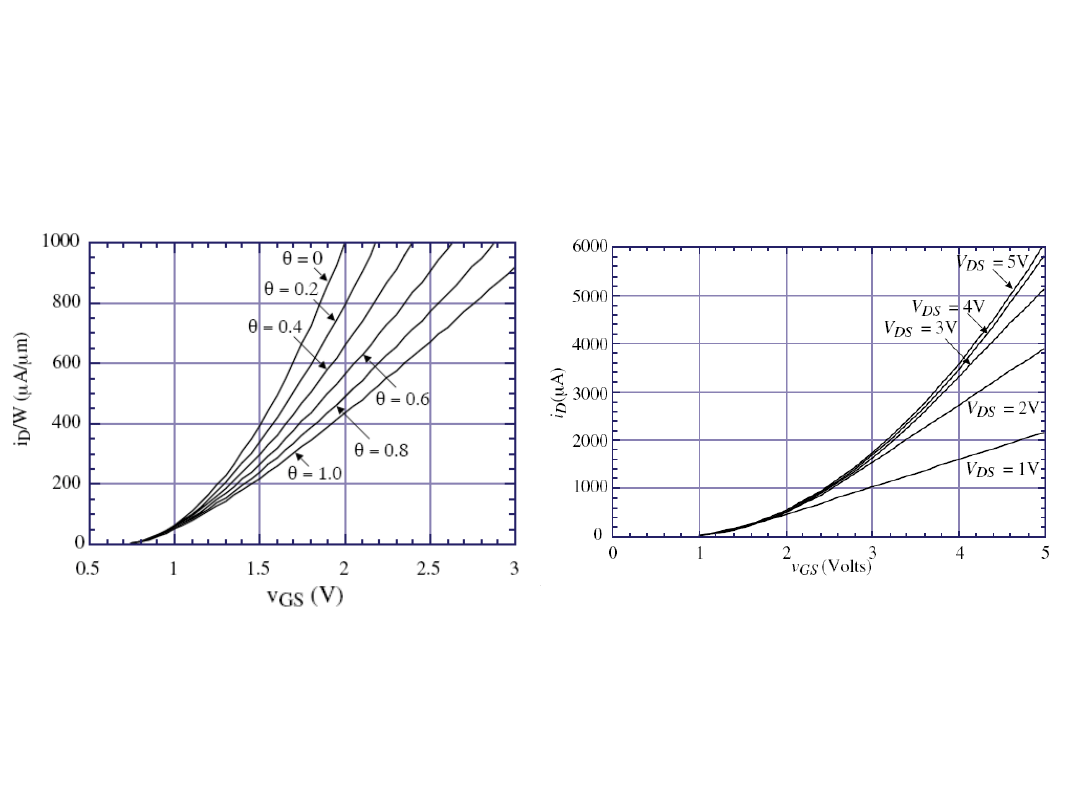

Przykładowe charakterystyki

wyjściowe tranzystorów z kanałem

wzbogacanym

Tranzystor z krótkim kanałem Tranzystor bez efektu

krótkiego kanału

Przykładowe

charakterystyki

przejściowe

tranzystora NMOS z kanałem

wzbogacanym

Tranzystor z krótkim kanałem Tranzystor bez efektu

krótkiego kanału

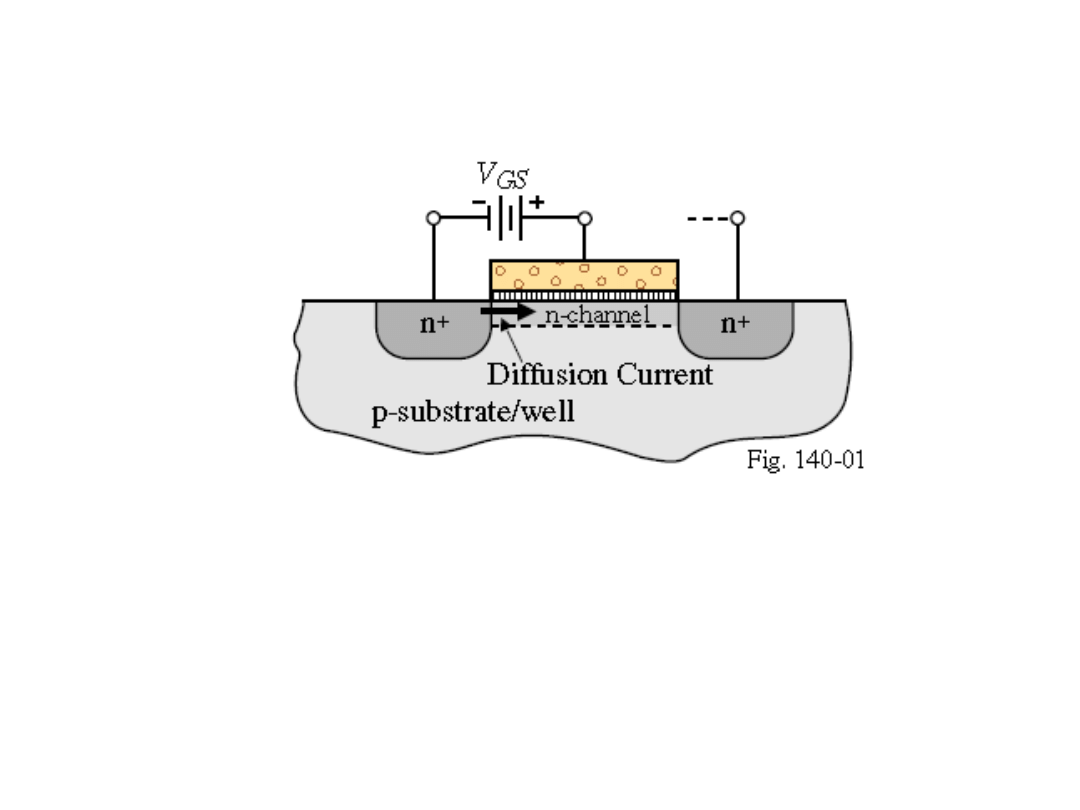

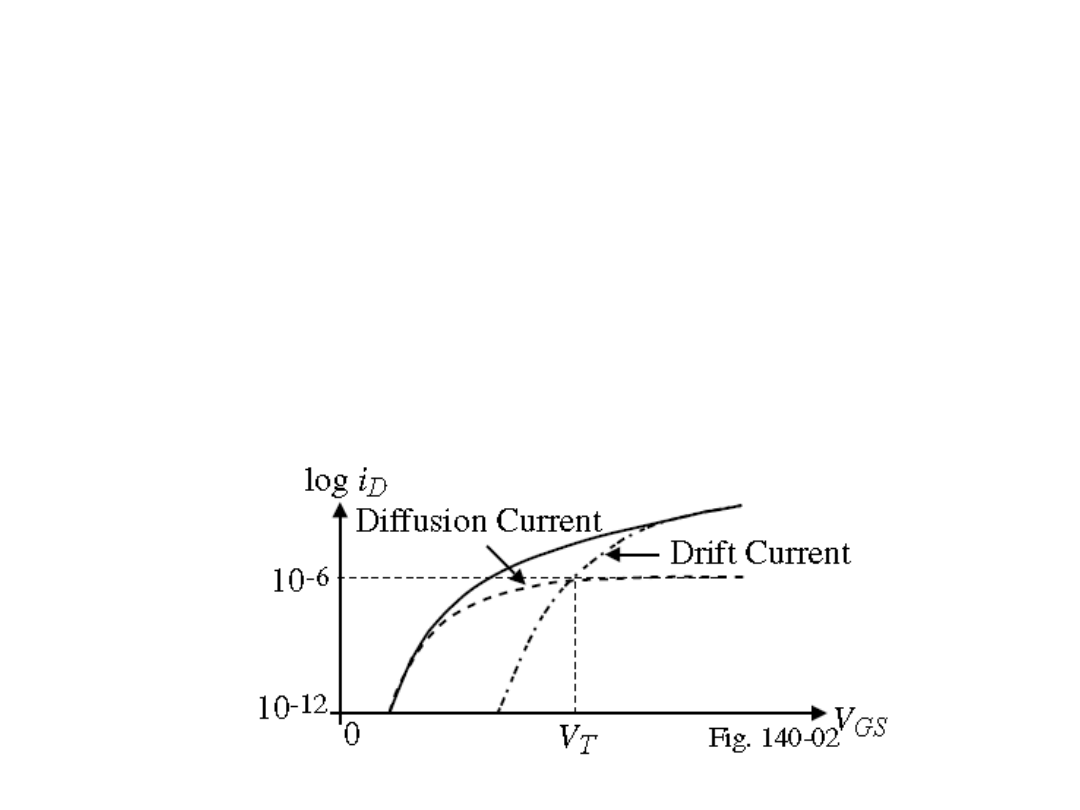

ZAKRES PODPROGOWY PRACY

TRANZYSTORA MOSFET

Zakresy pracy zależne są od potencjału powierzchniowego ϕ

S

przy

silnej inwersji półprzewodnika:

ϕ

S

< ϕ

F

; Brak inwersji podłoża

ϕ

S

< ϕ

F

< 2 ϕ

F

; Słaba inwersja kanału (płynie prąd dyfuzyjny do

drenu)

2ϕ

S

< ϕ

F

; Silna inwersja kanału (płynie prąd dryftowy do

drenu)

PRĄD DRENU - DRYFTOWY PRZY SILNEJ INWERSJI

PRĄD DRENU - DYFUZYJNY PRZY SŁABEJ INWERSJI

1). Przy silnej inwersji, napięcie bramki steruje ładunkiem w obszarze

inwersyjnym, tj w obszarze wyindukowanego kanału, a nie wpływa na

ładunek w obszarze zubożonym. Koncentracja ładunku w kanale jest

prawie stała, prąd dryftowy drenu płynie pod wpływem pola elektrycznego

w kanale.

2). Przy słabej inwersji, ładunek w kanale jest znacznie mniejszy niż w

obszarze zubożonym i

dryftowy prąd drenu jest znikomy

. Jednakże na

skutek gradientu koncentracji ładunku w kanale, płynie prąd dyfuzyjny

drenu. (Źródło S tranzystora jest obszarem n

+

i zachowuje się podobnie jak

emiter tranzystora bipolarnego.

A

DS

t

T

GS

t

D

V

V

nV

V

v

L

W

I

i

1

exp

WIELKOSYGNAŁOWY MODEL DLA SŁABEJ

INWERSJI

Jeżeli: v

DS

> 0, to:

S

źródła

n

warstwy

ć

grubos

yczny,

termokinet

potencja

ł

1

3

5

,

1

exp

:

gdzie

'

1

2

2

1

2

0

X

V

n

V

k

k

k

n

V

v

k

n

v

n

C

C

C

dv

d

n

V

k

n

qXD

I

t

T

T

GS

GS

S

jS

ox

ox

GS

S

t

p

n

t

Voltage

Early

A

A

D

ds

jS

ox

ox

t

D

m

V

V

I

g

C

C

C

V

I

g

TRANZYSTOR MOSFET W OBSZARZE SŁABEJ INWERSJI

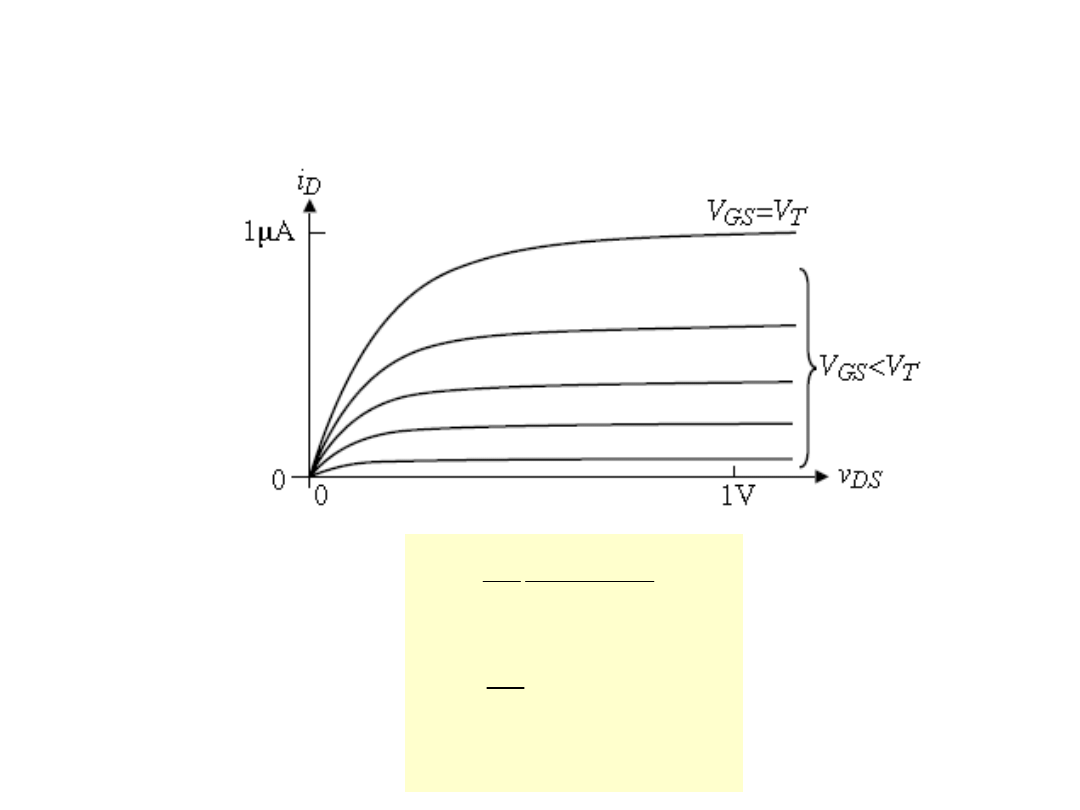

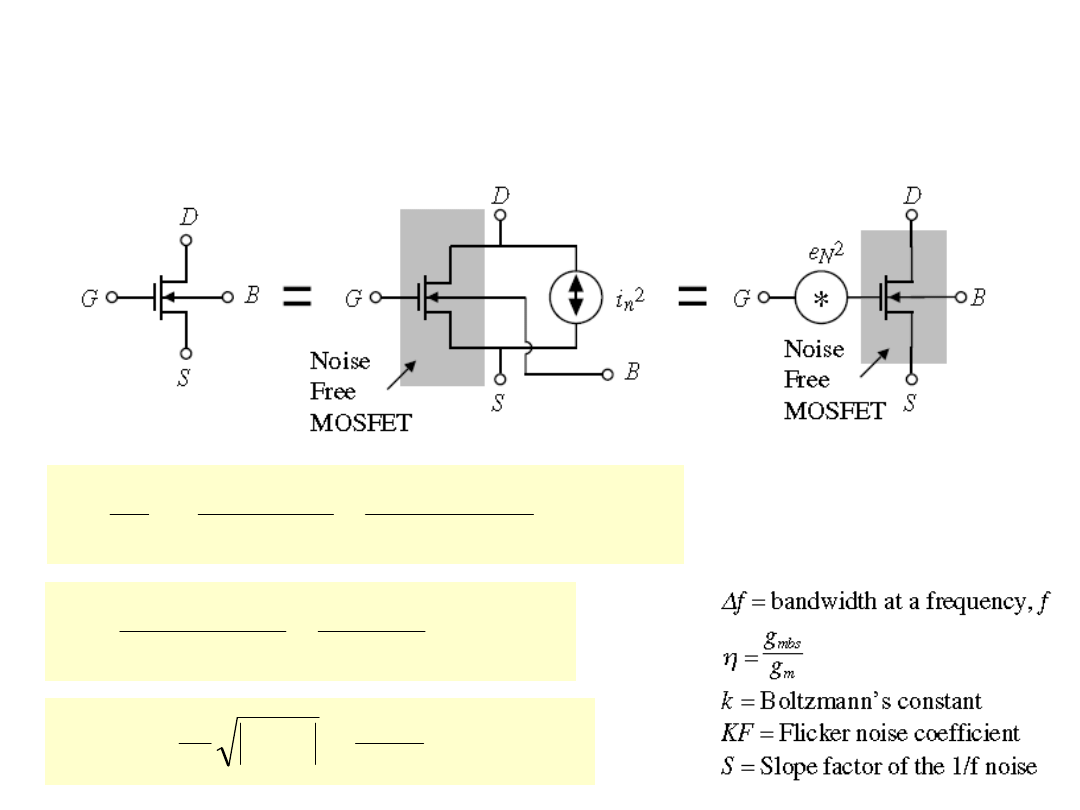

SZUMOWY MODEL TRANZYSTORA

MOSFET

2

'

0

2

2

2

V

2

3

)

1

(

8

f

WLK

C

f

I

K

g

kT

g

i

e

x

s

D

F

m

m

n

n

2

2

0

2

A

3

)

1

(

8

f

L

C

f

I

K

kTg

i

x

s

D

F

m

n

g

K

W

L

I

K W

L

U

U

m

Dsat

GS

T

2 '

'

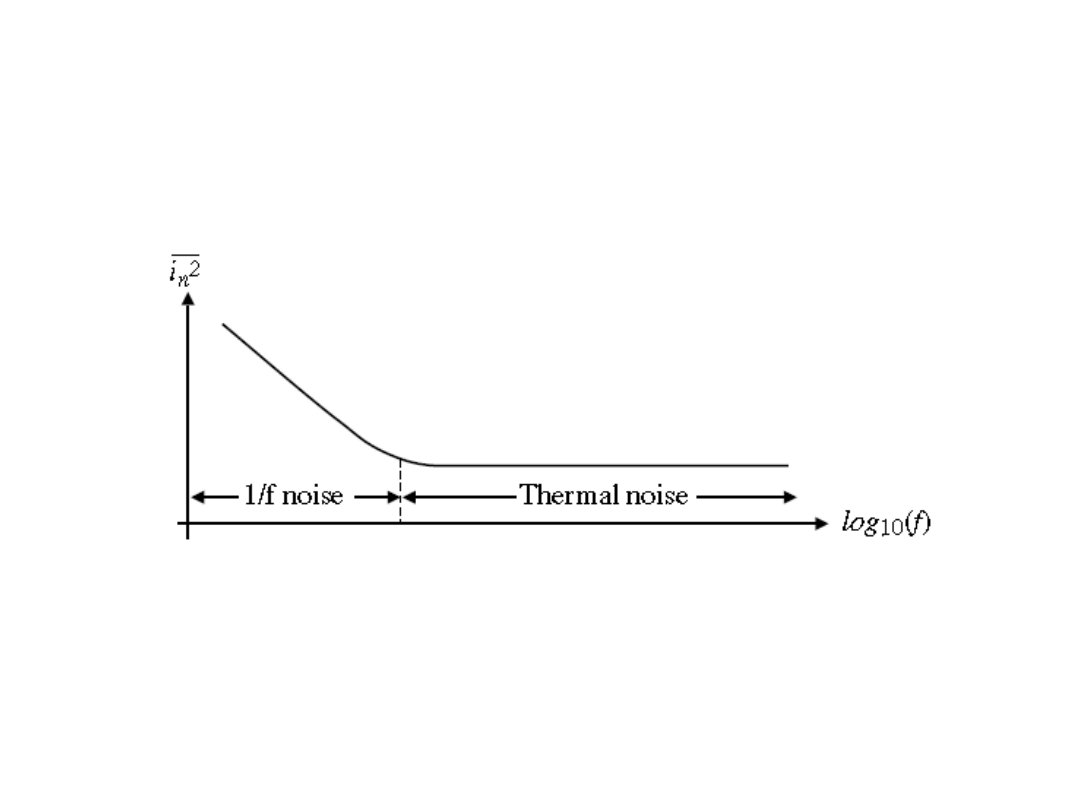

GĘSTOŚĆ WIDMOWA PRĄDU SZUMÓW

TRANZYSTORA MOSFET

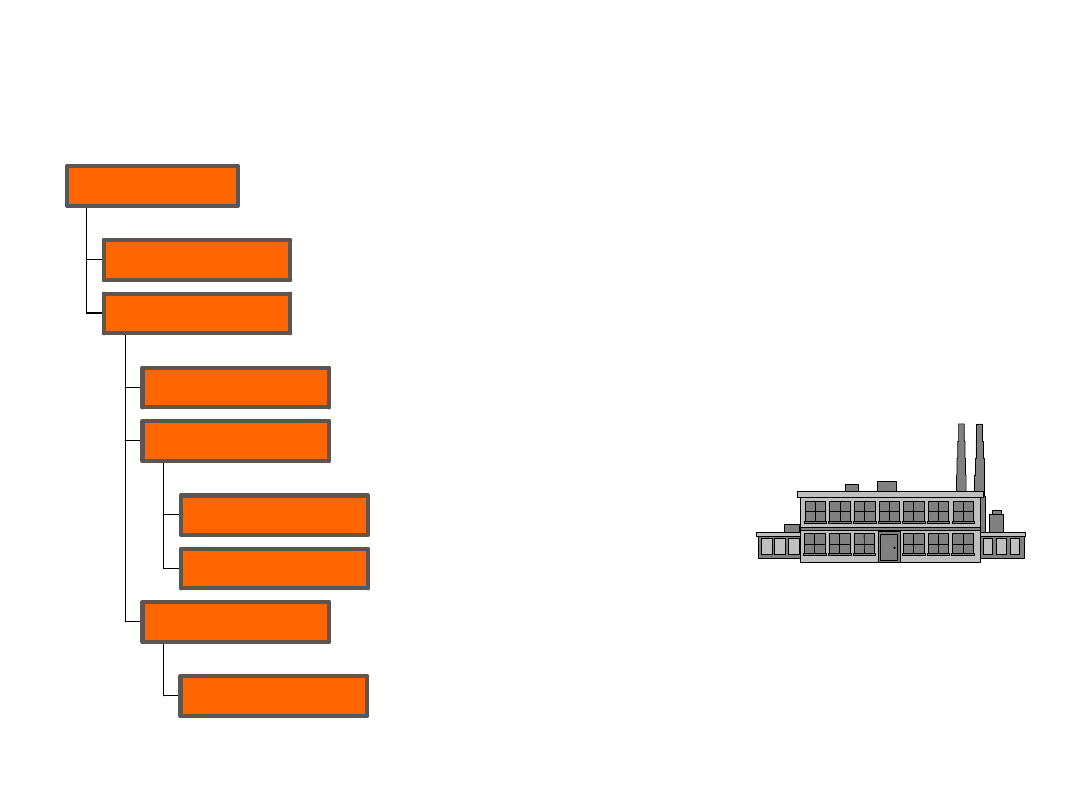

Układy specjalizowane

W i e l k i e s ta n d a r d y

F u l l C u s to m

G a te A r r a y

S ta n d a r d C e l l s

S e m i C u s to m

R e p r o g r a m o w a l n e

P r o g r a m o w a l n e

A S IC

U k ła d y s c a l o n e

Motorola, INTEL,Analog Devices, National

Semiconductors

Application Specific Integrated Circuit

Pełny cykl projektowania, projekt na poziomie masek (layout)

Układ projektowany na zamówienie

matryce bramek

komórki standardowe

Xilinx, Altera (cyfrowe), Zetex (ukł. analogowe!!)

Huta krzemu

(Silicon Foundry)

Strategie projektowania

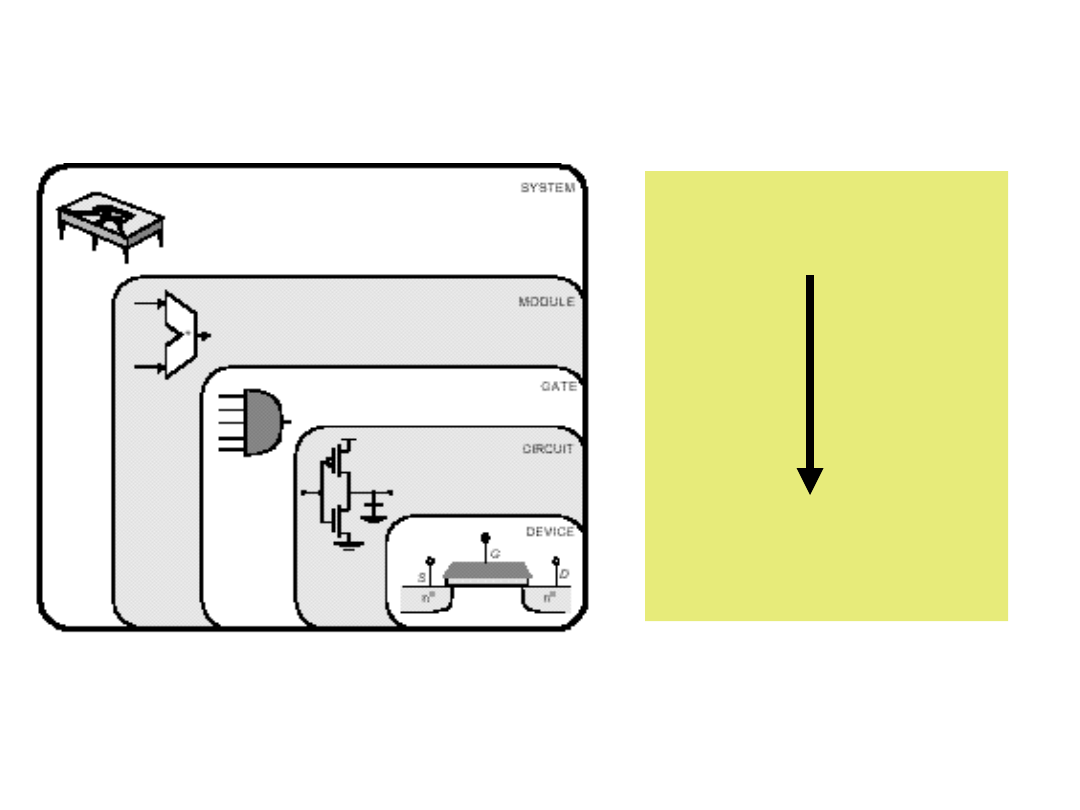

Up Top

Bottom Down

Hierarchia zadań projektowych wg. stopnia

abstrakcji

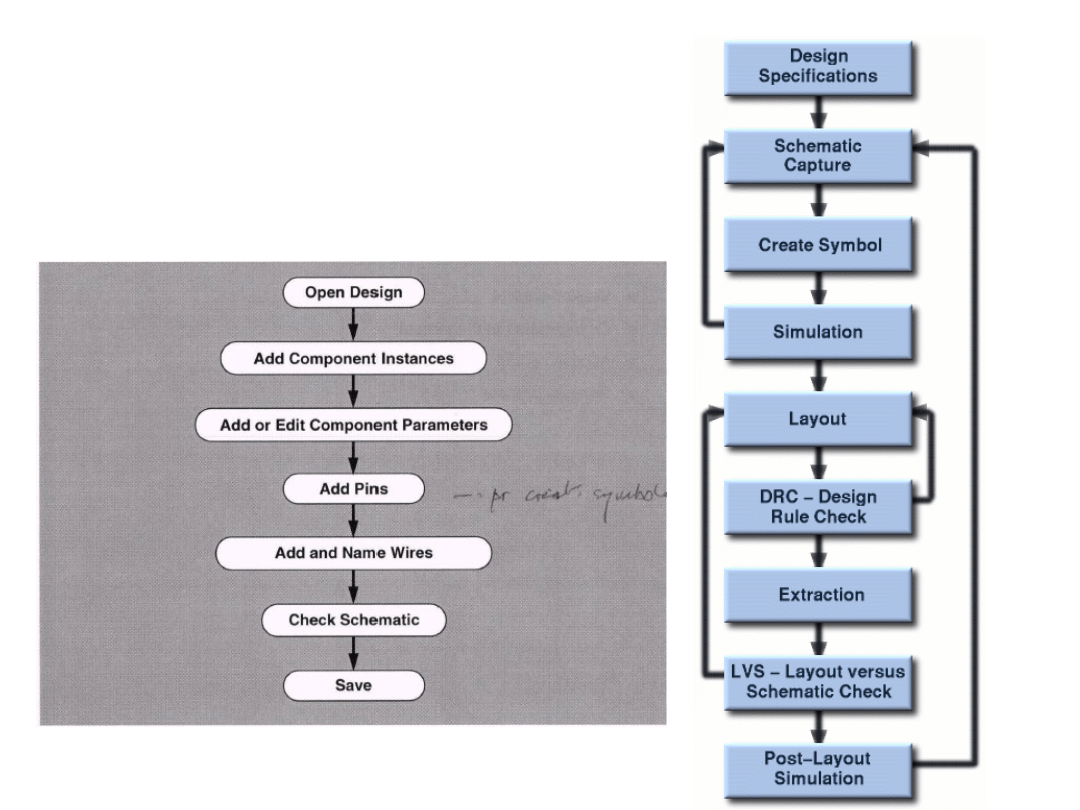

Środki CAD w projektowaniu

fizycznym

• Projekt wstępny

• Symulacja przedlayoutowa (SPICE, SMASH, APLAC etc.)

• Projektowanie layoutu (specjalizowany edytor graficzny)

• Weryfikacja reguł geometrycznych. (

DRC - Design Rule

Check)

• Weryfikacja elektrycznych reguł projektowch

(latch up!)

(ERC - Electrical Rule Check)

• Ekstrakcja schematu

(LVS - Layout versus Schematic

Check)

• Końcowa symulacja postlayoutowa (+statystyka!)

(PLS

Post - Layout Simulation)

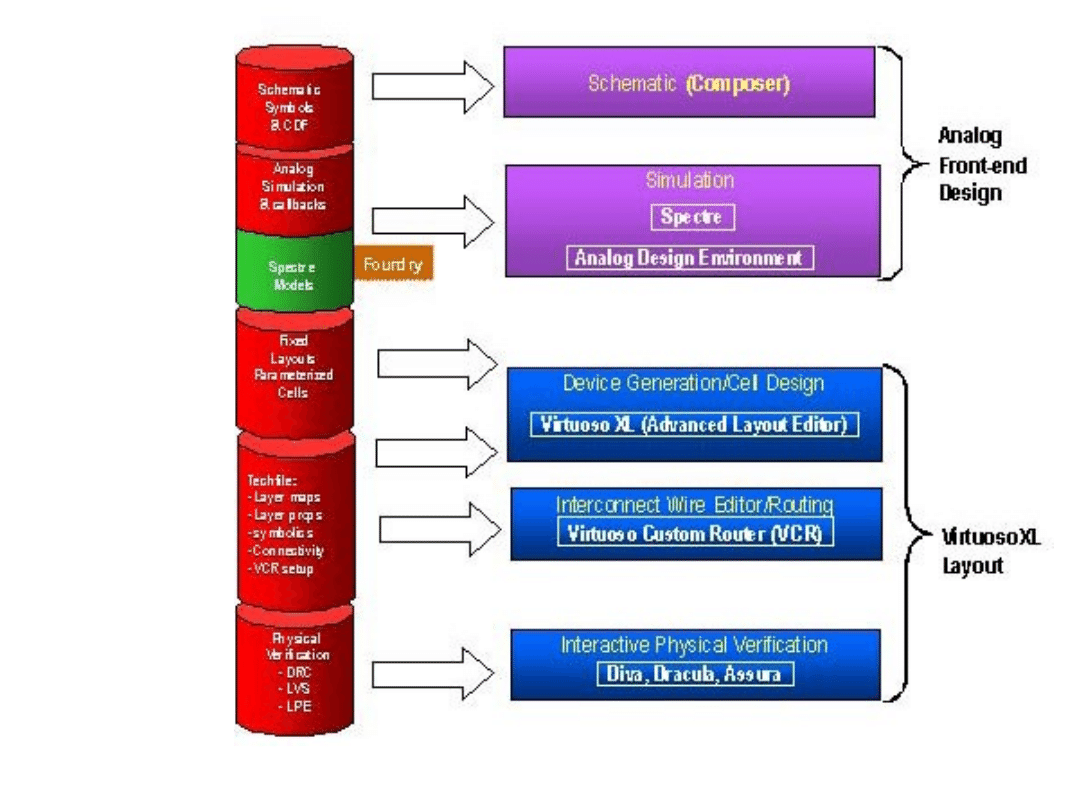

Typowy „design flow”

Schematic

Przebieg projektowania układu analogowego

CMOS

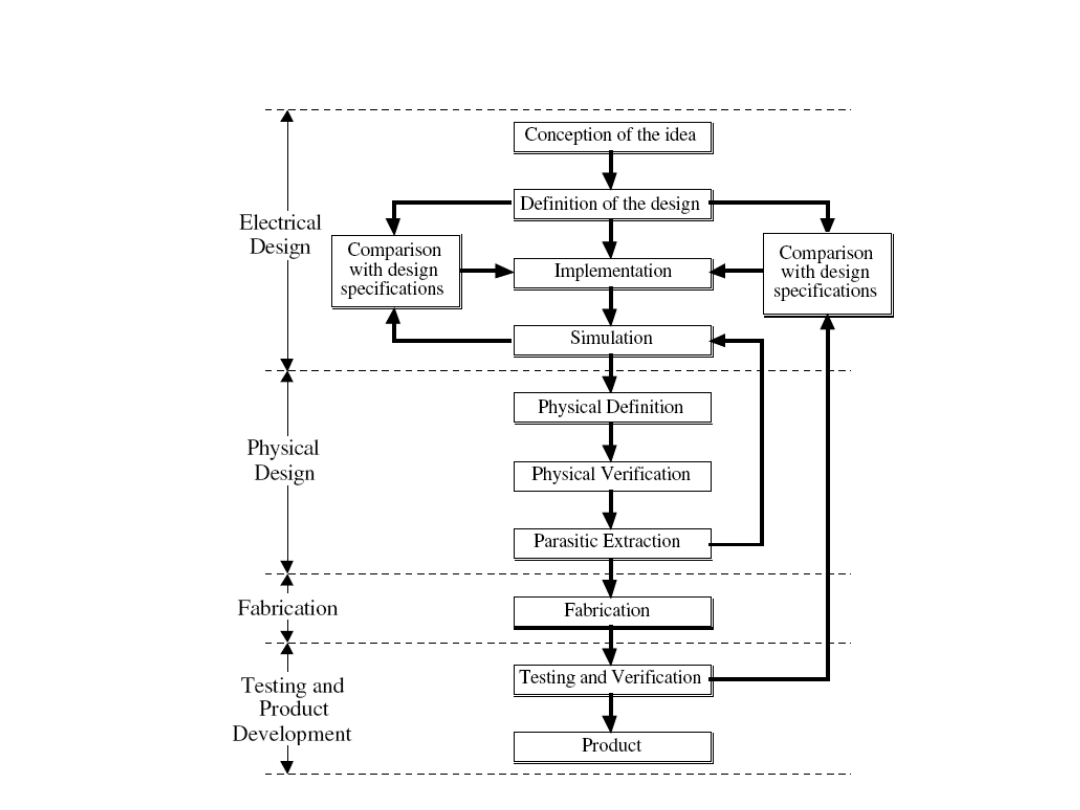

Reguły projektowania (LRS - Layout Rule Specification) dostarczją reguł

projektowania layoutu wraz z parametrami elektrycznymi wszystkich

elementów wykorzystywanych w danej technologii układów scalonych, np.:

0.35um CMOS, C035M-D Alcatel Microelectronics technology, (Alcatel 0.35

um)

0.35um CMOS, C35M-D Austria MicroSystems technology, (AMS 0.35

um),

Mixed mode/RF UMC’s 0.18um CMOS process, (UMC 180 nm)

itd

Przykładowo,

FDK (Foundry Design Kit) UMC 0.18um Cadence-based

Mixed Mode/RF CMOS

dostarcza kompletnych reguł projektowania dla

„front-end and back-end”

*)

zaawansowanej technologii RFIC (Radio

Frequency Integrated Circuits) w środowisku CADENCE.

FDK zapewnia dostęp do wszystkich danych potrzebnych do projektów na

poziomach: projektowania układu (circuit-level design), layoutu i jego

weryfikacji (layout-level design and layout verification ) oraz zapewnia

dostęp do dokładnych modeli wszystkich elementów (accurate RFdevice

models).

*)

Tranzystory MOSFET i pojemności MOS wytwarzane są w podłożu

półprzewodnikowym w kolejnych 7 etapach procesów technologicznych

FEOL - CMOS Front End of Line process , zaś metalowe połączenia,

kontakty oraz indukcyjności wytwarzane są w kolejnych etapach procesów

technologicznych BEOL - CMOS Back End of Line process.

Wyszczególnione etapy procesów technologicznych często nazywa się

„modułami technologicznymi”.

A FDK

(Foundry Design Kit)

contains the process technology

and needed information to do

device-level design in the Cadence

DFII environment.

DRC (Design Rule

Check)

(LVS

Layout

versus Schematic

Check)

(PLS Post - Layout

Simulation)

Design Support

Manual

Electrical Design

Rule

Topological

Layout Rule

Spice Modeling

Mask Tooling

DRC Rule Deck

SDL: schematic

driven layout

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

Wyszukiwarka

Podobne podstrony:

60 64 IB 7 8 2006 Techn proj cz III

W2 Model kopalni

proj Model (1)

60 64 IB 7 8 2006 Techn proj cz III

Psycholgia wychowawcza W2

mapy do celow proj

R 6 1 Obiektowy model zapytan

model relacyjny

SP dzienni w2

w2 klasy(1)

model komunikacji dwustronnej

W2 Chemiczne skladniki komorki

więcej podobnych podstron