MSP 430

Liczniki

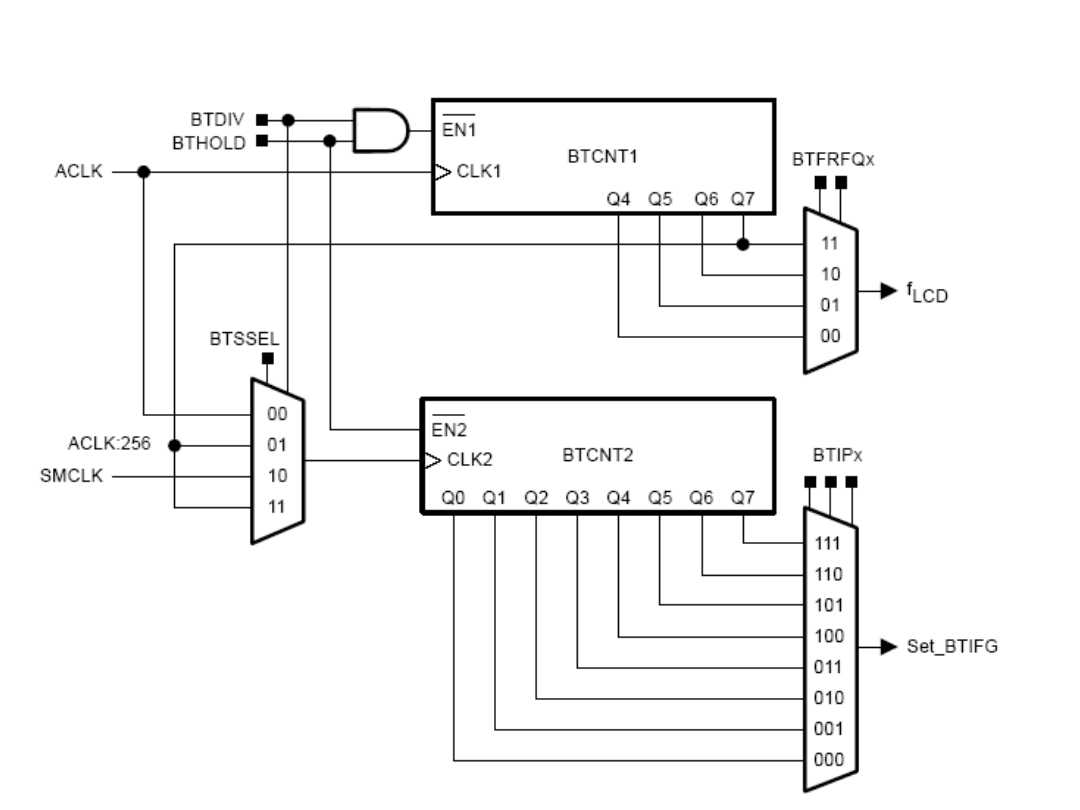

Basic Timer 1

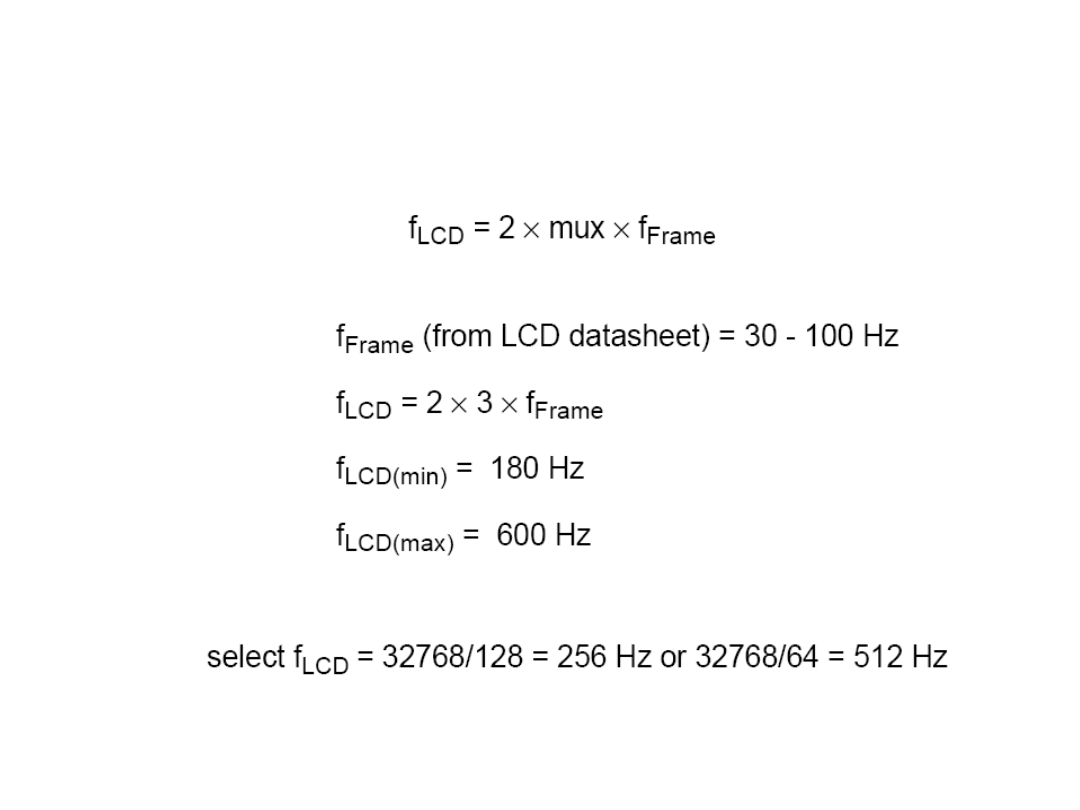

Taktowanie sterownika LCD (nie dotyczy LCD_A)

Sygnał taktujący jest określany zależnością: f

LCD

= 2xmulxf

takt

7 6 5 4 3 2 1

0

BTSSEL BTHOLD BTDIV BTFRFQx BTIPx

rw rw rw rw rw rw rw

rw

BTSSEL BTDIV

0 0 - ACLK

0 1 - ACLK/256

1 0 - SMCLK

1 1 - ACLK/256

BTHOLD - 0 – obydwa liczniki pracują, 1 – BTCNT2 stop, BTCNT1 stop jeżeli

BTDIV=1

BTFRFQx

0 0 - f

aclk

/32

0 1 - f

aclk

/64

1 0 - f

aclk

/128

1 1 - f

aclk

/256

BTIPx

0 0 0

- f

CLK2

/2

0 0 1

- f

CLK2

/4

0 1 0

- f

CLK2

/8

0 1 1

- f

CLK2

/16

1 0 0

- f

CLK2

/32

1 0 1

- f

CLK2

/64

1 1 0

- f

CLK2

/128

1 1 1

- f

CLK2

/256

7 6 5 4 3 2 1

0

BTIE

rw=0

7 6 5 4 3 2 1

0

BTIFG

rw=0

IE2

IFG2

Taktowanie sterownika pola LCD

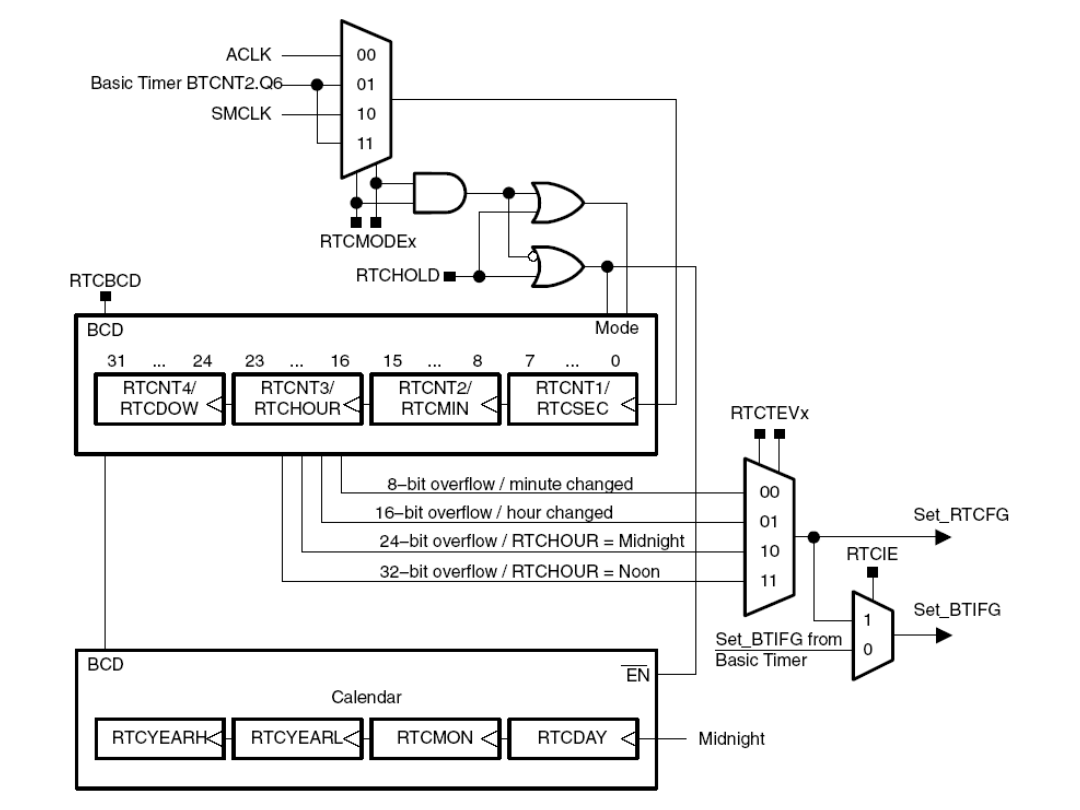

RTC - Układ zegara czasu rzeczywistego.

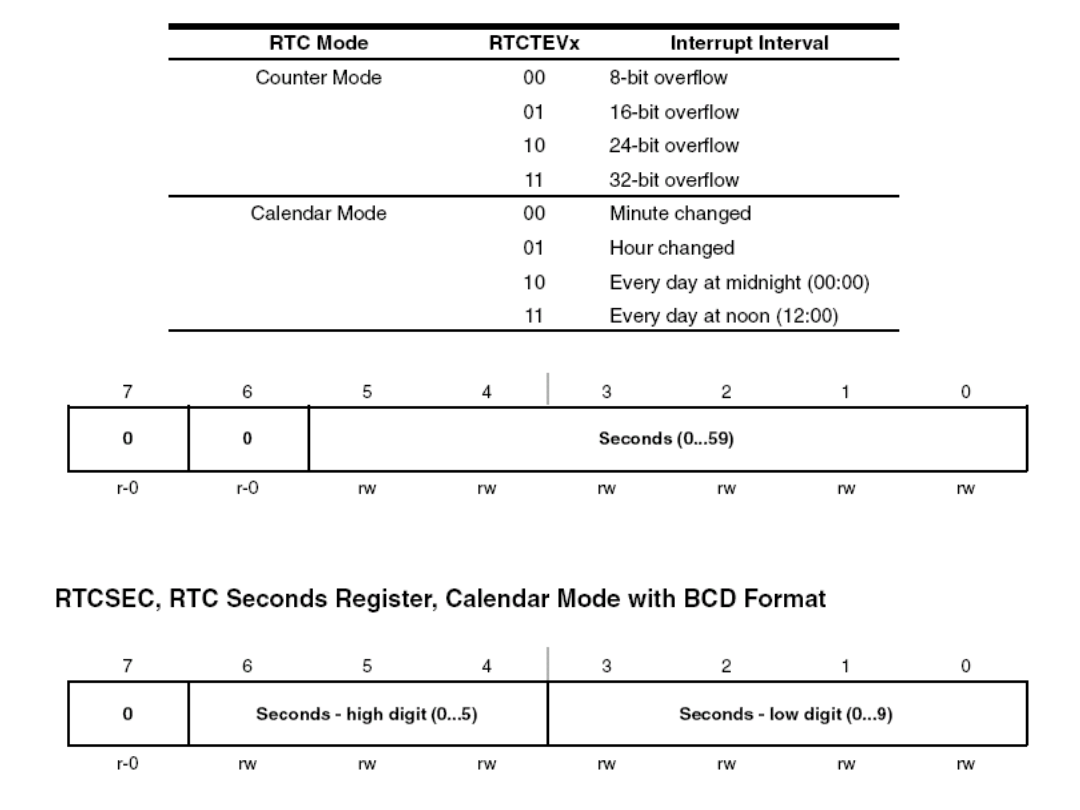

Układ zegara czasu rzeczywistego może pracować jako 32 bitowy licznik

ogólnego zastosowania lub jako zegar – kalendarz.

Właściwości:

- tryb kalendarza i zegara:

sekundy, minuty, godziny, dzień tygodnia dzień miesiąca, miesiąc,

rok.

- 32 licznik z wyborem źródła taktowania

- wybór trybu BCD lub HEX

- przerwanie.

Wybór licznika odbywa się przy RTCMODEx < 11. Rejestry licznika są

dostępne programowo. Można na nich dokonywać operacji odczytu lub

wpisu. Przełączenie z zegara na licznik zeruje rejestry.

Taktowanie licznika może odbywać się sygnałem ACLK, SMCLK lub

sygnałem z licznika BTCNT2. Praca licznika może być zatrzymana poprzez

ustawienie znacznika RTCHOLD.

Licznik składa się z 4 rejestrów 8 bitowych połączonych kaskadowo.

Można uruchomić przerwanie sygnałem z wyjścia każdego rejestru.

Kiedy licznik jest taktowany sygnałem asynchronicznym w stosunku do

CPU, do odczytu stanu licznika należy wstrzymać jego pracę, gdyż inaczej

odczyt może być niepoprawny. Można również dokonać kilkukrotnego

odczytu licznika o określić właściwa wartość programowo.

Wybór trybu kalendarza następuje gdy RTCMODEx = 11. W tym trybie

układ RTC zlicza sekundy, minuty, godziny, dzień tygodnia, dzień

miesiąca, miesiąc i rok w wybranym formacie BCD lub heksadecymalnym.

Przełączenie z trybu licznika na kalendarz powoduje zerowanie wszystkich

danych poza dniem miesiąca i miesiąca, które przyjmują wartość 1.

Wybór formatu BCD następuje poprzez ustawienie znacznika RTCBCD =

1. Musi to nastąpić przed wpisaniem danych początkowych. Zmiana stanu

znacznika RTCBCD powoduje ustawienie dnia miesiąca i miesiąca na 1 i

zerowanie pozostałych danych.

Układ kalendarza zawiera algorytm korygujący lata przestępne. Jest on

aktualny od 1901 - 2099 roku.

Podobnie jak w trybie licznika, na czas odczytu rejestrów układ nie

powinien pracować. Można dokonać kilku odczytów i wybrać właściwy.

Można także odczytać rejestr sekund i jeżeli odczytana wartość nie będzie

bliska granicznej, to można odczytać pozostałe rejestry.

W trakcie wpisu do rejestrów zatrzymywane jest taktowanie. Może to

spowodować stratę jednej sekundy. Wpis danej wykraczającej poza zakres

może spowodować nieprzewidziany rezultat.

Układ RTC nie posiada funkcji alarmów.

Wybranie trybu kalendarza automatycznie konfiguruje Basic Timer1.

Znaczniki BTSSEL, BTHOLD i BTDIV są ignorowane, a znacznik RTCHOLD

kontroluje układami RTC i Basic Timer1.

Układ RTC używa dwóch znaczników do wywoływania przerwania: BTIFG

umieszczonego w IFG2.7 od Basic Timer1 i RTCFG.

Gdy znacznik odblokowania przerwania RTCIE = 0, przerwanie jest

kontrolowane przez Basic Timer1. Znacznik RTCFG jest ustawiany przy

przepełnieniu rejestru zgodnie ustawieniem znaczników RTCEVx, ale nie

wywołuje przerwania. Znacznik RTCFG musi być kasowany programowo

gdy RTCIE = 0.

Jeżeli RTCIE = 1 przerwanie jest sterowane przez RTC, a Basic Timer1 jest

ignorowany. W tym przypadku są ustawiane obydwa znaczniki. Są one

kasowane automatycznie po wejściu do procedury obsługi przerwania, lub

mogą być kasowane programowo.

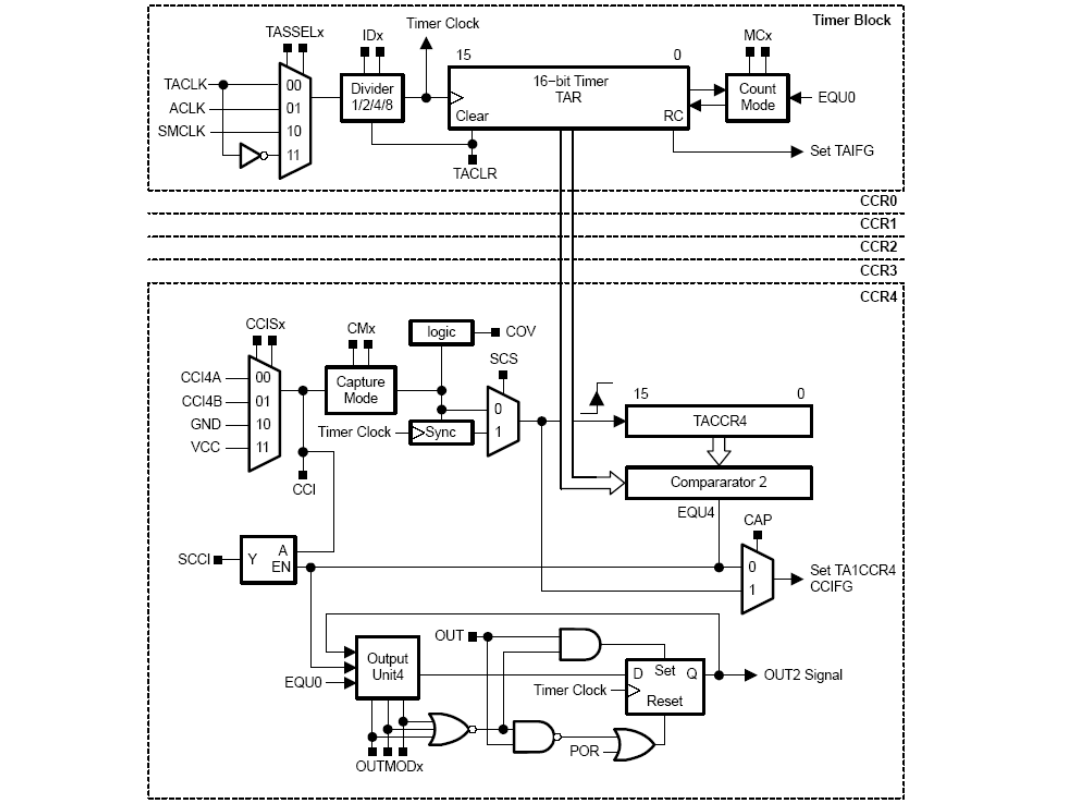

TIMER A3 (5)

Asynchroniczny 16-bitowy licznik z czterema trybami pracy

Wybór i konfiguracja różnych źródeł taktowania

Trzy lub pięć konfigurowalnych rejestrów typu zatrzask/komparator

Konfigurowalne wyjścia, możliwość trybu PWM

Asynchroniczne zatrzaskiwane wejścia i wyjścia

Rejestr wektora przerwań do szybkiego dekodowania wszystkich

przerwań

Zalecane jest zatrzymanie licznika przed modyfikacją trybu jego pracy, poza

odblokowaniem przerwania i kasowaniem licznika poprzez ustawienie

znacznika TACLR.

Jeżeli taktowanie licznika jest asynchroniczne względem taktowania CPU,

odczyt stanu licznika powinien odbywać się przy zatrzymanym liczniku.

Inaczej odczyt może być niewłaściwy. Jeżeli taki odczyt jest konieczny, to

należy kilka razy odczytać licznik i programowo wybrać wartość

maksymalną.

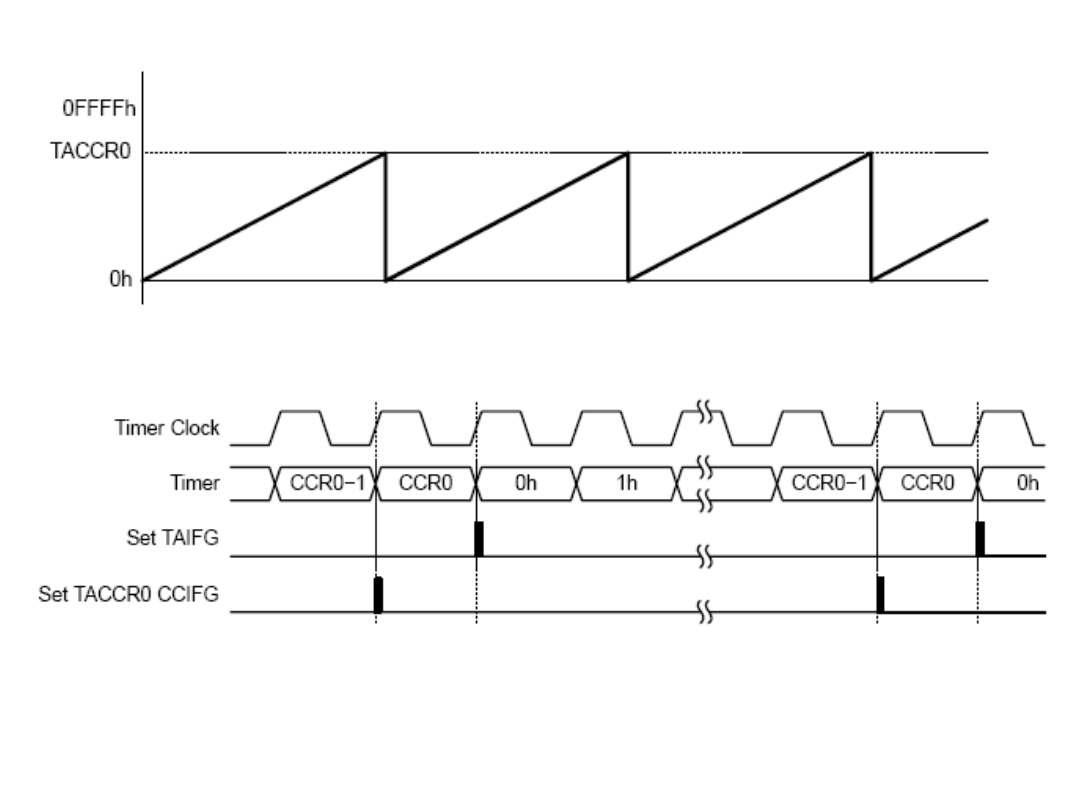

Cztery tryby pracy ustawiane znacznikami MCx:

MCx tryb

00

stop

- zatrzymanie licznika

01 w górę

- zliczanie od 0 w górę do osiągnięcia wartości w

rejestrze TACCR0

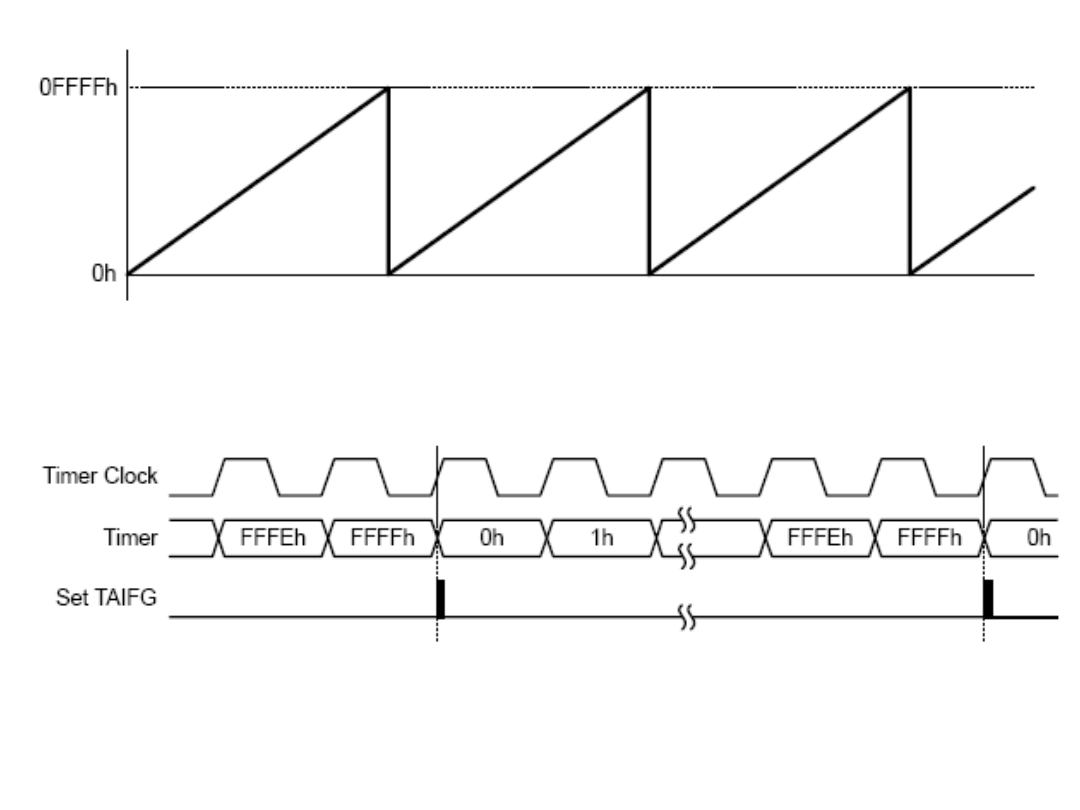

10 ciągły - zliczanie od 0 do 0FFFFh

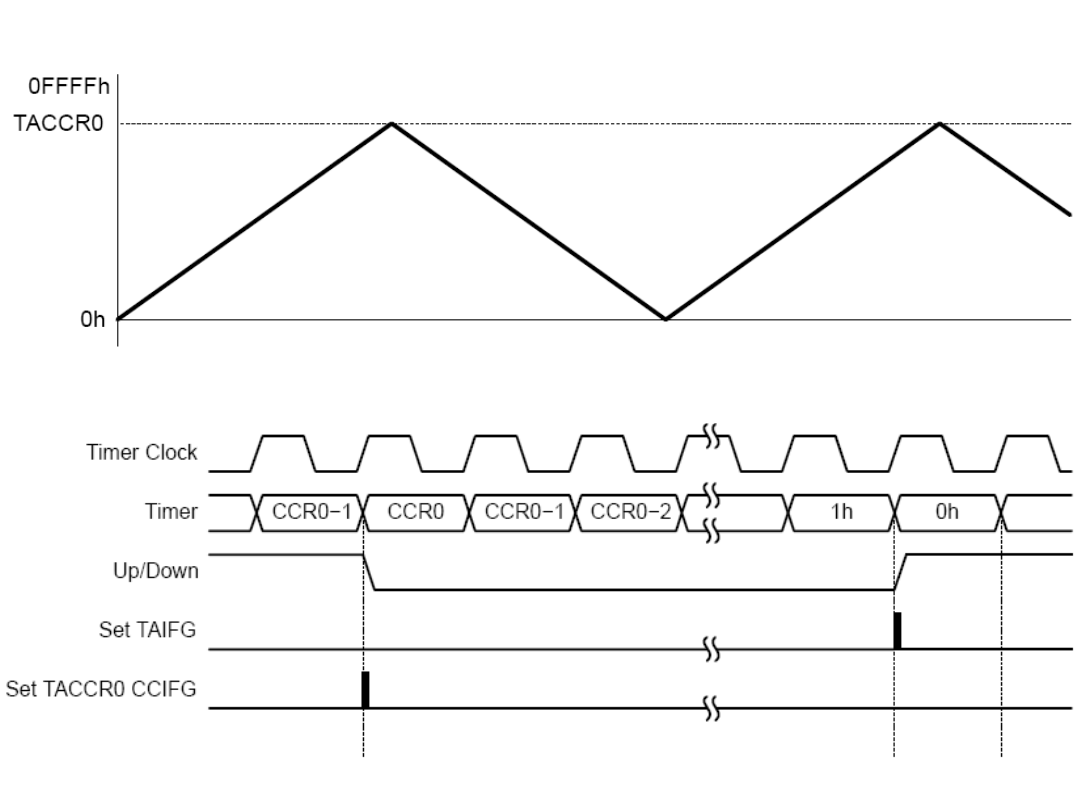

11 góra/dół

- zliczanie od 0 do wartości w rejestrze TACCR0, a

następnie do 0

Tryb „w górę”:

Ustawianie

znaczników

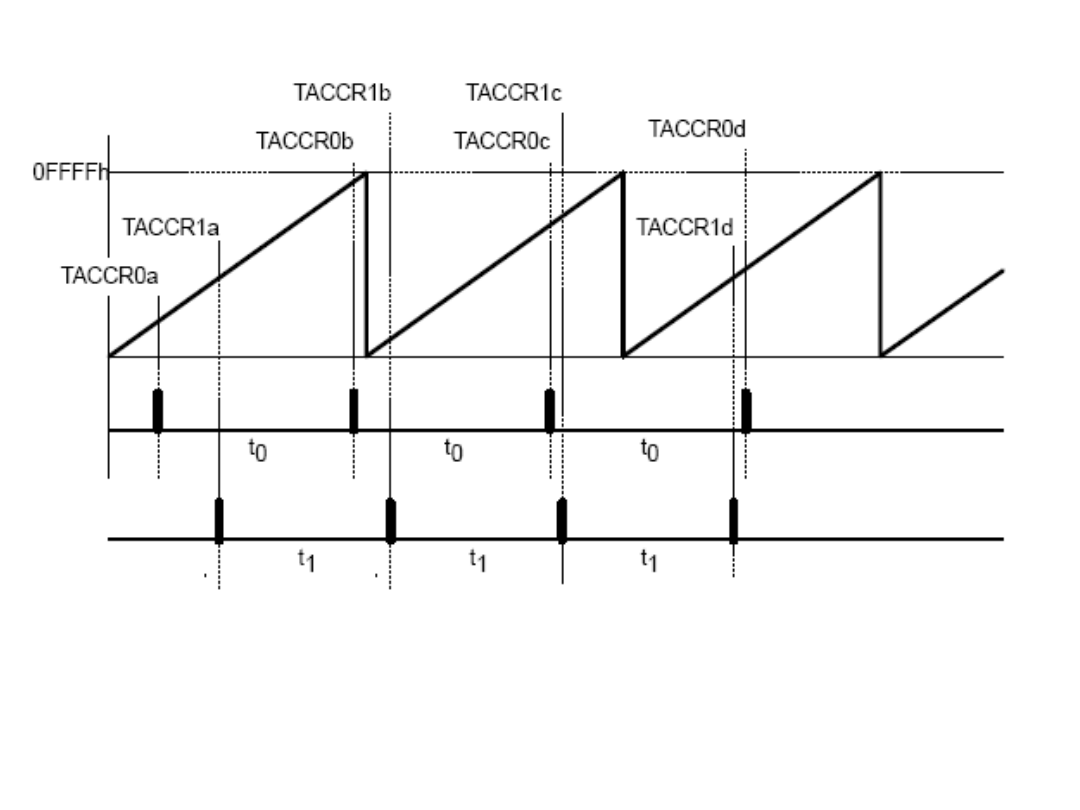

Tryb ciągły:

Ustawianie znaczników:

Przykład zastosowania trybu ciągłego

Wpis nowej wartości do rejestru TACCR0, gdy licznik zlicza w dół, daje dopiero efekt,

po dojściu licznika do 0.

Jeżeli licznik zlicza w górę i do rejestru TACCR0 zostanie wpisana wartość większa lub

równa wartości poprzedniej, lub jest większa od wartości licznika, to licznik liczy

dalej. W przeciwnym przypadku licznik, po zliczeniu ewentualnie jednego impulsu,

zaczyna zliczać w dół.

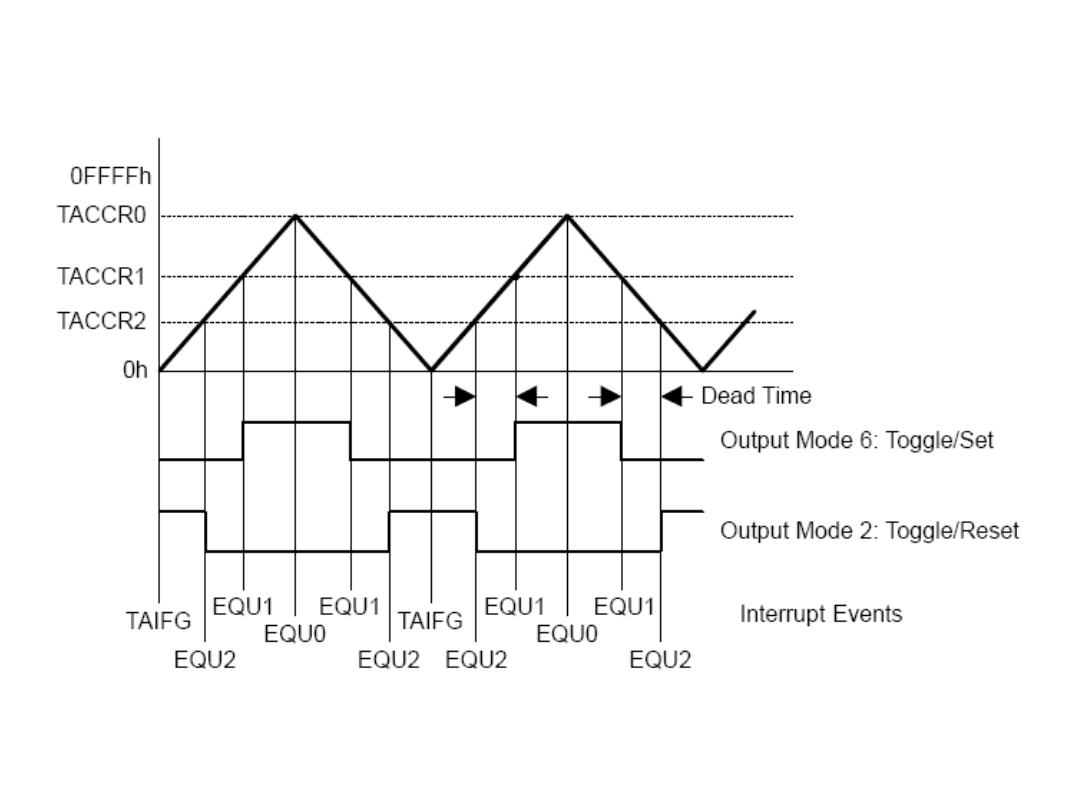

Tryb „góra/dół”:

Ustawianie znaczników:

Rejestry TACCRx – zatrzaski/komparatory

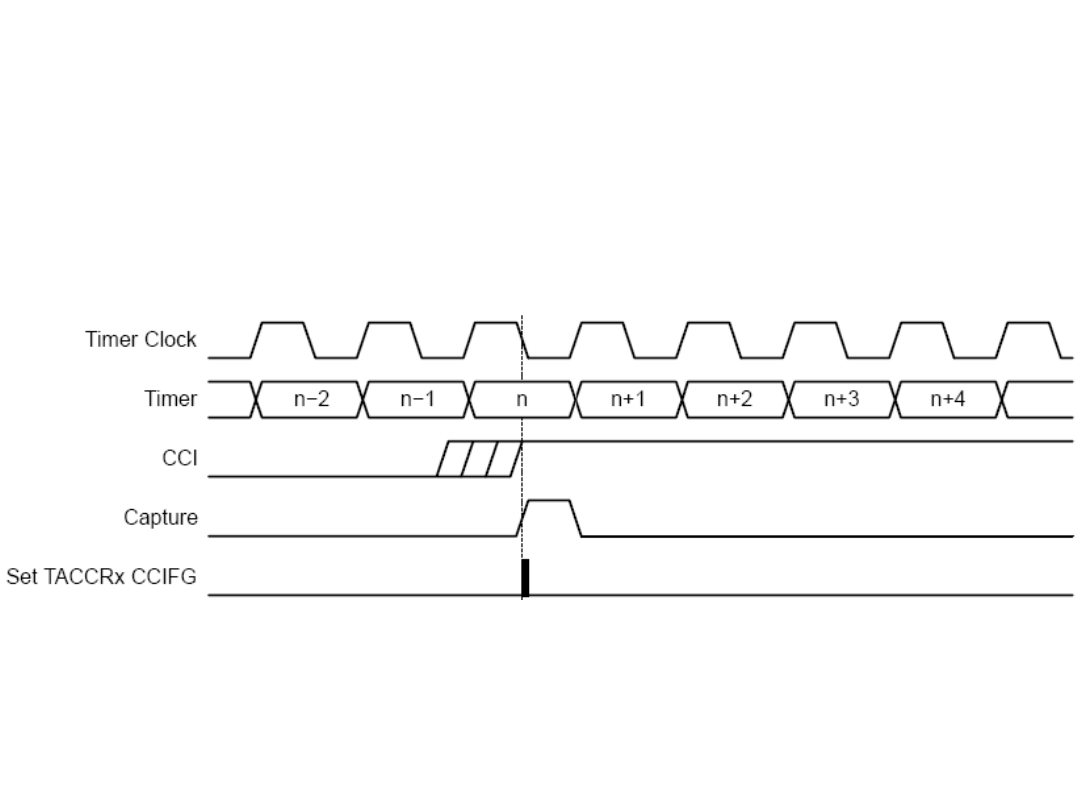

Tryb zatrzasku - znacznik CAP = 1

Rejestr zapamiętuje stan licznika pod wpływem impulsu zewnętrznego,

doprowadzonego do wejść CCIxA lub CCIxB. Można dobrać zbocze

narastające, opadające lub obydwa. Zalecana jest synchronizacja (SCS = 1)

momentu zatrzasku z sygnałem zegarowym licznika. Zatrzask można

wywołać również programowo.

Jeżeli stan rejestru nie zostanie odczytany przed wpisem kolejnej wartości,

to jest ustawiany znacznik przepełnienia COV.

Tryb porównania – znacznik CAP = 0:

Jeżeli wartość w liczniku dojdzie do wartości wpisanej do wybranego rejestru

TACCRx to:

- znacznik przerwania CCIFG = 1,

- znacznik EQUx = 1,

- znacznik EQUx ustawia wyjście w zależności od trybu wyjścia

- sygnał wejściowy CCI jest przepisywany do SCCI

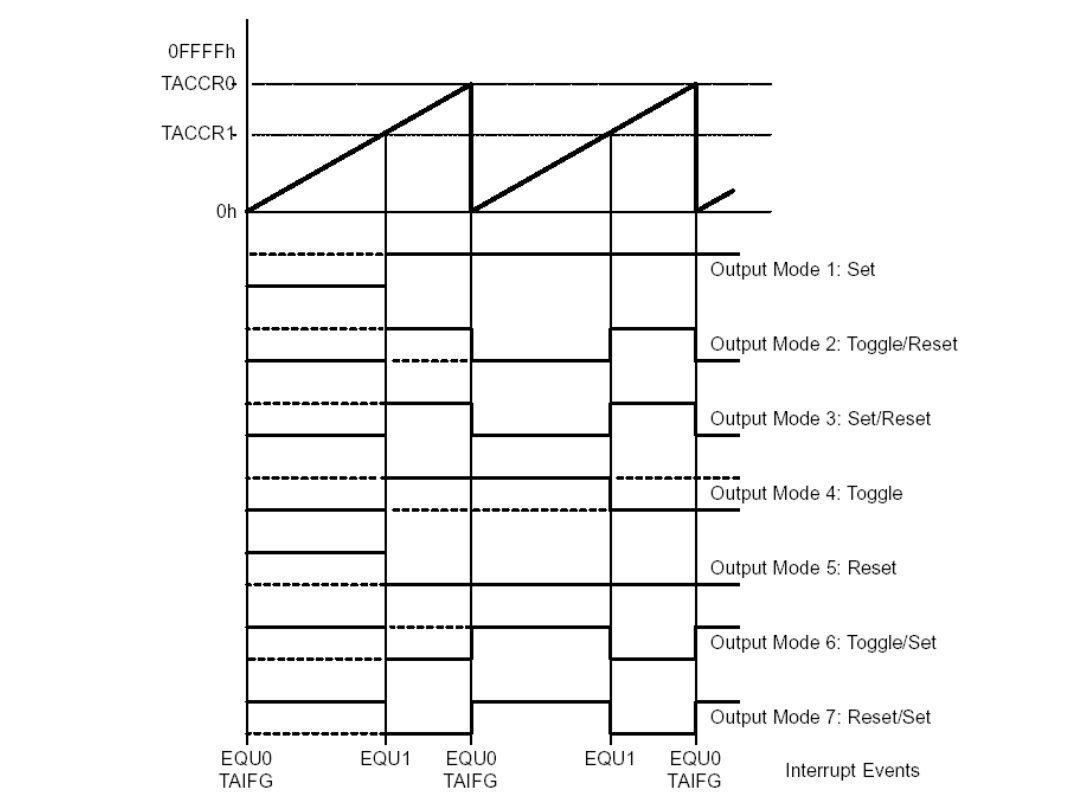

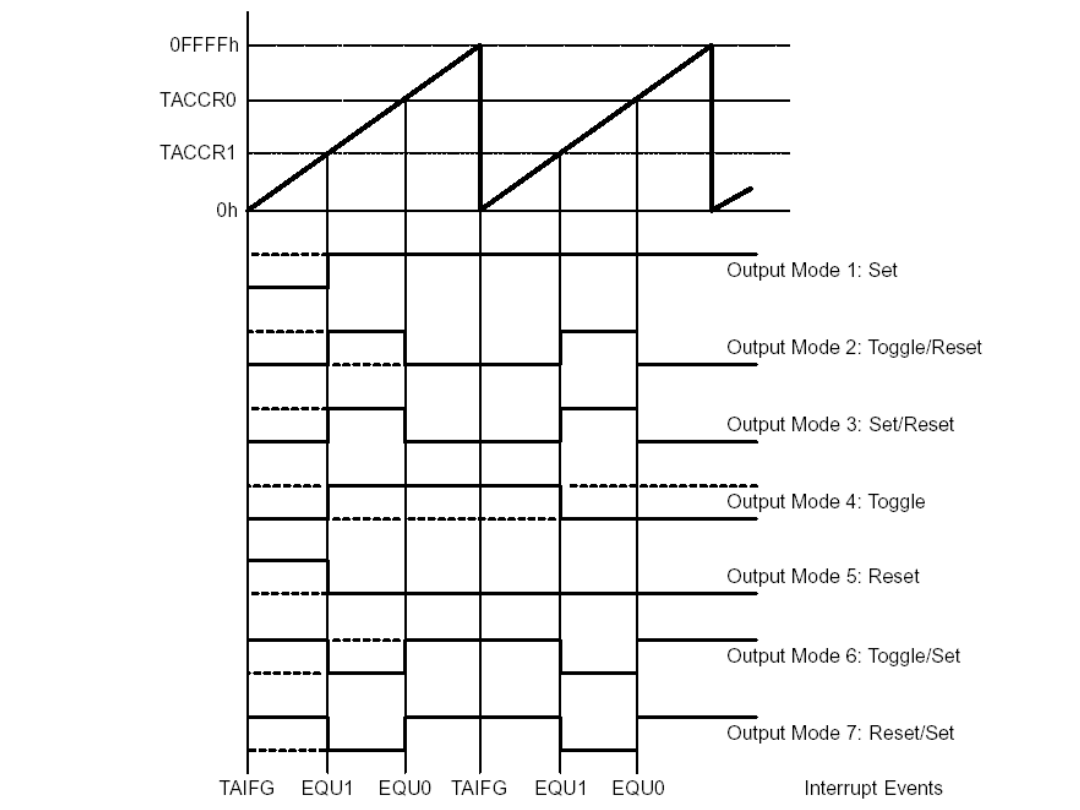

Układ wyjściowy:

Każdy blok komparator/zatrzask posiada układ wyjściowy do generowania

takich sygnałów wyjściowych jak np. PWM. Każdy układ wyjściowy może

pracować w jednym z ośmiu trybów, w których są generowane sygnały

oparte na sygnałach EQU0 i EQUx. Tryby wyjściowe są określane poprzez

ustawienie znaczników OUTMODx. Sygnał OUTx zmienia się wraz ze

zboczem narastającym sygnału zegarowego licznika dla wszystkich

trybów za wyjątkiem trybu 0. Tryby 2, 3,6 i 7 nie mają zastosowania dla

modułu 0, ponieważ EQUx = EQU0.

OUTMODx tryb

000 Output - sygnał wyjściowy OUTx jest określony stanem

znacznika OUTx

001 Set - wyjście jest ustawiane w stan 1 gdy stan licznika

osiągnie

wartość rejestru TACCRx. Stan ten trwa

do momentu resetu

licznika lub zmiany trybu wyjścia.

010 Toggle/Reset - stan wyjścia jest zmieniany na przeciwny gdy licznik

osiągnie

wartość rejestru TACCRx i zerowany gdy licznik

osiągnie stan rejestru TACCR0.

011 Set/Reset - wyjście jest ustawiane w stan 1 gdy stan licznika

osiągnie

wartość rejestru TACCRx i w stan 0 gdy

licznik osiągnie stan

rejestru TACCR0.

100 Toggle - stan wyjścia jest zmieniany na przeciwny gdy licznik

osiągnie

wartość rejestru TACCRx. Okres sygnału

wyjściowego ma

podwojoną wartość okresu licznika.

101 Reset - wyjście jest ustawiane w stan 1 gdy stan licznika

osiągnie

wartość rejestru TACCRx.

110 Toggle/Set - stan wyjścia jest zmieniany na przeciwny gdy licznik

osiągnie

wartość rejestru TACCRx i ustawiany gdy

licznik osiągnie stan

rejestru TACCR0.

111 Reset/Set - wyjście jest ustawiane w stan 0 gdy stan licznika

osiągnie

wartość rejestru TACCRx i w stan 1 gdy

licznik osiągnie stan

rejestru TACCR0.

Przerwania:

wartość przerwania

- źródło

- priorytet

00h

- brak przerwania

02h

- CCIFG - TACCR1

- najwyższy

04h

- CCIFG - TACCR2

06h

- CCIFG - TACCR3

08h

- CCIFG - TACCR4

0Ah

- TAIFG - przepełnienie licznika

0Ch

- rezerwa

0Eh

- rezerwa

- najniższy

Wartość przerwania jest wpisywana do rejestru

TAIV

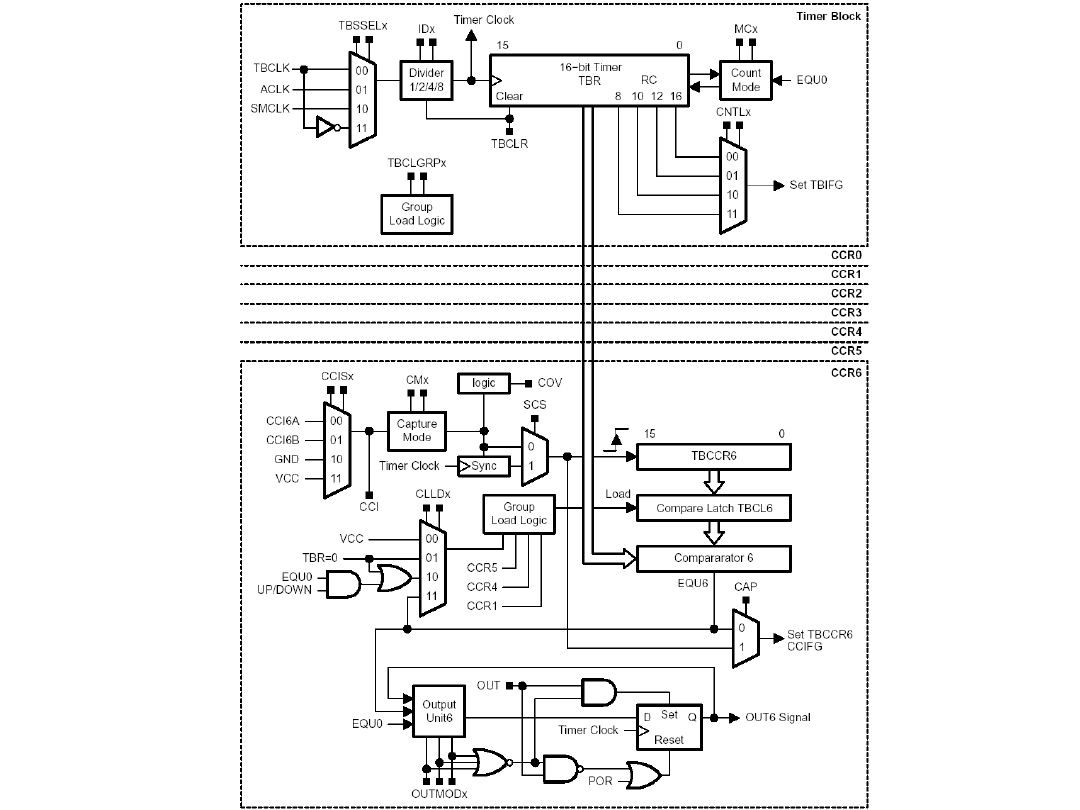

Timer_B

Timer_B jest identyczny z Timer’em A z następującymi wyjątkami:

• długość licznika B może być programowana jako 8, 10, 12 lub 16

bitów

• rejestry TBCCRx są podwójnie buforowane i mogą być grupowane

• wszystkie wyjścia Timera_B mogą być ustawione w stan wysokiej

impedancji

• funkcja znacznika SCCI nie jest zaimplementowana w Timerze_B

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

Wyszukiwarka

Podobne podstrony:

FUNKCJA EXCEL (JEZELI, LICZ, SU Nieznany

PRZEGR 1, Sprawdzi˙ pod wzgl˙dem cieplno-wilgotno˙ciowym przegrod˙ budowlan˙ pionow˙ o nast˙puj˙cym

pk licz nat 5

licz scyn1, Wprowadzenie teoretyczne

pan wołodyjowski, 37, Oddzia˙ Czeremis˙w kilkana˙cie koni licz˙cy szed˙ w mili naprz˙d, by drog˙ opa

Licz do 6

lekcja 24 Licz najbardziej za siebie

Licz gm, LABORATORIUM FIZYKI

LICZ 8

tab licz

Nie licz baranów, S E N T E N C J E, E- MAILE OD PANA BOGA

licz do - bajka, dla dzieci i o dzieciach

MSP7

Protokol transmisji danych licz Nieznany

Licz i Koloruj, Nauka Liczenia

Charakterystyki statyczne pneumatycznych elementow licz cych

Nie licz lat i dni

Licz

PROJEKT CAMELOT 2012 ROK budoj tunele zbieraj zywnosc nie licz na pomoc rzadu

więcej podobnych podstron