Pętla PLL

mk

Pętla sprzężenia fazowego (ang. phase-

locked loop - PLL) - sposób synchronizacji

pośredniej;

Pętla zawiera generator przestrajany

napięciem VCO

(ang. voltage controlled oscillator).

Błąd fazy - potrzebny do wytworzenia w

detektorze fazy sygnału do odpowiedniego

odstrojenia generatora VCO w celu

utrzymania równości częstotliwości

Układy PLL są używane, np.

do synchronizacji generatorów

do przemiany częstotliwości, tj. w układach

modulacji i demodulacji AM, FM, i PM,

w syntezerach częstotliwości i powielaczach

w dzielnikach częstotliwości

w dekoderach sygnału stereofonicznego,

w modulatorach i demodulatorach AM, FM

PWM, itd

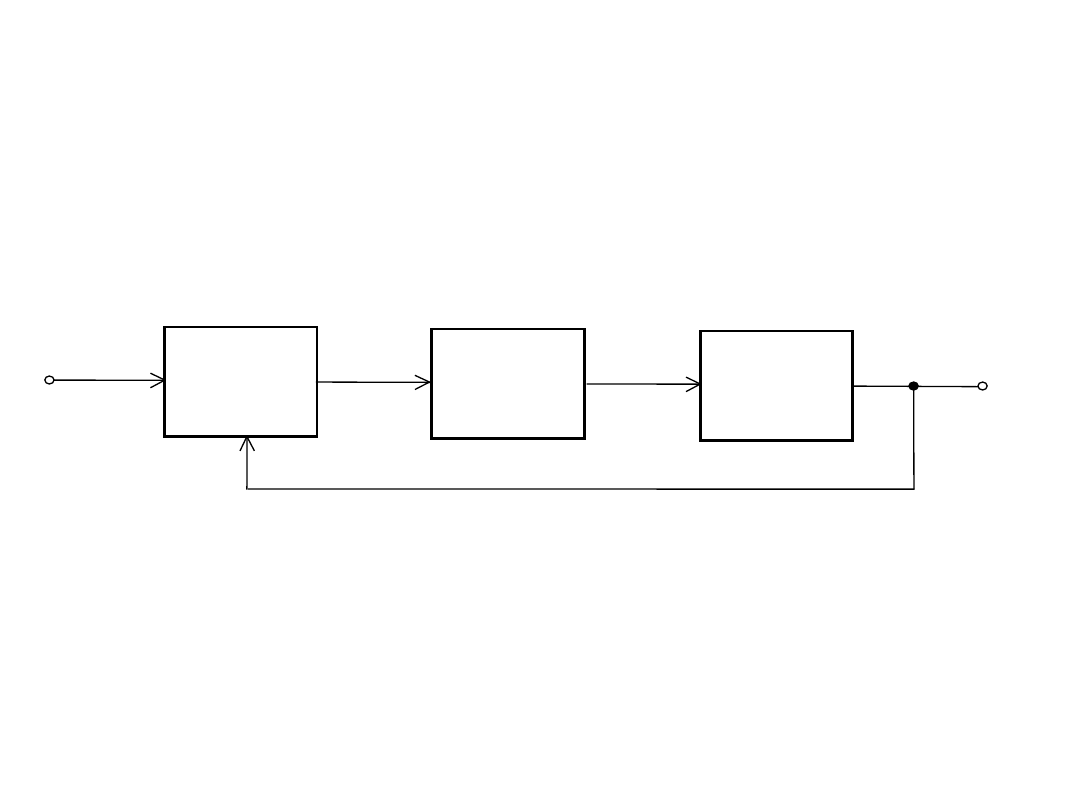

Struktura pętli fazowej

u

i

(t) u

d

(t) u

g

(t) u

0

(t)

i

(t)

0

(t )

DF

VCO

Filtr

[rad] [V/rad] [V] [V/V] [V] [rad/Vs] [rad]

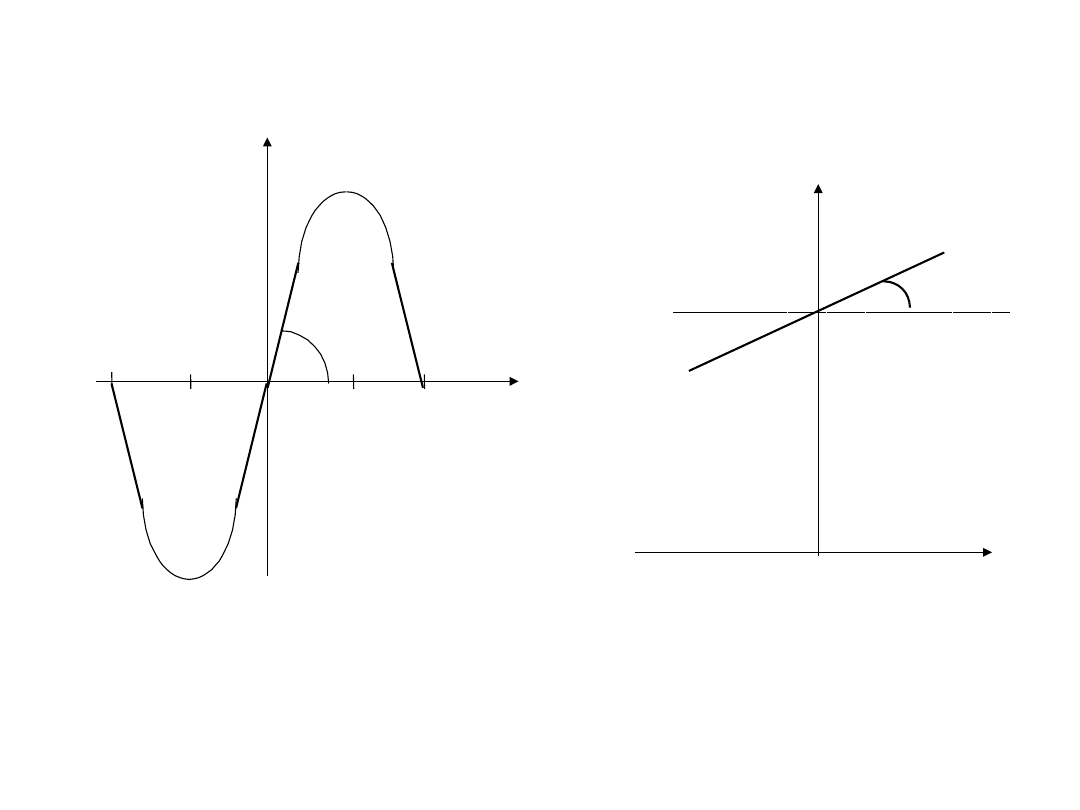

Charakterystyka mnożącego detektora fazy Charakterystyka przestrajania generatora VCO

-

f

e

arctg Kd

Ud

U

dmax

/2

-

/2

ug

0

arctg K

g

0

g

-U

dmax

)

t

(

t

sin

U

)

t

(

u

i

0

i

i

)

t

(

t

cos

U

)

t

(

u

g

0

g

0

gdzie:

0

- pulsacja własna generatora VCO

)

t

(

)

t

(

t

2

sin

)

t

(

)

t

(

sin

2

U

U

k

)

t

(

u

g

i

0

g

i

g

i

i

d

gdzie: k

i

- stała detektora fazy[1/V]

s. wejściowy

s. wyjściowy

Sygnał na wyjściu mnożącego detektora fazy:

)

t

(

sin

K

)

t

(

)

t

(

sin

K

)

t

(

u

e

d

g

i

d

d

e

max

d

e

d

sin

U

)

(

u

)

t

(

)

t

(

)

t

(

g

i

e

- błąd fazy

2

U

U

k

K

g

i

i

d

- wzmocnienie detektora fazy

U

dmax

- maksymalne napięcie detektora fazy

)

t

(

)

t

(

g

0

g

)

t

(

u

K

)

t

(

dt

d

)

t

(

g

g

g

g

K

g

- transmitancja (czułość przestrajania) generatora VCO

wyrażona w rad/Vs

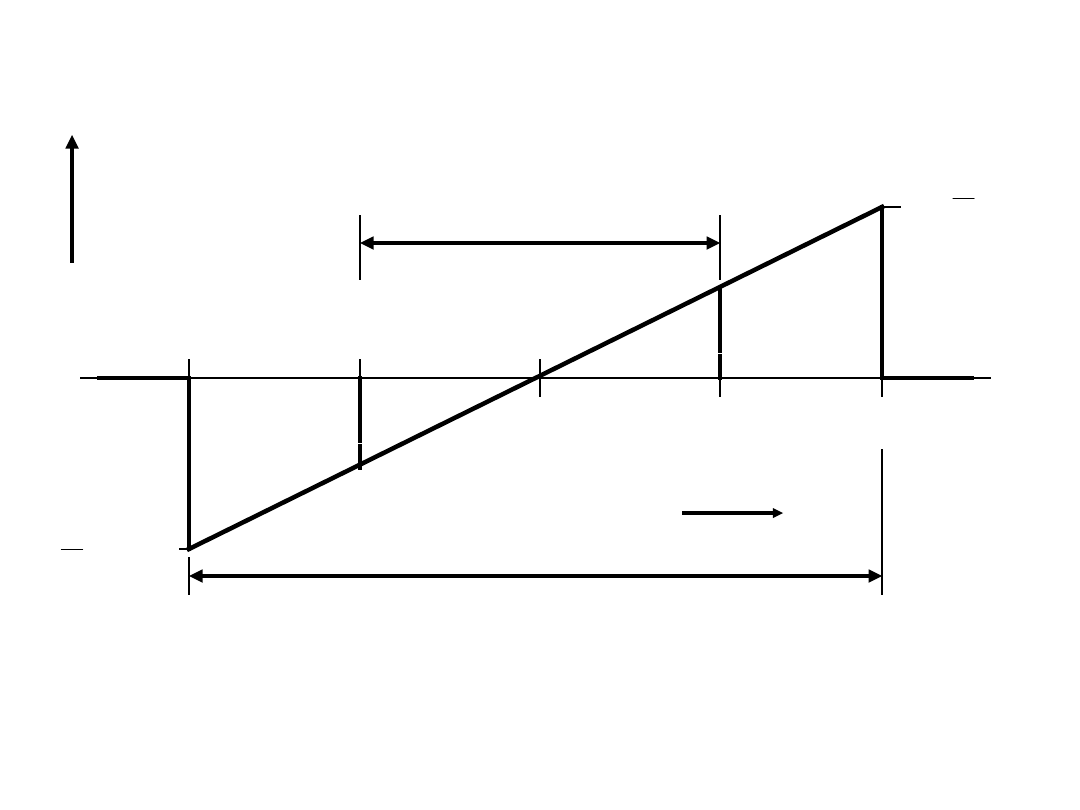

Przestrajanie generatora VCO

ug

0

arctg K

g

0

g

Maksymalna

różnica

częstotliwości

sygnału

wejściowego i częstotliwości własnej generatora

VCO, przy której układ PLL może dojść do

synchronizmu, jest nazywana

zakresem chwytania synchronizacji f

C

.

Maksymalna różnica częstotliwości między

częstotliwością przebiegu wejściowego i

częstotliwością własną generatora, przy której

układ PLL może utrzymać synchronizm, jest

nazywana zakresem trzymania synchronizacji f

L

G

max

d

L

K

U

- przy transmitancji filtru dla

napięcia stałego równej jedności

(u

g

=U

dmax

)

df

)

j

(

)

j

(

B

2

0

i

g

n

- pasmo szumowe pętli PLL

U

S

-

napięcie

przestrajaj

ące

generator

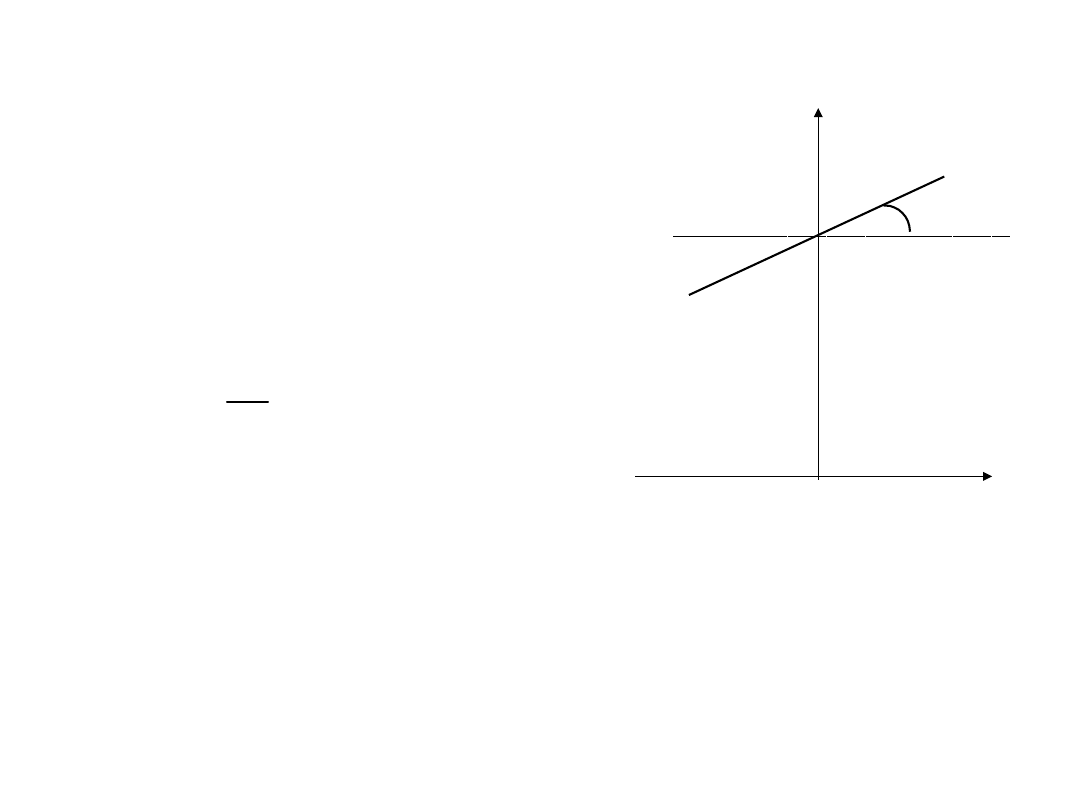

2ω

Z

= zakres

zaskoku

ω

0

-ω

L

ω

0

ω

0

+

ω

Z

ω

0

+ω

L

A

K

2

π

Φ

2ω

L

= zakres trzymania

nachylenie=1/

K

V

ω

I

Zakres trzymania oraz

zaskoku

ω

0

- ω

Z

A

K

2

π

Φ

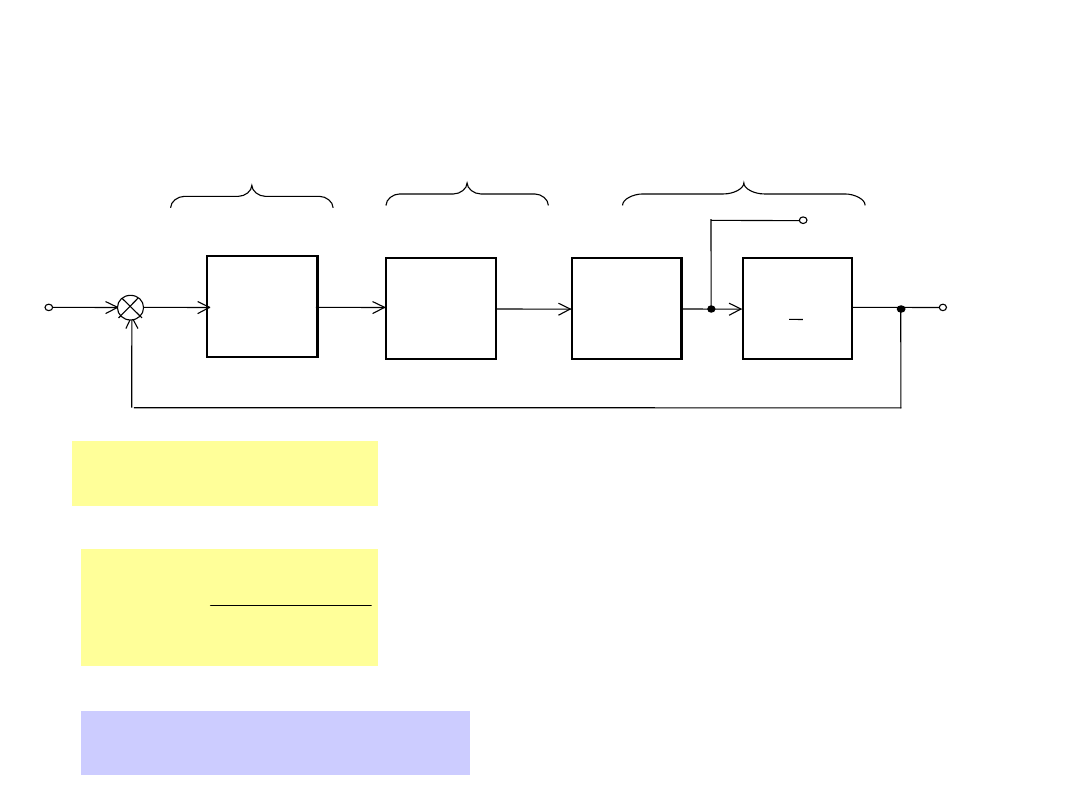

Liniowy model pętli fazowej w stanie synchronizmu

)

s

(

H

)

s

(

)

s

(

i

g

)

s

(

KF

s

)

s

(

KF

)

s

(

H

)

s

(

H

1

)

s

(

)

s

(

i

e

K=K

d

K

g

- wzmocnienie w pętli [1/s]

- błąd fazy

g

(s)

i

(s) +

e

(s) u

d

(s) u

g

(s) Faza

K

d

1

s

K

g

F(s)

[V/rad] [V/V] [rad/V

S

]

Pulsacja

g

(s)

Detektor fazy Filtr VCO

)

t

cos(

)

t

(

0

i

i

)

t

cos(

)

t

(

0

0

g

)

(

sin

j

)

(

cos

)

(

)

(

)

j

(

)

j

(

)

j

(

H

i

0

i

0

W stanie synchronizmu zachodzą związki:

x

t

0

g

g

x

g

dt

)

t

(

u

K

)

t

(

s

1

K

)

s

(

u

)

s

(

g

g

g

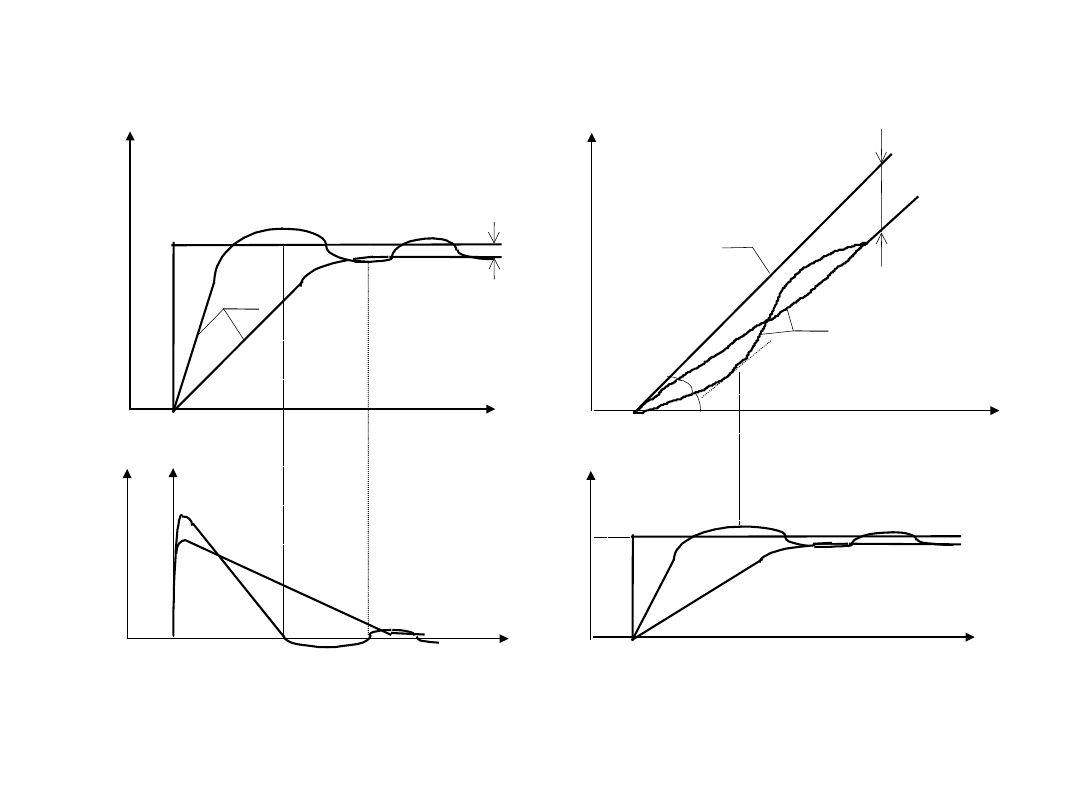

a) przy skoku jednostkowym fazy przebiegu

wejściowego;

b) przy skoku jednostkowym częstotliwości przebiegu

wejściowego

Przebiegi fazy i częstotliwości na wejściu i wyjściu pętli PLL

a) b)

e

()

t

t

g

i

g

i

g

g

i

i

t

t

i

g

i

g

g

i

0

0

e

()

K

s

K

)

s

(

H

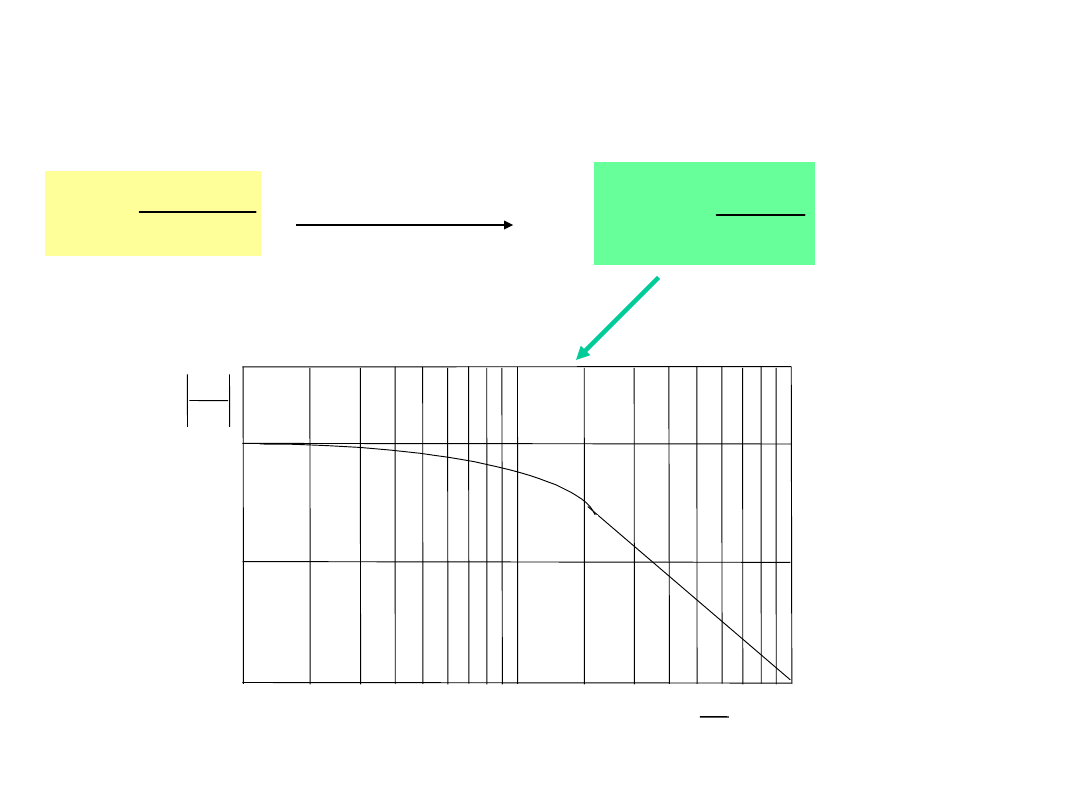

Pętla bez filtru DP - pętla pierwszego rzędu

)

s

(

KF

s

)

s

(

KF

)

s

(

H

F(s)=1

Charakterystyka amplitudowo-cz

ęstotliwościowa pętli PLL bez filtru

0,1

1

10

10

20

0

0

i

K

dB

2

n

n

2

i

g

s

2

s

)

s

(

L

)

s

(

)

s

(

)

s

(

H

)

s

(

KF

s

)

s

(

KF

)

s

(

H

Pętla drugiego rzędu

F(s)= filtr I rzędu

Pętla z filtrem I rzędu przekształca się w pętlę drugiego rzędu.

Układ drugiego rzędu może być niestabilny

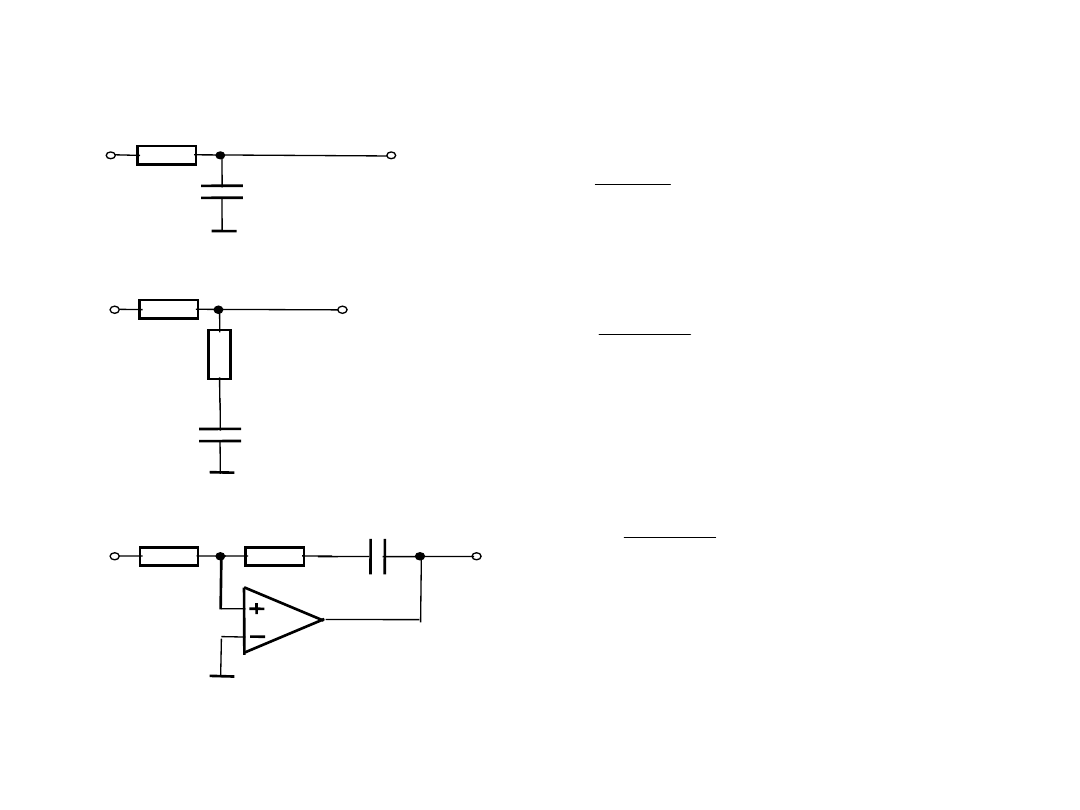

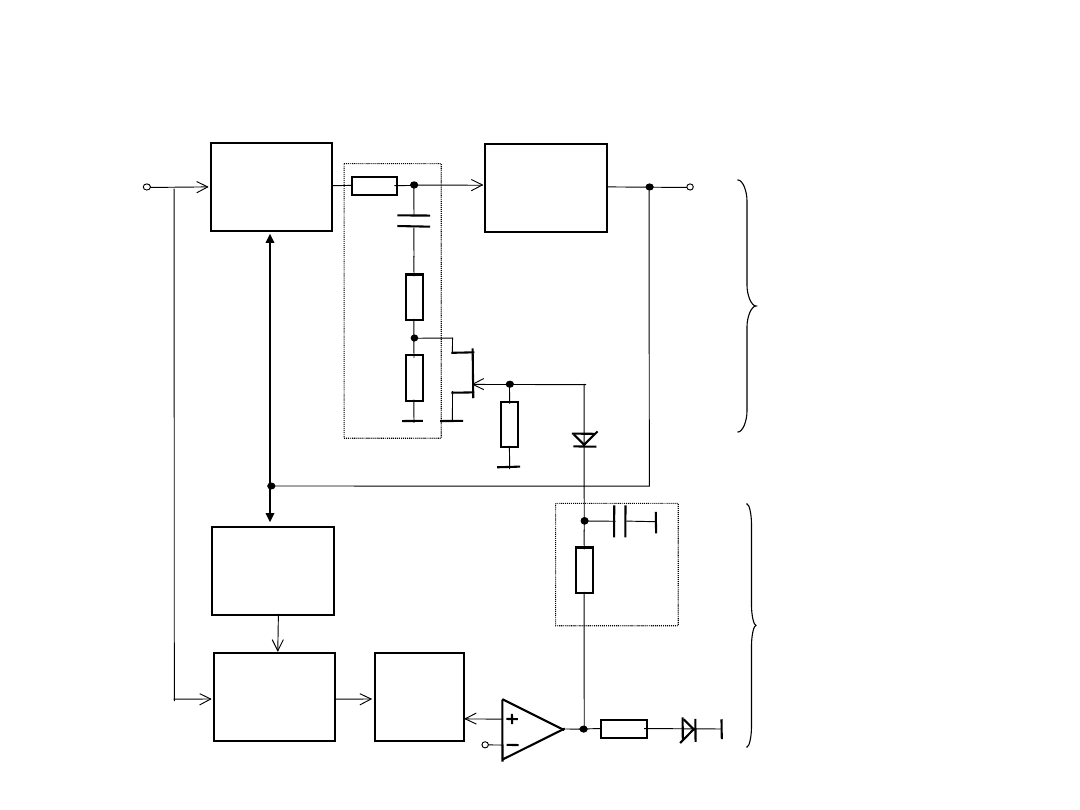

Typowe filtry I rzędu stosowane w pętlach PLL

a) filtr dolnoprzepustowy RC; b) filtr proporcjonalno-

calkujący; c) filtr aktywny proporcjonalno-całkujący

a)

b)

c)

R

R

2

C

R

1

C

R

2

R

1

C

s

1

1

)

s

(

F

C

R

C

)

R

R

(

s

1

s

1

)

s

(

F

2

2

2

1

1

1

2

C

R

C

R

s

s

1

)

s

(

F

2

2

1

1

1

2

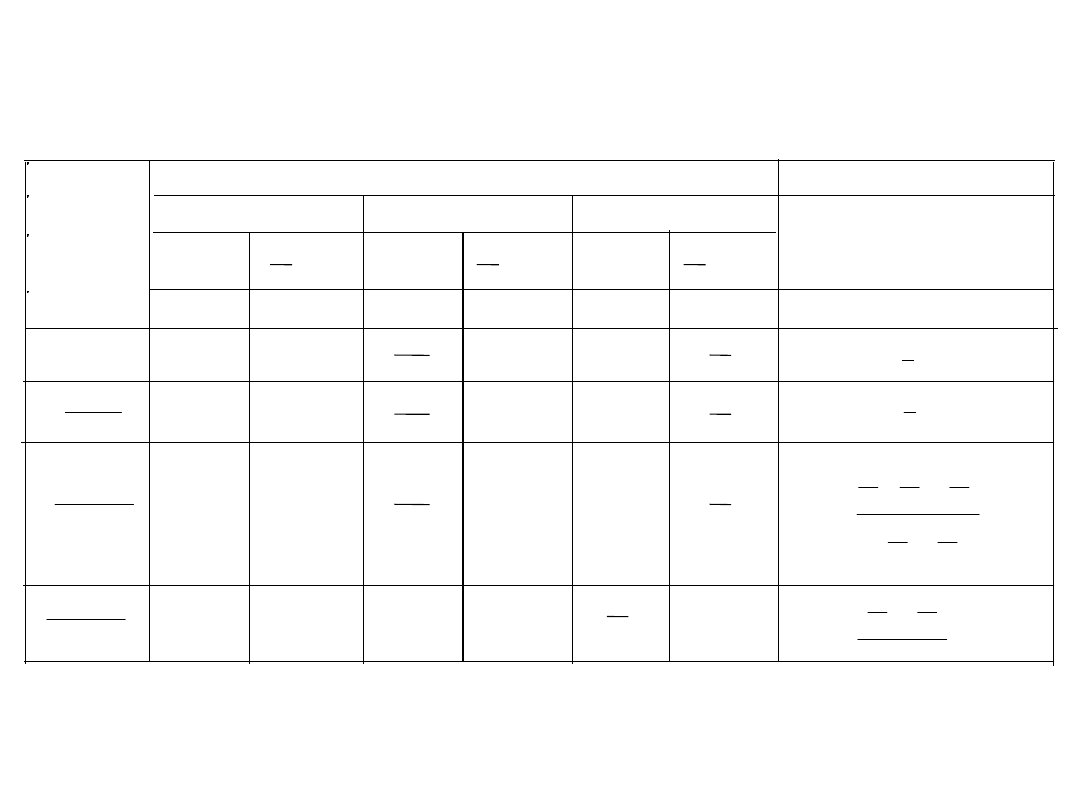

Statyczny błąd fazy, szybkość narastania błędu fazy oraz pasmo

szumowe pętli

Filtr

Błąd fazy

Pasmo szumowe

i

t

t

( )

( )

1

i

t

t t

( )

( )

1

i

t

t

t

( )

,

( )

05

1

2

F(s)

e

( )

d

dt

e

( )

e

( )

d

dt

e

( )

e

( )

d

dt

e

( )

B

n

rad

rad/s

rad

rad/s

rad

rad/s

Hz

1

0

0

K

0

K

0

0

K

0

K

0

0

K

0

K

0

0

0

0

K

0

4

k

4

k

2

1

2

2

1

2

1

2

1

k

4

1

k

k

4

1

k

2

1

2

s

1

1

1

2

s

1

s

1

1

2

s

s

1

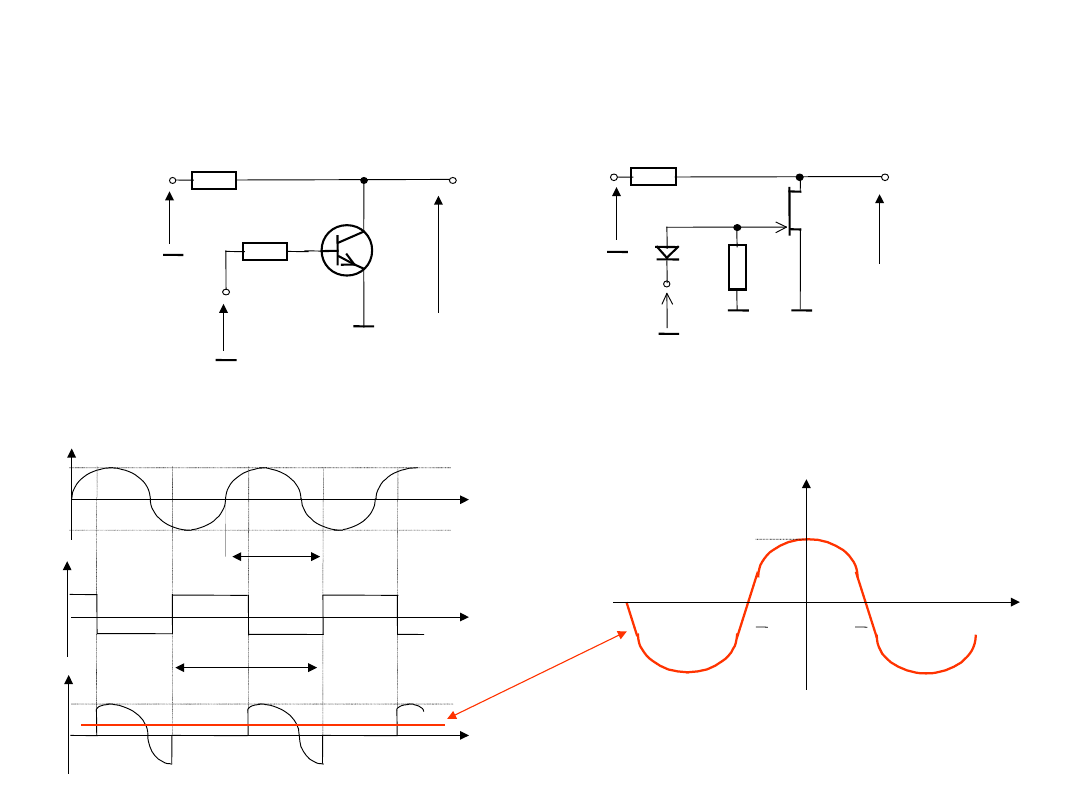

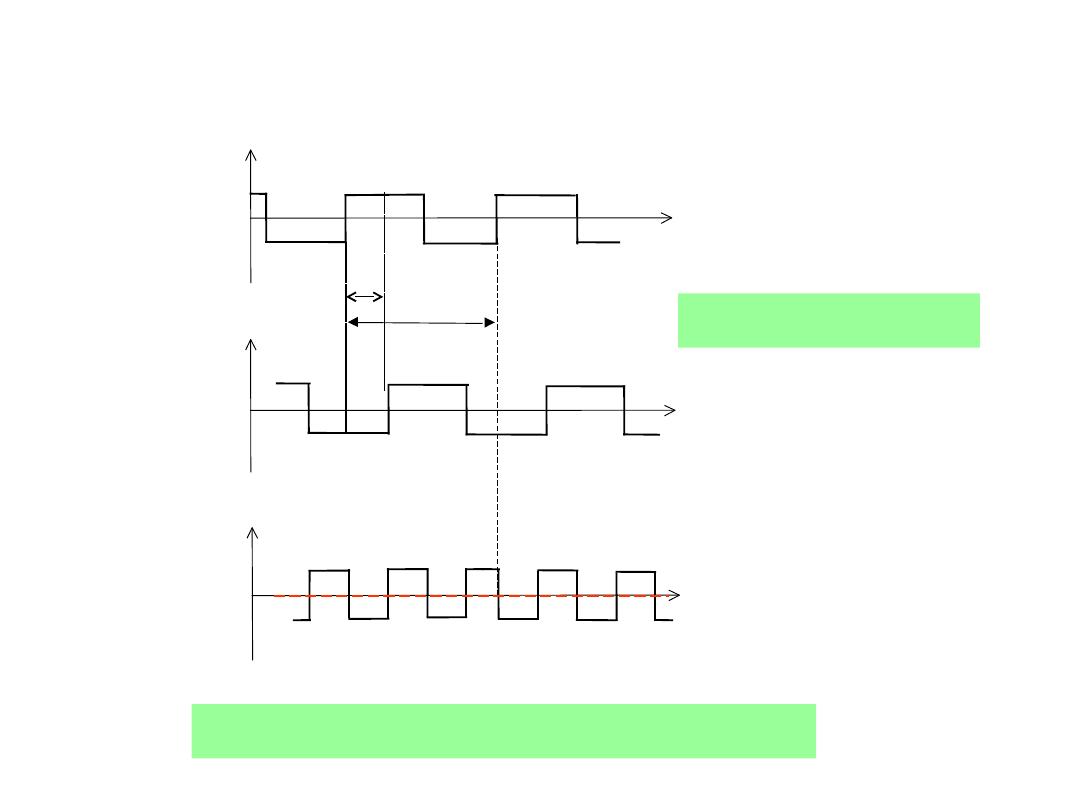

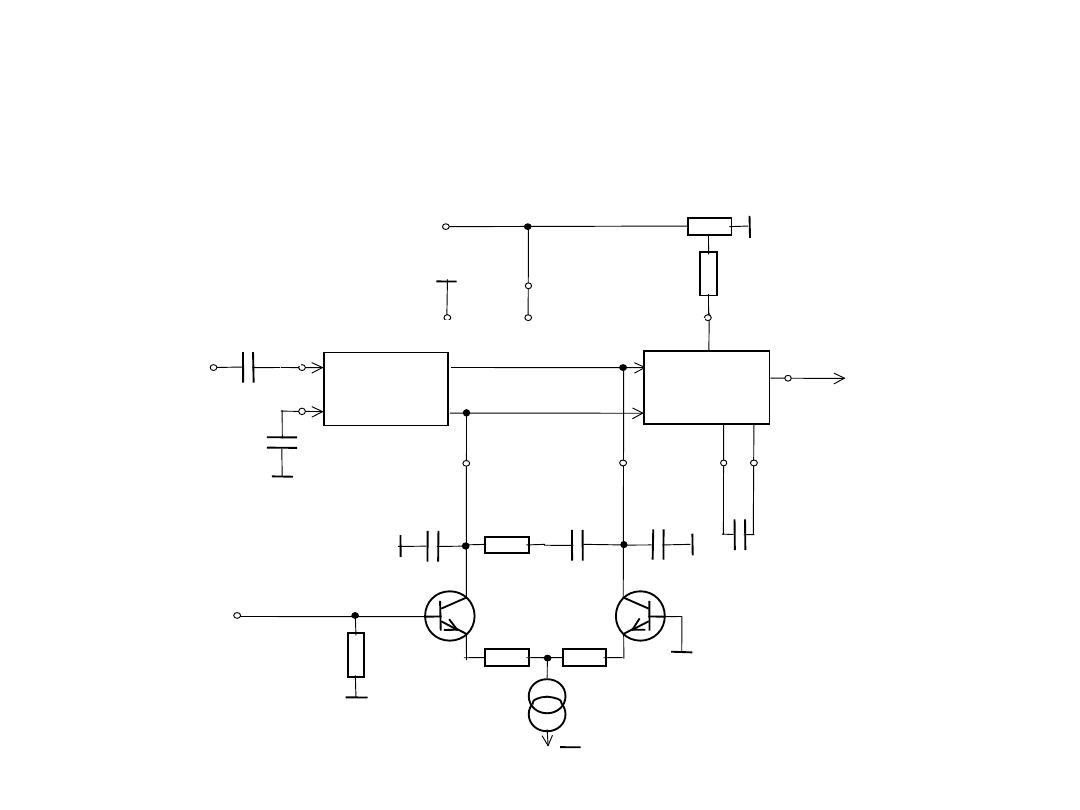

Detektory fazy mnożący z kluczem tranzystorowym

RG

R

R

RB

ui(t)

ug(t)

ud(t)

ud(t)

ug(t)

ui(t)

t

t

t

0

0

0

Dt

T

ud

ug

ui

- p

2

p

2

Ud

U

dmax

-udmax

0

p

-p

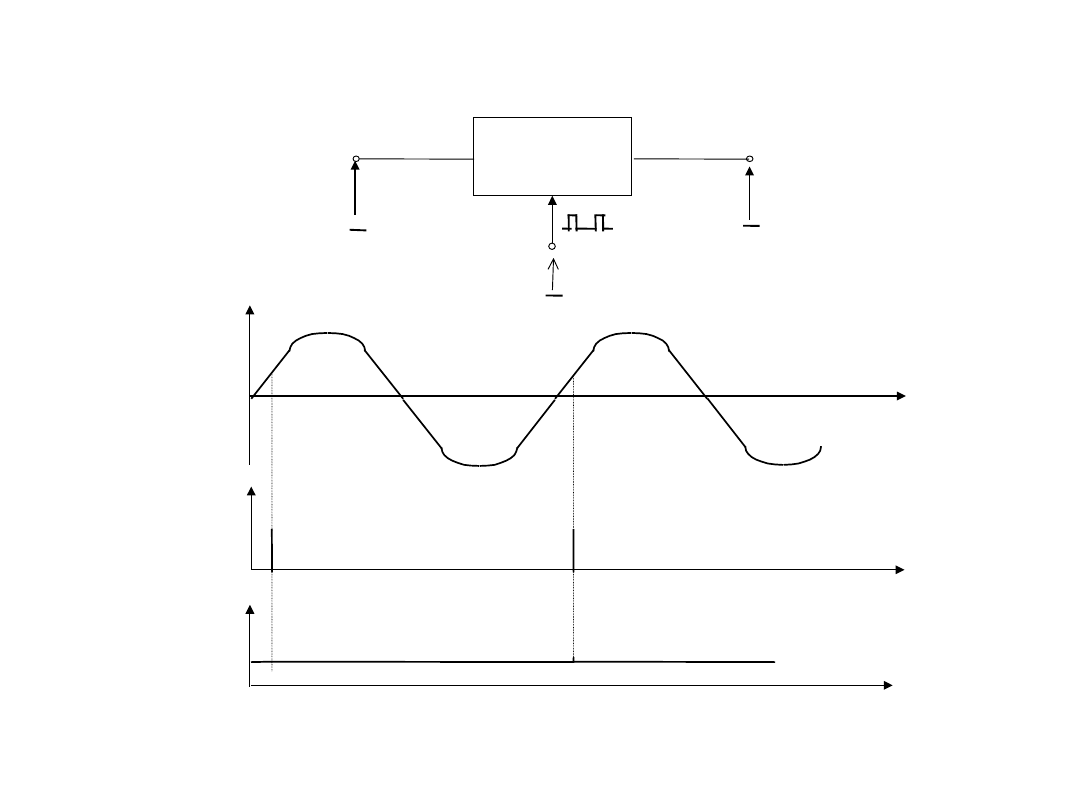

Detektor fazy z układem S/H

Przebiegi w det. fazy S/H w stanie synchronizmu

Układ

próbkująco-

-pamiętający

~

u

i

(t)

u

d

(t)

u

g

(t)

a)

u

i

t

t

t

0

u

d

u

g

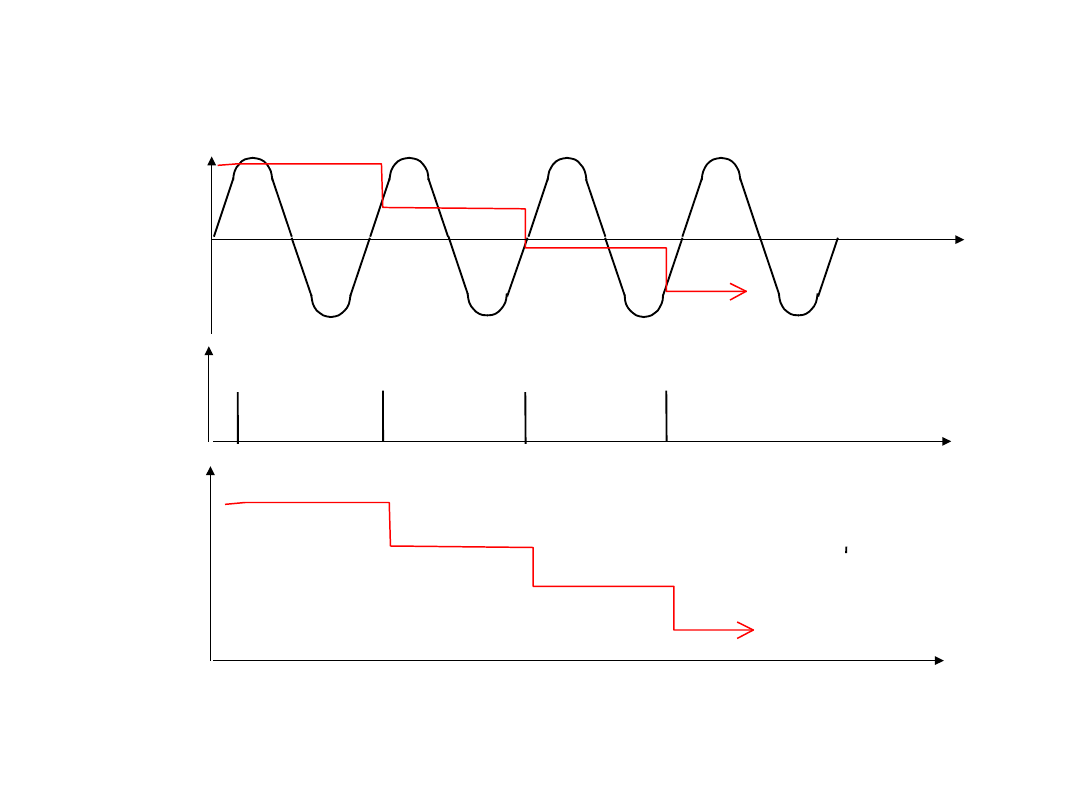

Detektor fazy z układem S/H

Przebiegi w det. fazy S/H przy braku synchronizmu

ui

t

t

t

0

ud

ug

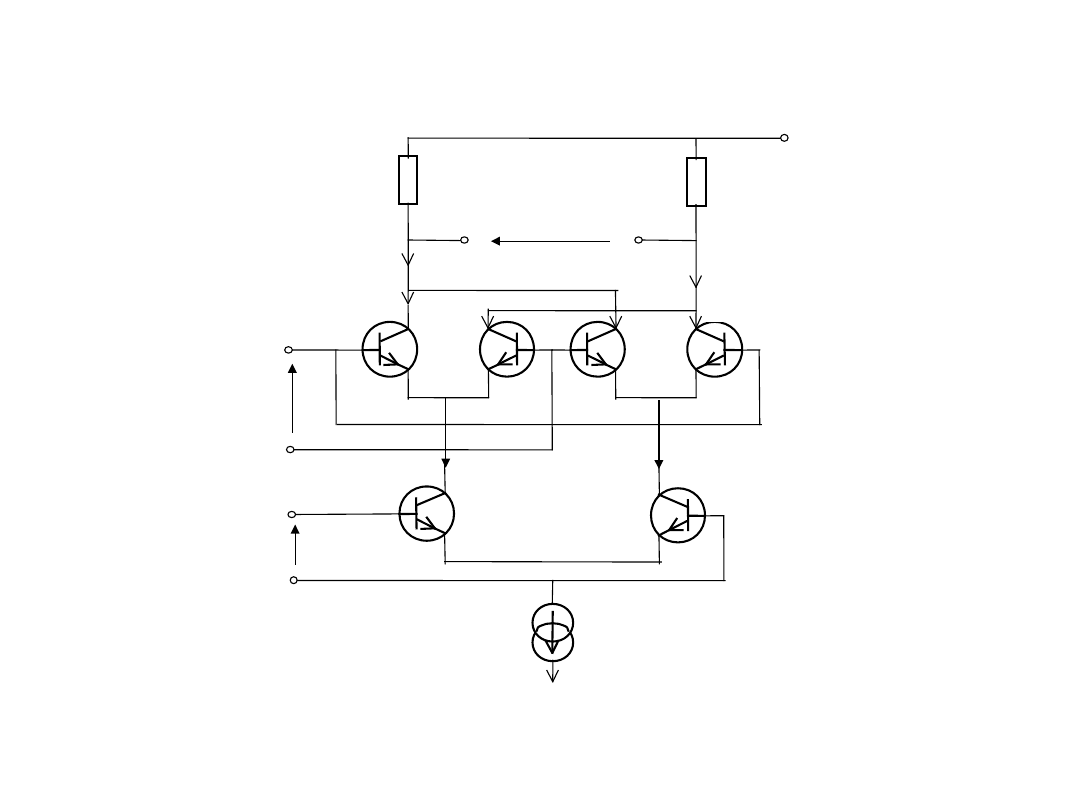

Detektor fazy mnożący z mnożnikiem transkonduktancyjnym

Schemat mnożnika transkonduktancyjnego

R

C

R

C

u

d

+U

CC

u

i

u

g

I

E

T6

T5

T4

T3

T

2

T

1

i

c1

i

c2

i

2

i

c5

i

cC

i

c4

i

1

Detektor fazy mnożący z mnożnikiem transkonduktancyjnym

Przebiegi w układzie

Przebiegi przy braku synchronizmu

t

IERC

t

t

t

0

0

0

ui

ug

ud

- I

ERC

T

u

d śr

<0

Detektor fazy mnożący z mnożnikiem transkonduktancyjnym

Przebiegi w układzie

t=T/4

IERC

t

t

t

0

0

0

ui

ug

ud

- I

ERC

T

Przebiegi w stanie synchronizmu

Błąd fazy = 90

0

u

d śr

=0

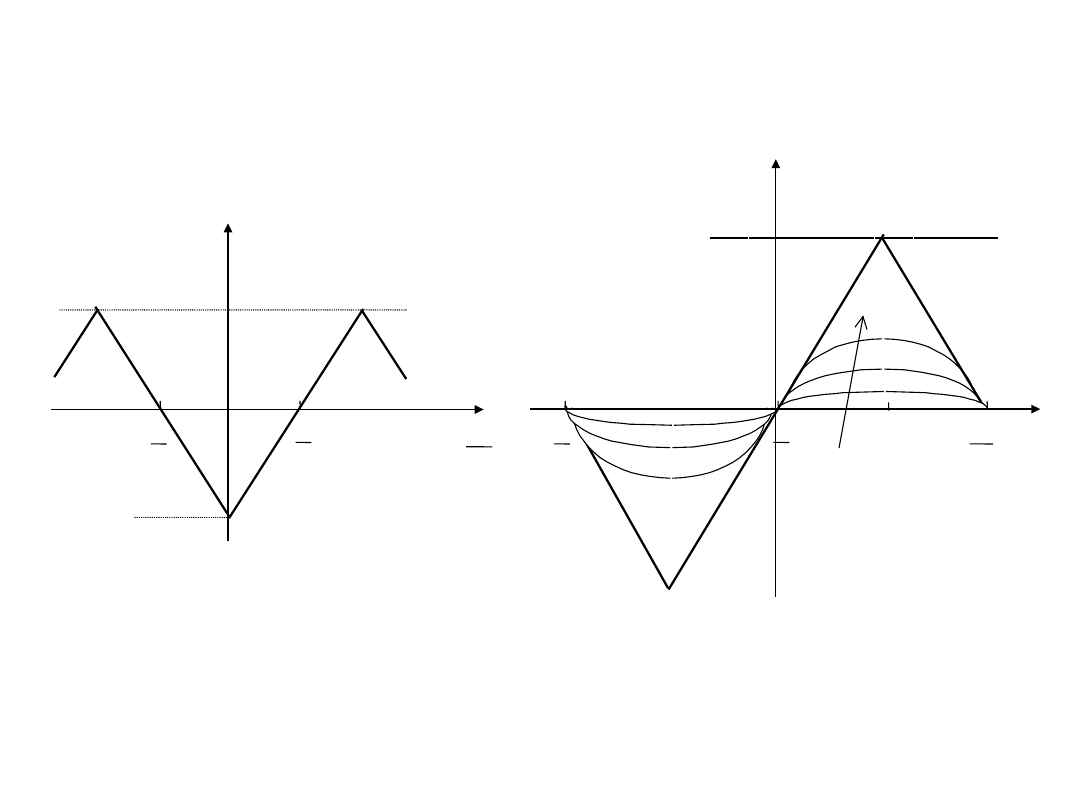

Charakterystyki przejściowe detektora fazy z mnożnikiem

Przy prostokątnych sygnałach sterujących Przy sinusoidalnych sygnałach sterujących

2

2

2

2

U

dmax

=I

E

RC

U

dmax

=I

E

RC

-I

E

RC

-I

E

RC

U

d

U

d

U

i

,U

g

e

e

t

T

2

3

2

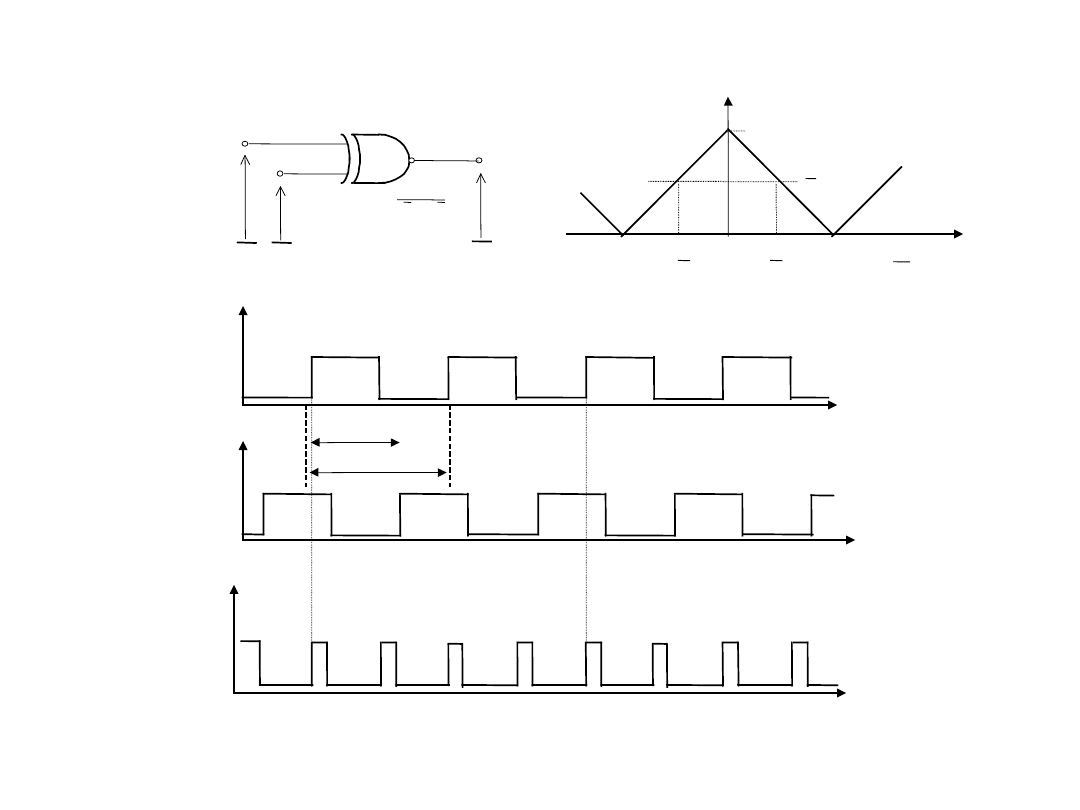

a) schemat; b) przebiegi; c)charakterystyka przej

ściowa

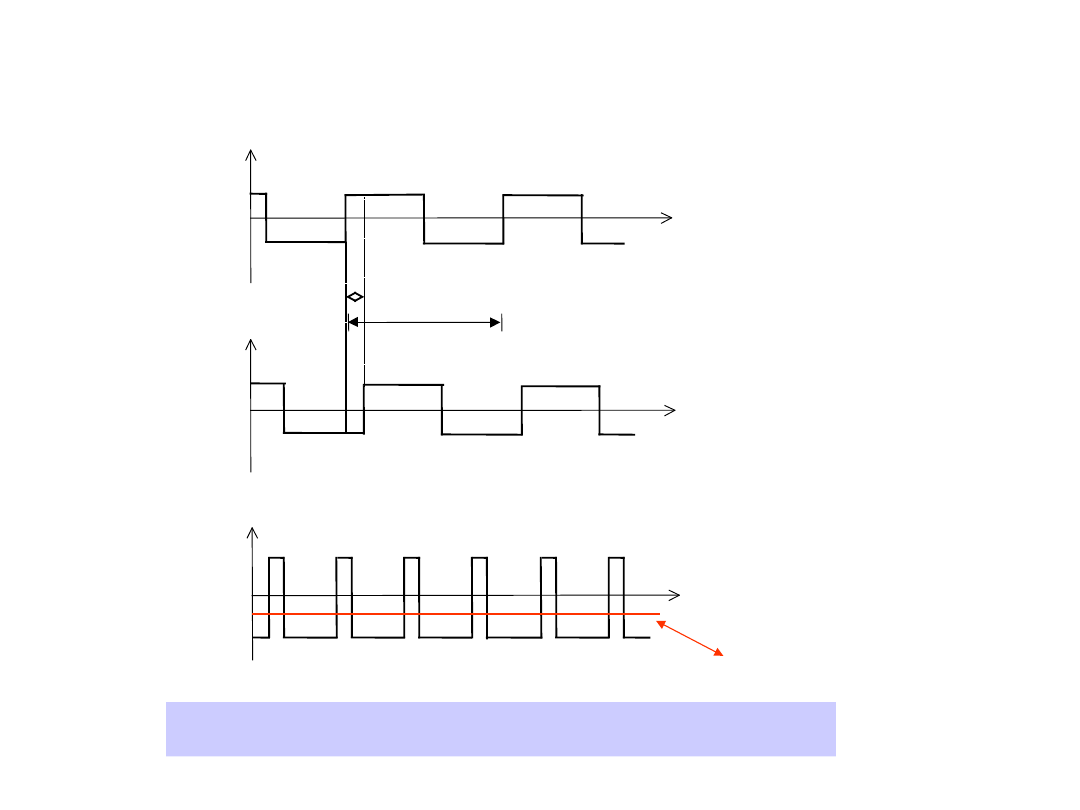

Detektor fazy z układem EX-NOR

a)

c)

b)

u

i

(t)

u

d

(t)

u

g

(t)

A

B

F

F=AB+BA

u

d

U

H

1

2

U

H

0

2

2

e

t

T

2

t

t

u

d

U

H

T

t

u

i

t

u

g

D Q

A

C

R

D R Q

B

C

R

R

R

R

u

QA

u

QB

u

g(t)

u

i(t)

u

d(t)

1

1

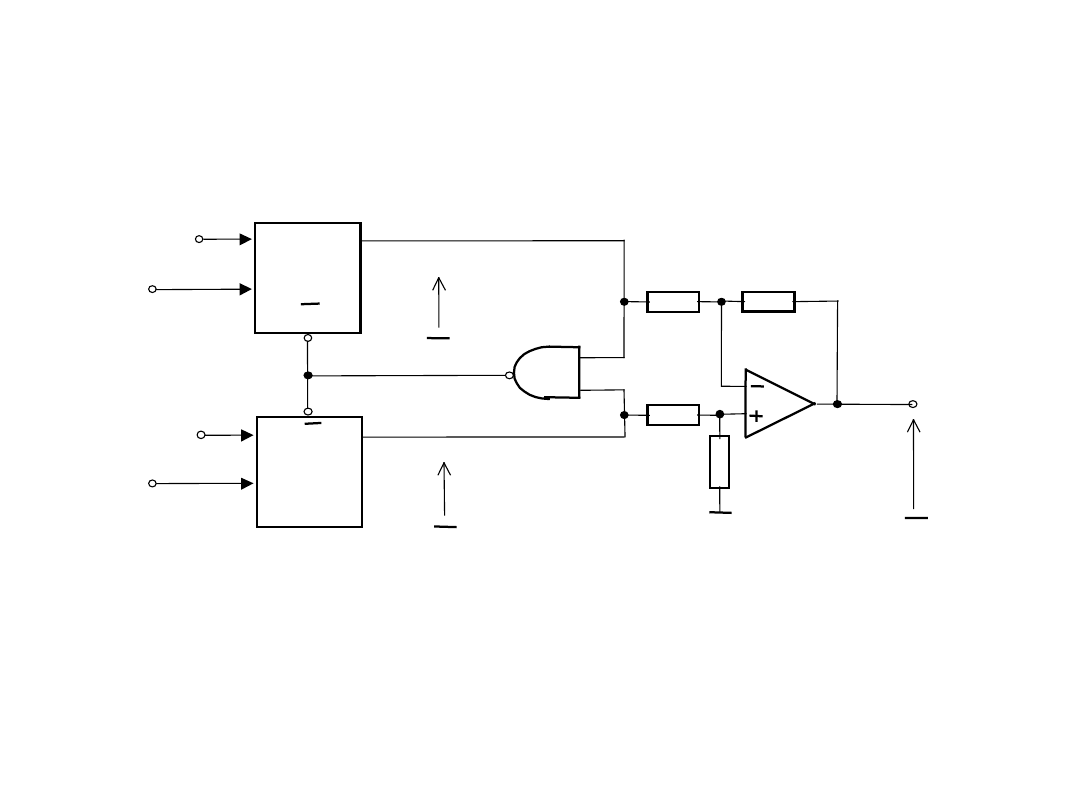

Detektor fazy - czestotliwości

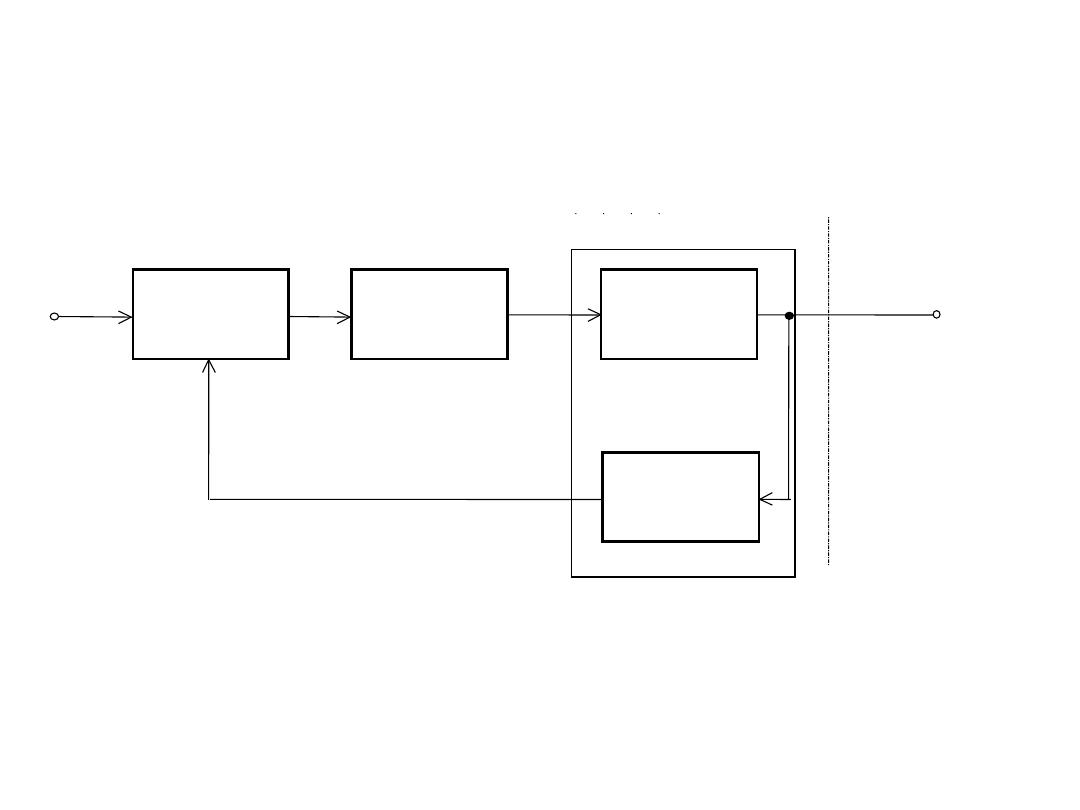

Układy poszerzające zakres chwytania synchronizacji pętli PLL

g

=(t)+90

Komparator

R

1

C

R

2

R

3

R

6

R

f

C

f

Detektor

fazy

DF1

90

VCO

Detektor

fazy

DF2

Filtr2

LED

Filtr3

D

T

g

(t)

Filtr1

u

g

u

i

PLL

uk ad

ekcjisynchroniz

acji

ł

det

Przykłady zastosowań pętli PLL

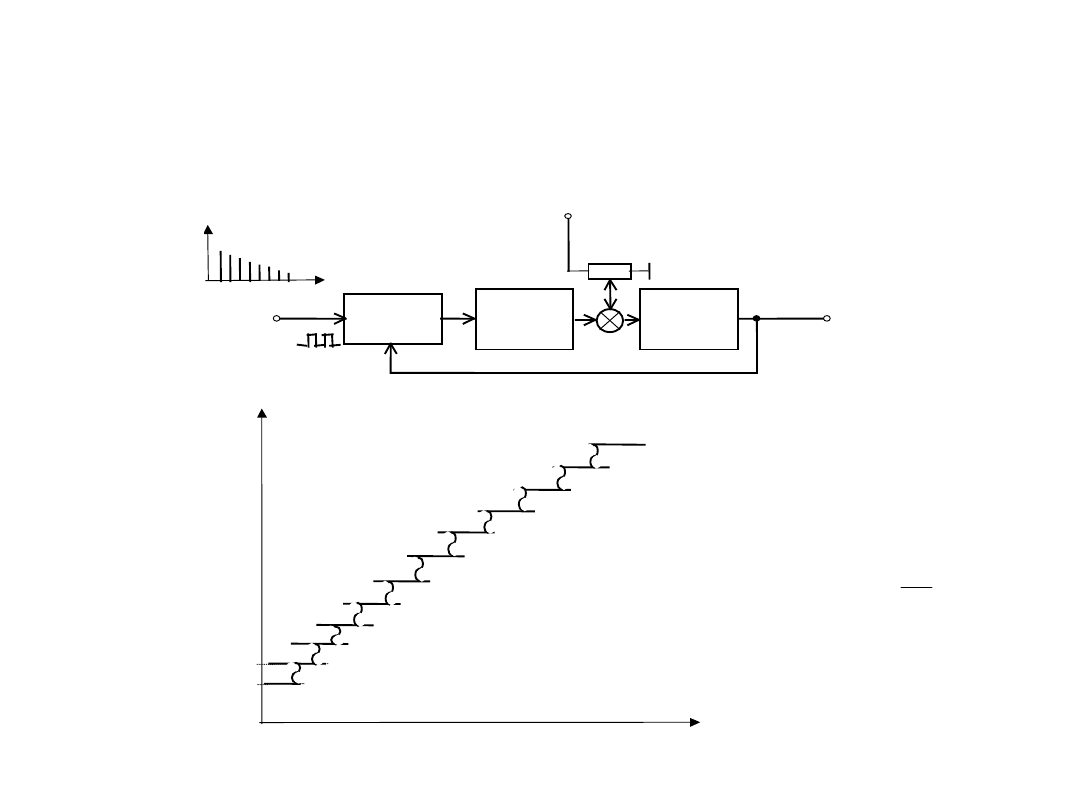

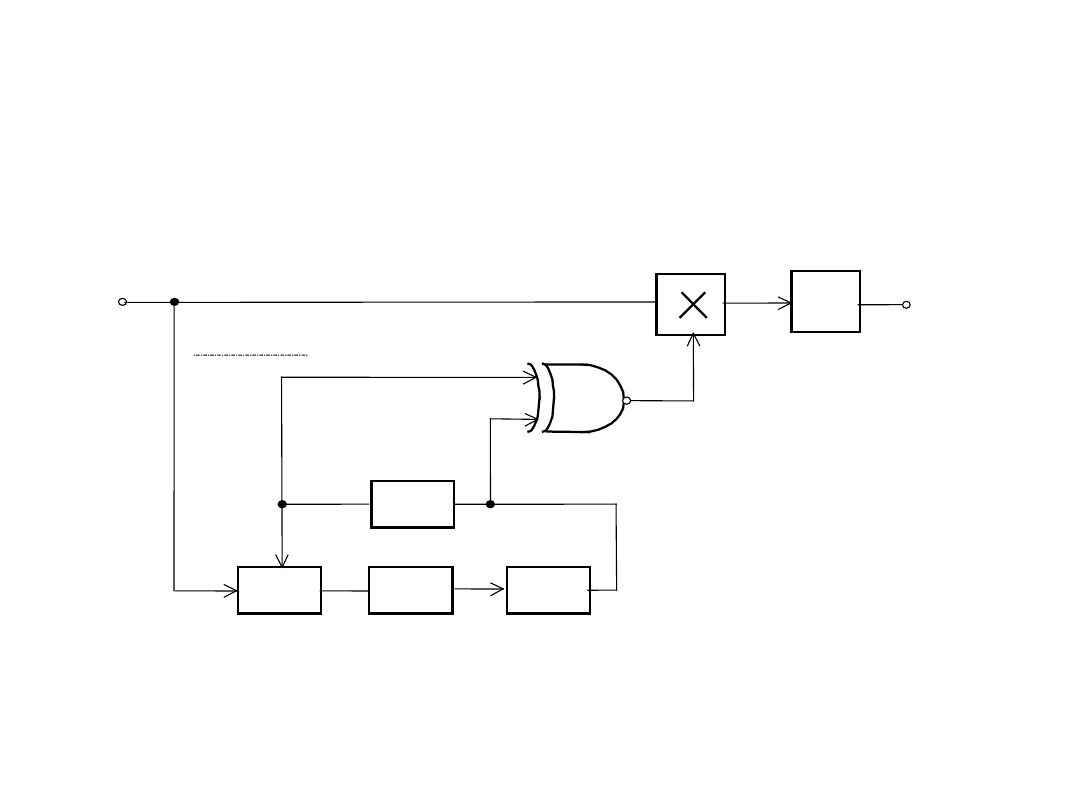

Układy przemiany częstotliwości - powielacz częstotliwości

U

K

Detektor

fazy

Filtr

VCO

U

i

(t)

U

f

0

=nf

1

Zmiana krotności

powielania

A

f

f

1

nf

1

U

K

nf

1

f

0

2f

1

3f

1

f

1

m

n

f

f

i

g

Pętla dostraja się do harmonicznych sygnału wejściowego

Przykłady zastosowań pętli PLL

u

g

(t)

f

0

=Nf

i

0

=N

g

Zmodyfikowany VCO

Detektor

fazy

Filtr

VCO

f

i

f

g

=f

0

f

i2

lub

f

g

= f

i2

f

0

:N

f

g

=f

i

g

i

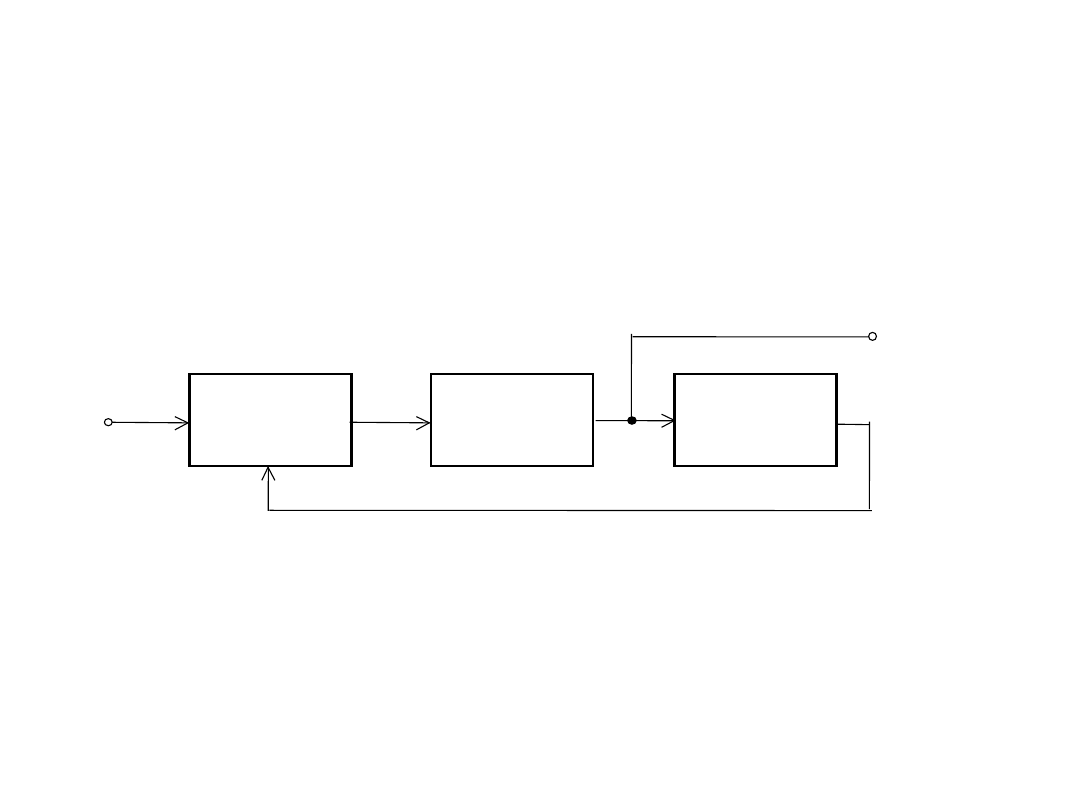

Powielacz częstotliwości z układem PLL i z dzielnikiem

Detektor

fazy

Filtr

VCO

f

i

(t)

u

g

(t)

Przykłady zastosowań pętli PLL

Demodulator częstotliwości

C

1k

10n

F

C

15

k

10k

2k

R

2

2k

Detektor

fazy

10nF

U

m

0,5mA

T

2

T

1

+18V

Regulacja f

0

f

0

f

i

i

NE 561

2 3

6

8

5

VCO

12

13

14

15

16

Przykłady zastosowań pętli PLL

Modulator fazy z układem NE561firmy Signetics

:2

VCO

DF

FD

p

Filtr selektywny

2

N

N

N

+

M

N

N

(0)

N

90

u

1

(t)

u

2

(t)

WY

Przykłady zastosowań pętli PLL

Detektor synchroniczny amplitudy

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 31

- Slide 32

- Slide 33

- Slide 34

Wyszukiwarka

Podobne podstrony:

DX 5 Pętla PLL ver lato 2004

15 Uklady PLL i t s

Petla For w C

PLL KONIEC

Otocz pętlą odcinki

M Hłasko, Pętla

Ferroelektryki. Pętla histerezy, Materiałoznawstwo

21 2 Pętla Autobusowa sanitane Kanalizacja deszczowa

PLL analogi

Bagaz zaginiony PLL LOT

Badanie pętli fazowej PLL, INSTYTUT TELEKOMUNIKACJI I AKUSTYKI

zasady, ZASADY LOTU PLL(A), ZASADY LOTU lic

[lekcja 15] Pętla do while Kurs C++ » Poziom 2

PLL SAA1057 Sterownik syntezy czest

PLL Niziol Pacholek Surdyka

Petla sprzezenia zwrotnego mini2 (Odzyskany) new

Otocz pętlą te obrazki, które kojarzą ci się z wiosną

EO CO i PLL

008 Pętla REPEAT

więcej podobnych podstron