Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

1

SYSTEMY WBUDOWANE

PROGRAMY WBUDOWANE – WYTWARZANIE I TESTOWANIE

Organizacja i rozbudowa pamięci mikrokontrolera AT89C52

2

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

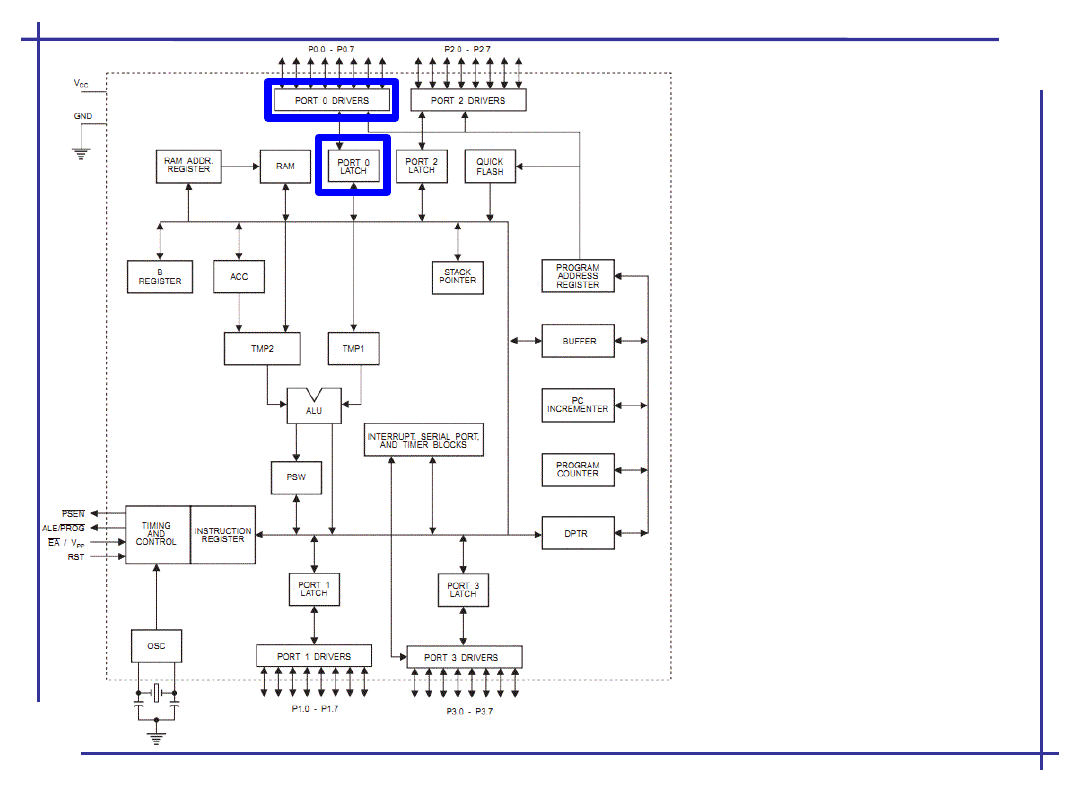

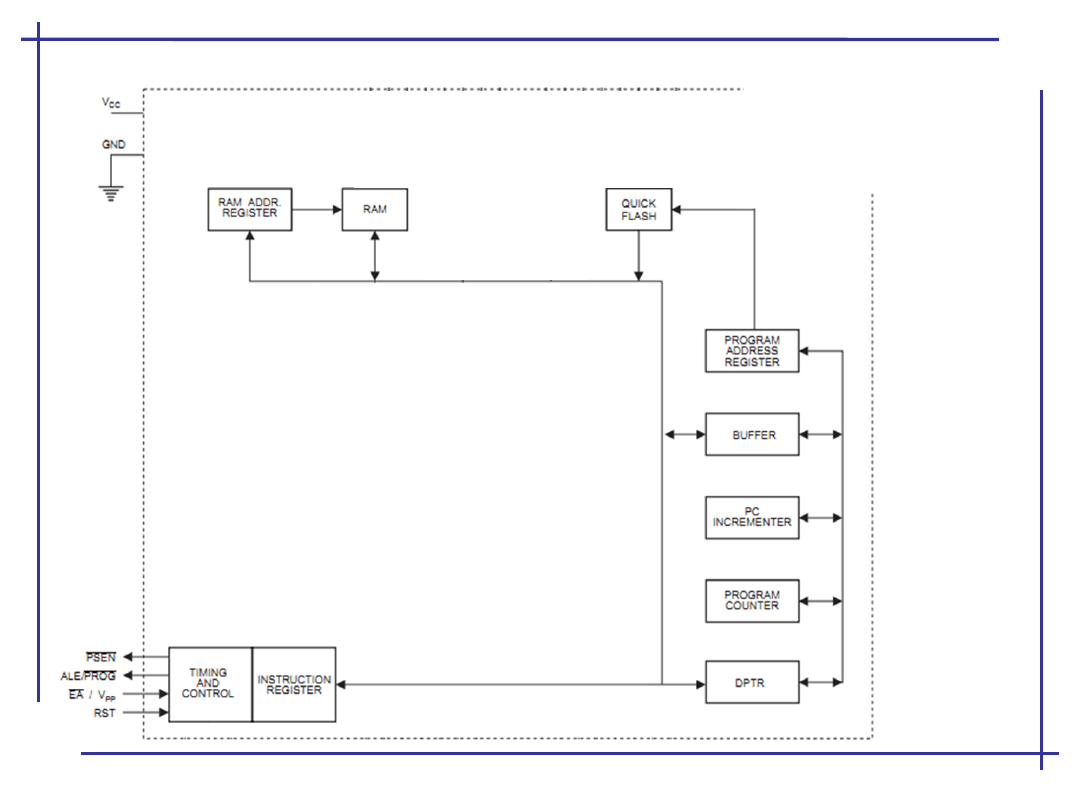

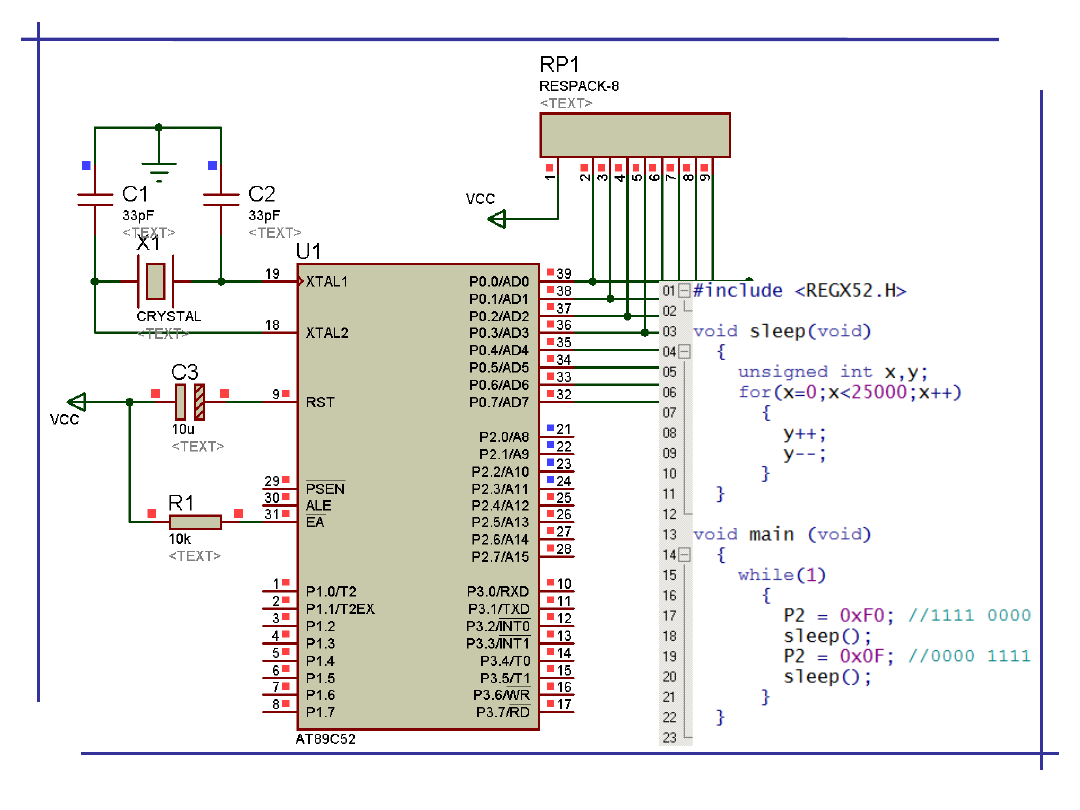

AT89C52

SCHEMAT

BLOKOWY

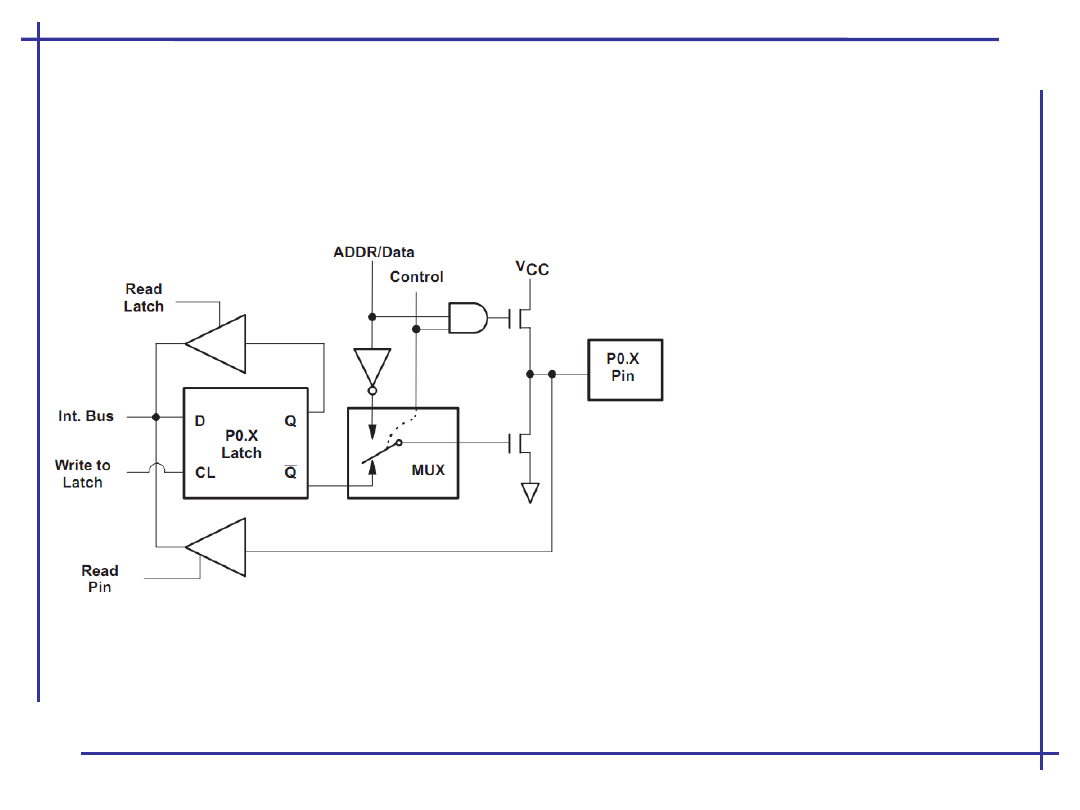

Port 0 is an 8-bit open

drain bi-directional I/O

port. As an output port,

each pin can sink

eight TTL

inputs

. When 1s are written

to port 0 pins, the pins can

be

used

as

high

-

impedance inputs.

Port 0 can also be

configured to be the

multiplexed

low-order

address/data bus during

accesses

to

external

program

and

data

memory. In this mode, P0

has internal pullups.

PORT 0

3

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

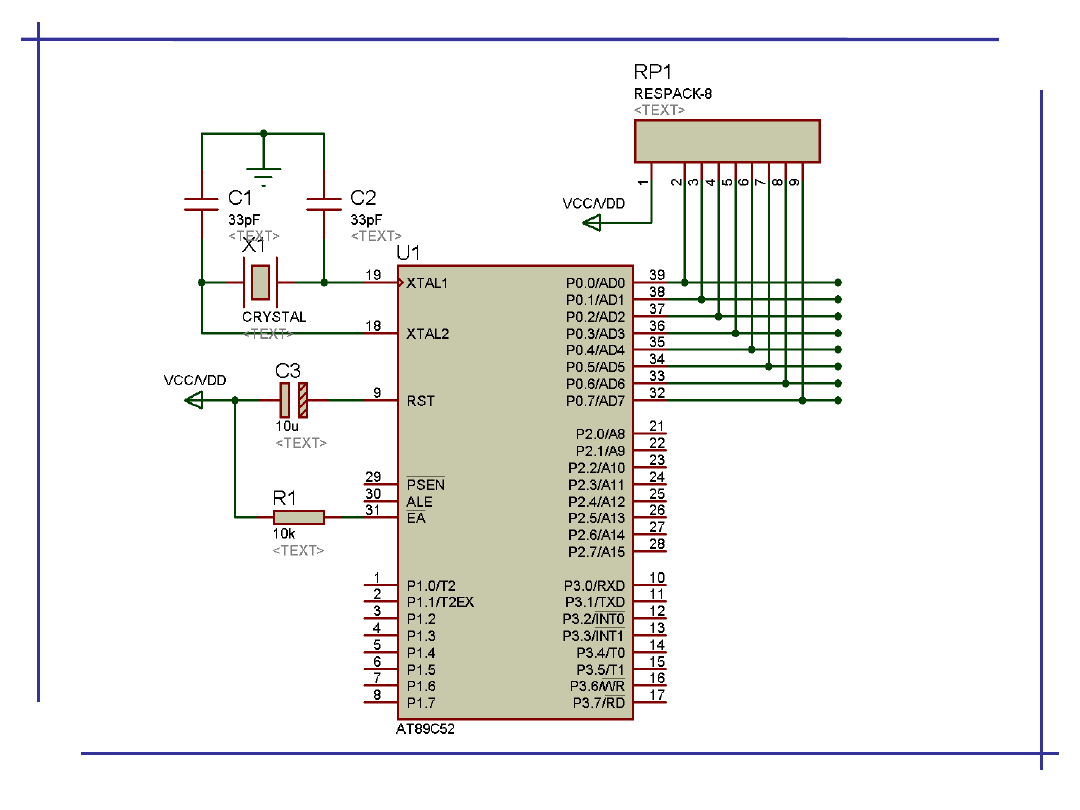

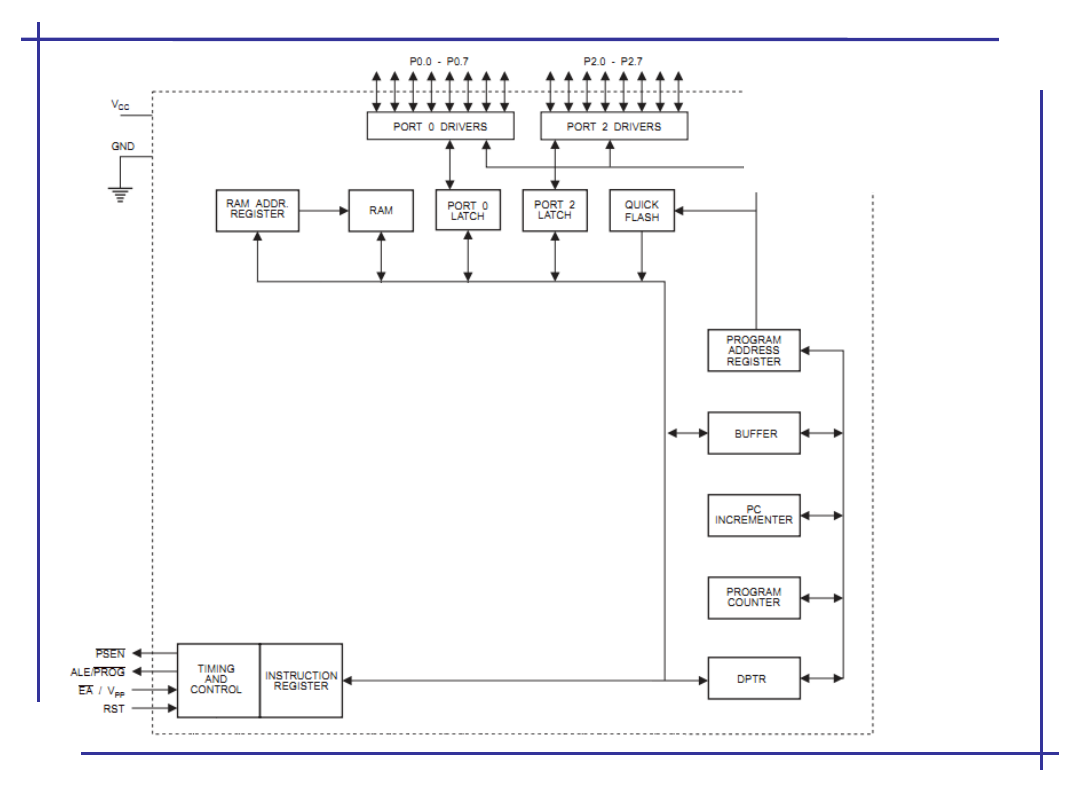

AT89C52

SCHEMAT

BLOKOWY

Port 0 is an 8-bit open

drain bi-directional I/O

port. As an output port,

each pin can sink

eight TTL

inputs

. When 1s are written

to port 0 pins, the pins can

be

used

as

high

-

impedance inputs.

Port 0 can also be

configured to be the

multiplexed

low-order

address/data bus during

accesses

to

external

program

and

data

memory. In this mode, P0

has internal pullups.

PORT 0

0

1

4

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

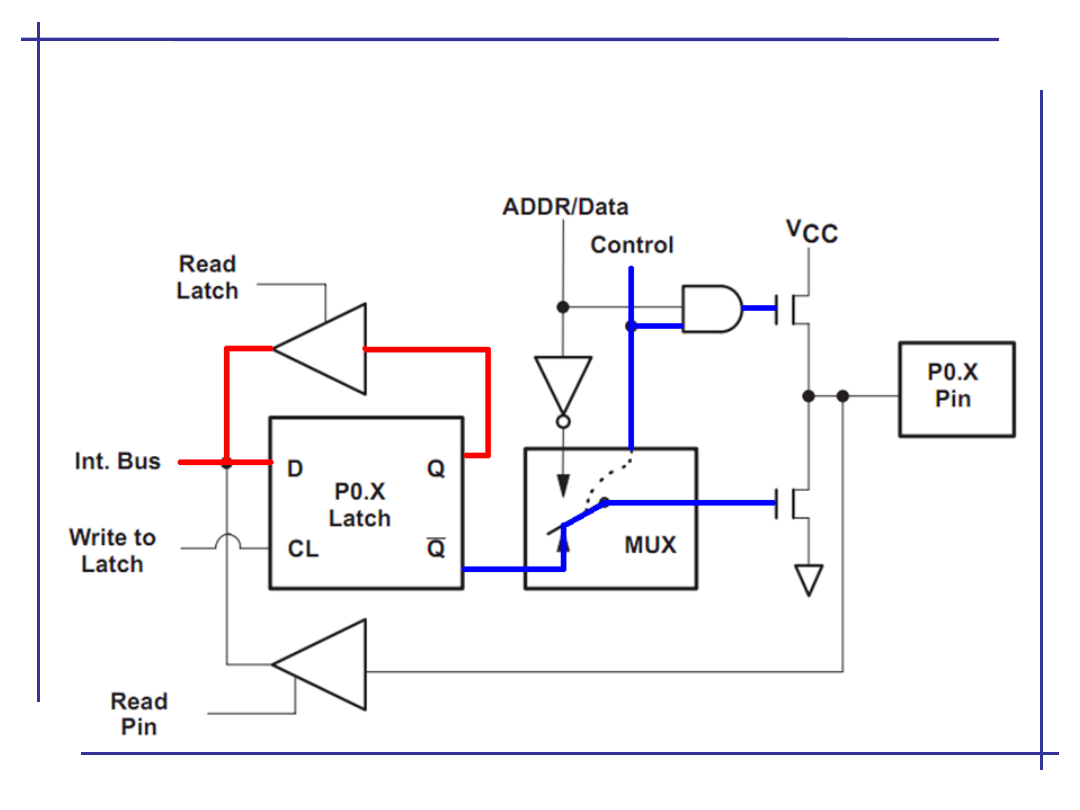

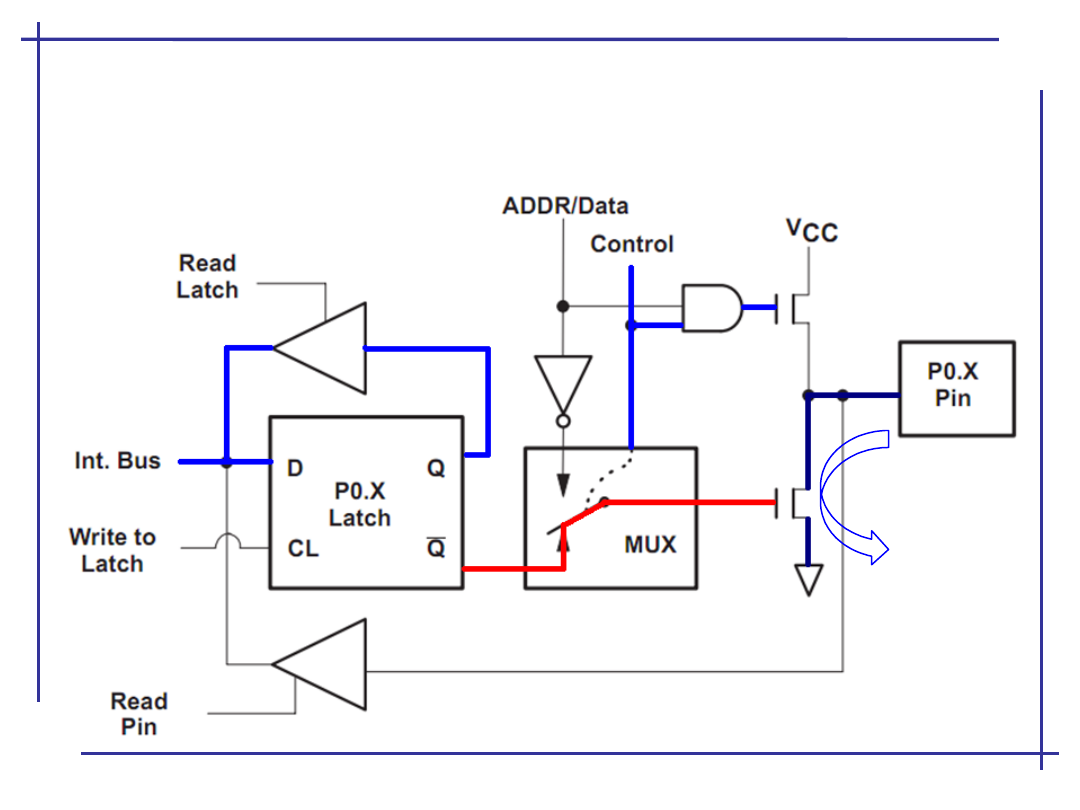

PORT 0 – WPIS „

1

” DO PORTU

TRYB PRACY – WEJ/WYJ

1

0

0

5

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

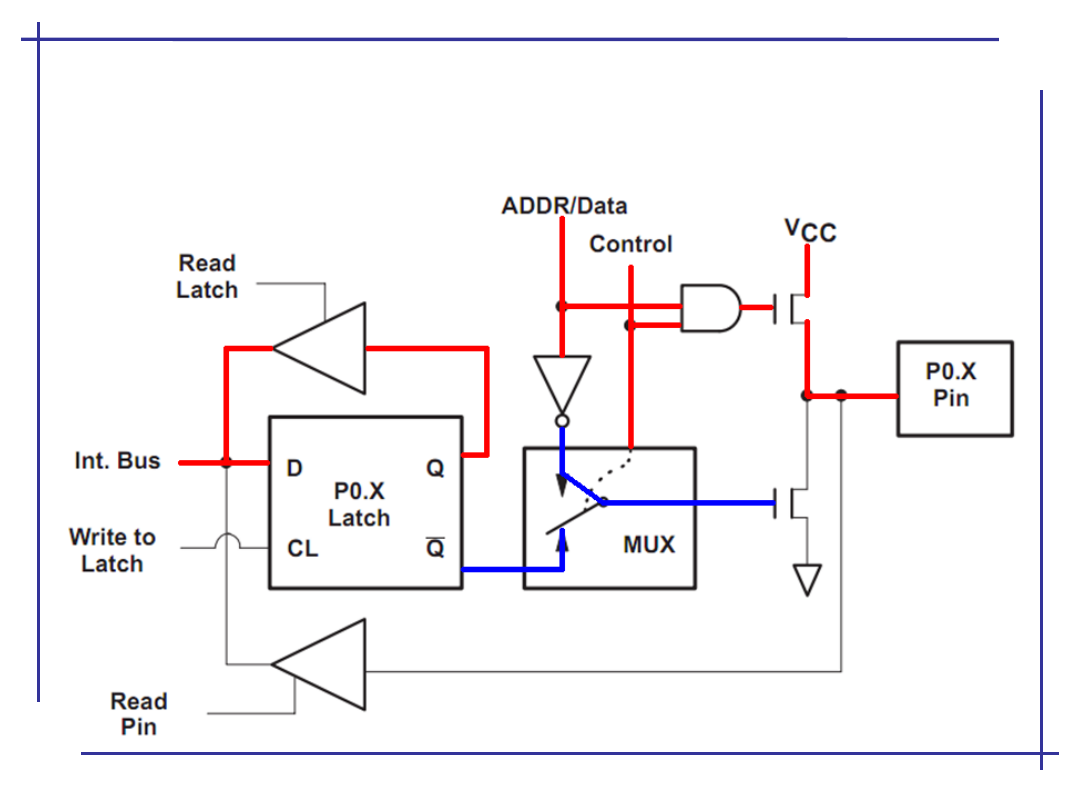

PORT 0 – WPIS „

0

” DO PORTU

TRYB PRACY – WEJ/WYJ

1

0

0

6

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

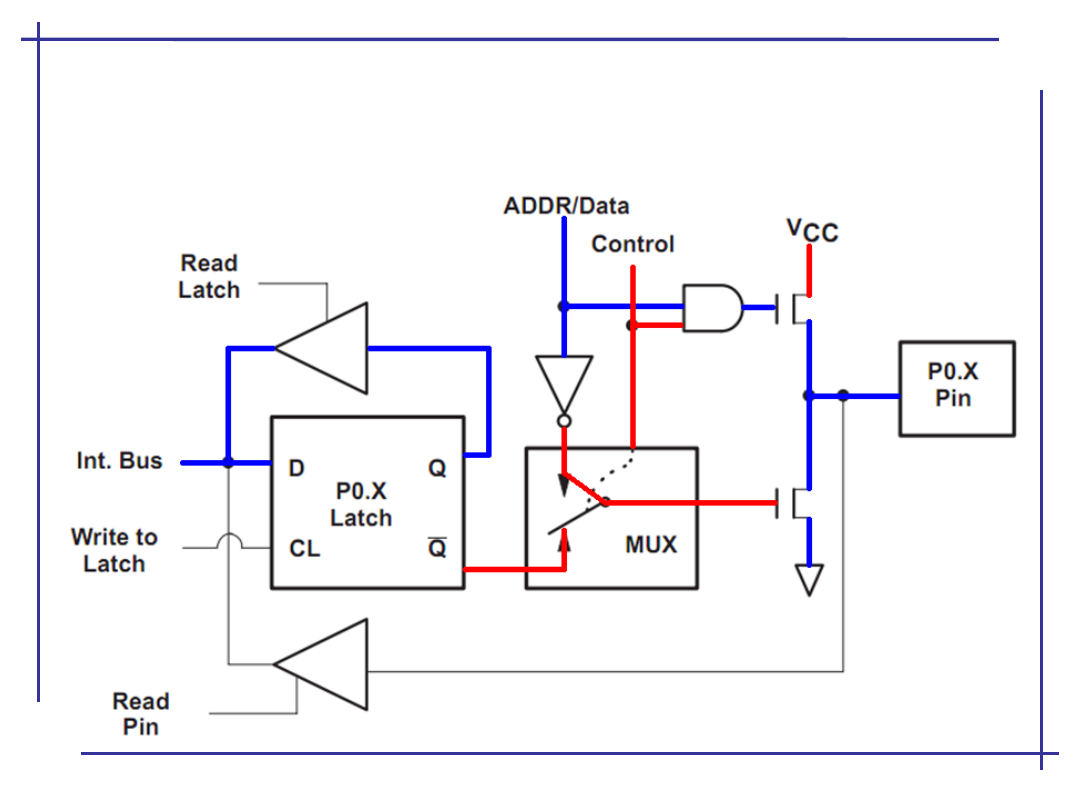

PORT 0 – WPIS „

1

” DO PORTU

TRYB PRACY – OBSŁ. PAMIĘCI

1

0

1

1

7

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

PORT 0 – WPIS „

0

” DO PORTU

TRYB PRACY – OBSŁ. PAMIĘCI

1

0

0

1

8

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

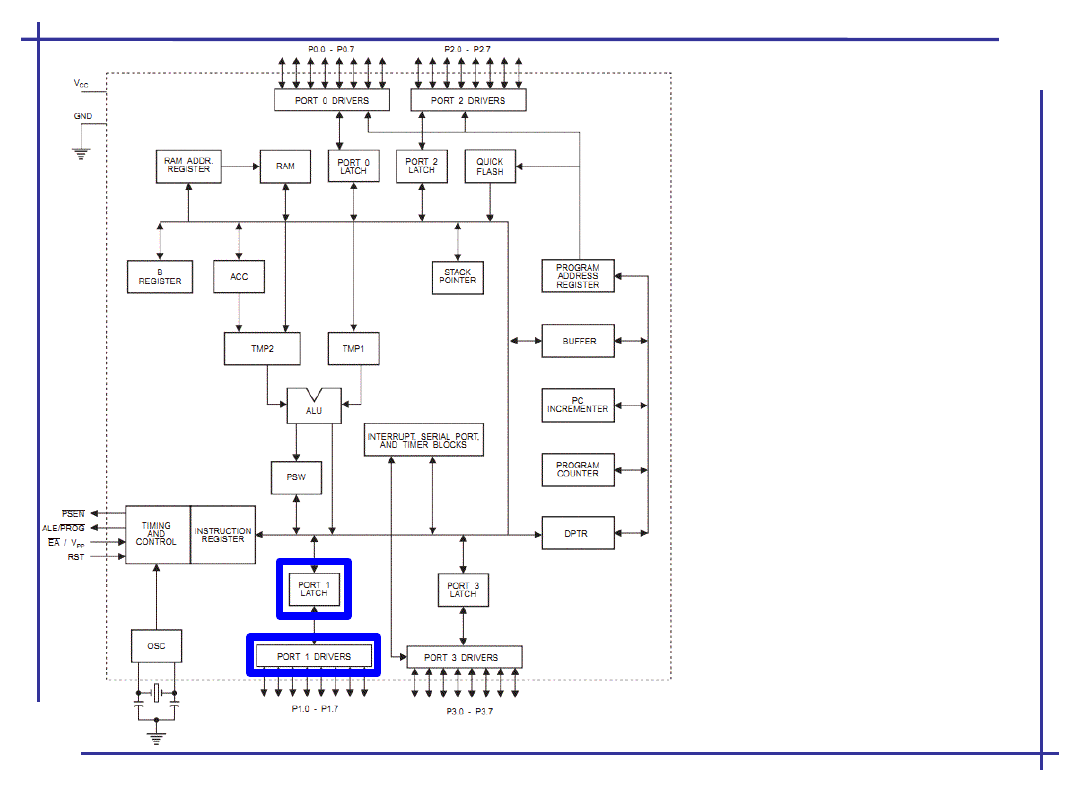

AT89C52

SCHEMAT

BLOKOWY

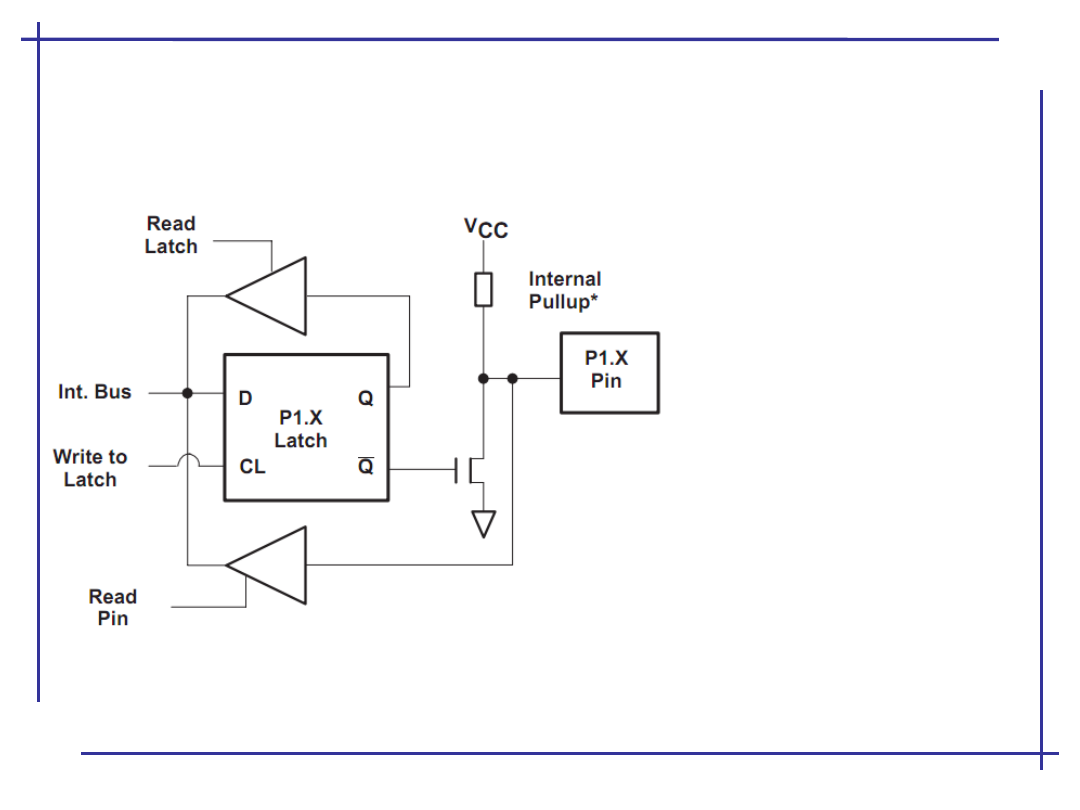

Port 1 is an 8-bit bi-

directional I/O port with

internal pullups. Output

buffers can sink/source

four

TTL inputs

. When 1s are

written to Port 1 pins,

they are pulled high by

the internal pullups and

can be used as inputs. In

addition, P1.0 and P1.1 can

be configured to be the

timer/counter 2 external

count input (P1.0/T2) and

the timer/counter 2 trigger

input (P1.1/T2EX).

PORT 1

9

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

AT89C52

SCHEMAT

BLOKOWY

Port 1 is an 8-bit bi-

directional I/O port with

internal pullups. Output

buffers can sink/source

four

TTL inputs

. When 1s are

written to Port 1 pins,

they are pulled high by

the internal pullups and

can be used as inputs. In

addition, P1.0 and P1.1 can

be configured to be the

timer/counter 2 external

count input (P1.0/T2) and

the timer/counter 2 trigger

input (P1.1/T2EX).

PORT 1

10

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

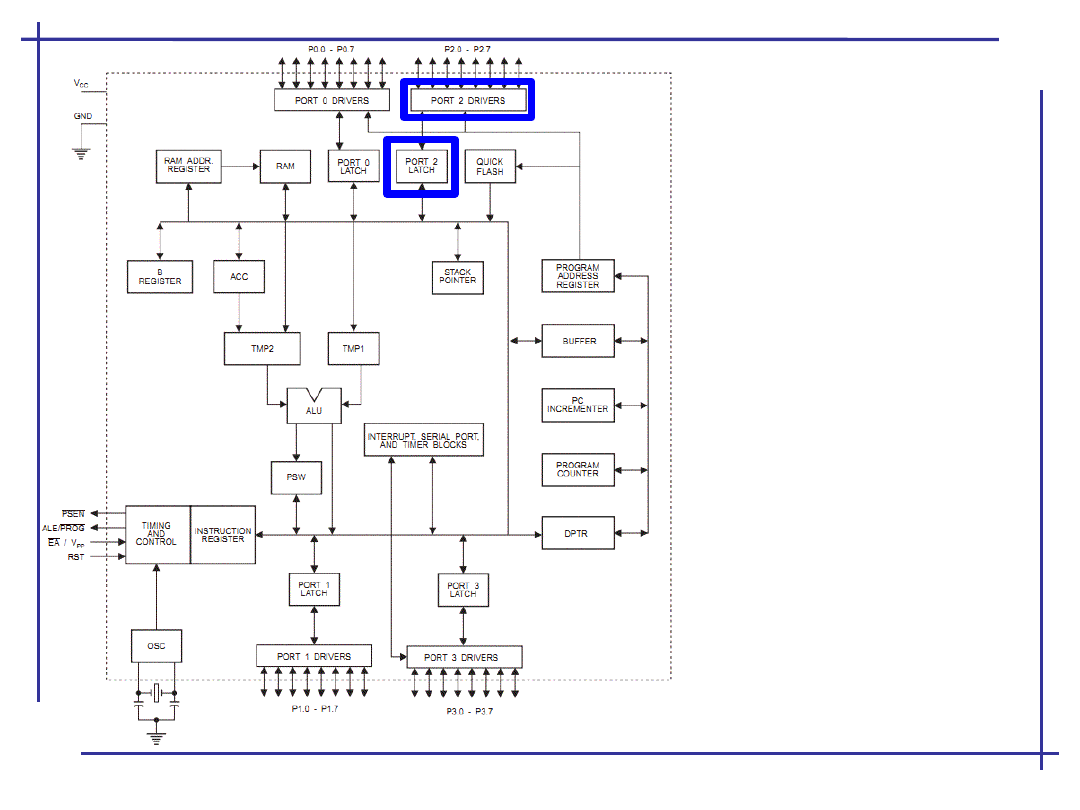

AT89C52

SCHEMAT

BLOKOWY

Port 2 is an 8-bit bi-

directional I/O port with

internal pullups. Output

buffers can sink/source

four

TTL inputs

. When 1s are

written to Port 2 pins,

they are pulled high by

the internal pullups and

can be used as inputs.

Port 2 emits the high-

order

address

byte

during

fetches

from

external

program

memory

and

during

accesses to external data

memory that use 16-bit

addresses

(MOVX

@DPTR).

In

this

application, Port 2 uses

strong

internal

pullups

when emitting 1s.

PORT 2

11

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

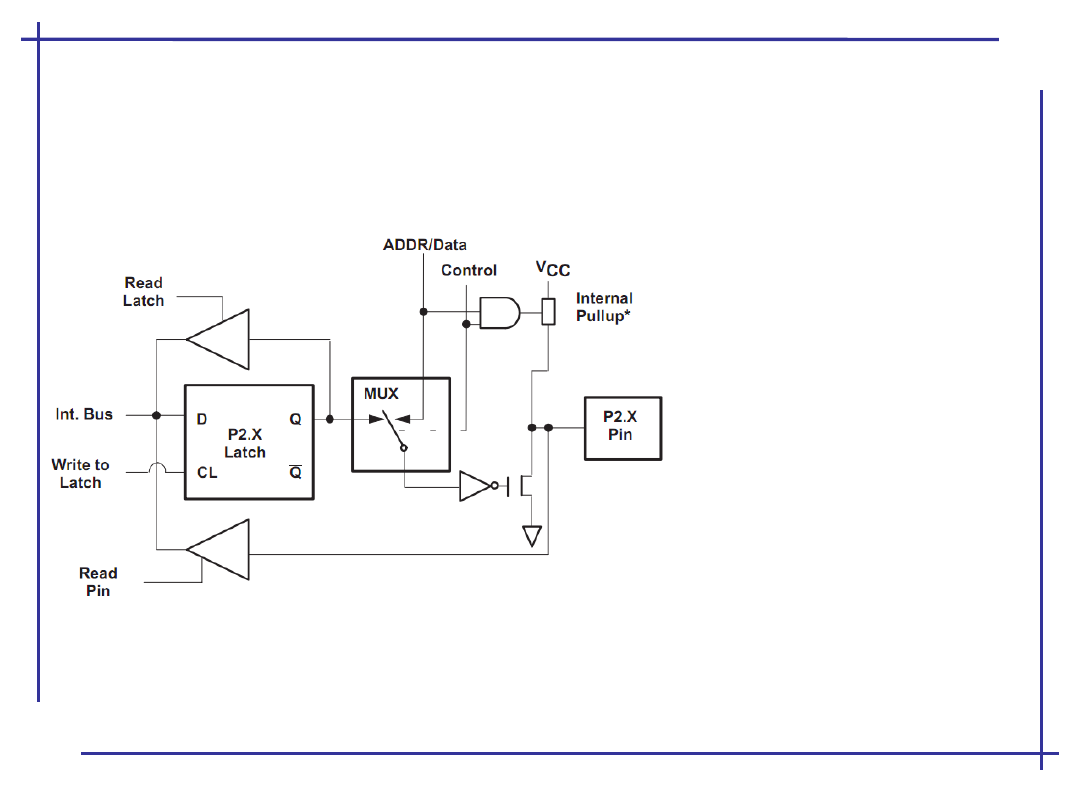

AT89C52

SCHEMAT

BLOKOWY

Port 2 is an 8-bit bi-

directional I/O port with

internal pullups. Output

buffers can sink/source

four

TTL inputs

. When 1s are

written to Port 2 pins,

they are pulled high by

the internal pullups and

can be used as inputs.

Port 2 emits the high-

order

address

byte

during

fetches

from

external

program

memory

and

during

accesses to external data

memory that use 16-bit

addresses

(MOVX

@DPTR).

In

this

application, Port 2 uses

strong

internal

pullups

when emitting 1s.

PORT 2

1

0

12

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

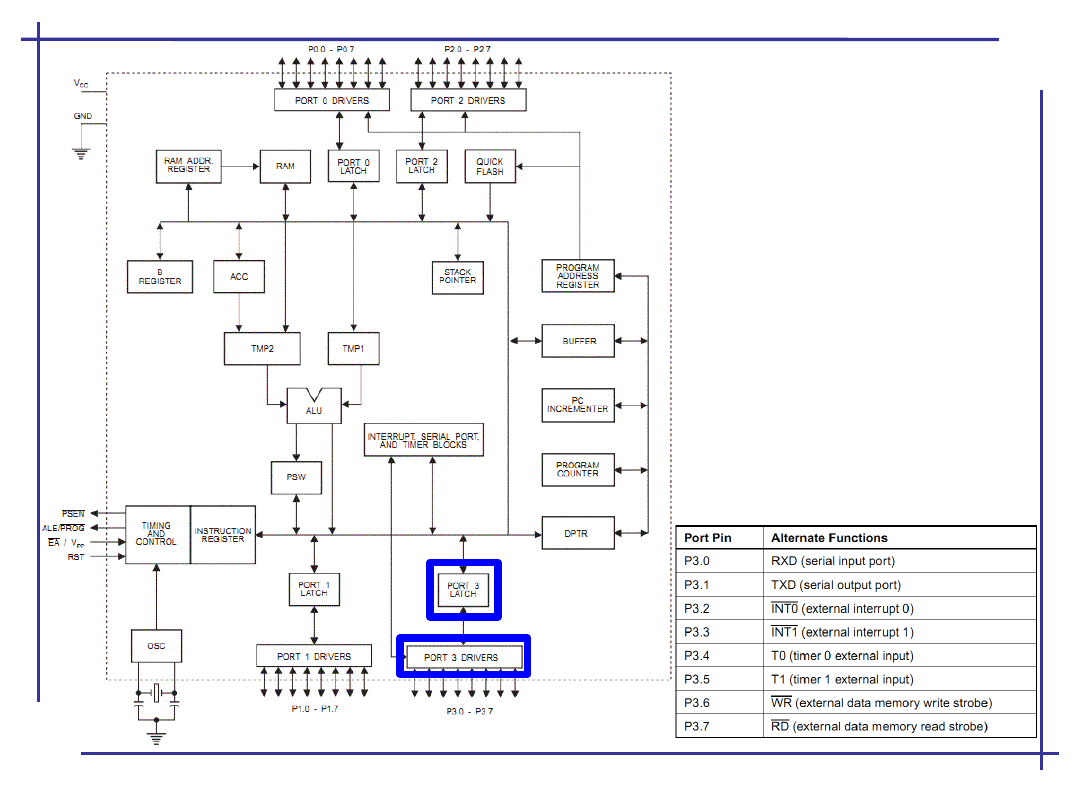

AT89C52

SCHEMAT

BLOKOWY

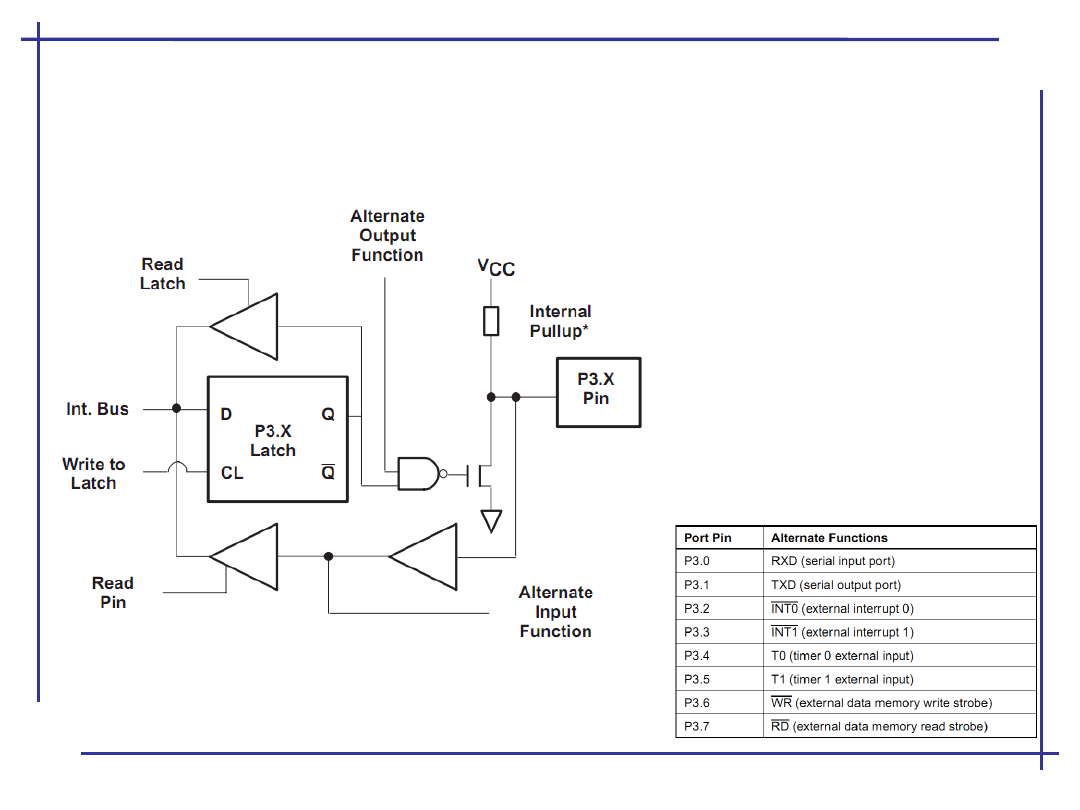

Port 3 is an 8-bit bi-

directional I/O port with

internal pullups. Output

buffers can sink/source

four

TTL inputs

. When 1s are

written to Port 3 pins,

they are pulled high by

the internal pullups and

can be used as inputs.

Port 3 also

serves the

functions of various special

features

of the AT89C51.

PORT 3

13

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

AT89C52

SCHEMAT

BLOKOWY

Port 3 is an 8-bit bi-

directional I/O port with

internal pullups. Output

buffers can sink/source

four

TTL inputs

. When 1s are

written to Port 3 pins,

they are pulled high by

the internal pullups and

can be used as inputs.

Port 3 also

serves the

functions of various special

features

of the AT89C51.

PORT 3

14

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

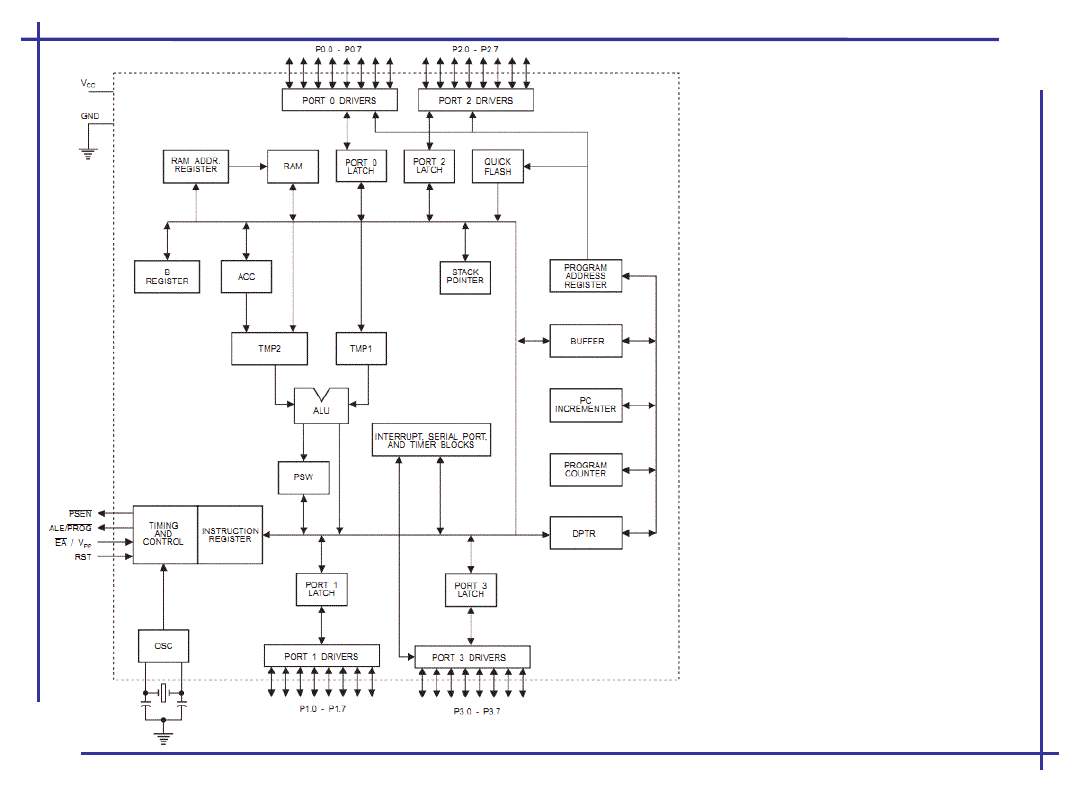

AT89C52

ORGANIZACJA

MIKROKONTROLE

RA

WSZYSTKIE

BLOKI

FUNKCJONALNE

C WIDZIANE SĄ

JAK

KOMÓRKI

PAMIĘCI.

NIEKTÓRE Z NICH

ADRESOWANE SĄ

BITOWO

I

BAJTOWO.

15

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

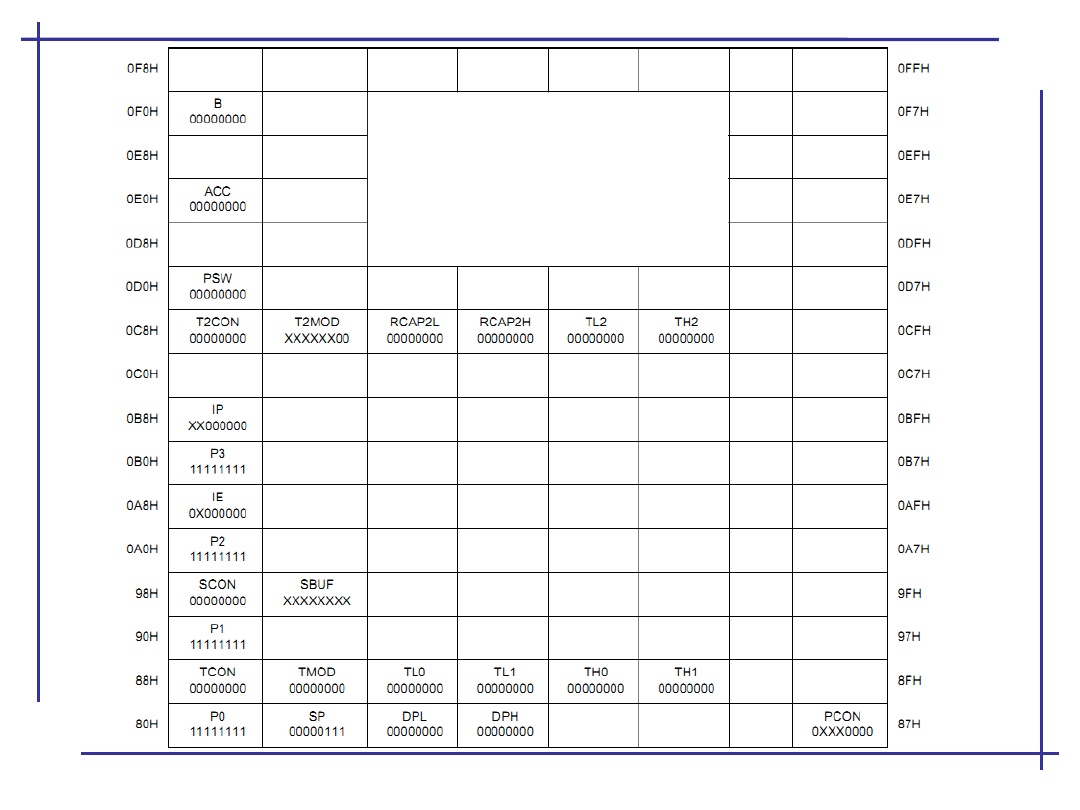

MAPA PAMIĘCI

REJESTRY SFR

16

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

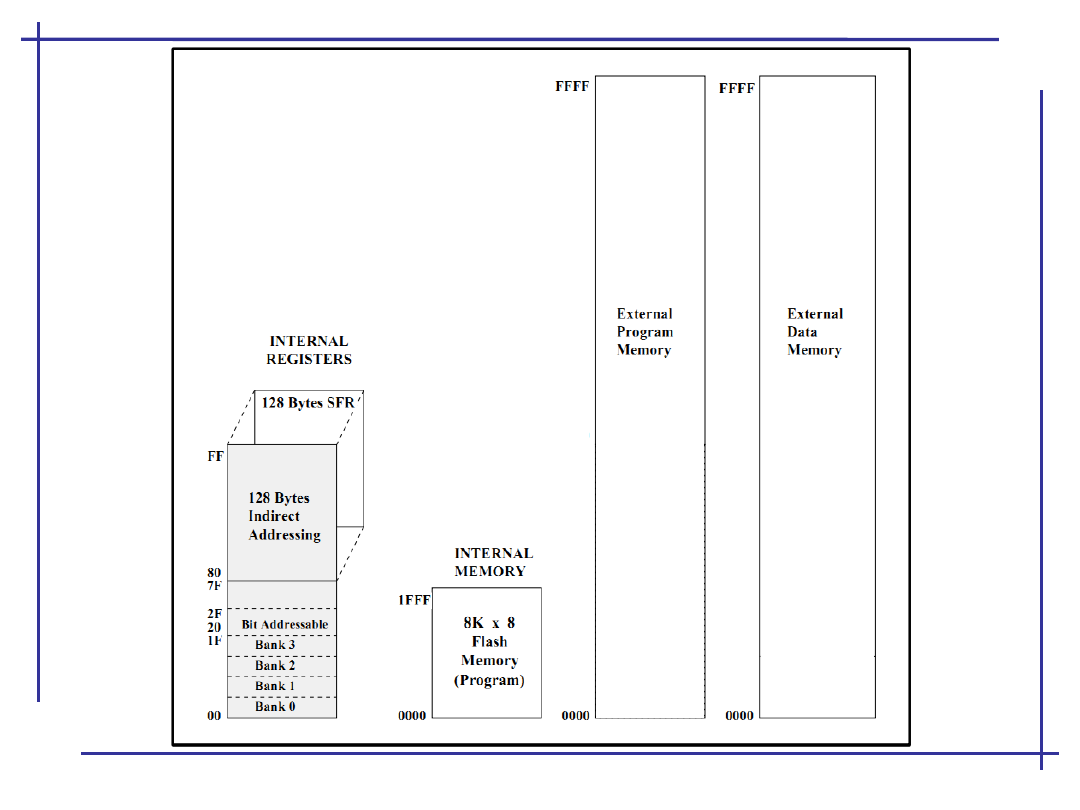

MAPA PAMIĘCI

17

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

PAMIĘĆ

WEWNĘTRZNA

18

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

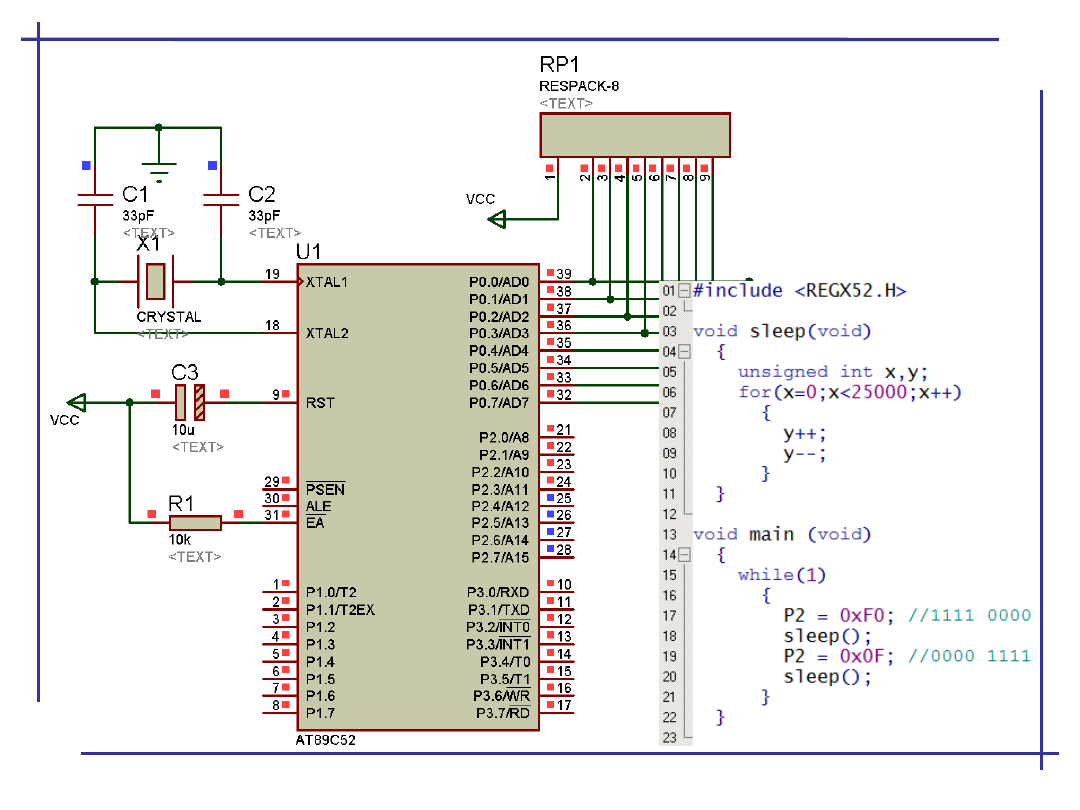

Wej/Wyj

Wej/Wyj

Wej/Wyj

Wej/Wyj

19

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

AT89X52.H

sfr P0

= 0x80;

sfr SP

= 0x81;

sfr DPL

= 0x82;

sfr DPH

= 0x83;

sfr PCON

= 0x87;

sfr TCON

= 0x88;

sfr TMOD

= 0x89;

sfr TL0

= 0x8A;

sfr TL1

= 0x8B;

sfr TH0

= 0x8C;

sfr TH1

= 0x8D;

sfr AUXR

= 0x8E;

sfr P1

= 0x90;

sfr SCON

= 0x98;

sfr SBUF

= 0x99;

sfr P2

= 0xA0;

sfr IE

= 0xA8;

sfr P3

= 0xB0;

sfr IP

= 0xB8;

sfr T2CON

= 0xC8;

sfr T2MOD = 0xC9;

sfr RCAP2L = 0xCA;

sfr RCAP2H = 0xCB;

sfr TL2

= 0xCC;

sfr TH2

= 0xCD;

sfr PSW

= 0xD0;

sfr ACC

= 0xE0;

sfr B

= 0xF0;

/*------------------------------------------------

P0 Bit Registers

------------------------------------------------*/

sbit P0_0 = 0x80;

sbit P0_1 = 0x81;

sbit P0_2 = 0x82;

sbit P0_3 = 0x83;

sbit P0_4 = 0x84;

sbit P0_5 = 0x85;

sbit P0_6 = 0x86;

sbit P0_7 = 0x87;

sbit T2 = 0x90; /* External input to Timer/Counter 2, clock out */

sbit T2EX = 0x91; /* Timer/Counter 2 capture/reload trigger & dir ctl */

/*------------------------------------------------

SCON Bit Registers

------------------------------------------------*/

sbit RI = 0x98;

sbit TI

= 0x99;

sbit RB8 = 0x9A;

sbit TB8 = 0x9B;

sbit REN = 0x9C;

sbit SM2 = 0x9D;

sbit SM1 = 0x9E;

sbit SM0 = 0x9F;

20

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

21

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

22

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

PAMIĘĆ

ZEWNĘTRZNA

23

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

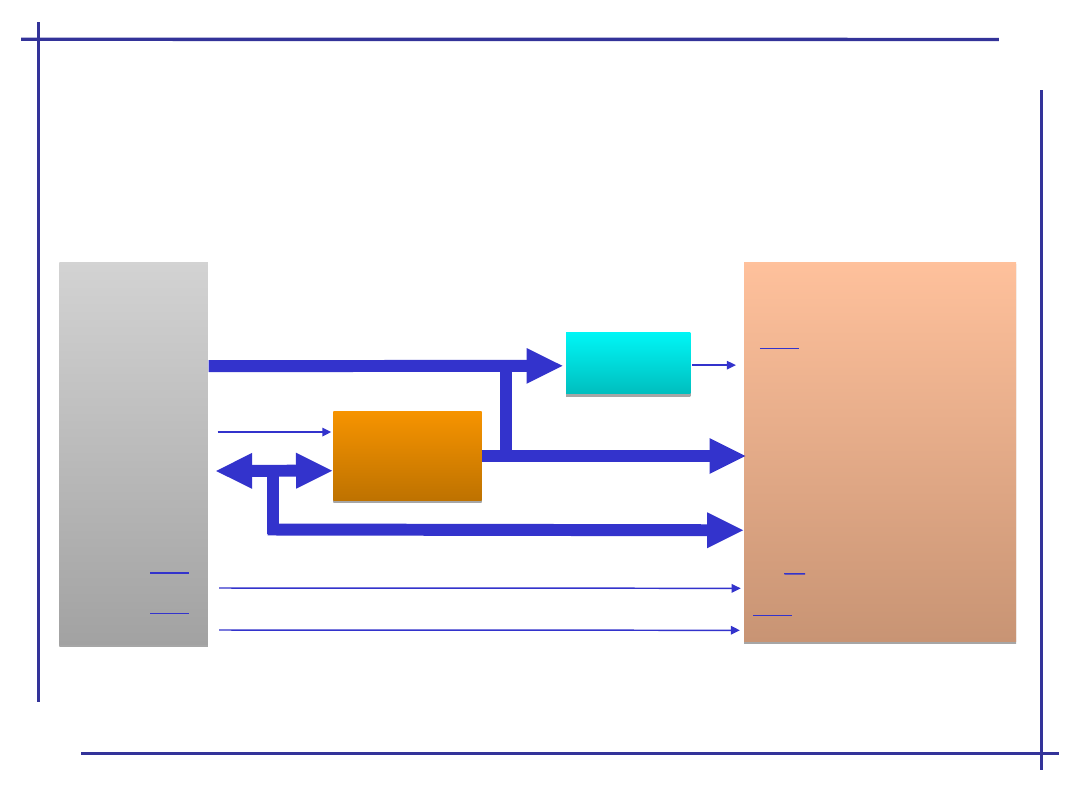

8051

PORT 2

PORT 0

ALE

P3.7

P3.6

PSEN

A15 - A8: High byte of

address

AD7 - AD0: Data and low byte

address

ALE: Address latch enable

RD: Read strobe

WR: Write strobe

PSEN: Program store

enable

WSPÓŁPRACA Z PAMIĘCIĄ ZEWNĘTRZNĄ

24

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

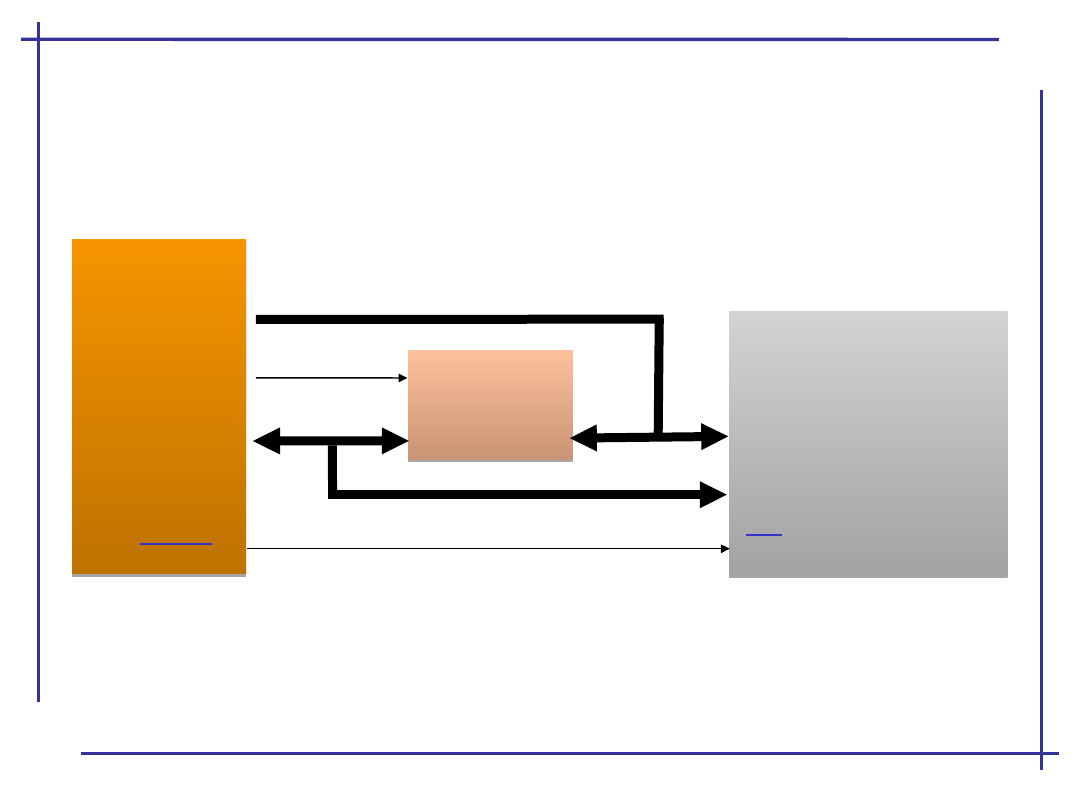

WSPÓŁPRACA Z PAMIĘCIĄ ZEWNĘTRZNĄ PROGRAMU

8051

PORT

2

ALE

PORT0

PSEN

ADDRES

S

LATCH

ROM(S)

ADDRESS

INPUTS

DATA OUTPUTS

OE

A15 - A8

A15 - A0

D7 - D0

AD7 - AD0

25

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

WSPÓŁPRACA Z PAMIĘCIĄ ZEWNĘTRZNĄ DANYCH

8051

PORT

2

ALE

PORT

0

WR

RD

RAM(S) or I/O

CE

DATA OUTPUTS

ADDRESS

INPUTS

R/W

OE

ADDRES

S LATCH

DECODE

A15 - A8

A14 - A0

A15

D7 - D0

26

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

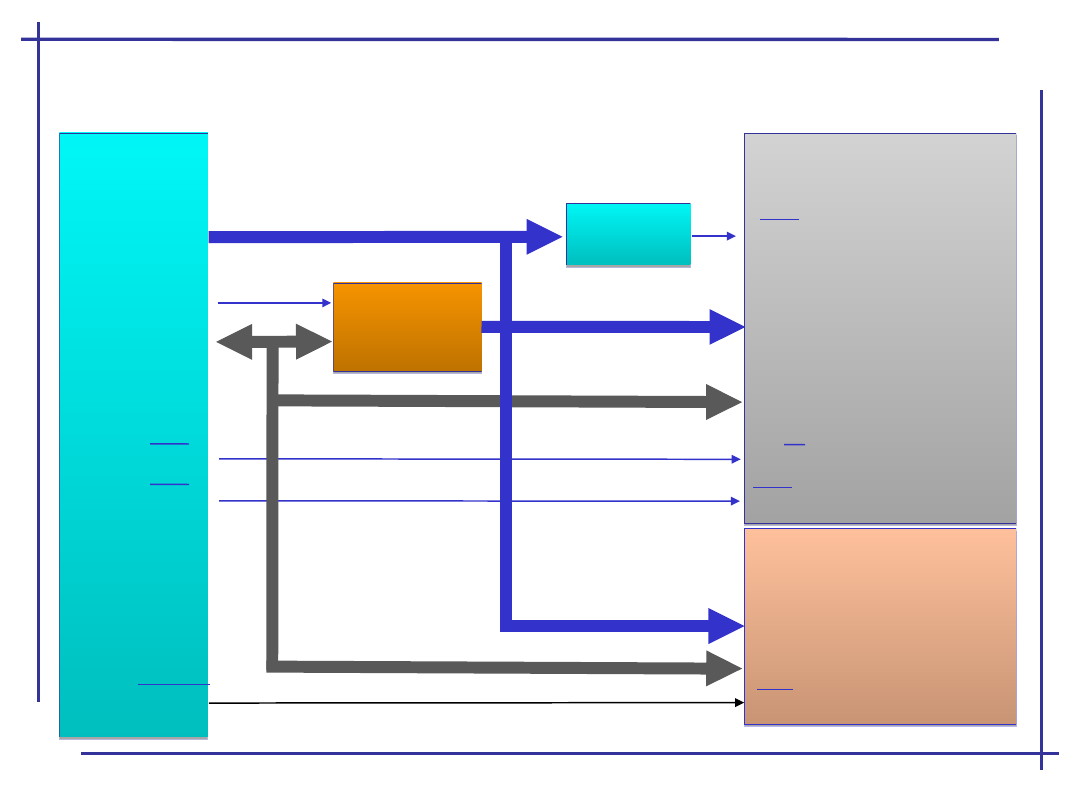

WSPÓŁPRACA Z PAMIĘCIĄ ZEWNĘTRZNĄ PROGRAMU I

DANYCH

8051

PORT

2

ALE

PORT

0

WR

RD

RAM(S) or I/O

CE

DATA OUTPUTS

ADDRESS

INPUTS

R/W

OE

ADDRES

S LATCH

DECODE

ROM(S)

ADDRESS

INPUTS

DATA OUTPUTS

OE

PSEN

OE

A15 - A8

A14 – A0

A14 – A0

A15

D7 - D0

D7 - D0

D7 - D0

27

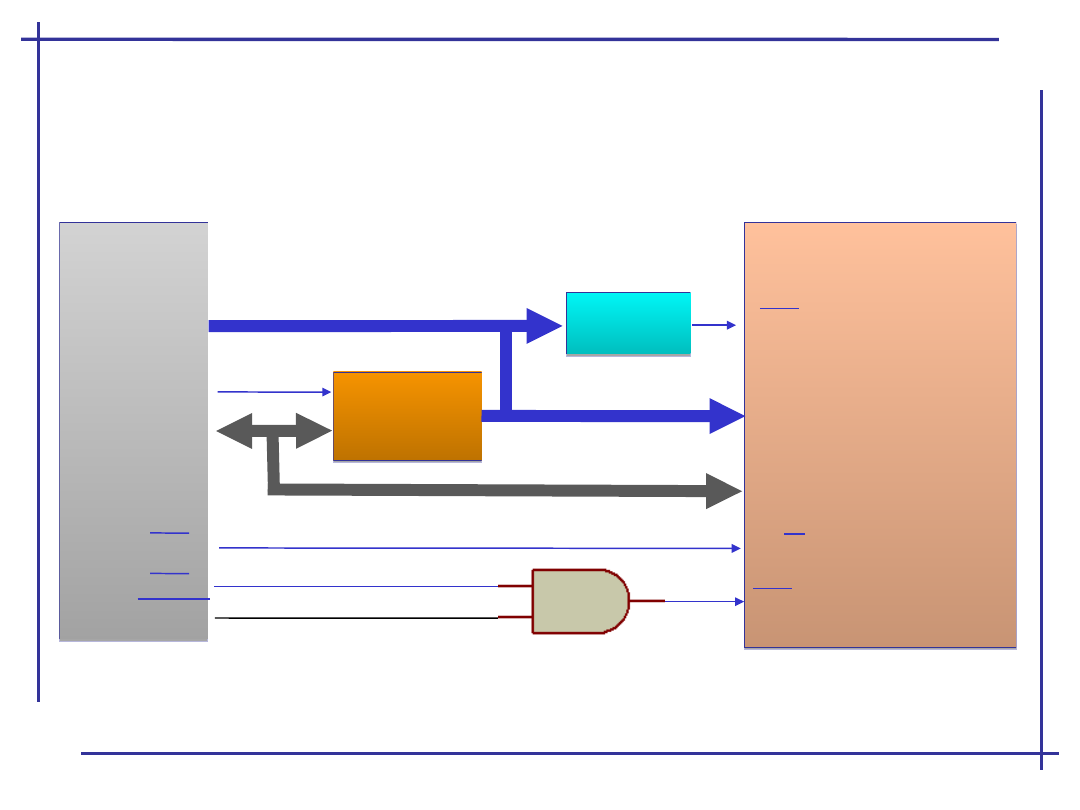

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

WSPÓŁPRACA Z PAMIĘCIĄ ZEWNĘTRZNĄ PROGRAMU I

DANYCH

8051

PORT

2

ALE

PORT

0

WR

RD

RAM(S) or I/O

CE

DATA OUTPUTS

ADDRESS

INPUTS

R/W

ADDRES

S LATCH

DECODE

AND ROM(S)

PSEN

OE

A15 - A8

A14 – A0

A15

D7 - D0

D7 - D0

1

2

3

U2:A

7408

28

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

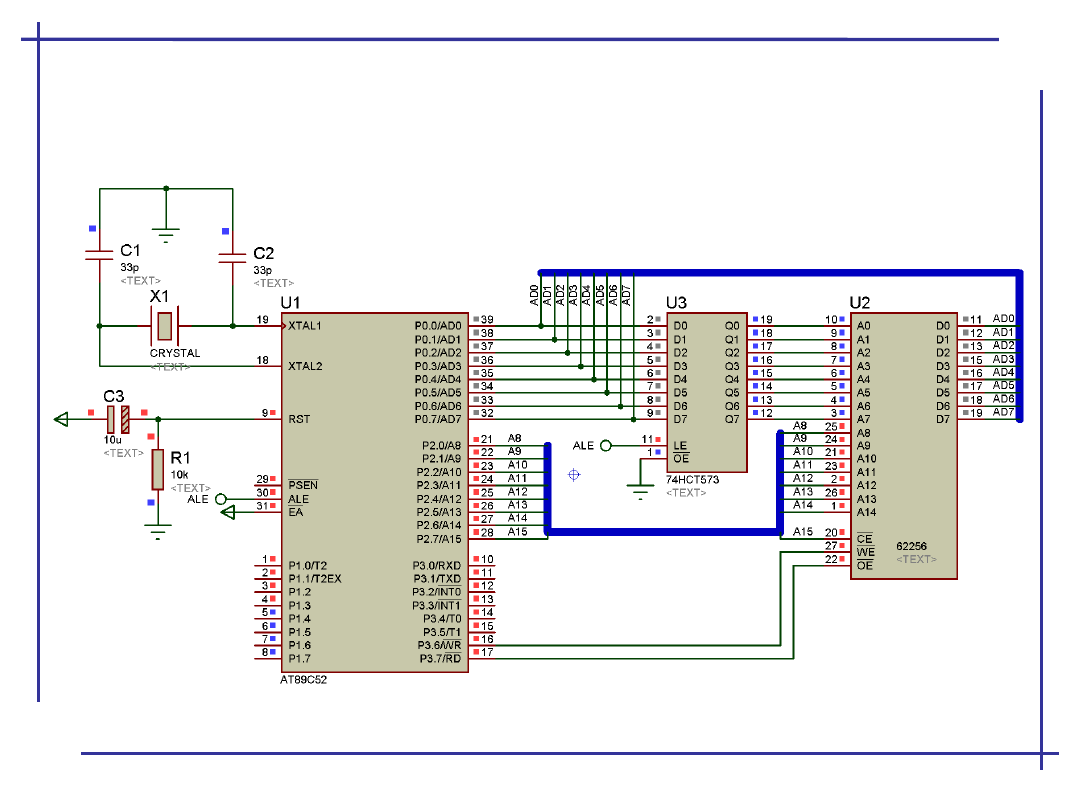

PRZYKŁAD DOŁĄCZENIA ZEWNĘTRZNEJ PAMIĘCI

DANYCH

29

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

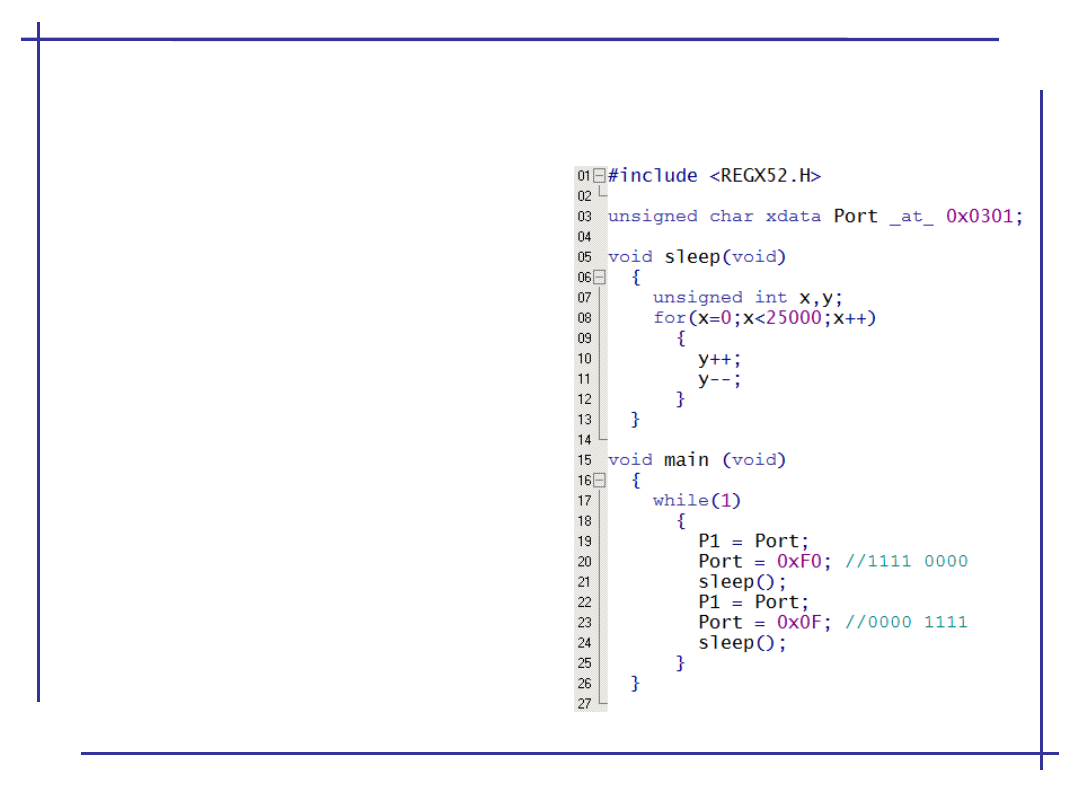

TYPY DANYCH I MODYFIKATORY

Modele pamięci:

Small

Compact

Large

Lokacja zmiennej lub stałej

w PAO:

typ kwalifikator pamięci _at_

adres;

Kwalifikatory pamięci:

code

data

idata

bdata

xdata

far

pdata

30

Instytut Teleinformatyki i Automatyki, Wydział Cybernetyki WAT

TYPY DANYCH I MODYFIKATORY

Data Types

Bits

Bytes Value Range

1

0 to 1

8

1

-128 — +127

8

1

0 — 255

8 / 16 1 or 2 -128 — +127 or -32768 — +32767

16

2

-32768 — +32767

16

2

0 — 65535

16

2

-32768 — +32767

16

2

0 — 65535

32

4

-2147483648 — +2147483647

32

4

0 — 4294967295

32

4

±1.175494E-38 — ±3.402823E+38

32

4

±1.175494E-38 — ±3.402823E+38

1

0 or 1

8

1

0 — 255

16

2

0 — 65535

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

Wyszukiwarka

Podobne podstrony:

motumbo www prezentacje org

czerwony kapturek2 www prezentacje org 3

bez makijazu www prezentacje org

dobrze byc mezczyzna www prezentacje org

puchar swiata 2006 www prezentacje org

moja kariera www prezentacje org

PRK 23 10 2011 org

typy kobiet www prezentacje org 3

czemu faceci gina mlodo www prezentacje org

socjologia org

wypadek przy pracy www prezentacje org

bezwzgledny sport www prezentacje org

za szybko www prezentacje org

milosc jest jak bezmiar wod www prezentacje org

więcej podobnych podstron