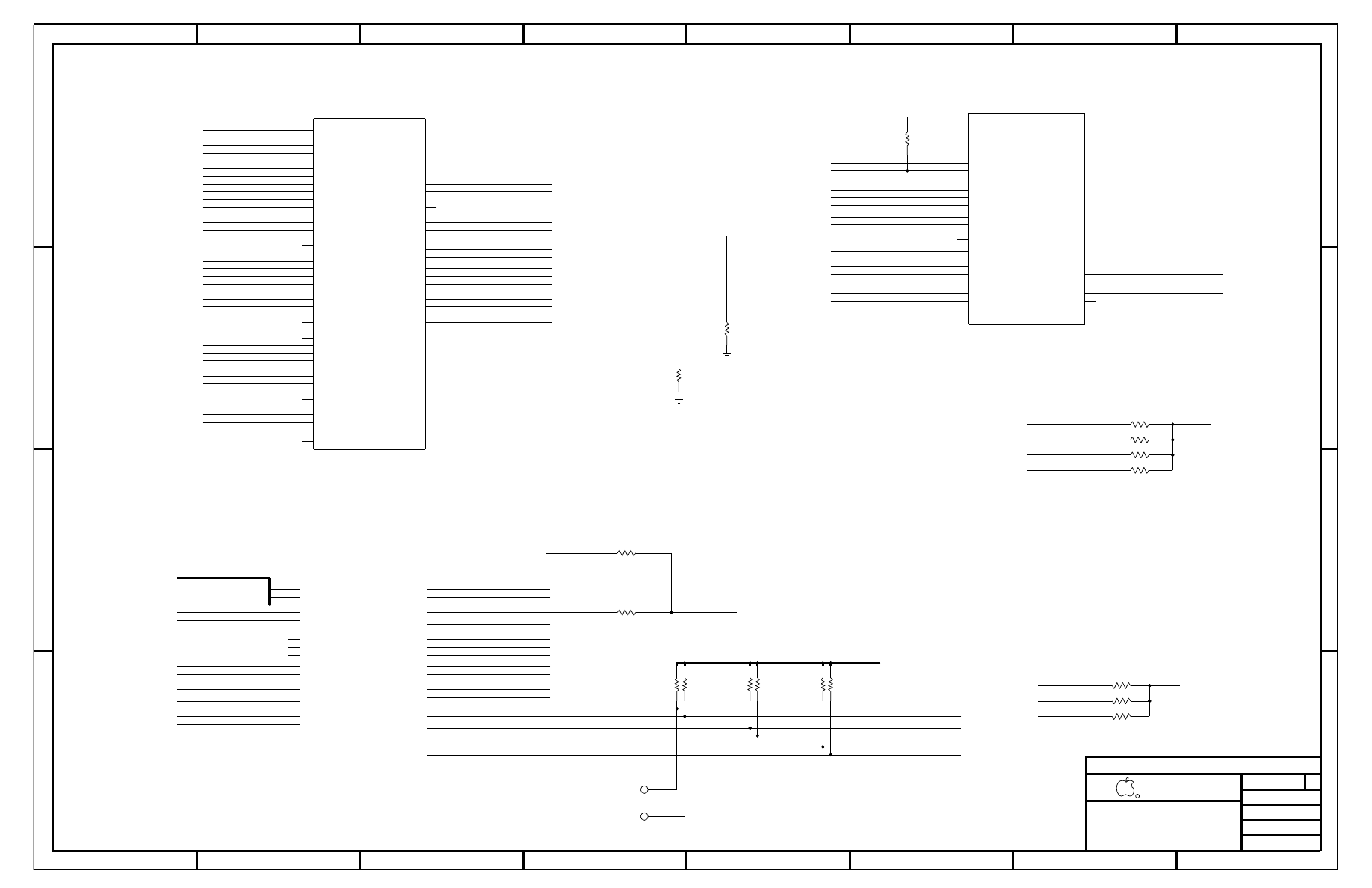

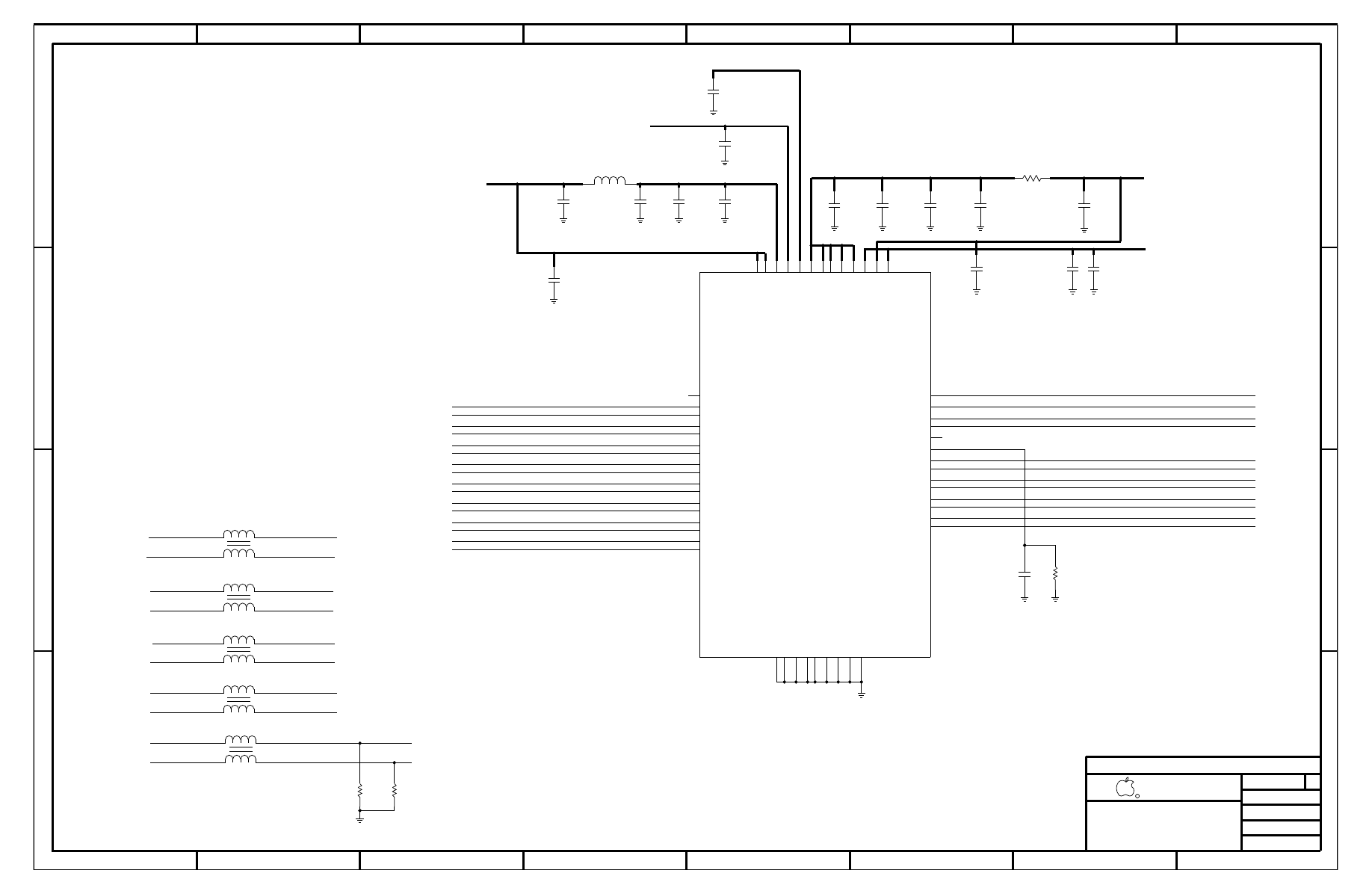

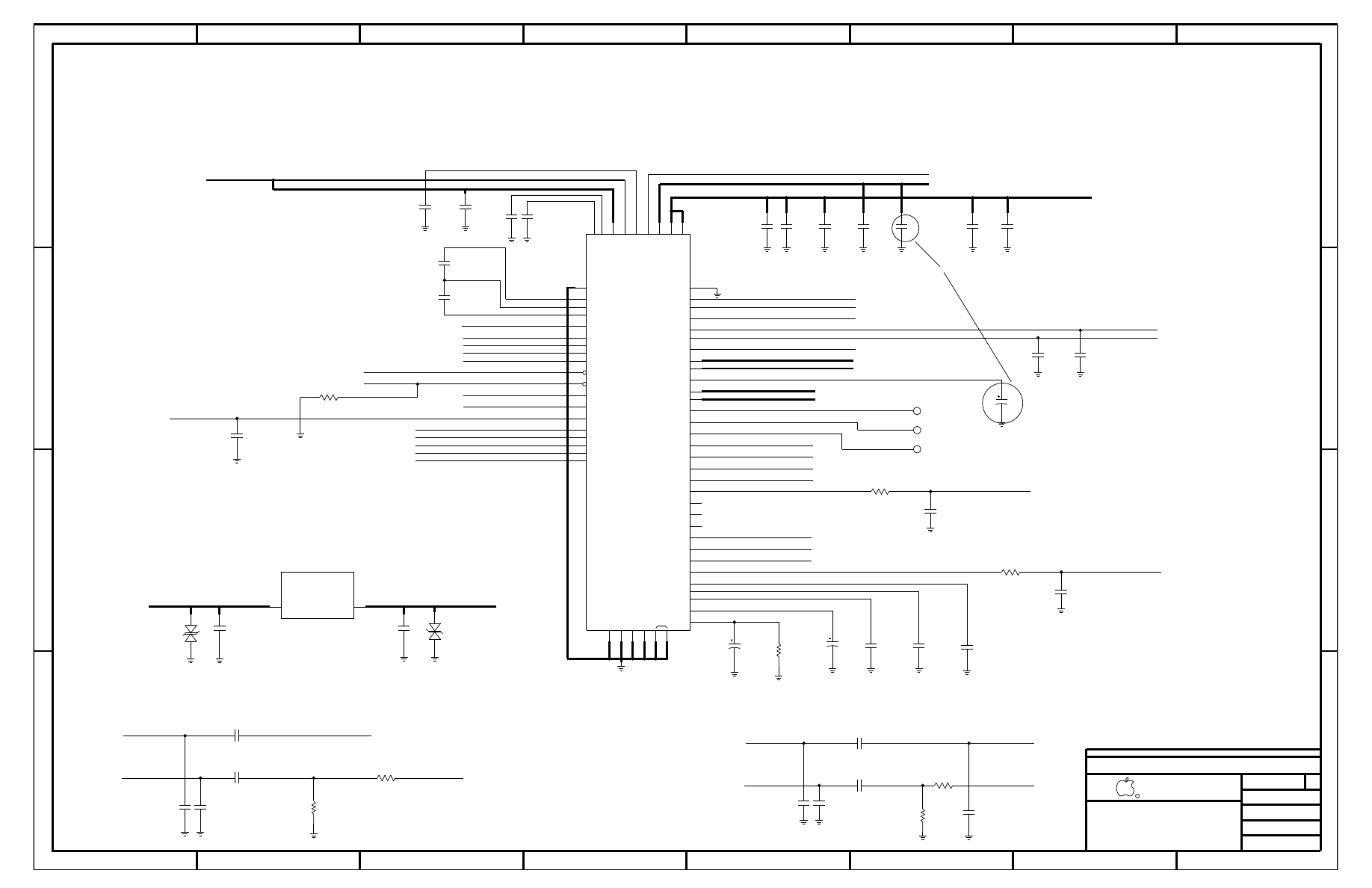

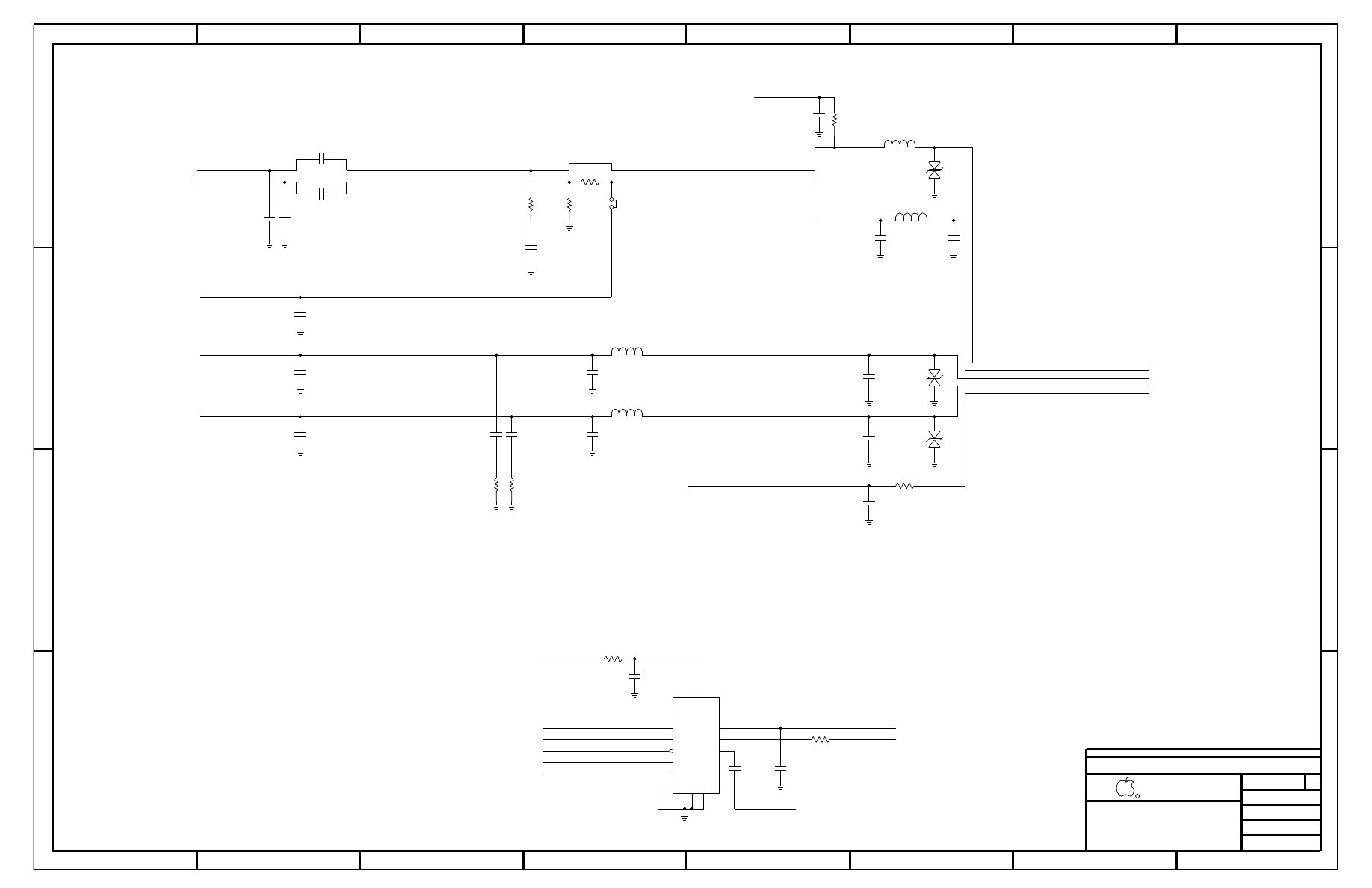

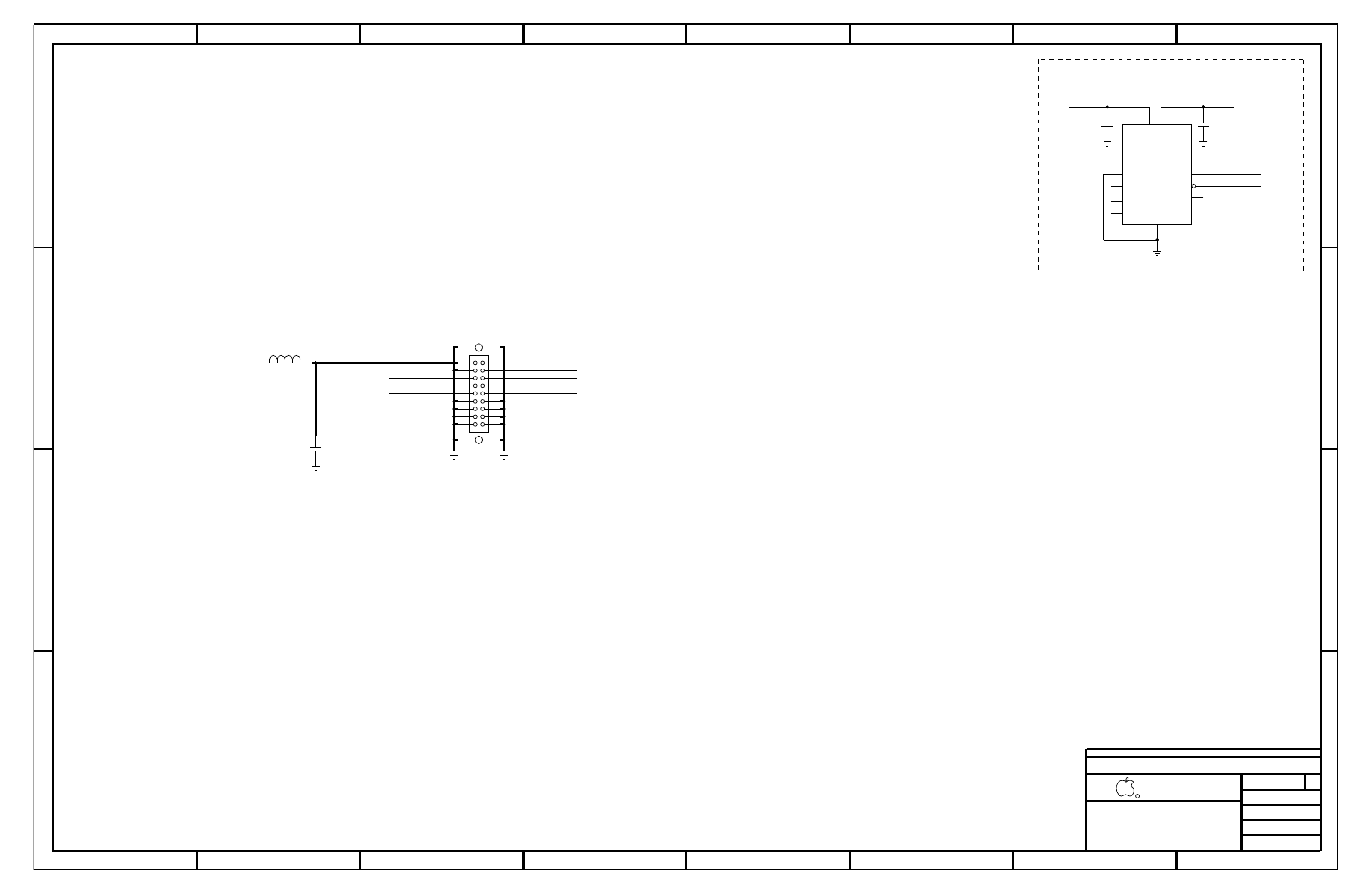

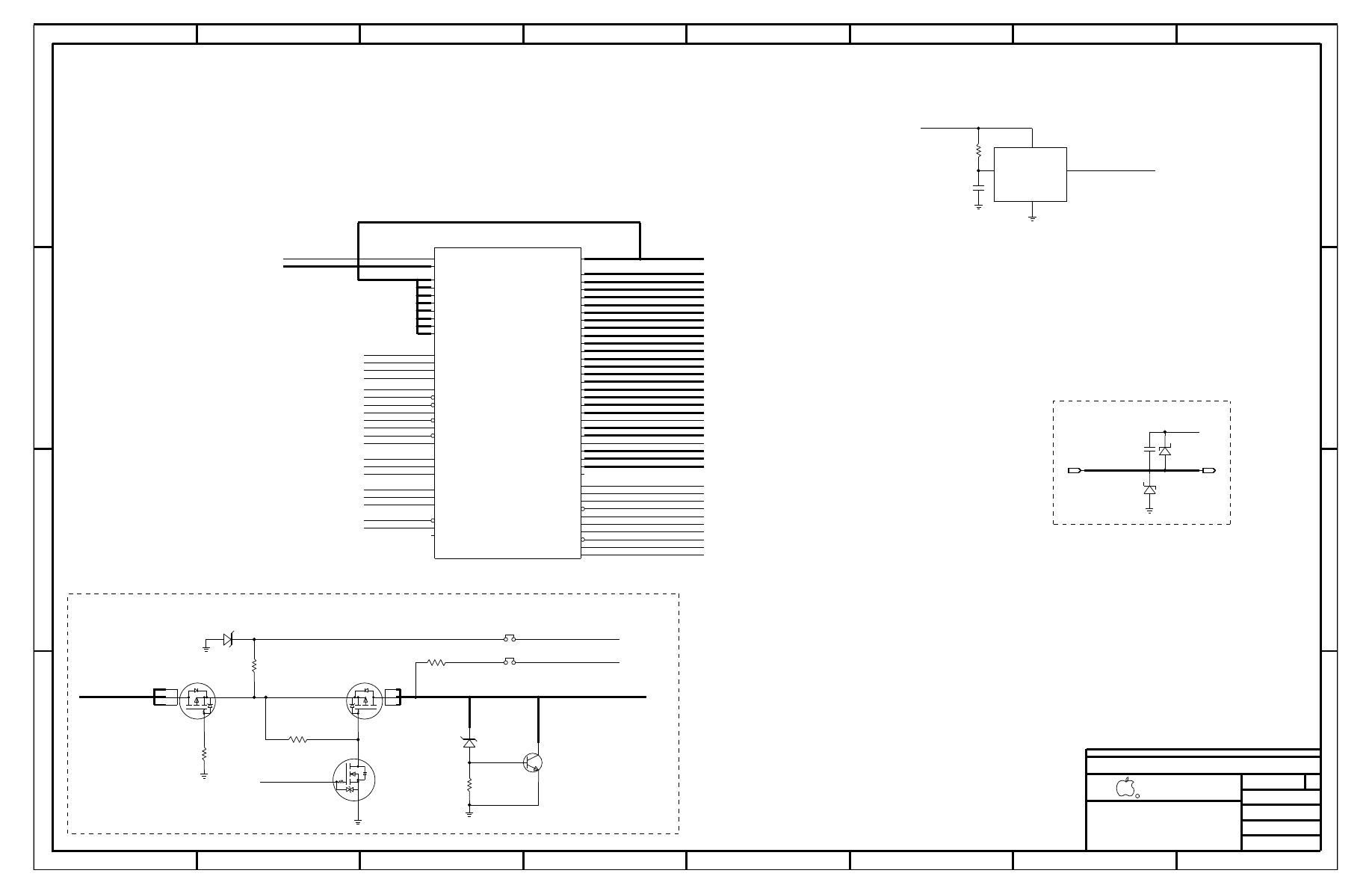

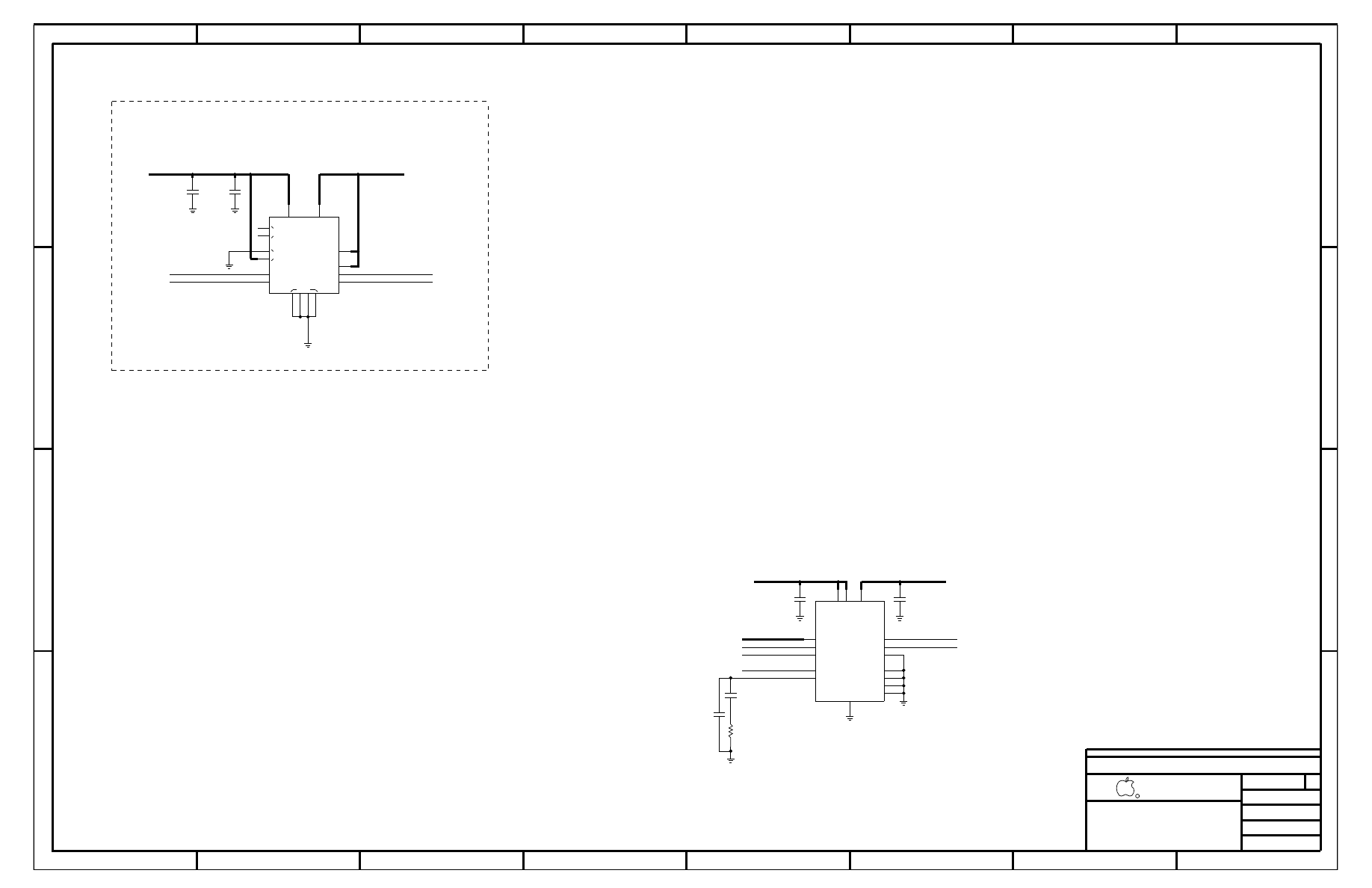

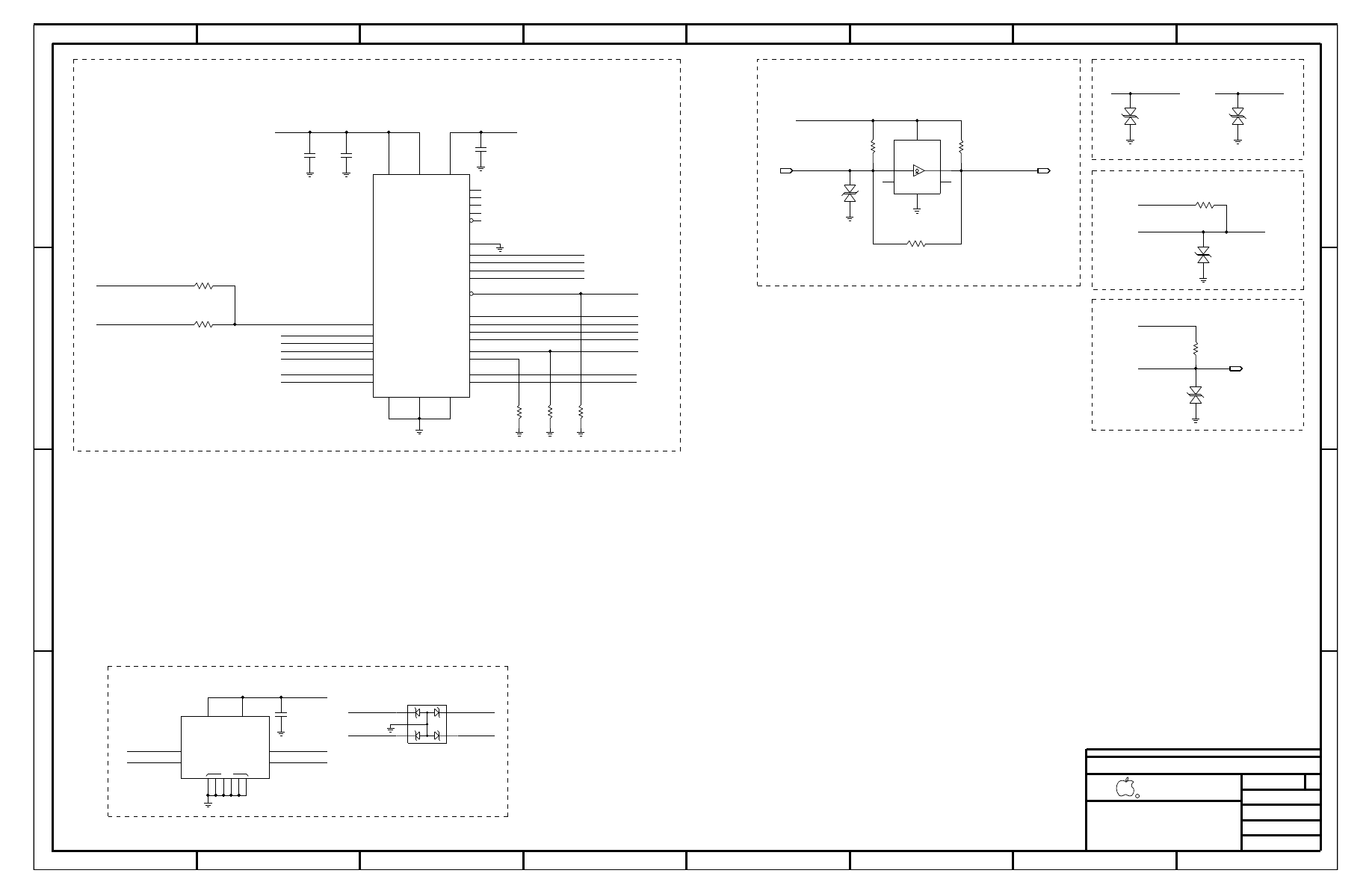

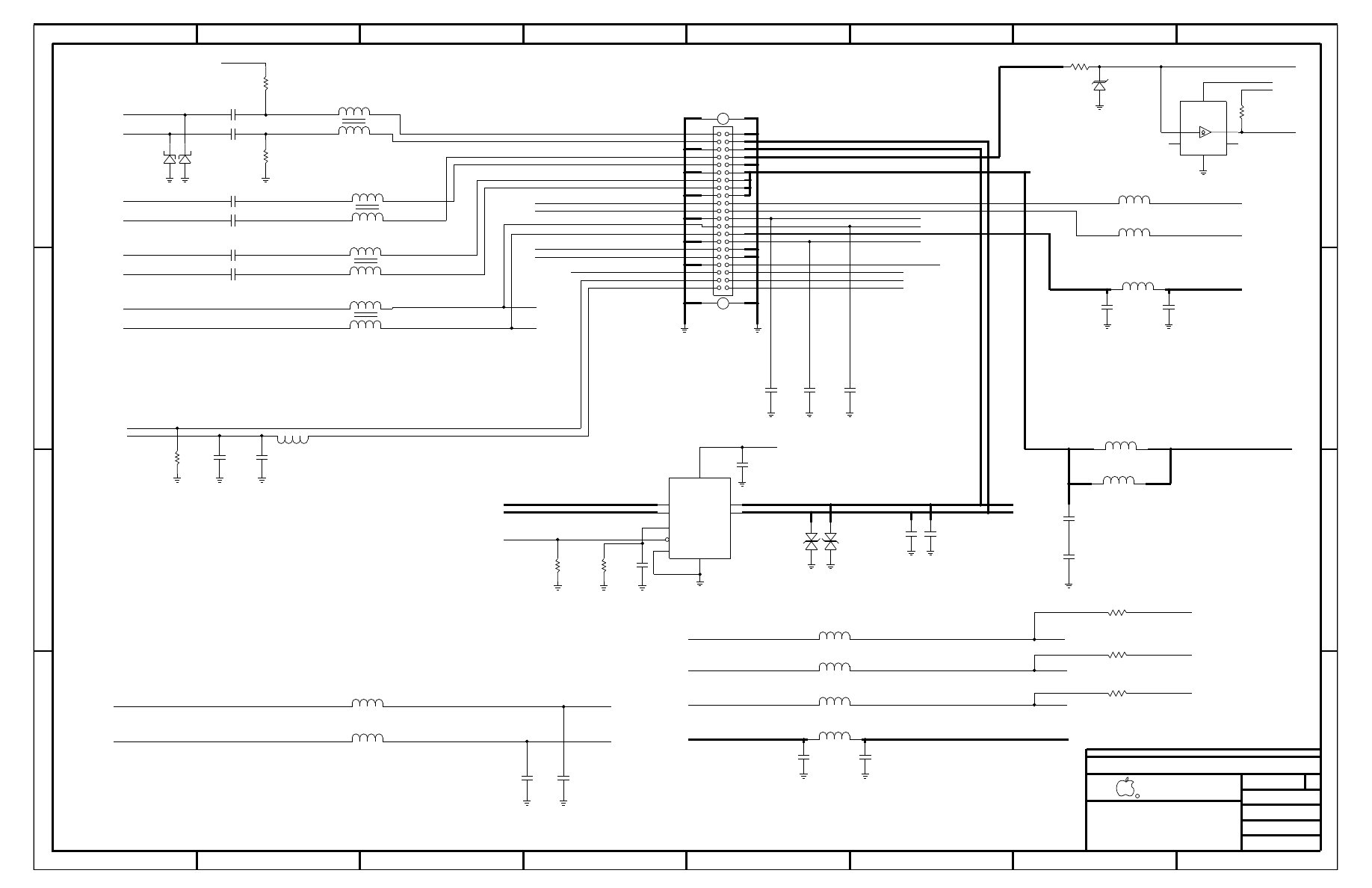

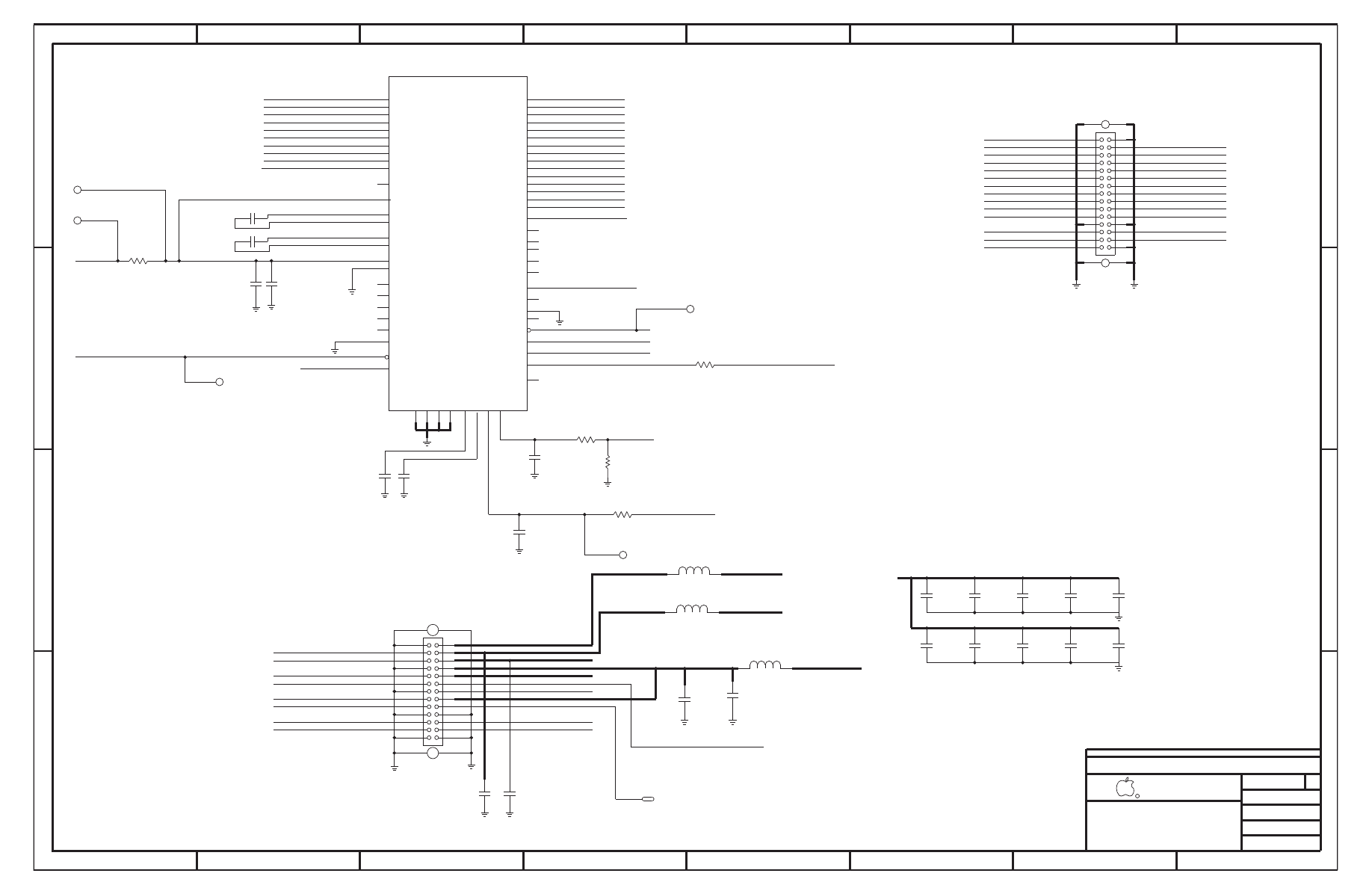

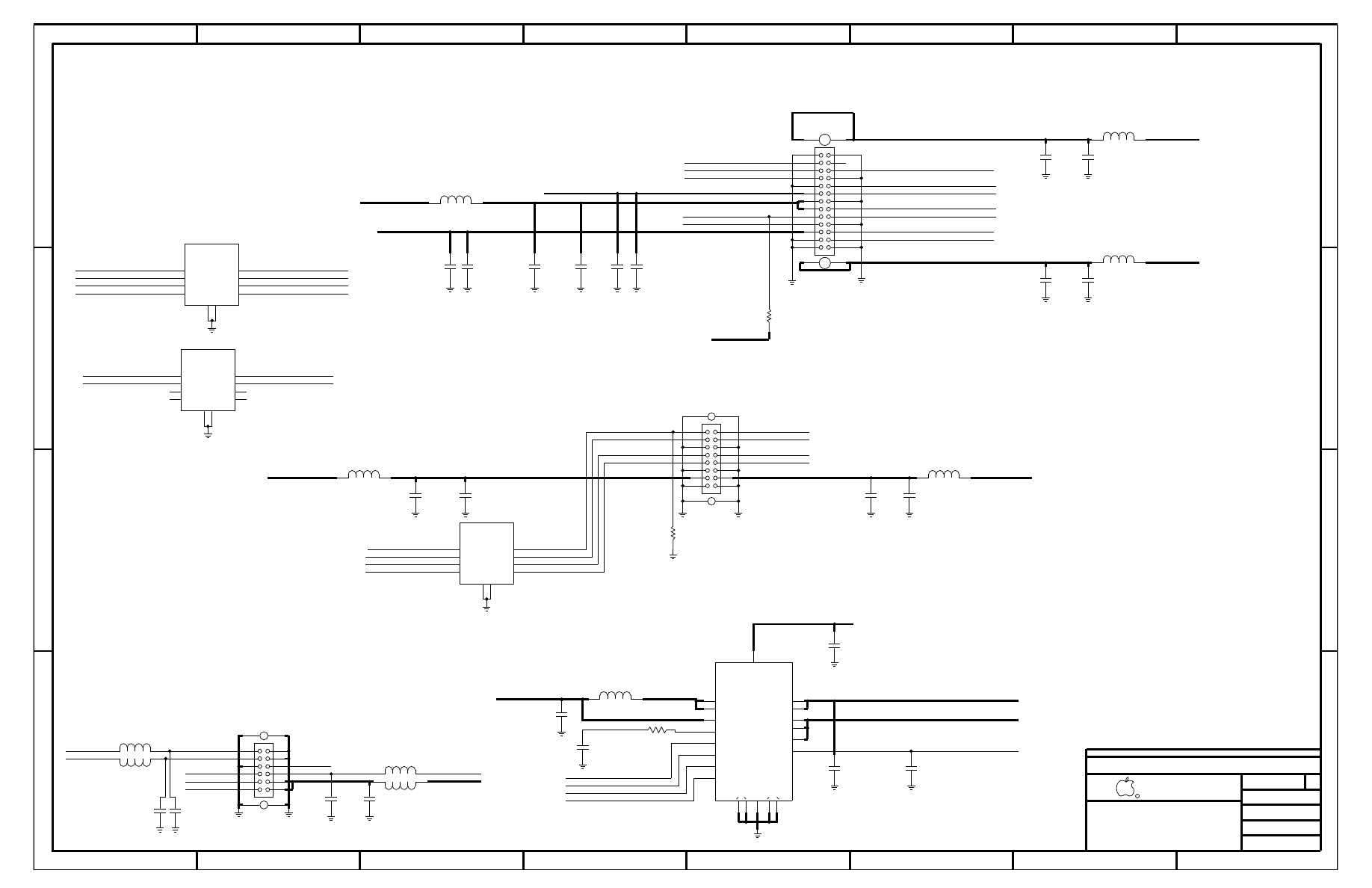

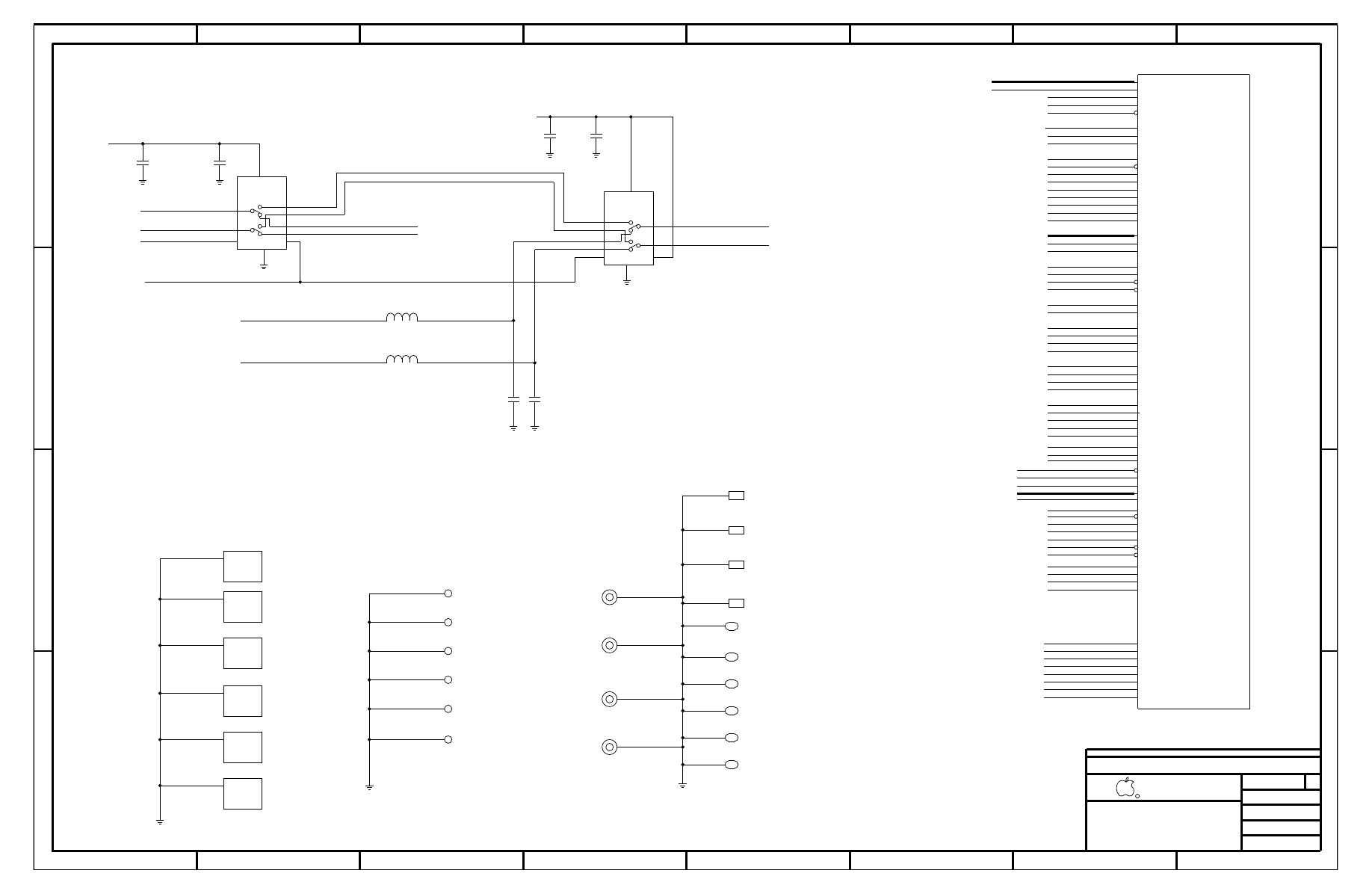

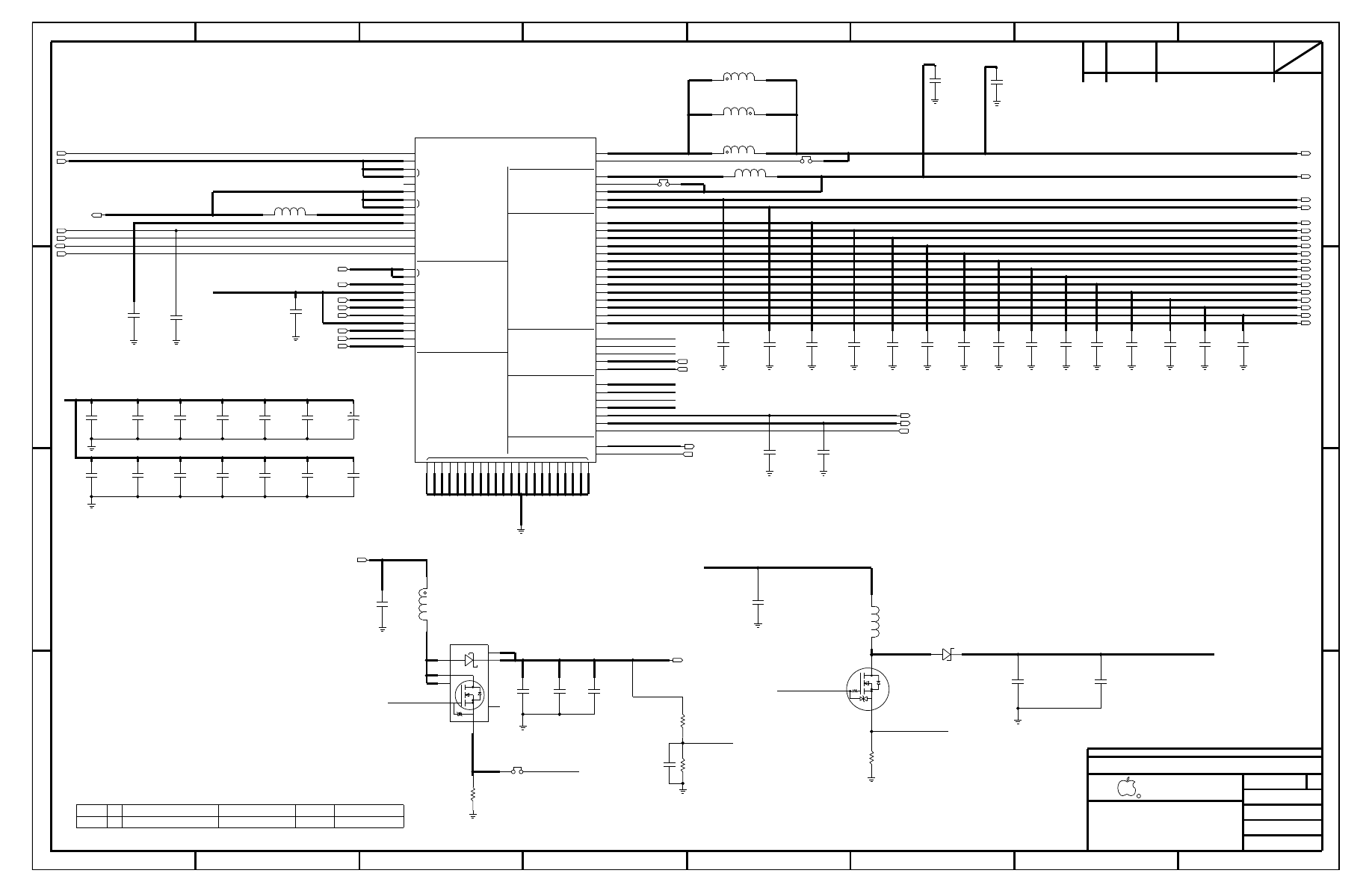

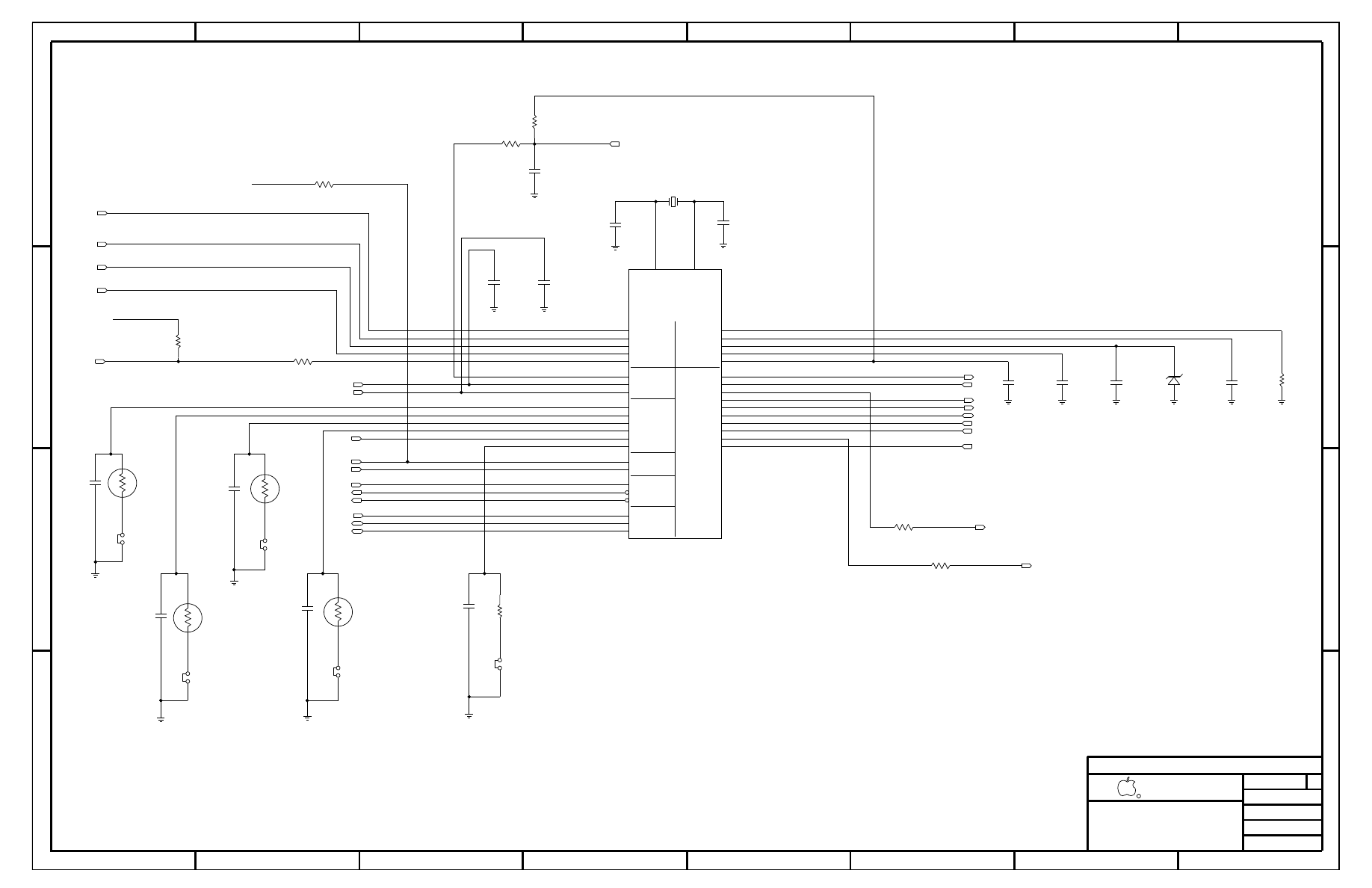

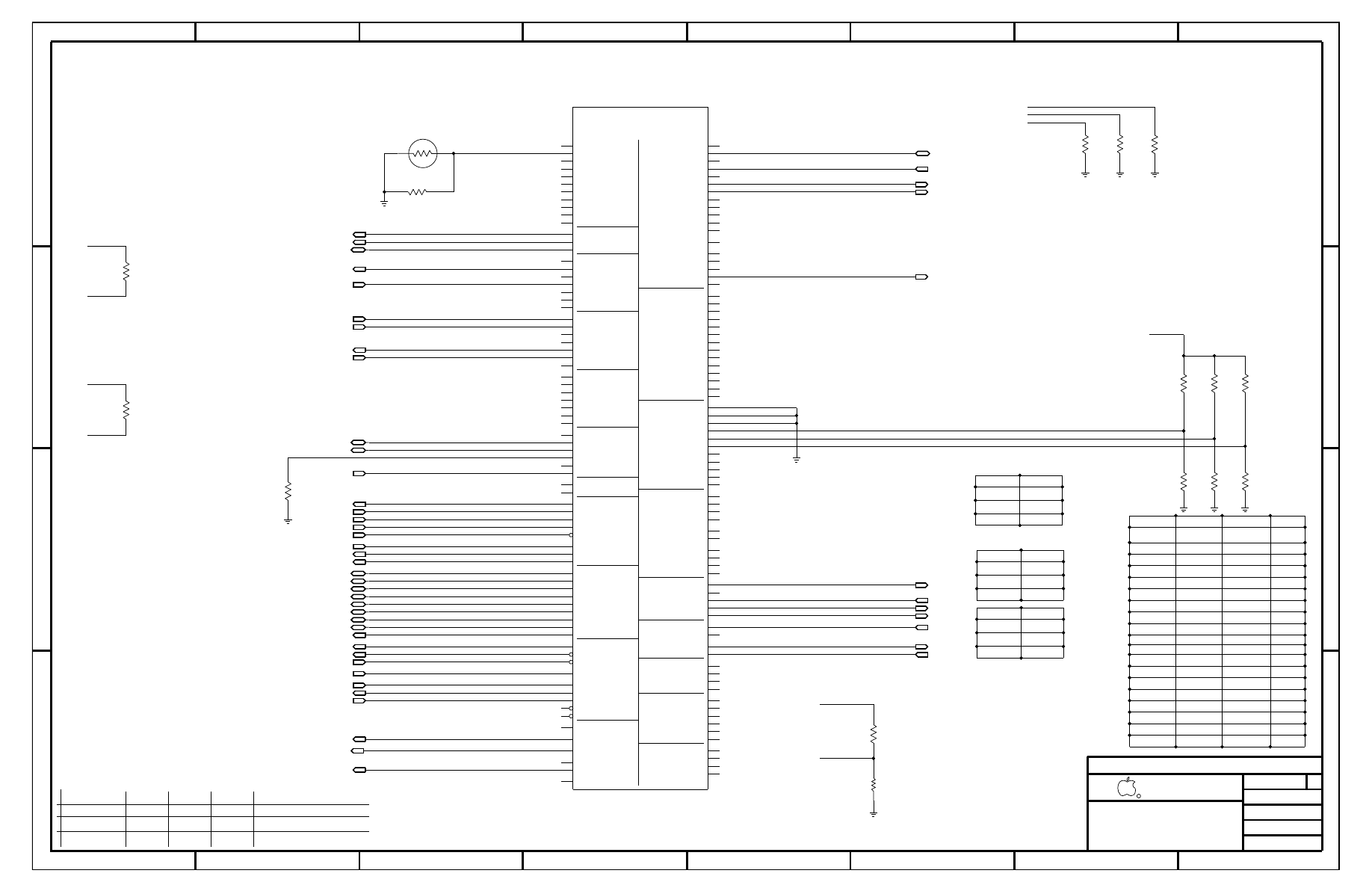

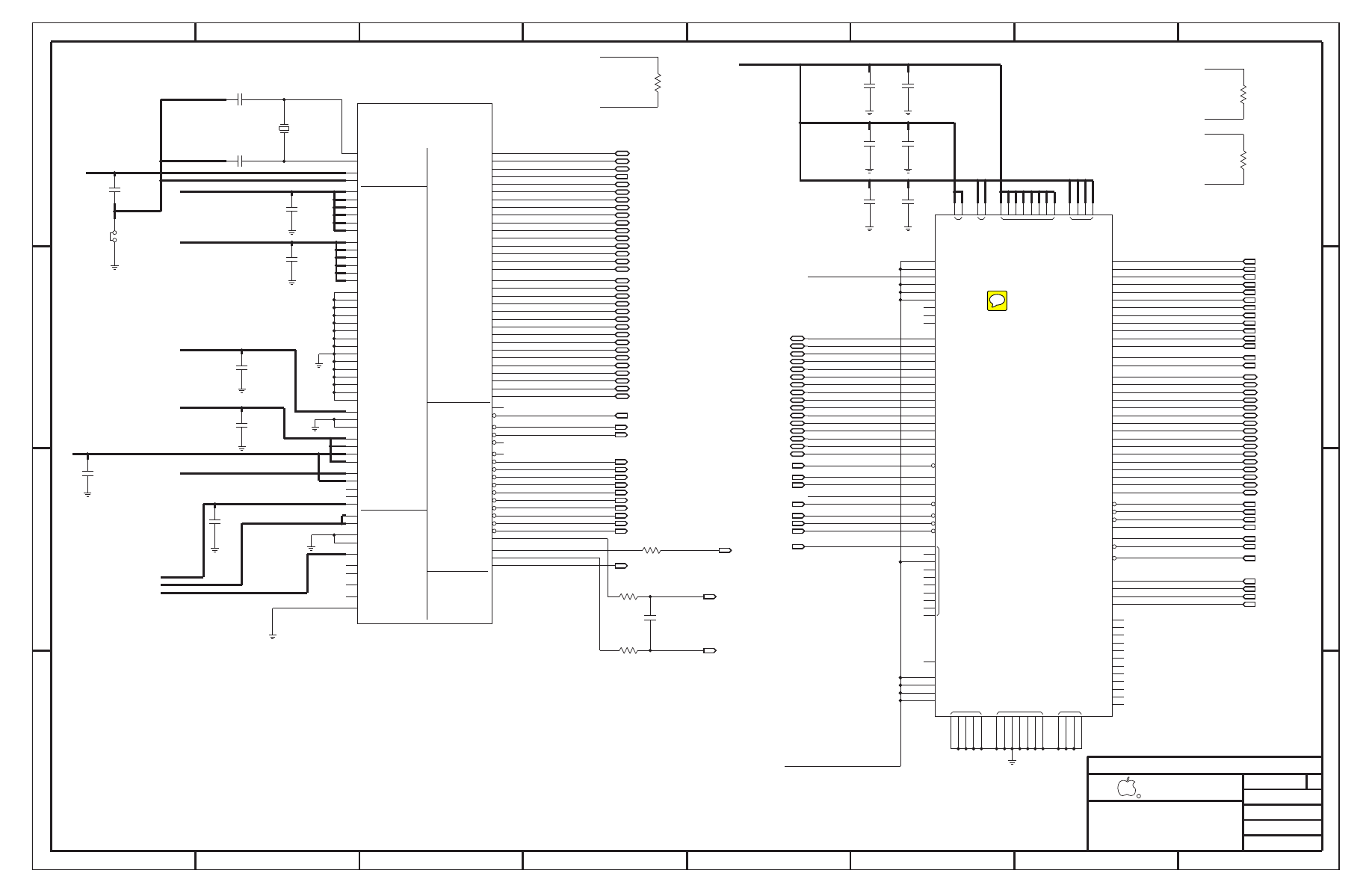

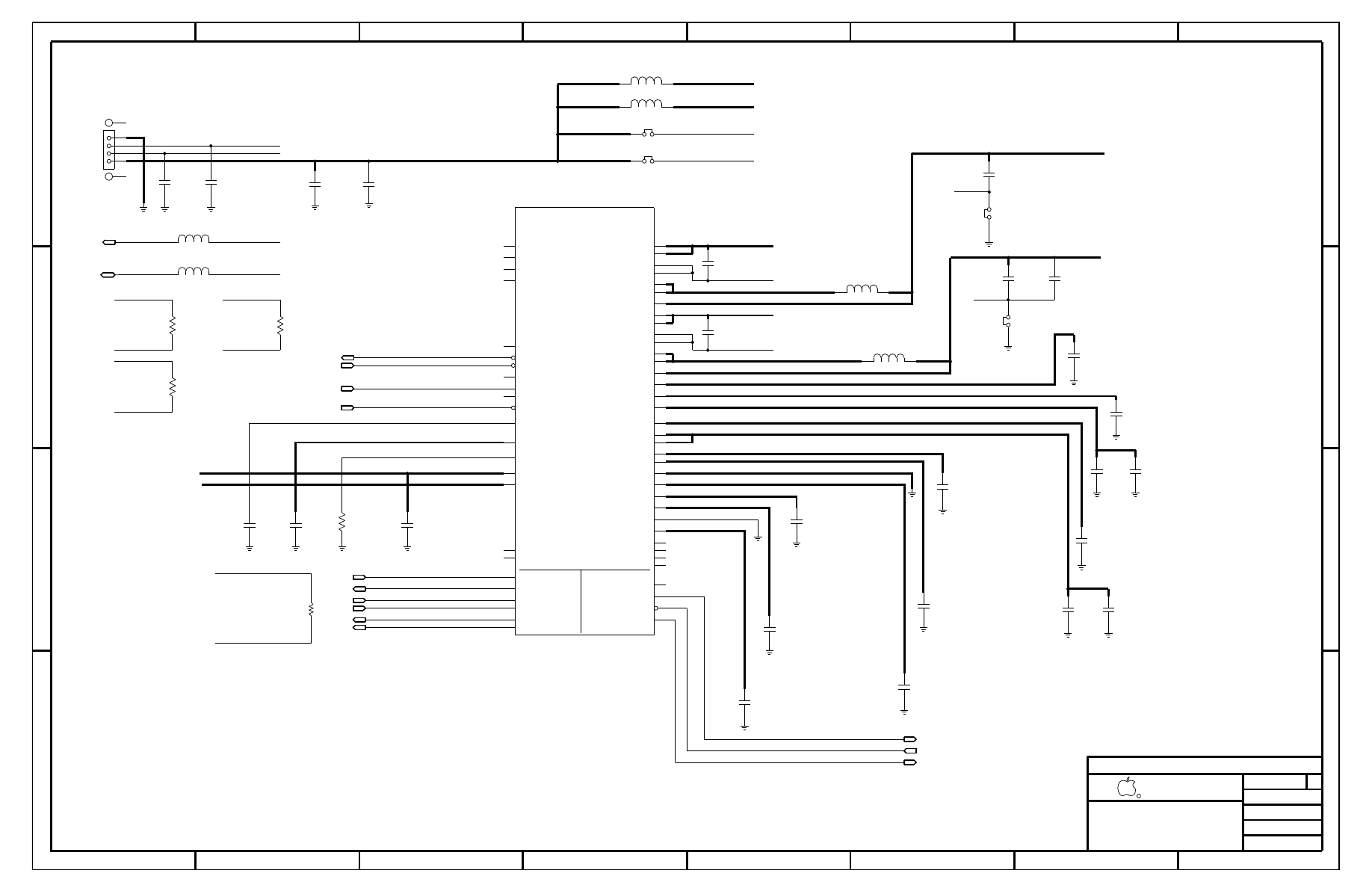

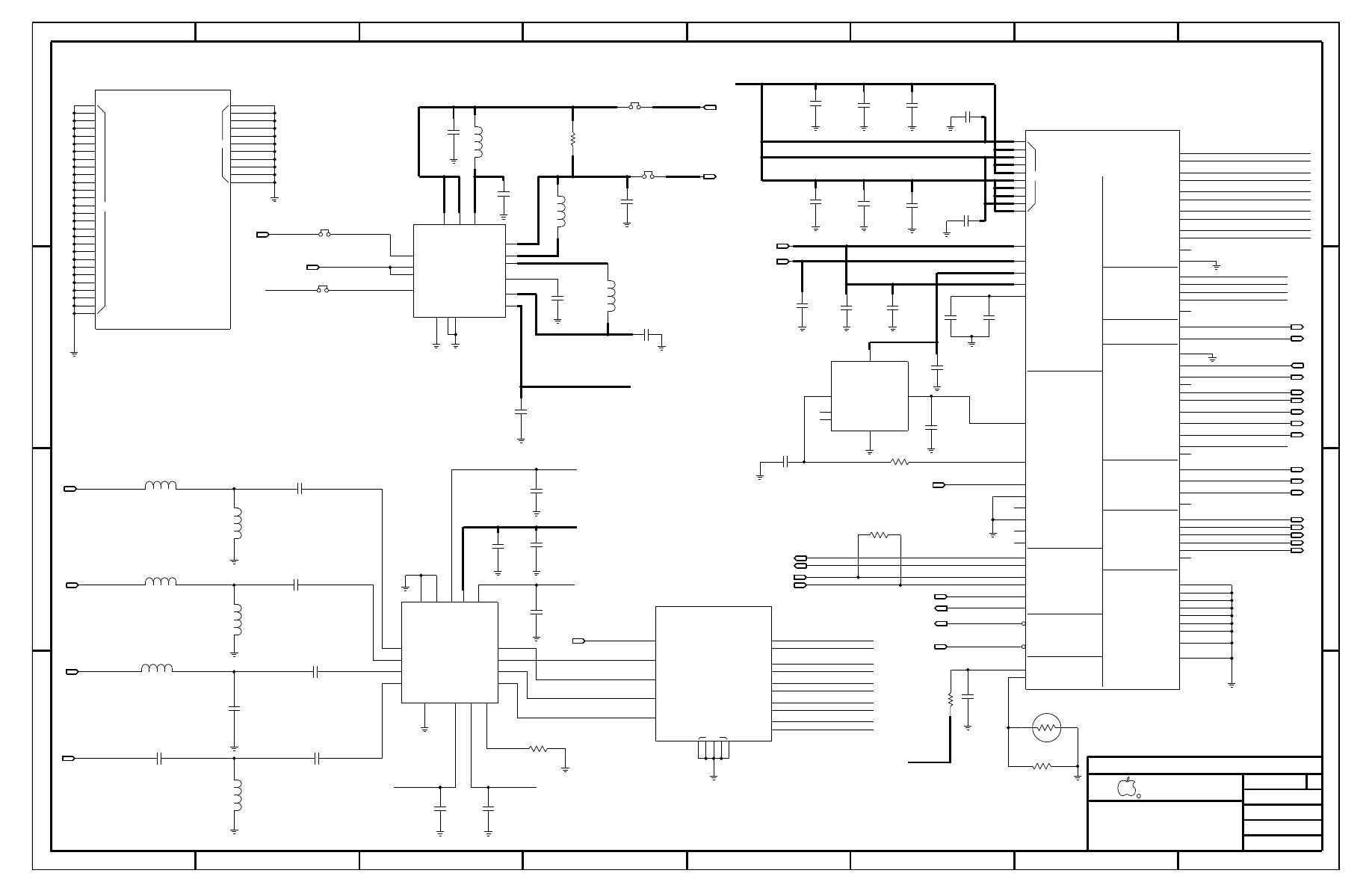

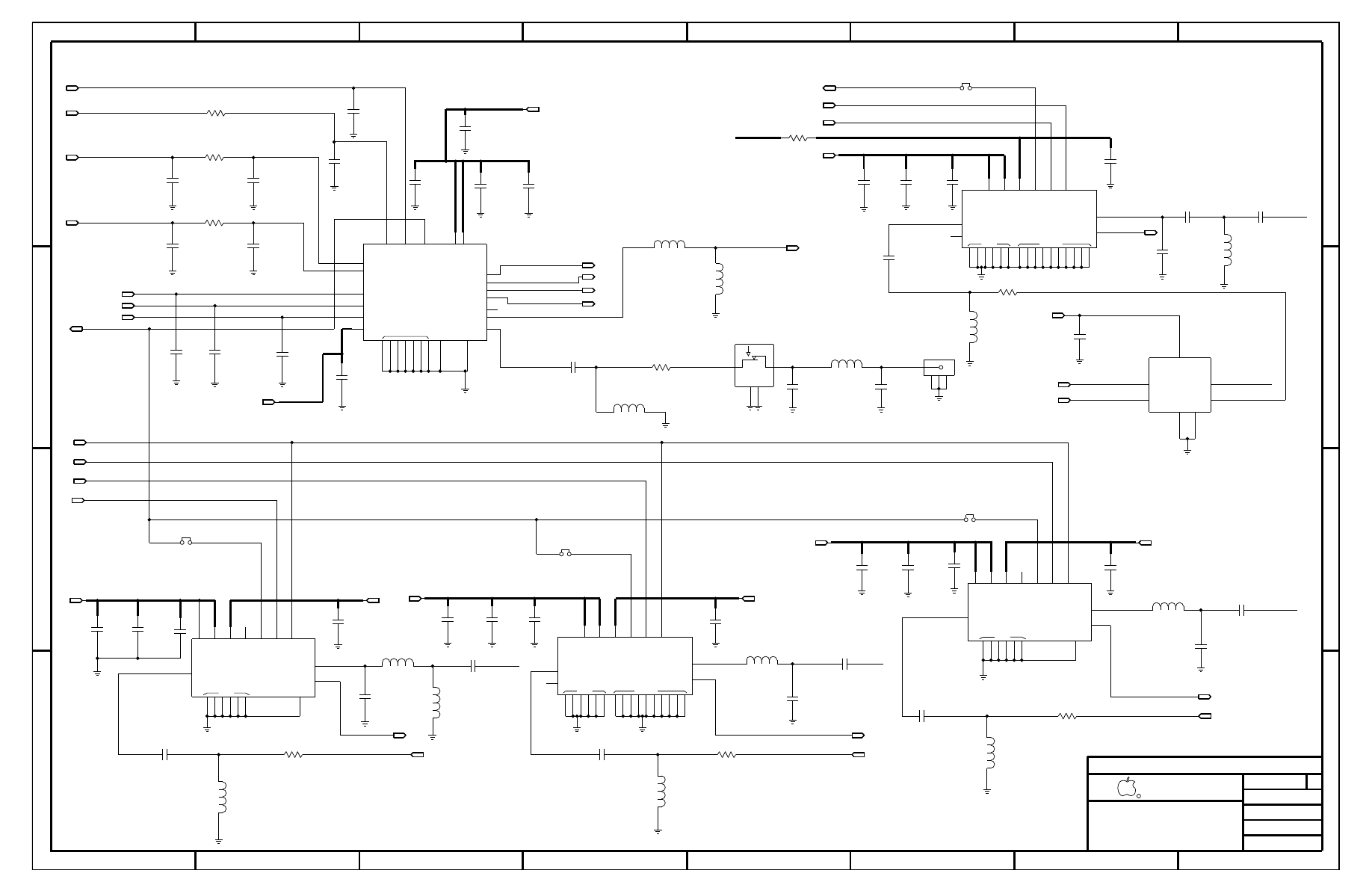

iPhone 4 Schematic

Jailbreake By OM Tesla

Big Thanks to Weaver &

130877 from Mobile-files!

J1_RF

A

D

C

B

A

D

C

B

8

7

6

5

4

3

2

1

8

7

6

5

4

3

2

1

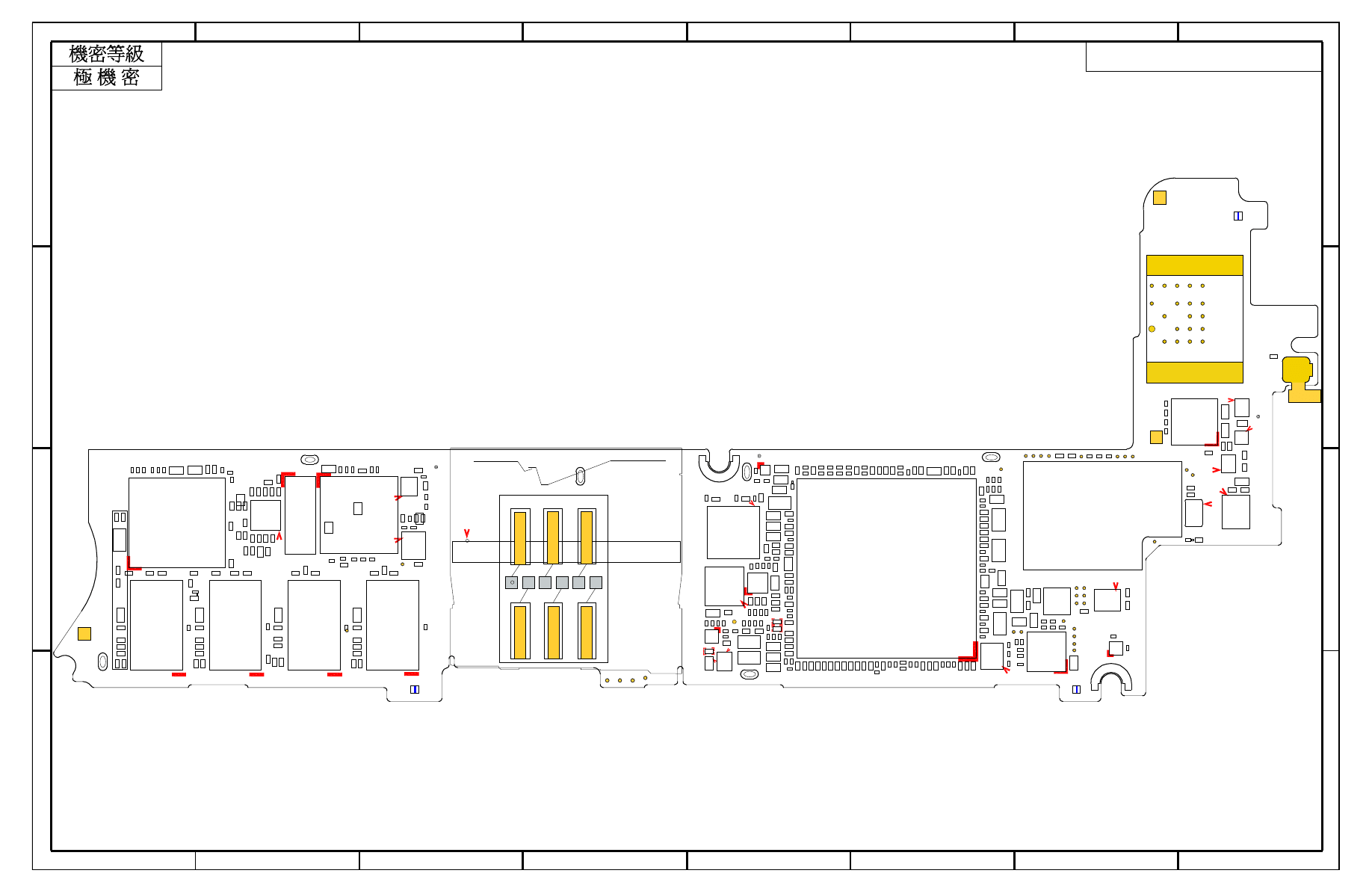

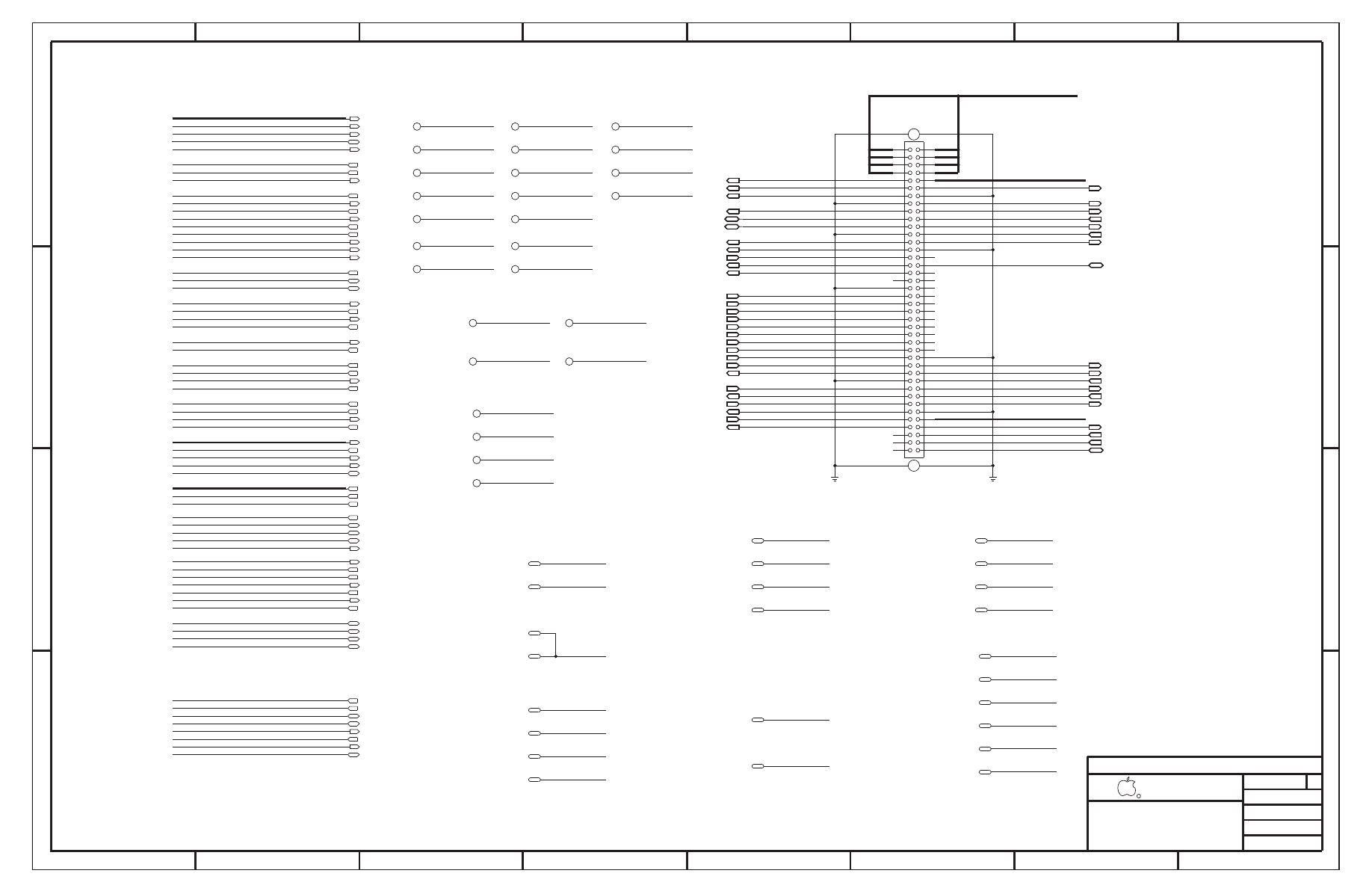

820-2548-10/820-2803-02 Top side

TP447

TP65_RF

TP56_RF

TP59_RF

TP12_RF

TP6

TP441

TP424

TP415

TP12

TP13

TP469

TP468

TP466

TP465

TP442

TP440

TP438

TP431

TP425

TP413

TP412

TP7

TP11

TP10

C

13

5_

R

F

U8_RF

U21_RF

G2_RF

U6_RF

L21_RF

L1_R

F

L5_R

F

L24_RF

C

88

_R

F

C

73

_R

F

C74_RF

C

75

_R

F

C76_RF

C

78

_R

F

C

79

_R

F

C81_RF

C83_RF

C

85

_R

F

C77_RF

C

11

4_

R

F

C

37

_R

F

C

42

_R

F

C

8

C9

C

21

C27

C29

C30

C

71

C

24

8

C

26

4

C

7

C

13

C

23

C16

C18

C

10

8

C118

C

12

6

C136

C

13

8

C

22

9

C231

C

23

2

C238

C244

C

12

2

C

17

9

C222

C239

C240

C

24

2

C153

C163

C

17

8

C

18

0

C107_RF

C

19

C

20

C44

C

40

_R

F

C

60

_R

F

C

61

_R

F

C

63

_R

F

C5_PMU

C6_PMU

C

7_

PM

U

C

23

0

L6

5_

RF

L84_RF

L413_RF

L1

3_

RF

L10_RF

L6_R

F

L4_R

F

L5

4_

RF

L7_R

F

L9_R

F

L15_RF

L1

6_

RF

L1

2_

RF

L11_RF

L23_RF

L19_RF

L8_R

F

X

W

29

_R

F

X W14_RF

R

74

_R

F

R

75

_R

F

R

73

_R

F

R

37

_R

F

R

3_R

F

R

14

_R

F

R

22

_R

F

R10_RF

R26

R

83

R100

R8_RF

C39_RF

C84_RF

C

23

8_

R

F

C

24

1_

R

F

C

24

6_

R

F

C

44

1_

R

F

C164_RF

C

28

C46

C60

C65

C115

C116

C128

C129

C152

C165

C166

C181

C182

C

18

3

C

18

4

C6

C154

C

16

8

C172

C

56

_R

F

C

31

_R

F

C291_RF

C

15

2_

R

F

C

13

0

C167

C

16

9

C

21

8

C219

C221

R

38

_PM

U

R45_PMU

R48_PMU

R

28

_R

F

R

84

_R

F

R

40

_R

F

R

5

R

46

R

47

R42

R129

FL

1

FL2_RF

C454_RF

C86_RF

C21_RF

C

10

4_

R

F

C

10

5_

R

F

C

69

_R

F

C

71

_R

F

C

17

2_

R

F

C

33

6_

R

F

C

16

5_

R

F

C

68

_R

F

C

72

_R

F

C

70

_R

F

C1_RF

C

32

_R

F

C

13

0_

R

F

C

35

_R

F

C

38

_R

F

C438_RF

C19_RF

C237_RF

C

17

_R

F

C331_RF

C242_RF

C236_RF

C

10

2_

R

F

C332_RF

C243_RF

C

32

2_

R

F

C244_RF

C330_RF

C245_RF

C333_RF

C443_RF

C

62

_R

F

C436_RF

C303_RF

C

14

1_

R

F

C9_RF

C125_RF

C

13

_R

F

C3_RF

C47_RF

C80_RF

C

94

_R

F

C437_RF

C

11

7_

R

F

C

12

0_

R

F

C82_RF

C249

C

1

C2

C3

C4

C10

C11

C

12

C

14

C15

C41

C

43

C

48

C

51

C52

C54

C

55

C56

C57

C

79

C

80

C81

C

95

C

96

C

10

2

C103

C

10

4

C

10

5

C

10

7

C111

C112

C114

C

12

1

C

13

2

C135

C

14

1

C

24

C25

C

26

C88

C

99

C109

C

11

7

C143

C150

C

15

1

C160

C

16

1

C

16

2

C

17

0

C

17

6

C

22

C201

C202

C190

C191

C

6_R

F

C

24

_R

F

C

22

5_

R

F

C15_RF

C

17

3

C

17

7

C228

C203

C

18

6

C63

R68_RF

R

41

_R

F

R6_RF

R25_RF

R81_RF

R7_RF

R9

R

3

R

4

R

43

R

77

R

87

R

88

R

41

9

R

42

4

R40

R

8

R

15

R

27

R

29

R7

R

76

R89

R72

R73

R2

R12

R19

R20

R

24

R78

R

44

R65

R

96

R97

R

12

3

R265

R266

R268

R275

R362

R

36

9

R

40

1

R

17

R58

R36

R80

R

71

R

1

R

25

R

33

R

92

R75

R

31

_R

F

R

16

_R

F

R6

R101

R102

R103

R

11

_R

F

R

12

_R

F

R41

R69

R

42

_R

F

R30_RF

R34_RF

R

35

_R

F

R

68

R

61

R94

R

98

R

28

C

13

6_

R

F

Y2_RF

L60_RF

L1

4_

RF

U33_RF

U14_RF

FL

1_

RF

G

3_R

F

X

W

20

_R

F

X

W

43

_R

F

X

W

4_

RF

PP1_RF

PP2_RF

PP3_RF

PP4_RF

PP1

PP5_RF

P P10_RF

P P11_RF

PP7_RF

PP8_RF

PP9_RF

P P12_RF

P P13_RF

P P14_RF

P P15_RF

P P16_RF

P P17_RF

P P19_RF

P P20_RF

P P21_RF

P P22_RF

P P23_RF P P24_RF

P P25_RF

P P26_RF

U2_RF

U9

C

13

9

U62

U7

S

P

1

SH1

SH5

U3

D3

D2

Y2

Q3

SL8

SL9

DZ5

XW2

X

W

2_

PM

U

X W5_PMU

X

W

6_

PM

U

X

W

4_

PM

U

U52

U2

X

W

1_

RF

X

W

7_

RF

X

W

8_

RF

C

53

C

77

U1_RF

U5_RF

U20_RF

U37_RF

U19_RF

U

7_R

F

SL1

SL3

S

L4

SL5

S

L6

S

L1

6

U8

Q1

F

L1

2_

R

F

F

L1

0_

R

F

X W10_RF

U16

FD2

FD1

FD6

C

87

_R

F

PP6_RF

X

W

9_

RF

SH2

C185

P P18_RF

R

43

_R

F

X

W

2_

RF

12

1

2

3

5

6

7

13

SP1_RF

J2

1 5 2 6 3 7

2

1

R21_RF

A

D

C

B

A

D

C

B

8

7

6

5

4

3

2

1

8

7

6

5

4

3

2

1

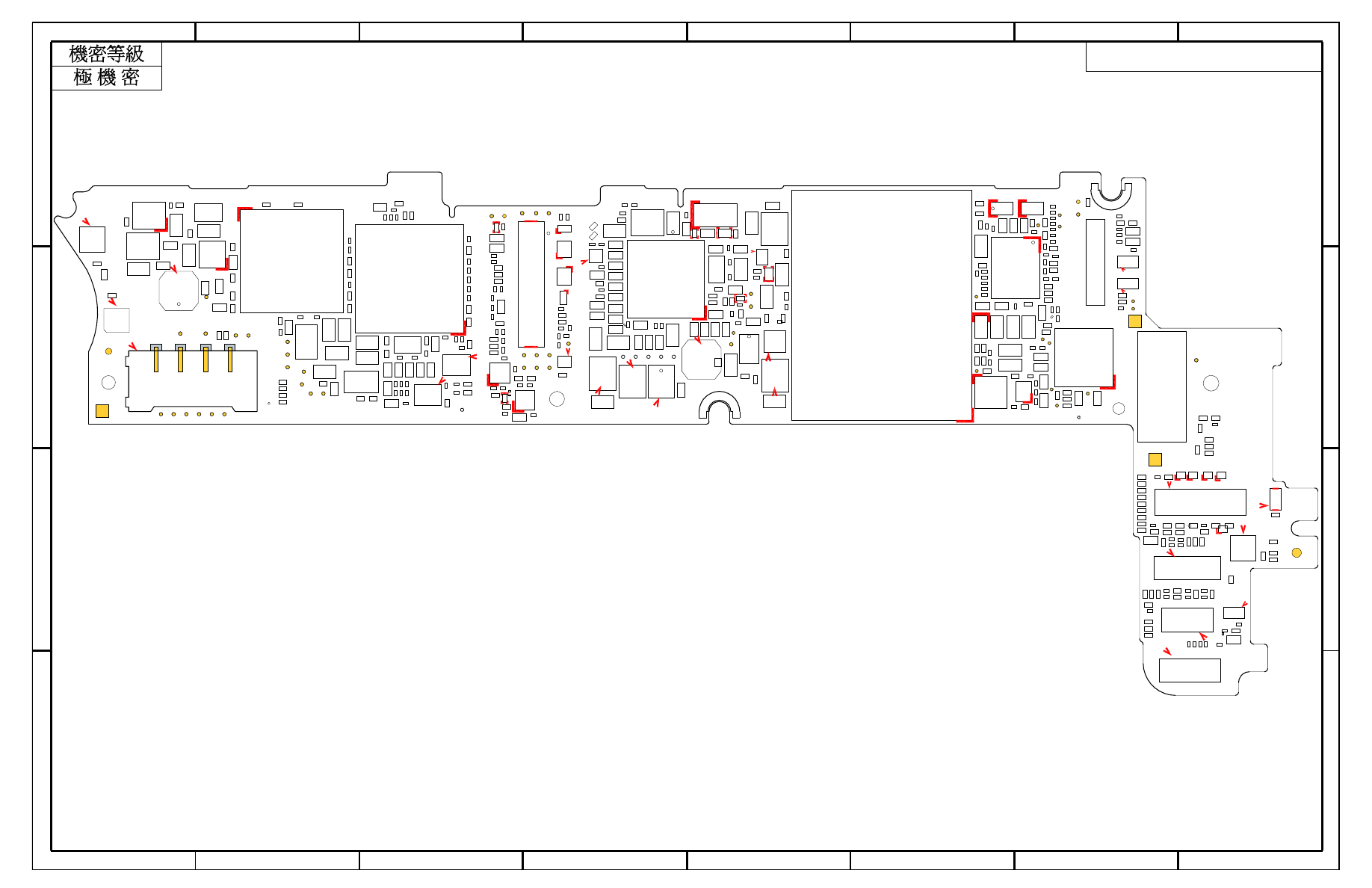

820-2548-10/820-2803-02 Bot side

U4

FL26

FL27

L5

L6

L13 L14

L17

L15

FD3

FD4

FD5

L16

J1

J9_RF

1

2

3

4

BS3

U17

L93_RF

C67_RF

U11_RF

R171_RF

F

L1

6

FL12

FL

9

FL8

F

L1

3

U4_RF

U9_RF

U6

J2_RF

J11_RF

BS1

BS2

J7_RF

J6

C

19

0_

PM

U

L2

1

1

BS4

X

W

13

_R

F

D1

D

1_

PM

U

X

W

1_

PM

U

X

W7_

PM

U

X

W

3_

PM

U

XW1

46

XW3

XW147_PMU

DZ1_P MU

D

Z6

D

Z

31

L1

C

67

_PM

U

D

Z1

2

D

Z9

D

Z1

3

D

Z

30

DZ28

DZ29

D

Z

11

DZ3

DZ4

DZ10

DZ2 DZ1

SL11

SL10

C

14

8

C134

C97

U15

L4

L3

F

L1

9

L8

L7

L11

Q

3_

PM

U

D

6

U48_PMU

S2

S1

C63_PMU

U60

R522_PMU

R18_PMU

SH3

SH4

J4

J7

U5

Q2

U1

J8

1

1

1

1

1

L3

_P

M

U

L1

_P

M

U

L9

L2_PMU

L7

_P

M

U

C27_RF

C29_RF

C30_RF

C

48

_R

F

C91

C82

C76

C

4_R

F

C

43

_R

F

C94

C

50

C45

C75

C68

C69

C70

C83

C84

C89

C

14

4

C

14

2

C

38

C37

J5

J3

U

70

Q1_PMU

U19

SP2_RF

L2_RF

L3_R

F

L1

8_

RF

PP11

PP10

PP8

PP9

PP18

PP17

PP16

PP2

PP5

PP4

PP3

PP7

PP6

L1

7_

RF

Y

1_

PM

U

Y1_RF

C522

C

2_

PM

U

C3_PMU

C

49

_

PM

U

C161_PMU

C

20

8

C

20

6

C

20

5

C

19

8

C87 C86

C210

C212

R11

R

70

R

11

9

R91

R90

R

38

_R

F

R

76

_R

F

R

97

_R

F

R

96

_R

F

R

95

_R

F

R

9_R

F

R45

R54

R

14

R

10

4

R

93

R

81

R

39

R

10

R67

R124

R

99

R

38

R

84

R

82

R

18

R

86

R85

R115

R113

R57

R56

R165_PMU

R

64

2

R741_PMU

R

51

6

R53

R

51

7_

PM

U

R13

R23

R79

R51

R50

R52

R48

R308

R

78

_R

F

R

66

_R

F

R

20

_R

F

R2_RF

R

53

_R

F

R

52

_R

F

R

50

_R

F

R

48

_R

F

R

47

_R

F

R

46

_R

F

R

18

_R

F

R

13

_R

F

R

58

_R

F

R

61

_R

F

R

57

_R

F

R

56

_R

F

C225

C177_PMU

C273

C204

C

25

0

C247

C

57

_R

F

C95_RF

C93_RF

C20_RF

C12_RF

C

36

_R

F

C

91

_R

F

C89_RF

C

54

_R

F

C

52

_R

F

C

25

_R

F

C98_RF

C96_RF

C64

C90

C487

C488

C197

C47

C49

C

8_R

F

C16_RF

C1

89

C1

88

C

33

C

17

9_

PM

U

C524

C187

C175

C

15

9

C145

C106

C74

C

61

C39

C253

C

31

C

20

9

C457_PMU

C454_PMU

C

45

0

C

44

9

C265_PMU

C

21

1

C200

C

2_R

F

C22_RF

C

5_R

F

C

11

_R

F

C

90

_R

F

C

92

_R

F

C51_RF

C

97

_R

F

C

7_R

F

F

L2

1

FL4_RF

F

L2

9

FL7

FL4 FL3

F

L2

8

FL

6

FL

3_

RF

FL7_RF

FL5_RF

FL2

FL5

FL25

FL20

FL18

FL15

FL14

FL11

FL10

FL24

FL23

FL22

R74

R1_PMU

R28_PMU

R

43

0

R

32

_R

F

R

95

R37

R

22

5_

PM

U

R515_PMU

R30

R16

R

51

9_

PM

U

R6_PMU

R

51

0

R

50

9

R

19

0_

PM

U

R

83

_

PM

U

R49_PMU

C69_PMU

C246

C

34

2

_R

F

C

25

1

C

41

6

C

29

0

C

25

9

C

14

7

C

45

3_

PM

U

C269_PMU

C

24

3_

PM

U

C178_PMU

C

16

8_

PM

U

C160_PMU

C

15

3_

PM

U

C

20

9_

PM

U

C

32

_

PM

U

C

34

_R

F

C33_RF

C55_RF

C59_RF

C41_RF

C

34

3

_R

F

C

65

_R

F

C

14

_R

F

C485

C40

C171

C

85

C252

C

47

4_

PM

U

C462_PMU

C

46

0_

PM

U

C459_PMU

C301_PMU

C

30

0_

PM

U

C299_PMU

C298_PMU

C291_PMU

C

27

4_

PM

U

C267_PMU

C

20

3_

PM

U

C191_PMU

C

17

6_

PM

U

C164_PMU

C

76

_

PM

U

C70_PMU

C68_PMU

C58_PMU

C47_PMU

C1_PMU

C456_PMU

C

23

_R

F

C53_RF

C

18

_R

F

R22

R21

R

50

0

_R

F

R4_RF

R19_RF

R

33

_R

F

X W61_RF

X

W

24

_R

F

X

W

5_

RF

X

W

12

_R

F

X

W

11

_R

F

L10

L12

L2

2_

RF

L2

0_R

F

FL6_RF

FL8_RF

C

78

C108_RF

C226

C67

C10_RF

C

66

C255

C270

C256

C245

C34

C32

C125

C137

C156

C164

C

14

0

C

22

3

C220

C

13

3

C119

C110

C

8_

PM

U

C4_PMU

C

99

_R

F

C272_PMU

C486

C42

C193

C199

C124

C405

C

16

3_

PM

U

C

52

6

C

28

6

C

22

7

C224

C214

C207

C

19

6

C

19

5

C194

C192

C158

C157

C131

C127

C113

C

10

0

C98

C73

C72

C

62

C

59

C

26

3

C

26

2

C

26

1

C

26

0

C36

C

35

C266_PMU

C

83

_

PM

U

C

82

_

PM

U

C455_PMU

C523

C154_PMU

C

15

1_

PM

U

C42_PMU

C58

C5

C

25

8

C

25

7

C66_RF

C64_RF

C101_RF

C100_RF

C58_RF

C275

C

15

5

C

14

9

C

14

6

C

46

_R

F

C

44

_R

F

C

26

_R

F

C

45

_R

F

C

28

_R

F

L25_RF

C

17

C

49

_R

F

C50_RF

L92_RF

L17_PMU

TP11_RF

TP10_RF

TP3_RF

TP8

TP32_RF

TP477

TP475

TP474

TP457

TP452

TP451

TP450

TP449

TP443

TP432

TP433

TP430

TP429

TP423

TP421

TP

2

TP

1

TP455

TP

5

TP3

TP33_RF

TP68_RF

TP7_RF

TP29_RF

TP28_RF

TP24_RF

TP22_RF

TP5_RF

TP4_RF

TP2_RF

TP89_RF

TP82_RF

TP74_RF

TP6_RF

TP1_RF

TP30_RF

TP444

XW1

L1

6_

PM

U

L1

8_

PM

U

3. ALL CRYSTALS & OSCILLATOR VALUES ARE IN HERTZ.

8

1. ALL RESISTANCE VALUES ARE IN OHMS, 0.1 WATT +/- 5%.

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

IV ALL RIGHTS RESERVED

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

II NOT TO REPRODUCE OR COPY IT

3

B

7

ECN

REV

BRANCH

DRAWING NUMBER

REVISION

SIZE

D

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

DRAWING TITLE

THE POSESSOR AGREES TO THE FOLLOWING:

Apple Inc.

SHEET

R

DATE

D

A

C

THE INFORMATION CONTAINED HEREIN IS THE

2. ALL CAPACITANCE VALUES ARE IN MICROFARADS.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

C

3

4

5

6

D

B

8

7

6

5

4

2

1

1

2

APPD

CK

DESCRIPTION OF REVISION

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_TABLEOFCONTENTS_HEAD

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

CRITICAL

BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_ALT_ITEM

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

TABLE_ALT_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL

BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

CRITICAL

BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_ALT_ITEM

TABLE_5_ITEM

TABLE_ALT_ITEM

TABLE_TABLEOFCONTENTS_ITEM

TABLE_TABLEOFCONTENTS_ITEM

CRITICAL

BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_TABLEOFCONTENTS_ITEM

CRITICAL

BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL

BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

CRITICAL

BOM OPTION

TABLE_5_HEAD

PART#

DESCRIPTION

QTY

REFERENCE DESIGNATOR(S)

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

PART NUMBER

ALTERNATE FOR

PART NUMBER

BOM OPTION

REF DES

COMMENTS:

TABLE_ALT_HEAD

N90 SINGLE_BRD PVT

H3P ALTERNATES

L2_PMU ALTERNATE

L7_PMU ALTERNATE

PMU POWER IND ALTERNATE

G2_RF ALTERNATES

SCH 051-7921

BOM 639-0648(16GB,USI)

BRD 820-2548

MCO 056-3008

BOM 630-9941(16GB,MURATA)

Y2_RF ALTERNATE

LCD BL DRIVER ALTERNATE

Y1_PMU ALTERNATE

NAND BOM OPTIONS

VIDEO BUFFER ALTERNATE

L9 (STROBE) ALTERNATE

G3_RF ALTERNATES

BOM 639-0607(64GB,MURATA)

PMU POWER IND CALLOUT

BB MEMORY BOM CALLOUT

SCH & PCB BOM CALLOUT

H3P BOM CALLOUT

BOM 639-0437(32GB,USI)

BOM 639-0608(64GB,USI)

BOM 639-0609(32GB,MURATA)

WIFI/BT BOM OPTIONS

N90 EEE BOM LABELS

FL1_RF ALTERNATES

Y1_RF ALTERNATES

1 OF 29

Fri Apr 16 15:07:25 2010

CR-1 : @SINGLE_BRD_LIB.MLB(SCH_1):PAGE1

0000880153

A

051-7921

A.0.0

1 OF 18

PRODUCTION RELEASED

2010-03-23

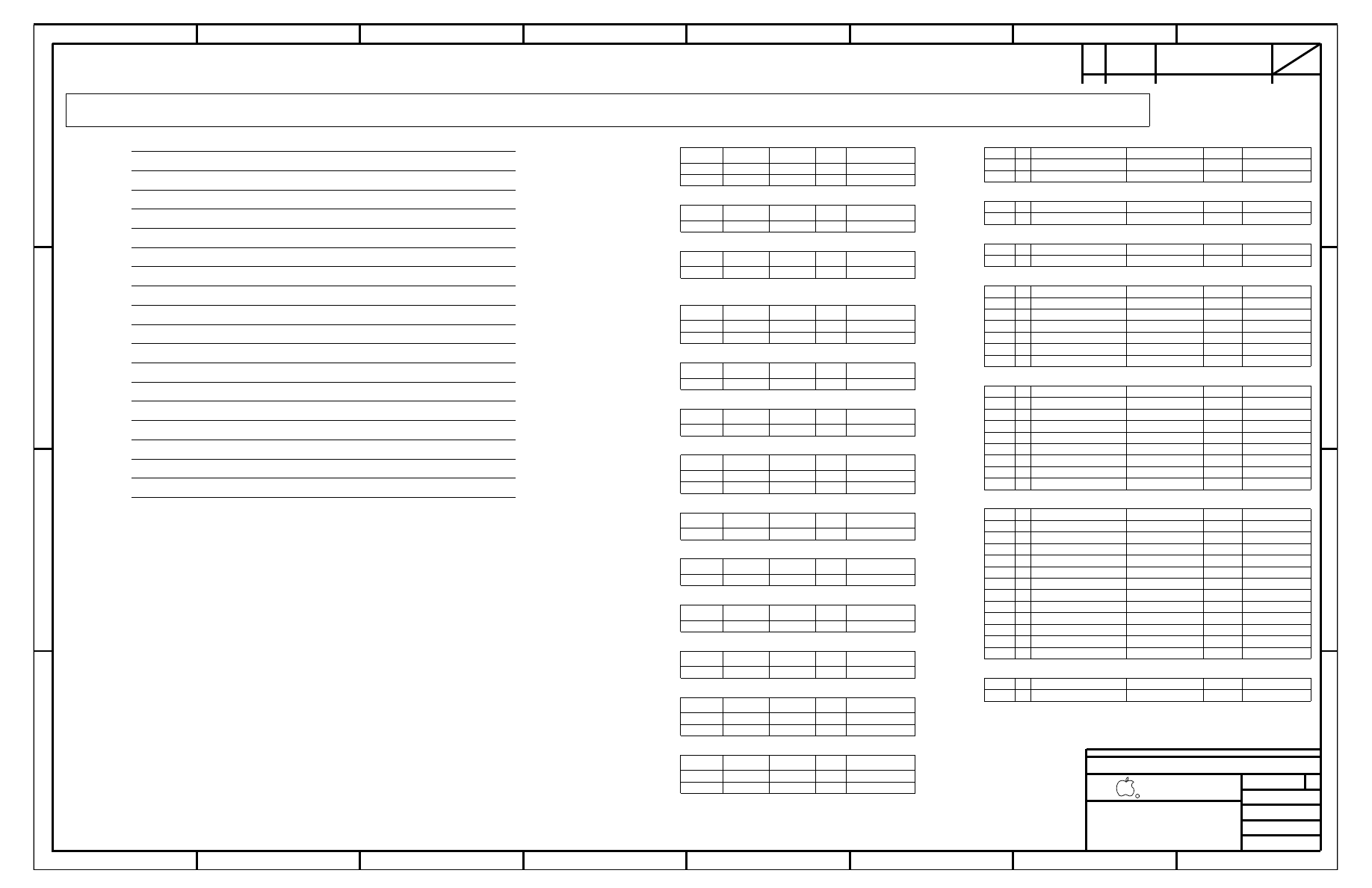

TABLE OF CONTENTS

H3 JTAG, USB ,MISC

ASHLEY PMU

SIM,ACCEL,OVP,GYRO COMPASS

HPARK, SWITCH ESD, SIM CARD

197S0342

RADIO,USB MUX,EM PARTS

AP PWR(CONT.)

197S0329

197S0299

L1_L3_L16_L18_PMU

CYNTEC INDUCTORS

SYNC_MASTER=N/A

TABLE OF CONTENTS

197S0371

155S0452

197S0364

?

?

155S0435

16GB SAMSUNG 35NM FLASH WLGA52

CAMERA,STROBE,SENSOR B2B

Y2_PMU

197S0297

?

152S1051

?

?

197S0369

197S0299

Y1_PMU

607-6810

607-6809

?

Y1_PMU

197S0369

?

?

197S0299

Y1_PMU

376S0768

376S0769

Q1_PMU

LCD BL FET DRIVER

152S0927

L7_PMU

?

152S0928

?

L2_PMU

152S1172

USI ID RESISTOR

64GB NAND CE7 CE8 JUMPERS

EEE_D7F

INTERSIL BUFFER

353S2684

U9

353S2493

?

152S1173

L9

152S0979

?

197S0299

?

Y1_RF

197S0369

197S0299

?

Y1_RF

197S0329

197S0334

197S0292

?

G2_RF

FL1_RF

G3_RF

197S0349

G3_RF

?

197S0349

POWER INDUCTORS

117S0161

339S0091

DATE

SYNC MASTER

BB_MEM_PROGRAMMED

2

EEE FOR 630-9941 (16G)

H3P WITH 512MB SAMSUNG DDR

U4_RF

EEE_6LU

14

H3P + ELPIDA 512MB

339S0108

339S0108

339S0126

H3P + HYNIX 512MB

U52

339S0123

U52

?

?

EEE FOR 639-0608 (64G)

N90_SINGLE_BOARD

1

Y

11

11

9

9

7

7

6

6

8

8

10

12

12

14

15

15

16

16

17

17

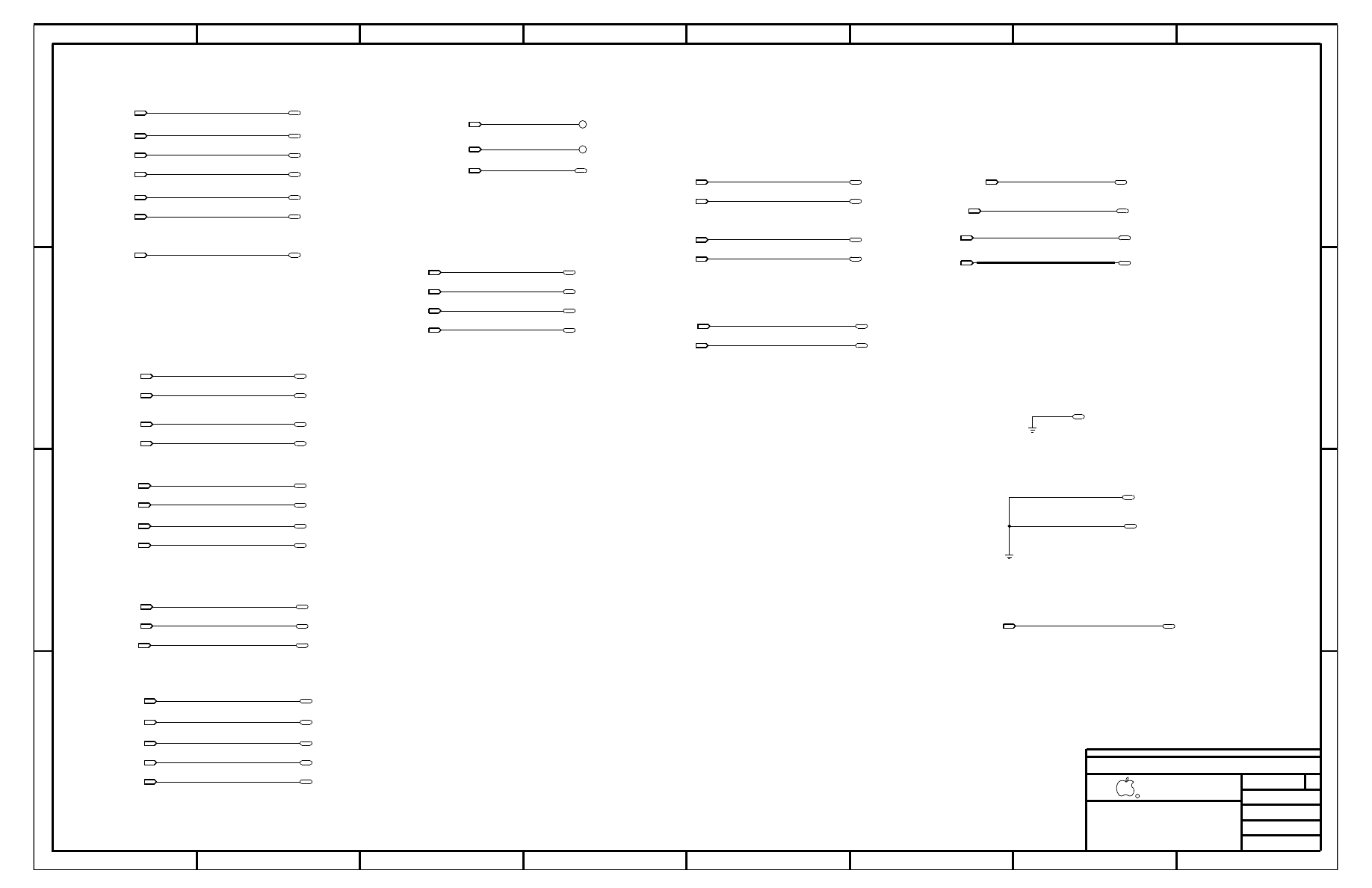

TEST POINTS

18

18

1

1

2

2

3

3

AP PWR

4

4

CSA PAGE

5

5

820-2548

PCB

?

Y

?

1

U52

339S0108

1

Y

BB_MEM

GOOD_MURATA

1

Y

825-2029

BETTER_MURATA

1

825-2029

GOOD_USI

825-2029

1

Y

EEE_DPM

GOOD_MURATA

Y

1

BEST_MURATA

Y

U1

GOOD_USI

Y

U1

BETTER_USI

U1

Y

BEST_USI

Y

1

U1

BEST_USI

R101, R102

Y

EEE_D7D

BEST_MURATA

825-2029

1

Y

BETTER_USI

Y

Y

1

BETTER_MURATA

U1

1

Y

BEST_MURATA

R101, R102

Y

2

GOOD_MURATA

U2_RF

Y

339S0092

GOOD_MURATA

Y

117S0161

339S0092

BETTER_MURATA

Y

U2_RF

117S0161

Y

R47_RF

BEST_USI

USI WIFI_BT MODULE

U2_RF

1

BEST_MURATA

U2_RF

339S0092

BEST_MURATA

1

117S0161

Y

GOOD_USI

Y

U2_RF

1

GOOD_USI

R46_RF

Y

1

USI WIFI_BT MODULE

BETTER_USI

1

339S0091

U2_RF

Y

BETTER_USI

R46_RF

USI ID RESISTOR

1

Y

R46_RF

1

BUTTON B2B, COMPASS

DOCK,SPKR AMP

13

13

335S0707

1

1

1

1

1

1

EEE FOR 639-0437 (32G)

1

U1

EEE_BA0

EEE_D7E

1

335S0682

10

L61 CODEC

ANALOG VIDEO,H3 NAND, NAND

?

1

Y

N90_SCHEMATIC_TOP

SCH

051-7921

CONTENTS

H3 GPIO,UART,SPI,I2S,I2C,SDIO

H3 MIPI,DPORT,SMIA

HPHONE FILTERS, MIKEY

NIMBUS, GRAPE, LCD CONN.

PDF PAGE

341S2509

339S0091

Y

BETTER_MURATA

EEE FOR 639-0648 (16G)

EEE FOR 639-0607 (64G)

EEE FOR 639-0609 (32G)

1

825-2029

825-2029

335S0665

335S0707

117S0161

335S0682

335S0665

117S0161

1

607-6809

Y

32GB SAMSUNG 35NM FLASH TLGA52

64GB SAMSUNG 35NM FLASH LGA52

R47_RF

Y

BEST_USI

16GB SAMSUNG 35NM FLASH WLGA52

32GB SAMSUNG 35NM FLASH TLGA52

64GB SAMSUNG 35NM FLASH LGA52

64GB NAND CE7 CE8 JUMPERS

117S0161

Y

BEST_USI

SYNC_DATE=N/A

?

Y

R47_RF

MURATA WIFI_BT MODULE

MURATA ID RESISTOR

MURATA WIFI_BT MODULE

MURATA ID RESISTOR

MURATA WIFI_BT MODULE

MURATA ID RESISTOR

USI WIFI_BT MODULE

USI ID RESISTOR

117S0161

L1_L3_L16_L18_PMU

REF

GND

IN

OUT

HSIC_VDD121

HSIC_VDD122

PLL0_AVDD11

USB_BRICKID

USB_VBUS

USB_DM

USB_DP

USB_ANALOGTEST

USB_REXT

HSIC_DVDD

FUSE1_FSRC

CFSB

DDR1_CKEIN

HSIC_DVSS

HSIC_VSS121

HSIC_VSS122

PLL0_AVSS11

PLL1_AVSS11

PLL2_AVSS11

PLL3_AVSS11

USB_DVSS

USB_VSSAC

USB_VSSA0

USB_ID

EHCI_PORT_PWR2

EHCI_PORT_PWR1

EHCI_PORT_PWR0

USB11_D-

HSIC2_STB

HSIC1_DATA

RESETN

TESTMODE

JTAG_TRSTN

JTAG_SEL

JTAG_TMS

JTAG_TCK

JTAG_TRTCK

JTAG_TDO

JTAG_TDI

TST_CLKOUT

TST_STPCLK

WDOG

XI0

XO0

USB_VDD330

USB_DVDD

PLL2_AVDD11

PLL3_AVDD11

PLL1_AVDD11

USB11_D+

HSIC2_DATA

HSIC1_STB

SYMBOL 1 OF 9

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

3

6

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2

1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

3

4

5

6

7

8

D

B

8

7

5

4

2

1

** LAYOUT(MLB): TIE TESTMODE PIN UNDER PKG

ENABLES RESET OF H3P FROM JTAG BOARD

NC

NC

NC

NC

NC

NC

NC

100K

01005

MF

NOSTUFF

5%

1/32W

01005

100K

5%

1/32W

MF

UCSP

MAX9061

01005

MF

0.00

0%

1/32W

5%

MF

NOSTUFF

1/32W

01005

5%

MF

1.00K

01005

X5R

10%

6.3V

0.01UF

01005

X5R

6.3V

10%

0.01UF

6.3V

10%

0.01UF

X5R

01005

01005

X5R

6.3V

10%

0.01UF

0

1/20W

MF

5%

201

6.3V

NP0-C0G

56PF

5%

01005

1/20W

0

MF

201

5%

201

MF

1/20W

0

5%

1%

1/32W

1.00M

01005

MF

MF

5%

01005

1/32W

10K

1/32W

MF

100K

01005

5%

5%

1/32W

MF

01005

54.9K

1%

MF

01005

1/32W

6.3V

10%

X5R

01005

1000PF

MF

1/32W

100K

01005

5%

100K

5%

1/32W

01005

MF

01005

0.01UF

6.3V

10%

X5R

10%

6.3V

402

CERM

1UF

01005

10%

0.01UF

6.3V

X5R

201

1/20W

MF

1%

43.2

01005

10%

0.01UF

X5R

6.3V

5%

100K

MF

1/32W

01005

22

MF

01005

1/32W

5%

X5R

01005

6.3V

10%

0.01UF

01005

5%

16V

CERM

22PF

SM-2

24.000MHZ-16PF-60PPM

5%

16V

01005

CERM

22PF

NOSTUFF

FBGA

H3P

256MB-DDR-FC

110K

1/32W

1%

MF

01005

01005

0%

MF

1/32W

0.00

0.01UF

X5R

01005

10%

6.3V

SYNC_DATE=N/A

SYNC_MASTER=N/A

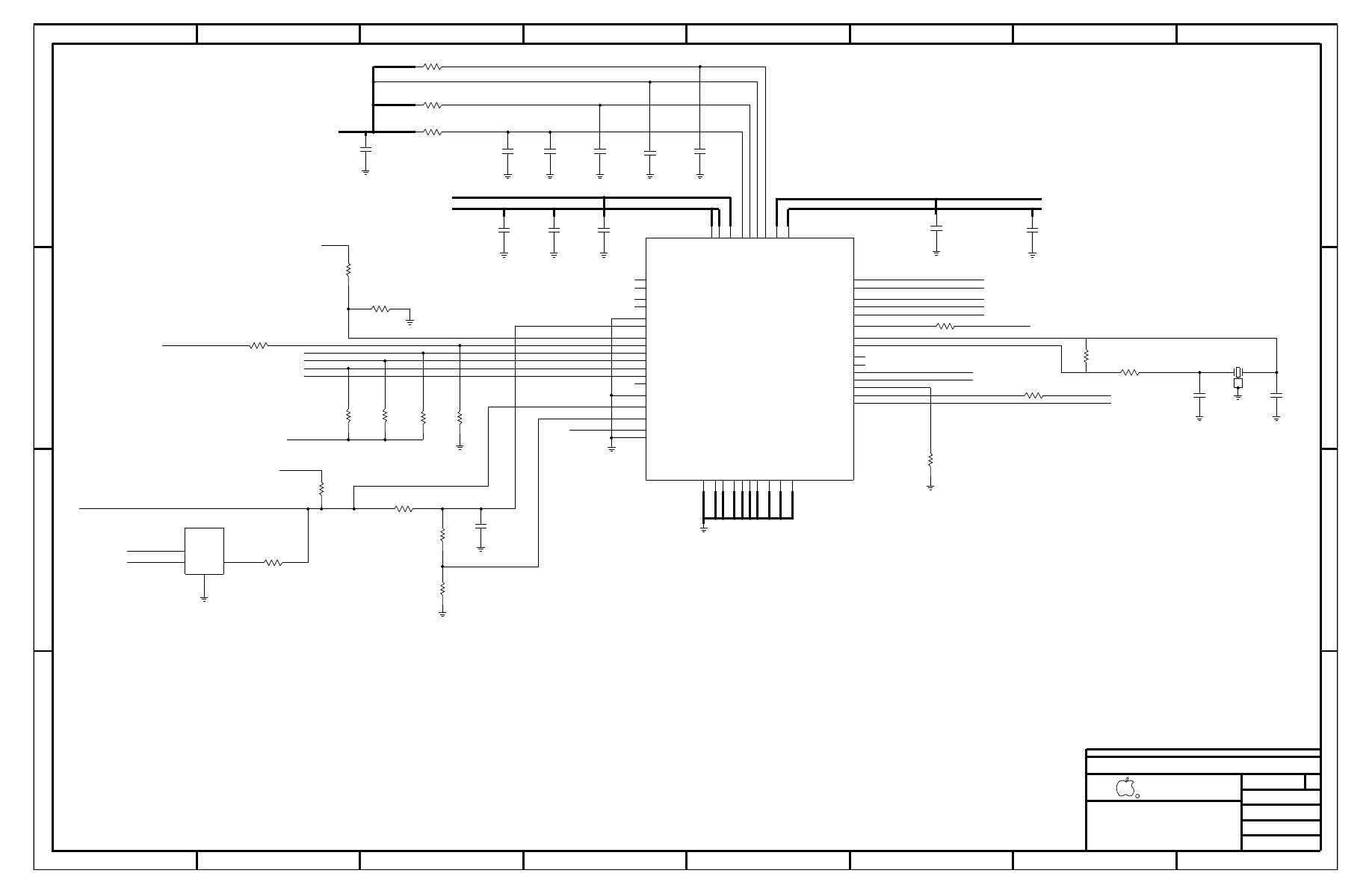

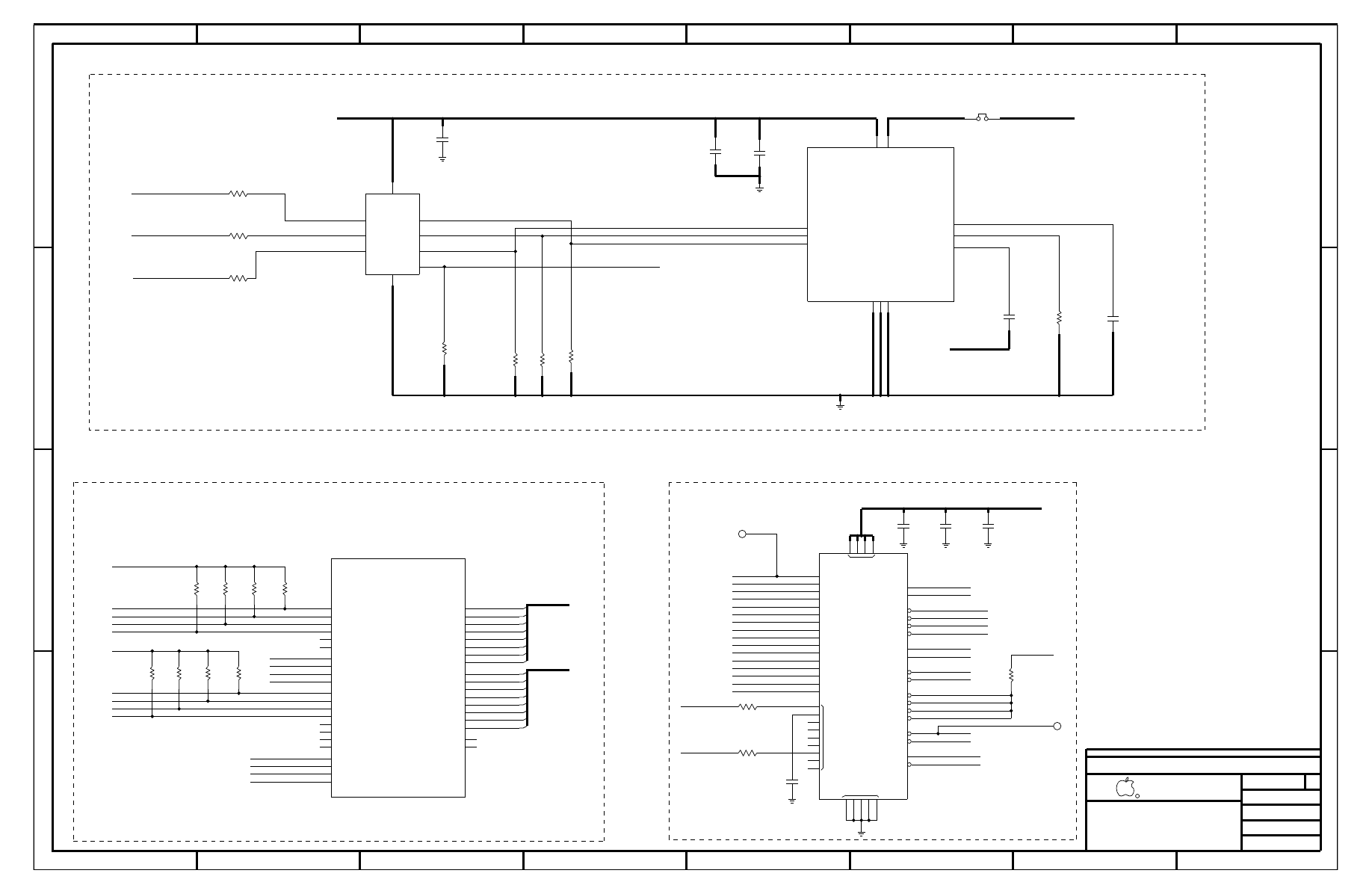

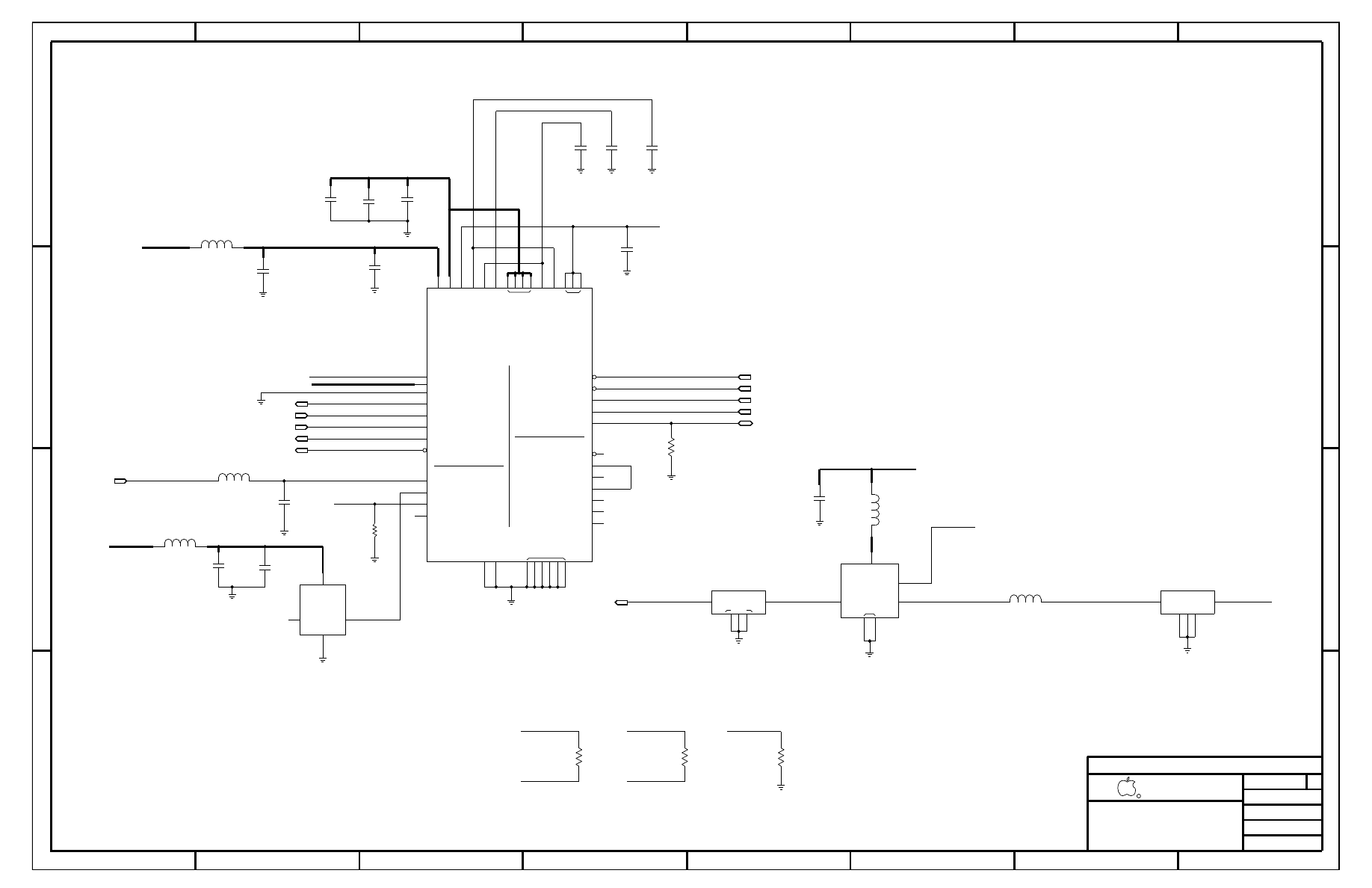

H3 JTAG, USB ,MISC

JTAG_TRSTN_GPIO

JTAG_ST

DOCK_TDI

DOCK_TDO

JTAG_ST

DOCK_TMS

JTAG_ST

RESET_3V0_L

RESET_L

RESET_1V2_L

PP1V8

USBFS_N

USB

EHCI_PORT_PWR0

EHCI_PORT_PWR1

EHCI_PORT_PWR2

CRYSTAL

XTAL_24M_I

CRYSTAL

XTAL_24M_O

USB_REXT

DOCK_TMS

PP3V0_IO

PMU_RESET_IN

PP1V2

PWR250

PP1V1

PLL1_AVDD

PWR50

PP1V1

PP3V0_IO

PP1V1

PLL3_AVDD

PWR50

PWR50

PLL0_AVDD

JTAG_SEL

USB_BRICKID

USB_VBUS

USBFS_P

USB

USBHS

USB_AP_DP

USB

USBHS_N

VBUS_PROT

USBHS

USB

USB_AP_DP

USBHS_P

TST_CLKOUT

PP3V0_IO

PP1V8

WDOG

XTAL_24M_O_R

CRYSTAL

DOCK_TCK

JTAG_ST

JTAG_ST

JTAG_TRSTN_GPIO_R

100K

100K

1/32W

01005

NOSTUFF

NOSTUFF

NOSTUFF

R17

1

2

R96

1

2

R24

1

2

R9

1

2

C264

1

2

R97

1

2

R123

1

2

C27

1

2

C6

1

2

C9

1

2

R42

1

2

C29

1

2

R2

1

2

R40

1

2

C30

1

2

C7

1

2

Y2

2

4

1

3

C13

1

2

U52

V26

N7

Y10

Y9

AA9

F19

P25

R25

M27

M26

L27

L26

N17

N18

N16

N19

C18

B15

A19

C19

D18

B18

D19

E14

E15

D13

E13

F15

F14

N23

N24

B19

F23

K20

J20

R27

R26

N20

R23

P27

P26

R20

R21

R22

N21

N25

P22

R24

N22

F22

B12

A12

R6

1

2

R93

1

2

C122

1

2

R401

1

2

R25

1

2

U2

B2

A2

A1

B1

R1

1

2

R33

1

2

R92

1

2

C19

1

2

C20

1

2

C44

1

2

C8

1

2

R26

1

2

C23

1

2

R100

1

2

R83

1

2

R41

1

2

2 OF 18

A.0.0

051-7921

CR-2 : @SINGLE_BRD_LIB.MLB(SCH_1):PAGE2

2 OF 29

3

14

14

2

14

11

17

18

2

3

4

7

8

10

11

12

13

14

15

16

17

3

3

3

2

14

2

3

4

6

10

11

14

11

4

11

2

7

11

2 7 11

2 3 4 6 10 11 14

2

7

11

11 18

17

14

11

14

18

2

3

4

6

10

11

14

2

3

4

7

8

10

11

12

13

14

15

16

14

14

GPIO6

GPIO2

SMII_SRDY

SMII_RRDY

SMII_SYNC

SMII_TXD

GPIO3

GPIO1

GPIO17

GPIO16

SENSOR_RST

SENSOR_CLK

GPIO_3V1

GPIO38

GPIO_3V0

GPIO36

GPIO37

GPIO35

GPIO34

GPIO33

GPIO31

GPIO32

GPIO30

GPIO28

GPIO29

GPIO26

GPIO27

GPIO25

GPIO24

GPIO23

GPIO21

GPIO22

GPIO20

GPIO19

GPIO18

GPIO15

GPIO14

GPIO13

GPIO11

GPIO12

GPIO10

GPIO8

GPIO9

GPIO7

GPIO5

GPIO4

GPIO0

SMII_CLK

SMII_RXD

SMII_PWR

SMII_WAKE

SMII_CLKSEL1

SMII_CLKSEL0

TMR32_PWM2

TMR32_PWM1

TMR32_PWM0

SPDIF

SYMBOL 6 OF 9

SDIO0_DATA0

SDIO0_DATA1

SDIO0_DATA2

I2S0_BCLK

I2S0_DIN

I2S0_DOUT

I2S0_LRCK

I2S0_MCK

SDIO0_CLK

SDIO0_CMD

SDIO0_DATA3

SPI0_SCLK

SPI0_MOSI

SPI0_MISO

SPI0_SSIN

SPI1_SCLK

SPI1_MOSI

SPI1_SSIN

SPI1_MISO

SPI2_SCLK

SPI2_MOSI

SPI2_MISO

SPI2_SSIN

I2S1_DIN

I2S1_DOUT

I2S1_BCLK

I2S1_LRCK

I2S1_MCK

I2S2_DIN

I2S2_DOUT

I2S2_BCLK

I2S2_LRCK

I2S2_MCK

I2C0_SDA

I2C0_SCL

I2C1_SDA

I2C1_SCL

I2C2_SDA

I2C2_SCL

SYMBOL 5 OF 9

UART6_CTSN

UART6_RTSN

UART6_RXD

UART6_TXD

UART5_RTXD

UART4_CTSN

UART4_RXD

UART4_TXD

UART3_CTSN

UART2_RTSN

UART1_RTSN

UART1_RXD

UART1_TXD

UART0_TXD

UART0_RXD

UART1_CTSN

UART3_RTSN

UART4_RTSN

UART3_RXD

UART3_TXD

UART2_CTSN

UART2_RXD

UART2_TXD

SYMBOL 7 OF 9

PP

PP

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

3

6

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2

1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

3

4

5

6

7

8

D

B

8

7

5

4

2

1

NC - GPIO25_CONFIG1

NC - DFU_STATUS

NC - SEL_SECURE_BOOT_3V0

3K3 ON R419 REDUCES CAMERA NOISE

1001 DVT

<---SELECTED

1010 EVT2 COMPBUTTON

BOARD_REV[3:0]={EHCI_PORT_PWR2,EHCI_PORT_PWR1,EHCI_PORT_PWR0,SMII_PWR}

1111 PROTO0

1110 PROTO1

1011 EVT2

1100 EVT1

1101 PROTO2

** BACKUP IN CASE I2S0_MCK DOES NOT WORK

101 XXX DEV

NC

NC

NC

GPS

DOCK

BB

NC

NC

BT

GAS GAUGE

HIGHLANDPARK

TODO: DO WE NEED A SERIES R HERE (THERE IS ONE ON DEV2)

UMTS

BOARD_ID[0:2]={SPI0_SCLK,SPI0_MOSI,SPI0_MISO}

1100 FMI0/1 2/2 CS

1101 FMI0/1 4/4 CS

1110 FMI0/1 4/4 CS W/TEST

<------SELECTED

1010 FMI1 4CS W/TEST

0010 SPI0 W/TEST

0011 SPI3 W/TEST

1000 FMI1 2 CS

1001 FMI1 4 CS

1111 RESERVED

0100 FMI0 2CS

0101 FMI0 4CS

0111 RESERVED

0000 SPI0

0001 SPI3

0110 FMI0 4CS W/TEST

010 XXX AP

110 XXX DEV

001 XXX AP

100 N90 DEV

000 N90 MLB

<---SELECTED

FLOAT=LOW, PULLUP=HIGH

NOTE: NO COMPONENTS REQIORED!

BOOT_CONFIG[3:0]={GPIO29_CONFIG3,GPIO28_CONFIG2,GPIO25_CONFIG1,CODEC_INT_L}

NC - DIF_MIC_SEL

01005

0.00

0.00

01005

NOSTUFF

01005

0.00

NOSTUFF

01005

0.00

33.2

1/32W

1%

MF

01005

01005

100K

5%

1/32W

MF

10K

01005

0.00

0%

1/32W

MF

01005

NOSTUFF

01005

10K

10K

01005

01005

1/32W

1.00M

1%

MF

01005

1/32W

MF

5%

3.3K

100K

5%

01005

1/32W

MF

NOSTUFF

256MB-DDR-FC

H3P

FBGA

3

2

1

0

01005

MF

5%

1/32W

1.00K

01005

1/32W

1.00K

5%

MF

1/32W

MF

01005

5%

1.00K

NOSTUFF

256MB-DDR-FC

H3P

FBGA

NOSTUFF

FBGA

H3P

256MB-DDR-FC

1.00K

1/32W

MF

01005

5%

1/32W

1.00K

MF

5%

01005

SM

P4MM

P4MM

SM

SYNC_DATE=N/A

SYNC_MASTER=N/A

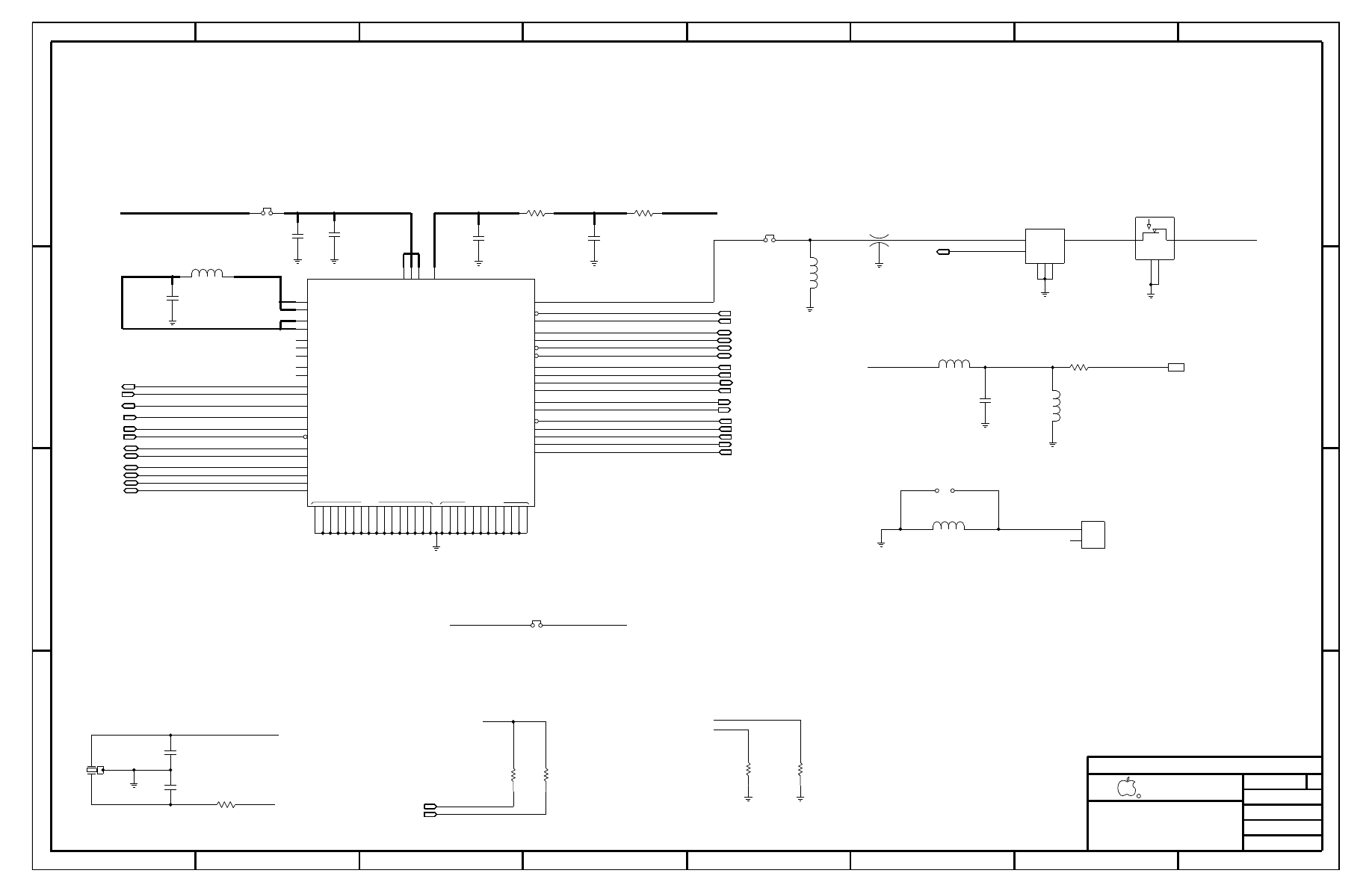

H3 GPIO,UART,SPI,I2S,I2C,SDIO

WLAN_SDIO_DATA<3:0>

MENU_KEY_BUFF_L

WLAN_RESET_L

BT_WAKE

RADIO_ON

UART_ST

UART0_TXD

UART_ST

UART0_RXD

UART1_TXD

UART_ST

UART_ST

UART1_RXD

UART_ST

UART1_RTS_L

UART_ST

UART1_CTS_L

UART2_TXD

UART_ST

UART2_RXD

UART_ST

UART3_TXD

UART_ST

UART4_TXD

UART_ST

UART4_RXD

UART_ST

UART4_RTS_L

UART_ST

UART4_CTS_L

UART_ST

UART6_TXD

UART_ST

UART6_RXD

UART_ST

UART3_RTS_L

UART_ST

SPI1_MOSI

SPI_ST

SPI1_MISO

SPI_ST

SPI1_CS_L

SPI_ST

SPI2_MRDY

SPI_ST

SPI2_MISO

SPI_ST

SPI2_MOSI

SPI_ST

SPI2_SCLK

SPI_ST

SPI1_SCLK

SPI_ST

I2S0_DIN

I2S_ST

I2S0_DOUT

I2S_ST

I2S0_BCLK

I2S_ST

I2S_ST

I2S0_LRCLK

I2S_ST

I2S2_DIN

I2S_ST

I2S2_DOUT

I2S1_LRCLK

I2S_ST

UART3_CTS_L

UART_ST

UART3_RXD

UART_ST

NIMBUS_INT_L

GRAPE_RESET_L

KEEPACT

CODEC_INT_L

JTAG_TRSTN_GPIO

GPS_INTR_L

CAM_VGA_SHUTDOWN_L

SMII_PWR

AG27_GND

IPC_GPIO

HP_GPIO_A

AG1_GND

CODEC_RESET_L

SPKR_AMP_EN

A27_GND

A1_GND

GPS_SYNC

CAM_STROBE_EN

PP1V8

CODEC_INT_L

GPIO29_CONFIG3

GPIO28_CONFIG2

EHCI_PORT_PWR0

PP1V8

AP_PMU_EXTON

L61HP_CLK_PWM

WLAN_SDIO_CMD

WLAN_SDIO_CLK

RINGER_A

VOL_DWN_L

VIB_PWM_EN

L61HP_CLK_PWM

ACCEL_INT2_L

BATTERY_SWI

CAM_5MP_SHUTDOWN

CAM_CLK

PP3V0_IO

I2S0_MCK_R

GPIO28_CONFIG2

EHCI_PORT_PWR1

AUDIENCE_RESET_L

IPC_SRDY

BB_RESET_L

GYRO_INT2

GYRO_INT1

SMII_PWR

PMU_IRQ_L

BT_RESET_L

I2S_ST

I2S1_BCLK

I2S_ST

I2S1_DOUT

I2S_ST

I2S0_MCK

I2S_ST

I2S1_DIN

I2S_ST

I2S1_MCK

I2S_ST

I2S2_BCLK

I2S2_MCLK

I2S_ST

I2S2_LRCLK

I2C_ST

I2C2_SCL_1V8

I2C_ST

I2C2_SDA_1V8

I2C_ST

I2C1_SCL_1V8

I2C_ST

I2C1_SDA_1V8

I2C0_SDA_1V8

I2C_ST

BB_RESET_DET_L

EHCI_PORT_PWR2

I2C_ST

I2C0_SCL_1V8

PP1V8

ALS_INT_L

ACCEL_INT1_L

VOL_UP_L

HOLD_KEY_L

RADIO_ON

VIDEO_AMP_EN_3V0

GPS_STANDBY_AP_L

GPS_RESET_AP_L

GPIO29_CONFIG3

FORCE_DFU

COMPASS_BRD_INT

LCD_HIFA

LCD_RESET_L

LCD_RESET_L

U52

F6

B6

C5

C9

C6

D6

F5

E5

F9

F3

F4

C10

B7

F10

E10

A4

B4

E4

E2

D10

E9

L2

G1

D9

G2

E3

B3

A3

B2

H2

L1

H1

E1

D5

A6

A7

B9

E6

A9

W24

W25

W20

V21

K23

K18

K19

H19

K21

J18

K22

G19

G18

J19

R18

AB25

AB27

AB26

R87

R88

R424

1

2

U52

AB5

AB6

AB3

AB4

AC15

AD15

V23

W21

W22

V18

V20

V25

V24

W19

V15

AB22

Y26

R17

R16

AB23

W23

J21

K25

J24

J25

J26

J27

V6

W7

V4

W3

U2

W8

V3

V2

V7

AA1

AA2

W6

U52

V27

Y27

Y1

V1

Y2

U1

V9

V10

W5

V5

AD5

R1

P3

R3

AD1

W4

AD6

AD2

V8

AC4

AC3

AC6

AC5

R75

1

2

R77

1

2

PP2

1

PP1

1

R27

1

2

R8

1

2

R29

1

2

R15

1

2

R36

1

2

R369

1

2

R362

1

2

R89

1

2

R103

1

2

R104

1

2

R68

1

2

R419

1

2

R28

1

2

3 OF 18

A.0.0

051-7921

CR-3 : @SINGLE_BRD_LIB.MLB(SCH_1):PAGE3

3 OF 29

17

11

13

17

17

3

17

17

18

17

18

17

17

17

17

17

17

17

17

17

17

17

13

13

17

15

15

15

17

17

17

17

15

18

8

8

8

8

13 17

13 17

13 17

17

17

15

18

15

11

3

8

2

17

16

3

4

17

13

4

8

14

4

4

17

12 16

2 3 4 7 8 10 11 12 13 14 15 16

3

8

3

3

2

2 3 4 7 8 10 11 12 13 14 15 16

11 17

3

13

17

17

10

11

13

18

10

13

18

11

3 13

12

11

17

16

16

2

4

6

10

11

14

8

3

2

13

17

17

12

12

3

11

17

13 17

13 17

13 17

8

13 17

13

13 17

12

12

16

16

8 9 10 11 13 16

17

2

8 9 10 11 13 16

2 3 4 7 8 10 11 12 13 14 15 16

16

12

10

13

18

11

13

16

18

3

17

6

17

17

3

18

10

15

3

15

3

15

DDR0VDDQ

DDR1VDDQ

VDDIO30

VDDIOD5

VDDIOD4

VDDIOD3

VDDIOD2

VDDIOD1

VDDIOD0

VDDIO18

VDDIOD

VSS

VDD

SYMBOL 8 OF 9

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

3

6

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2

1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

3

4

5

6

7

8

D

B

8

7

5

4

2

1

LAYOUT: PLACE THE 56PF IN PAIRS AROUND THE IC

NAND POWER GROUP

X5R

603

6.3V

20%

10UF

6.3V

10%

402

CERM

1UF

10%

1UF

CERM

402

6.3V

1UF

CERM

6.3V

402

10%

201

X5R

20%

0.22UF

6.3V

0.22UF

20%

6.3V

X5R

201

6.3V

NOSTUFF

01005

NP0-C0G

5%

56PF

0.22UF

20%

201

6.3V

X5R

X5R

201

20%

6.3V

0.22UF

6.3V

X5R

0.22UF

201

20%

0.22UF

6.3V

201

20%

X5R

6.3V

NP0-C0G

NOSTUFF

01005

5%

56PF

6.3V

20%

X5R

201

0.22UF

201

20%

X5R

6.3V

0.22UF

0.22UF

201

6.3V

20%

X5R

201

0.22UF

20%

6.3V

X5R

X5R

20%

201

6.3V

0.22UF

NP0-C0G

5%

01005

6.3V

NOSTUFF

56PF

0.22UF

201

X5R

6.3V

20%

6.3V

20%

0.22UF

X5R

201

6.3V

20%

0.22UF

X5R

201

0.22UF

20%

X5R

6.3V

201

0.22UF

6.3V

20%

201

X5R

56PF

5%

01005

NP0-C0G

NOSTUFF

6.3V

NP0-C0G

01005

NOSTUFF

56PF

5%

6.3V

01005

NP0-C0G

6.3V

NOSTUFF

5%

56PF

6.3V

NP0-C0G

01005

NOSTUFF

5%

56PF

402

10%

CERM

6.3V

1UF

201

X5R

6.3V

20%

0.22UF

NP0-C0G

5%

NOSTUFF

56PF

6.3V

01005

NOSTUFF

H3P

FBGA

256MB-DDR-FC

201

6.3V

20%

X5R

0.22UF

6.3V

402

10%

CERM

1UF

6.3V

20%

0.22UF

X5R

201

0.22UF

6.3V

20%

X5R

201

X5R

6.3V

0.22UF

201

20%

0.22UF

6.3V

X5R

201

20%

0.22UF

20%

6.3V

X5R

201

6.3V

20%

201

X5R

0.22UF

0.22UF

20%

6.3V

201

X5R

201

X5R

6.3V

20%

0.22UF

X5R

201

20%

0.22UF

6.3V

0.22UF

201

X5R

20%

6.3V

201

X5R

20%

6.3V

0.22UF

6.3V

X5R

603

20%

10UF

0.22UF

X5R

6.3V

201

20%

201

X5R

6.3V

0.22UF

20%

0.22UF

201

X5R

6.3V

20%

10%

6.3V

402

CERM

1UF

4V

20%

4.3UF

X5R-CERM

0610

0610

X5R-CERM

4V

20%

4.3UF

6.3V

0.22UF

201

20%

X5R

6.3V

X5R

603

10UF

20%

SYNC_MASTER=N/A

SYNC_DATE=N/A

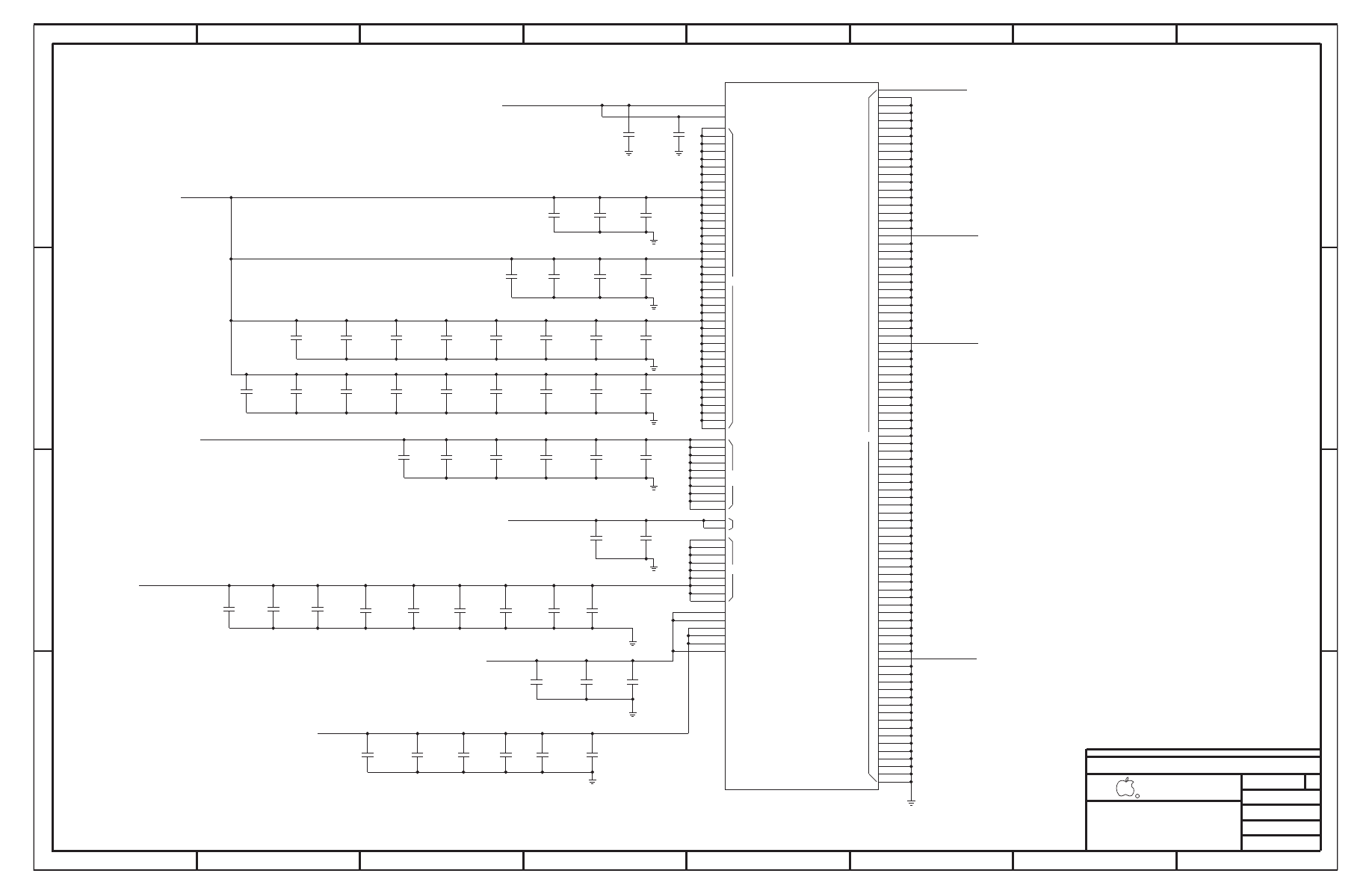

AP PWR

A27_GND

PP1V2_SDRAM

AG1_GND

AG27_GND

A1_GND

PP3V0_IO

PP1V8

PP3V0_IO

PPCPU_CORE

PP1V2

PP1V8

C169

1

2

C167

1

2

C166

1

2

C152

1

2

C60

1

2

C48

1

2

C151

1

2

C153

1

2

C160

1

2

C10

1

2

C114

1

2

C161

1

2

C163

1

2

C105

1

2

C79

1

2

C135

1

2

C132

1

2

C52

1

2

C229

1

2

C121

1

2

C15

1

2

C104

1

2

C112

1

2

C103

1

2

C232

1

2

C118

1

2

C138

1

2

C136

1

2

C154

1

2

C96

1

2

C126

1

2

U52

F13

N6

J10

J12

J13

J14

J15

J16

J17

J9

K10

K12

K9

L10

L12

L13

L14

L15

L16

L17

L9

M10

M12

M9

N10

N12

N13

N14

N15

P10

P12

R10

R12

R14

T10

U12

T12

T13

T14

T15

T16

T17

A10

A16

F1

N1

V22

W10

AB10

AC10

AD10

AE10

T21

U27

AB15

W18

AD22

V19

F18

H18

G13

H10

H9

J6

J7

J8

K8

N8

R8

A1

A18

AF10

AB13

AE9

AF1

AF11

AF23

AF16

AF17

AF2

AG1

C15

AG12

AB14

AF24

AF27

AF4

AF7

AG2

B10

B11

B16

A2

B17

AG23

AG26

AG27

B1

B20

B21

B5

B24

B26

A23

B27

C2

B8

C11

C17

D26

D11

D17

D2

E11

AD26

F26

E17

F11

F17

F2

G10

G11

G15

H17

H26

AE22

G17

G9

H11

H13

H15

J1

J11

J2

J3

J4

AD9

K13

J5

K11

A26

A27

AA17

AA10

AA11

AA15

AA26

AE17

AB2

AB11

AB17

AC11

AB9

AC13

AC17

AC2

AC9

AD11

AE2

AD17

C57

1

2

C168

1

2

C95

1

2

C81

1

2

C80

1

2

C56

1

2

C51

1

2

C55

1

2

C162

1

2

C170

1

2

C109

1

2

C99

1

2

C88

1

2

C130

1

2

C54

1

2

C102

1

2

C111

1

2

C165

1

2

C53

1

2

C77

1

2

C141

1

2

4 OF 18

A.0.0

051-7921

CR-4 : @SINGLE_BRD_LIB.MLB(SCH_1):PAGE4

4 OF 29

3

5

11

3

3

3

2

3

4

6

10

11

14

2

3

4

7

8

10

11

12

13

14

15

16

2

3

4

6

10

11

14

11

2

11

2

3

4

7

8

10

11

12

13

14

15

16

PP1V35

VSS

VDD_MEM

VDDQ

SYMBOL 9 OF 9

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

3

6

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2

1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

3

4

5

6

7

8

D

B

8

7

5

4

2

1

PLACE THE 56PF IN PAIRS AROUND THE IC

NP0-C0G

01005

6.3V

NOSTUFF

5%

56PF

CERM

10%

402

6.3V

1UF

NOSTUFF

01005

6.3V

5%

NP0-C0G

56PF

01005

NP0-C0G

6.3V

5%

56PF

NOSTUFF

402

CERM

1UF

10%

6.3V

10%

1UF

6.3V

CERM

402

20%

0.22UF

6.3V

X5R

201

6.3V

X5R

0.22UF

201

20%

201

20%

0.22UF

6.3V

X5R

0.22UF

20%

6.3V

X5R

201

0.22UF

20%

6.3V

X5R

201

10%

1UF

6.3V

CERM

402

0.22UF

X5R

201

20%

6.3V

X5R

20%

201

6.3V

0.22UF

X5R

201

20%

6.3V

0.22UF

201

6.3V

20%

X5R

0.22UF

NOSTUFF

FBGA

256MB-DDR-FC

H3P

201

X5R

20%

6.3V

0.22UF

CERM

1UF

10%

6.3V

402

X5R

6.3V

603

20%

10UF

10%

01005

6.3V

X5R

0.01UF

0.01UF

10%

X5R

6.3V

01005

10UF

20%

6.3V

X5R

603

20%

10UF

6.3V

603

X5R

10%

X5R

01005

6.3V

0.01UF

X5R

01005

10%

0.01UF

6.3V

6.3V

5%

56PF

01005

NP0-C0G

NOSTUFF

402

1UF

6.3V

10%

CERM

SYNC_MASTER=N/A

SYNC_DATE=N/A

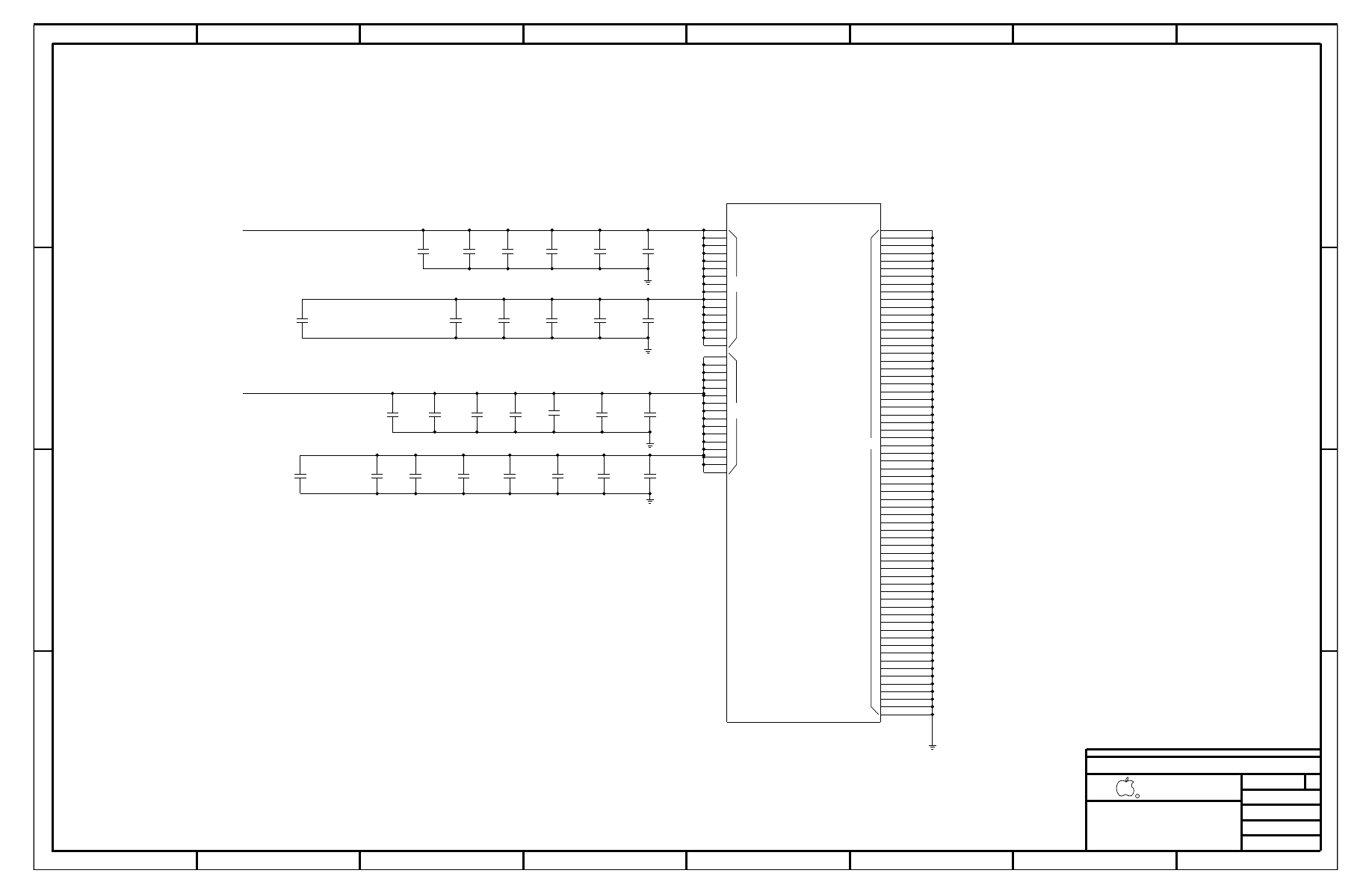

AP PWR(CONT.)

PP1V2_SDRAM

PP1V8_SDRAM

C238

1

2

C129

1

2

C128

1

2

C231

1

2

C65

1

2

C46

1

2

C18

1

2

C16

1

2

C115

1

2

C116

1

2

C107

1

2

C14

1

2

C11

1

2

C12

1

2

C4

1

2

C3

1

2

C2

1

2

C43

1

2

C41

1

2

U52

A11

A21

P1

T27

W27

AG10

F27

AB1

AE1

AG11

AG16

AG24

D1

D27

H27

M1

A17

A24

W1

N27

T1

A20

A8

AA27

A5

AC1

AD27

AG4

AG7

C1

K1

K27

K6

K7

L11

M11

M13

M14

M15

M16

M17

M2

N11

N2

N26

N3

N4

N5

N9

P11

P13

P14

P15

P16

P17

P2

P23

P24

P4

P5

P6

P9

R11

R13

R15

R2

R4

R5

R6

R7

R9

T11

T2

T26

U11

U13

U14

U15

U16

U17

U19

U22

U26

W17

W2

W26

W9

K14

K15

K16

K17

K2

K26

K3

K4

K5

C1

1

2

C218

1

2

C222

1

2

C240

1

2

C221

1

2

C219

1

2

C242

1

2

C239

1

2

5 OF 18

A.0.0

051-7921

CR-5 : @SINGLE_BRD_LIB.MLB(SCH_1):PAGE5

5 OF 29

4

11

9

11

13

17

VSS

NC

R_B1_1*

R_B1_2*

R_B2_1*

R_B2_2*

IO0_2

IO1_1

IO2_1

IO2_2

IO3_1

IO3_2

IO4_1

IO4_2

IO5_1

IO5_2

IO6_1

IO6_2

IO7_1

IO7_2

ALE1

ALE2

CE1_1*

CE1_2*

CE2_1*

CE2_2*

CLE1

CLE2

RE1*

RE2*

WE1*

WE2*

WP1

WP2*

IO0_1

VCC

IO1_2

PP

PP

FMI0_CEN3

FMI0_CEN2

FMI0_IO7

FMI0_IO2

FMI0_IO0

FMI0_IO1

FMI0_IO4

FMI0_IO5

FMI0_IO6

FMI0_CEN1

FMI0_CEN0

FMI0_IO3

FMI0_CEN5

FMI0_CEN4

FMI0_CLE

FMI0_ALE

FMI0_WEN

FMI0_REN

FMI1_CEN0

FMI1_CEN1

FMI1_CEN2

FMI1_CEN3

FMI1_CEN4

FMI1_CEN5

FMI1_CEN6

FMI1_CEN7

FMI1_CLE

FMI1_REN

FMI1_ALE

FMI1_WEN

FMI1_IO0

FMI1_IO1

FMI1_IO2

FMI1_IO3

FMI1_IO4

FMI1_IO5

FMI1_IO6

FMI1_IO7

ENET_MDC

ENET_MDIO

SYMBOL 4 OF 9

CH.2OUT

EN

CH.3IN

CH.2IN

VS+

CH.1IN

CH.1OUT

CH.3OUT

GND

DAC_AVDD30D

DAC_VREF

DAC_OUT2

DAC_IREF

DAC_COMP

DAC_AVSS30D

DAC_AVSS30A2

DAC_AVSS30A1

DAC_OUT1

DAC_OUT3

DAC_AVDD30A

SYMBOL 3 OF 9

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

3

6

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2

1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

3

4

5

6

7

8

D

B

8

7

5

4

2

1

NAND, BANK ZERO

*TPS FOR NAND TESTING

YIN

CIN

CVBSIN

X5R

01005

6.3V

0.01UF

10%

6.3V

X5R

201

10%

0.1UF

201

200

1%

MF

1/20W

200

1%

1/20W

MF

201

NOSTUFF

16GX8-3.3V

TLGA

K9PDG08U5D-LCBO

200

1/20W

201

MF

1%

20%

X5R

1.0UF

6.3V

0201

P4MM

SM

SM

P4MM

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

201

X5R

10%

0.1UF

6.3V

256MB-DDR-FC

H3P

FBGA

5%

MF

1/32W

01005

100K

01005

1/32W

100K

MF

5%

MF

01005

1/32W

100K

5%

MF

01005

5%

1/32W

100K

100K

5%

1/32W

01005

MF

1/32W

5%

01005

MF

100K

100K

1/32W

01005

MF

5%

100K

5%

1/32W

MF

01005

1/32W

100K

5%

MF

01005

0.00

1/32W 0%

01005 MF

NOSTUFF

NOSTUFF

01005

0%

1/32W

0.00

MF

X5R

NOSTUFF

0201

6.3V

20%

1.0UF

6.3V

X5R-CERM-1

603

22UF

20%

6.34K

1%

MF

201

1/20W

5%

MF

01005

100K

1/32W

6.3V

X5R

10%

201

0.1UF

1%

1/32W

MF

01005

75

402

1UF

10%

6.3V

CERM

MF

01005

75

1/32W

1%

01005

MF

1%

75

1/32W

NOSTUFF

SM

THS7319

BGA

NOSTUFF

FBGA

256MB-DDR-FC

H3P

6.3V

X5R

201

10%

0.1UF

SYNC_DATE=N/A

SYNC_MASTER=N/A

ANALOG VIDEO,H3 NAND, NAND

F0AD<7..0>

F1AD<7..0>

RDYBSY_L

F0CE1_L

NAND_ST

NAND_ST

F0CE0_L

NAND_ST

F1CE1_L

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

NAND_ST

F1WE_L

F1ALE

NAND_ST

NAND_ST

F1RE_L

NAND_ST

F1CLE

F0WE_L

NAND_ST

F0CLE

NAND_ST

PP3V0_NAND

F0WE_L

F1CE3_L

F0CE3_L

F1AD<1>

F0CE2_L

F1CE2_L

F1WE_L

F1RE_L

F0RE_L

F1CLE

F0CLE

F1CE1_L

F0CE1_L

F1CE0_L

F0CE0_L

F1ALE

F0ALE

F1AD<6>

F0AD<6>

F1AD<5>

F0AD<5>

F1AD<4>

F0AD<4>

F1AD<3>

F0AD<3>

F1AD<2>

F0AD<2>

F0AD<1>

VDDI

F0AD<0>

PP3V0_NAND

DAC_OUT3

VIDEO

DAC_OUT1

VIDEO

VIDEO_AMP_EN_3V0

DAC_OUT2

VIDEO

VIDEO

DAC_VREF

DAC_IREF

VIDEO

PWR100

PP3V0_IO

DAC_COMP

VIDEO

PWR100

PP3V0_IO_XW

PP3V0_VIDEO

PP3V0_VIDEO

VIDEO

YOUT

75_OHM

75_OHM

VIDEO

COUT

75_OHM

VIDEO

VID_Y

VIDEO

VID_COMP

75_OHM

75_OHM

VIDEO

VID_C

F0AD<7>

F1AD<7>

NAND_ST

F0ALE

NAND_ST

F0RE_L

NAND_ST

F1CE3_L

NAND_ST

F1CE0_L

PP3V0_NAND

NAND_ST

F0CE3_L

F0CE2_L

NAND_ST

F1CE2_L

NAND_ST

F1AD<0>

PWR250

PP3V0_NAND

VIDEO

CVBS_OUT

75_OHM

PWR1500

PWR1500

C71

1

2

C143

1

2

R5

1

2

R46

1

2

R47

1

2

C26

1

2

R129

1

2

R44

1

2

C150

1

2

R43

1

2

C28

1

2

R4

1

2

R3

1

2

XW2

1

2

U9

A1

A3

B1

B3

C1

C3

B2

A2

C2

U52

C13

D14

B14

C14

D15

E18

A13

A15

A14

B13

E19

C61

1

2

U1

C1

D2

A5

C5

A1

OA0

A3

C3

G3

G1

H2

J1

J3

L1

K2

N3

L5

N5

K6

L7

J5

J7

H6

G7

OB0

OB8

OC0

OC8

OD0

OD8

OE0

OF0

OF8

E5

E7

A7

OA8

C7

D6

N7

N1

M6

B6

M2

L3

F6

B2

OE8

E3

E1

F2

G5

C139

1

2

PP6

1

PP7

1

U52

K24

J22

AG19

AC18

AG17

AD18

AB19

J23

F25

AF18

AC19

AF15

AE18

AG15

AD19

AE19

AB18

AE15

AF19

AF22

AE23

AE27

AF20

AG20

AG18

AG25

AF25

AB24

AD23

AE26

AF26

AC22

AC23

AC27

AC25

AC26

AC24

AG22

AF21

AG21

R275

1

2

R268

1

2

R12

1

2

R7

1

2

R266

1

2

R265

1

2

R19

1

2

R20

1

2

R18

1

2

R102

1

2

R101

1

2

C50

1

2

C17

1

2

6 OF 18

A.0.0

051-7921

CR-6 : @SINGLE_BRD_LIB.MLB(SCH_1):PAGE6

6 OF 29

6

6

6

6

6

6

6

6

6

6

6

6

11

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6 11

3

2 3 4 10 11 14

6

11

6

11

14

14

14

6

6

6

6

6

6

6

11

6

6

6

6

6 11

DP_PAD_TX0-

DP_PAD_TX1-

SMIA_RX_DATA+

SMIA_RX_DATA-

SMIA_RX_CLK+

MIPID_VDD11_PLL

DP_PAD_AVDD0

DP_PAD_AVDD1

DP_PAD_AVDDP0

DP_PAD_AVDDX

DP_PAD_DVDD

SMIA_VDD18

SMIA_VDD11

DP_PAD_DC_TP

SMIA_VSS18

DP_PAD_DVSS

DP_PAD_AVSSX

DP_PAD_AVSSP0

DP_PAD_AVSS1

MIPID_DPDATA2

MIPID_DNDATA2

MIPID_DNDATA0

MIPID_DPDATA1

MIPID_DNDATA1

MIPID_DNDATA3

MIPID_DPCLK

MIPID_DNCLK

MIPIC_DPDATA0

MIPI_VDD11

MIPID_VDD18

DP_HPD

SWI_DATA

MIPID_VREG_0P4V

DP_PAD_AVDD_AUX

DP_PAD_AUXN

DP_PAD_AUXP

MIPIC_DNCLK

MIPIC_DPCLK

MIPI_VSS

DP_PAD_AVSS_AUX

MIPID_DPDATA3

MIPIC_DNDATA0

MIPIC_DPDATA1

MIPIC_DNDATA1

DP_PAD_AVSS0

MIPID_DPDATA0

MIPI_VSYNC

SMIA_RX_CLK-

DP_PAD_TX1+

DP_PAD_TX0+

DP_PAD_R_BIAS

SYMBOL 2 OF 9

SYM_VER-1

SYM_VER-1

SYM_VER-1

SYM_VER-1

SYM_VER-1

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

3

6

BRANCH

REVISION

DRAWING NUMBER

SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2

1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

3

4

5

6

7

8

D

B

8

7

5

4

2

1

NC

NC

100 OHM DIFF

10%

01005

X5R

6.3V

0.01UF

56PF

5%

01005

NP0-C0G

6.3V

0201-1

80-OHM-0.2A-0.4-OHM

X5R

10%

6.3V

201

0.1UF

NP0-C0G

01005

6.3V

5%

56PF

10%

2.2NF

X5R

10V

201

6.3V

X5R

NOSTUFF

10%

01005

0.01UF

10%

6.3V

201

X5R

0.1UF

0.1UF

10%

6.3V

X5R

201

10%

0.01UF

01005

X5R

6.3V

0.22UF

X5R

6.3V

20%

201

6.3V

0.22UF

201

X5R

20%

20%

201

X5R

6.3V

0.22UF

6.3V

56PF

5%

01005

NP0-C0G

MF

1/32W

0.00

0%

01005

56PF

6.3V

5%

01005

NP0-C0G

256MB-DDR-FC

H3P

FBGA

NOSTUFF

1UF

10%

402

CERM

6.3V

0.1UF

10%

201

6.3V

X5R

MF

1%

01005

1/32W

4.99K

90-OHM-50MA

TCM0605

90-OHM-50MA

TCM0605

TCM0605

90-OHM-50MA

TCM0605

90-OHM-50MA

TCM0605

90-OHM-50MA

5%

201

MF

1/20W

0

NOSTUFF

5%

0

1/20W

MF

201

NOSTUFF

SYNC_DATE=N/A

SYNC_MASTER=N/A

H3 MIPI,DPORT,SMIA

LCM_MIPI_DATA1_P

LCM_MIPI_DATA1_N

LCM_MIPI_DATA0_P

LCM_MIPI_DATA0_N

LCM_MIPI_DATA0_C_P

MIPI

LCM_MIPI_DATA0_C

LCM_MIPI_DATA0_C

DP_DATA0_P

DP_DATA0

DPORT_D0_ST

DPORT

DP_DATA1

DPORT

DP_DATA1_P

DPORT_D1_ST

SMIA

SMIA_CLK

SMIA_CLK_ST

SMIA_CLK_N

LCM_MIPI_DATA0_P

LCM_MIPI_DATA0

MIPI

LCM_MIPI_DATA0

CAM_MIPI_DATA1_P

CAM_MIPI_DATA1

CAM_MIPI_DATA1

MIPI

CAM_MIPI_DATA0_N

CAM_MIPI_DATA0

CAM_MIPI_DATA0

MIPI

LCM_MIPI_DATA3

LCM_MIPI_DATA3

LCM_MIPI_DATA3_P

MIPI

CAM_MIPI_CLK

CAM_MIPI_CLK

MIPI

CAM_MIPI_CLK_P

CAM_MIPI_CLK

CAM_MIPI_CLK

MIPI

CAM_MIPI_CLK_N

DP_AUX

DPORT

DP_AUX

DP_AUX_P

DP_AUX_N

DPORT

DP_AUX

DP_AUX

SWI_BLCTRL

DP_HPD

CAM_MIPI_DATA0_P

CAM_MIPI_DATA0

CAM_MIPI_DATA0

MIPI

LCM_MIPI_CLK_N

LCM_MIPI_CLK

LCM_MIPI_CLK

MIPI

LCM_MIPI_CLK

LCM_MIPI_CLK_P

LCM_MIPI_CLK

MIPI

LCM_MIPI_DATA1

LCM_MIPI_DATA1

LCM_MIPI_DATA1_N

MIPI

LCM_MIPI_DATA1

LCM_MIPI_DATA1

MIPI

LCM_MIPI_DATA1_P

LCM_MIPI_DATA0

LCM_MIPI_DATA0

LCM_MIPI_DATA0_N

MIPI

LCM_MIPI_DATA2

LCM_MIPI_DATA2

LCM_MIPI_DATA2_N

MIPI

LCM_MIPI_DATA2

LCM_MIPI_DATA2

LCM_MIPI_DATA2_P

MIPI

SMIA_CLK

SMIA

SMIA_CLK_ST

SMIA_CLK_P

SMIA

SMIA_D

SMIA_D_ST

SMIA_DATA_N

SMIA

SMIA_D

SMIA_D_ST

SMIA_DATA_P

DP_DATA1_N

DP_DATA1

DPORT

DPORT_D1_ST

DP_DATA0

DP_DATA0_N

DPORT

DPORT_D0_ST

PP1V1

PWR250

PWR250

PP1V8_DP_AVDD

PP1V1

PWR250

PP1V1_MIPI_PLL

PP1V8

PP1V8

DP_R_BIAS

MIPID_VREG

PWR250

LCM_MIPI_CLK_C_N

LCM_MIPI_CLK_C

MIPI

LCM_MIPI_CLK_C

LCM_MIPI_CLK_P

LCM_MIPI_CLK_C

LCM_MIPI_CLK_C

MIPI

LCM_MIPI_CLK_C_P

LCM_MIPI_CLK_N

CAM_MIPI_DATA1_N

CAM_MIPI_DATA1

CAM_MIPI_DATA1

MIPI

LCM_MIPI_DATA3

LCM_MIPI_DATA3_N

LCM_MIPI_DATA3

MIPI

LCM_MIPI_DATA3_P

LCM_MIPI_DATA3_N

LCM_MIPI_DATA3_C

MIPI

LCM_MIPI_DATA3_C

LCM_MIPI_DATA3_C_N

LCM_MIPI_DATA2_N

LCM_MIPI_DATA2_P

LCM_MIPI_DATA2_C

MIPI

LCM_MIPI_DATA2_C

LCM_MIPI_DATA2_C_N

LCM_MIPI_DATA0_C_N

LCM_MIPI_DATA0_C

LCM_MIPI_DATA0_C

MIPI

LCM_MIPI_DATA1_C

MIPI

LCM_MIPI_DATA1_C

LCM_MIPI_DATA1_C_P

LCM_MIPI_DATA1_C

MIPI

LCM_MIPI_DATA1_C

LCM_MIPI_DATA1_C_N

LCM_MIPI_DATA2_C

MIPI

LCM_MIPI_DATA2_C

LCM_MIPI_DATA2_C_P

LCM_MIPI_DATA3_C

LCM_MIPI_DATA3_C

MIPI

LCM_MIPI_DATA3_C_P

C248

1

2

C244

1

2

FL1

1

2

C117

1

2

C108

1

2

C249

C179

1

2

C25

C24

C21

1

2

C173

1

2

C176

1

2

C177

1

2

C178

1

2

R69

1

2

C180

1

2

U52

R19

E26

E27

E22

F24

C23

E23

C22

D22

E24

B23

D23

B22

A22

G27

G26

E25

C26

C27

B25

A25

Y18

Y15

W15

AA13

AG13

AE14

AF9

AF12

AE13

AG9

AF13

AG5

AF3

AE5

AF6

AG8

AF5

AG3

AE6

AG6

AF8

Y13

V13

W13

AG14

AF14

AD13

AD14

AA18

AC14

Y19

AA19

C172

1

2

C22

R71

1

2

L13

1

2

3

4

L14

1

2

3

4