1

Aby zrozumieć sposób zarządzania pamięcią, należy zrozumieć sposób pracy procesorów o architekturze zgodnej z procesorem 80386 (©Intel’a)

pracujących w trybie chronionym (ang. Protected Mode).

Dodatkowe mechanizmy i ograniczenia obsługi określonej ilości pamięci fizycznej RAM wynikające z typu danej platformy sprzętowej (wersji

procesora i płyty głównej) oraz wersji systemu Windows będą stopniowo wyjaśniane. Uwaga

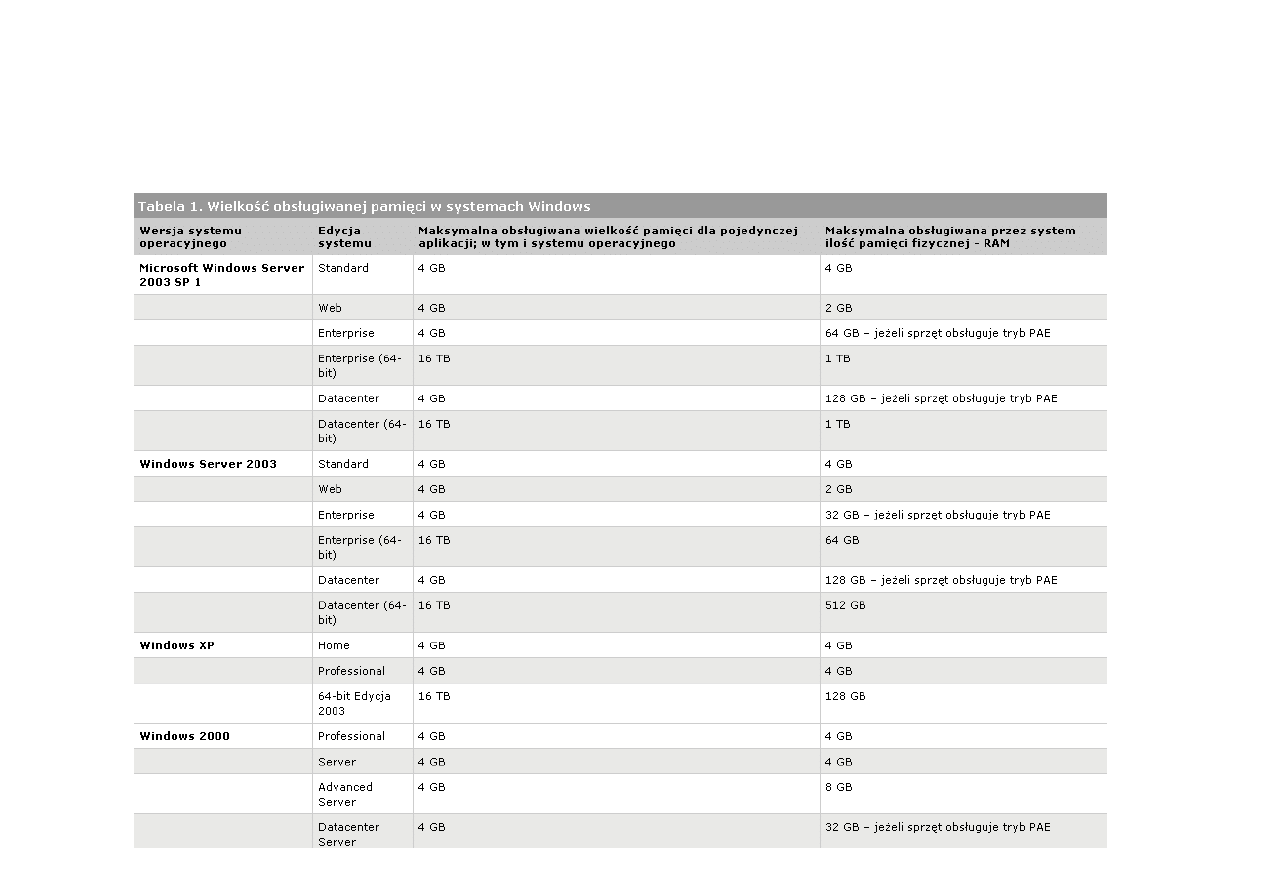

Dla uproszczenia środowisko Windows definiuje dwa pojęcia pamięci, często przez użytkowników mylone. Mówimy o pamięci fizycznej (pamięci RAM

zainstalowanej w komputerze/serwerze) oraz o pamięci widzianej przez daną aplikację (proces) – między innymi przez 32 czy 64-bitowy system operacyjny. W

tabeli poniższej przedstawiamy zestawienie wielkości obsługiwanej pamięci fizycznej i dostępnej dla danej aplikacji w zależności od systemu operacyjnego,

jego wersji oraz obsługi specjalnych trybów adresowania pamięci (jak PSE czy PAE).

2

Do wykonania podstawowych operacji arytmetycznych i logicznych wykorzystuje się rejestry oznaczone jako E(AX), E(BX), E(CX), E(DX) oraz rejestr

(E)FLAGS (są to 32-bitowe rejestry, mogące pracować również, jako 16-bitowe – oznaczane są wtedy, jako AX, BX, CX, DX, FLAGS lub 8–bitowe: AH, AL,

BH, BL, CH, CL, DH, DL). W skrócie. I386 posiada następujące, najważniejsze rejestry:

♦

♦

♦

♦

osiem 32-bitowych rejestrów ogólnego przeznaczenia (ang. General-Purpose Register): E(AX), E(BX), E(CX), E(DX), E(SI), E(DI), E(BP) i E(SP)

♦

♦

♦

♦

sześć 16-bitowych rejestrów segmentowych (ang. Segment register): CS, DS, SS, ES, FS i GS

♦

♦

♦

♦

cztery rejestry systemowe zarządzania dostępem do pamięci (ang. System Register): GDTR, IDTR, LDTR, TR

♦

♦

♦

♦

wskaźnik instrukcji (zwany również licznikiem rozkazów) (ang. Instruction Pointer): E(IP)

♦

♦

♦

♦

rejestr znaczników/flag: E(FLAGS)

♦

♦

♦

♦

rejestry sterujące (ang. Control Register): CRO (MSW), CR2, CR3, (od procesora Pentium dodano CR4)

♦

♦

♦

♦

rejestry uruchomieniowe (ang. Debug Register): DR0, DR1, DR2, DR3, DR6, DR7

♦

♦

♦

♦

rejestry testowe (ang. Test Register): TR6 i TR7, (od i486 dodano TR3,TR4,TR5)

Przeznaczenie rejestrów procesora

Rejestry ogólnego przeznaczenia są wykorzystywane przez programy systemowe i użytkowe. Niektóre pełnią również funkcje specjalne: np. AX –

akumulator – zapisywany jest w nim wynik operacji arytmetyczno-logicznych, SP – wskaźnik stosu, CX – licznik, SI i DI – wskaźnik pozycji w łańcuchu.

System Windows (2k, 2k3, 2k8, XP, Vista) w momencie startu pracuje w trybie 16-bitowym (tzw. trybie rzeczywistym), po czym następuje za

pomocą odpowiednich wpisów do dodatkowych rejestrów systemowych przełączenie w 32-bitowy tryb chroniony procesora (chyba że jest to procesor z

rozszerzeniem EM-64T i mamy zainstalowany system 64-bitowy, wtedy następuje przełączenie w tryb 64-bitowy).

Większość operacji arytmetycznych i logicznych wykonuje się na (w) pamięci. Zatem procesor o architekturze 32-bitowej widzi aplikację jako kolejny

ciąg komórek pamięci zaczynających się od zera a kończących na wartości (4GB – tryb 32-bitowy). Dla procesora taką aplikacją jest również de facto 32-

bitowy system operacyjny. Nazwijmy ten adres adresem logicznym aplikacji.

Tryb rzeczywisty – Real Mode

W momencie startu lub resetu procesora przechodzi on w tryb rzeczywisty adresowania. W tym trybie procesor korzysta z rejestrów 16-bitowych (tryb

zgodności z 8086) i może zaadresować 1 MB pamięci operacyjnej.

Dla trybu 16-bitowego rzeczywistego

Adres logiczny jest reprezentowany przez parę liczb. Pierwsza nosi nazwę selektora (ang. Selector) i określa numer segmentu, druga przemieszczenie

(ang. Offset) wewnątrz segmentu. W każdej chwili procesor ma dostęp do 6 segmentów poprzez (16-bitowe) rejestry segmentowe CS, DS, ES, FS, GS i SS.

Taki sposób adresowania pozwala na adresowanie większej ilości pamięci RAM niż wynika to z 16-bitowego trybu pracy.

Dla trybu 32-bitowego chronionego

32-bitowy adres komórki pamięci w obrębie danej aplikacji - zostaje zamieniony na adres liniowy (również 32-bitowy) w obrębie pamięci fizycznej

obsługiwanej przez dany procesor

. Takie podejście pozwala na umieszczenie i jednoczesną obsługę wielu aplikacji 32-

bitowych w obrębie dostępnej dla procesora pamięci fizycznej RAM. Często wspólne dla wielu aplikacji

biblioteki dynamiczne .dll mogą być współdzielone przez wiele różnych aplikacji, co oznacza dostęp do tego

3

samego regionu pamięci RAM przez wiele aplikacji umożliwiając zmniejszenie zapotrzebowania na pamięć przez

wiele uruchomionych jednocześnie aplikacji.

Dodatkowo od modelu i386 wprowadzono dodatkowy mechanizm o nazwie stronicowanie (ang. Paging), który tłumaczy adres liniowy na adres

fizyczny.

Wyszukiwarka

Podobne podstrony:

zarządznie pamięcią

8 Systemy Operacyjne 21 12 2010 Zarządzanie Pamięcią Operacyjną

9 Systemy Operacyjne 04 01 2011 Zarządzanie Pamięcią Operacyjną2

C Wyklady, Zarzadzanie Pamiecia

C Wyklady Zarzadzanie Pamiecia

Zarządzanie pamięcią wewnętrzną

W jaki sposób zarządzanie łańcuchem zaopatrzenia stało się tym

SO7 Zarzadzanie pamiecia zewn

Zarzadzanie pamiecia

zarzadzanie pamiecia pomocnicza

Zarzadzanie pamiecia, systemy

Zarządzanie pamięcią operacyjną

2006 08 Zarządzanie pamięcią w systemach operacyjnych [Inzynieria Oprogramowania]

Nowoczesne sposoby zarządzania sieciami protokół NetFlow

Dynamiczne zarządzanie pamięcią new i delete, Programowanie, wykłady C++

SO6 Zarządzanie pamięcią wewnętrzną 1

więcej podobnych podstron