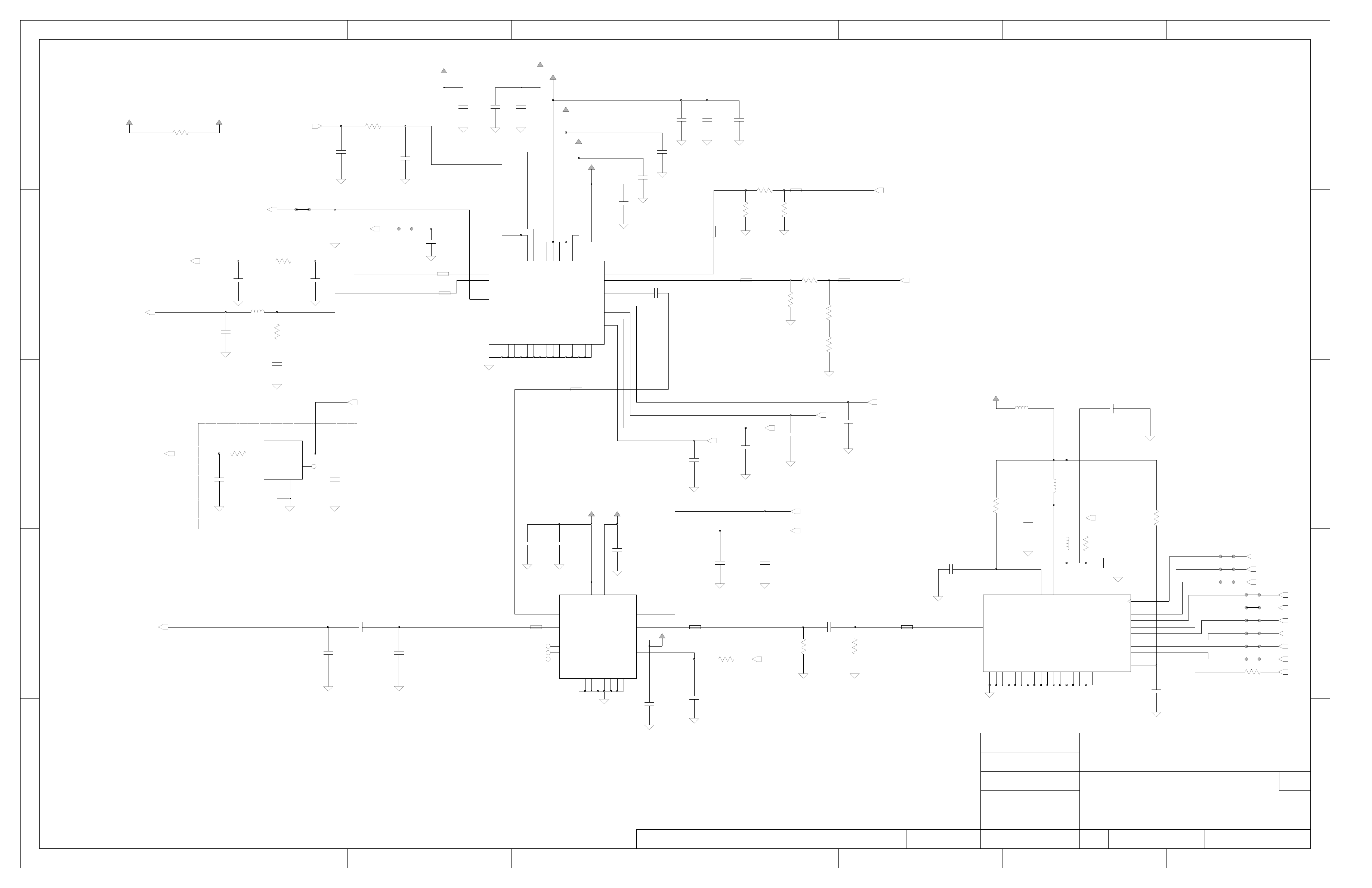

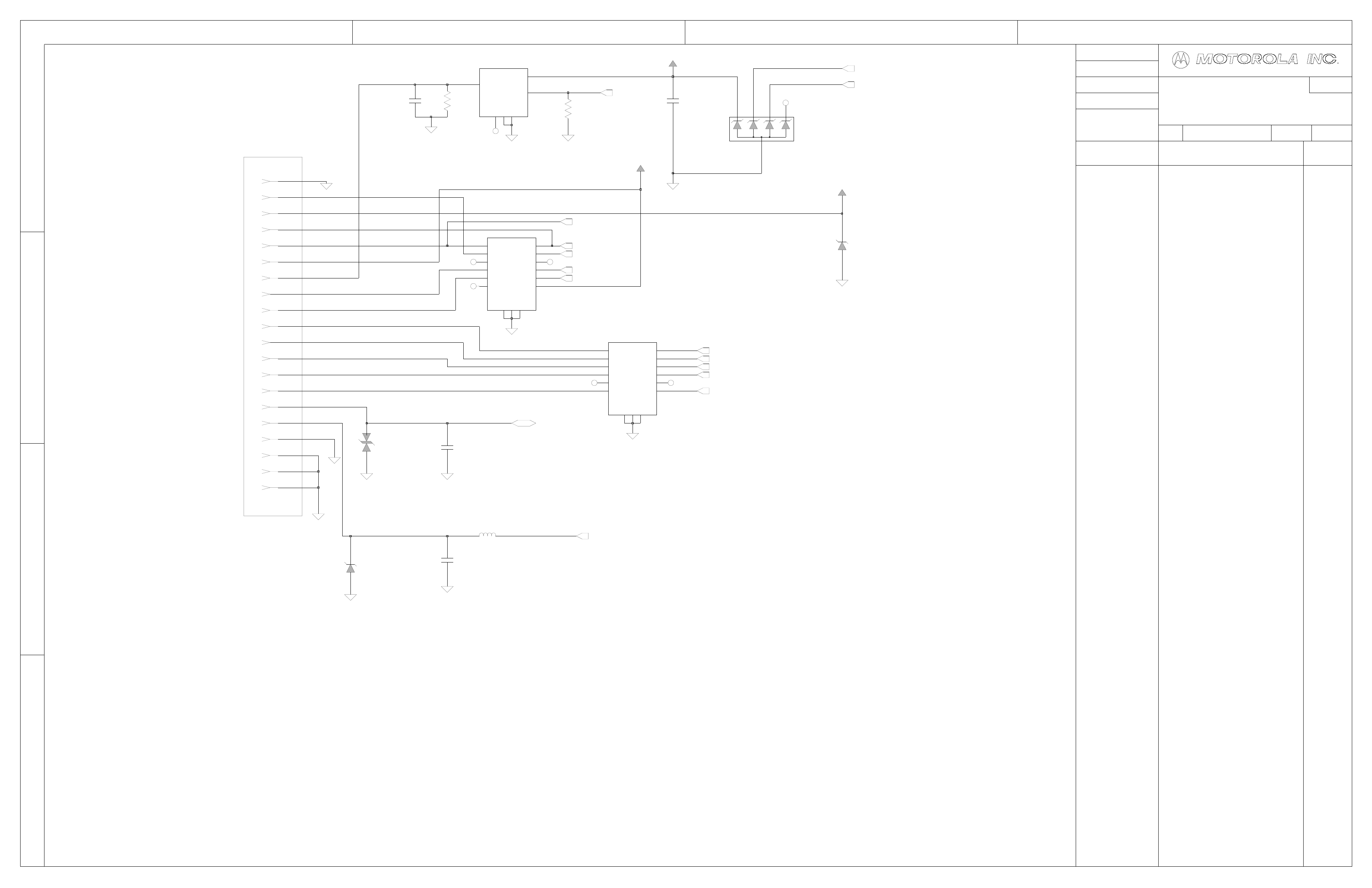

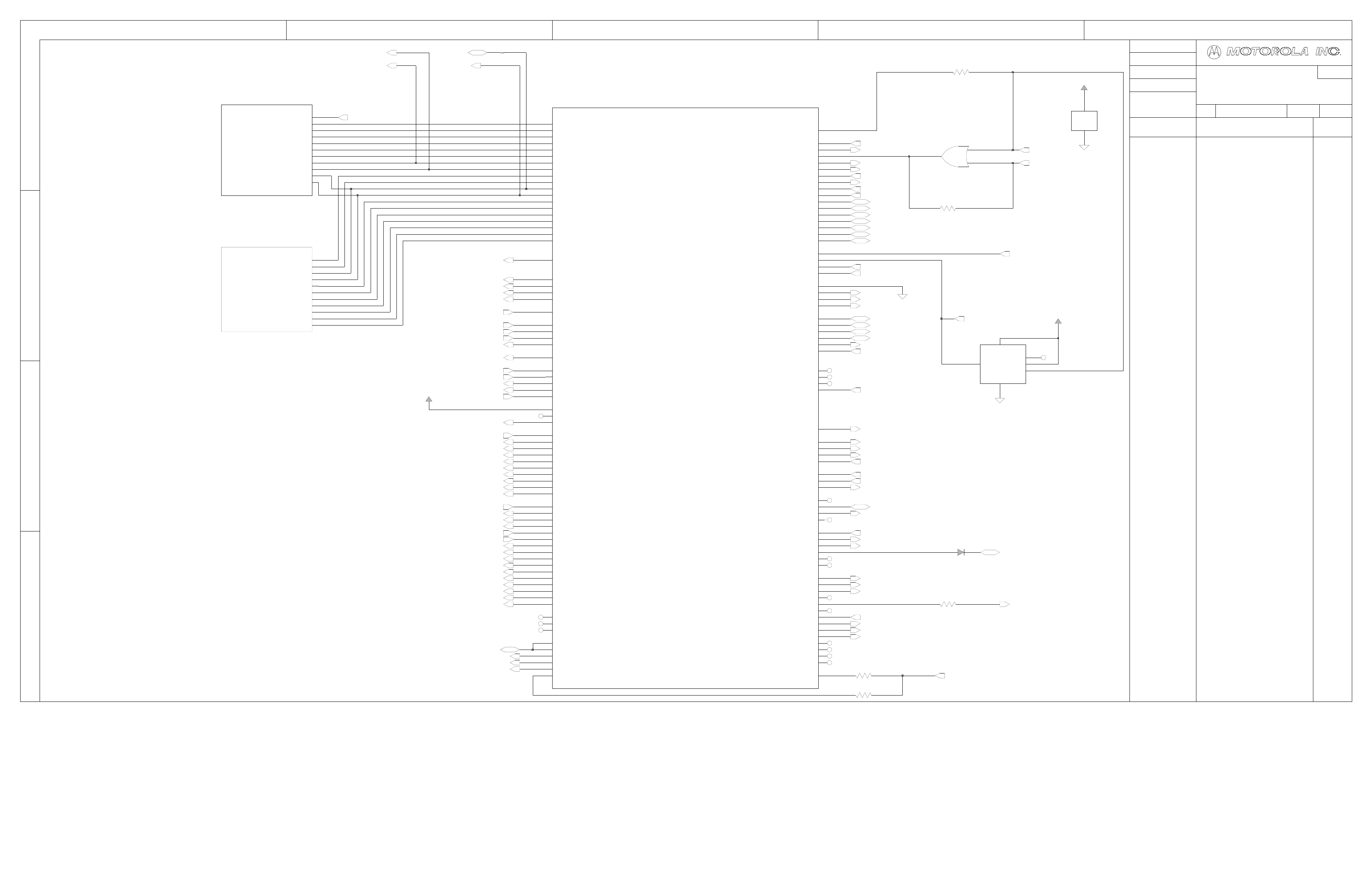

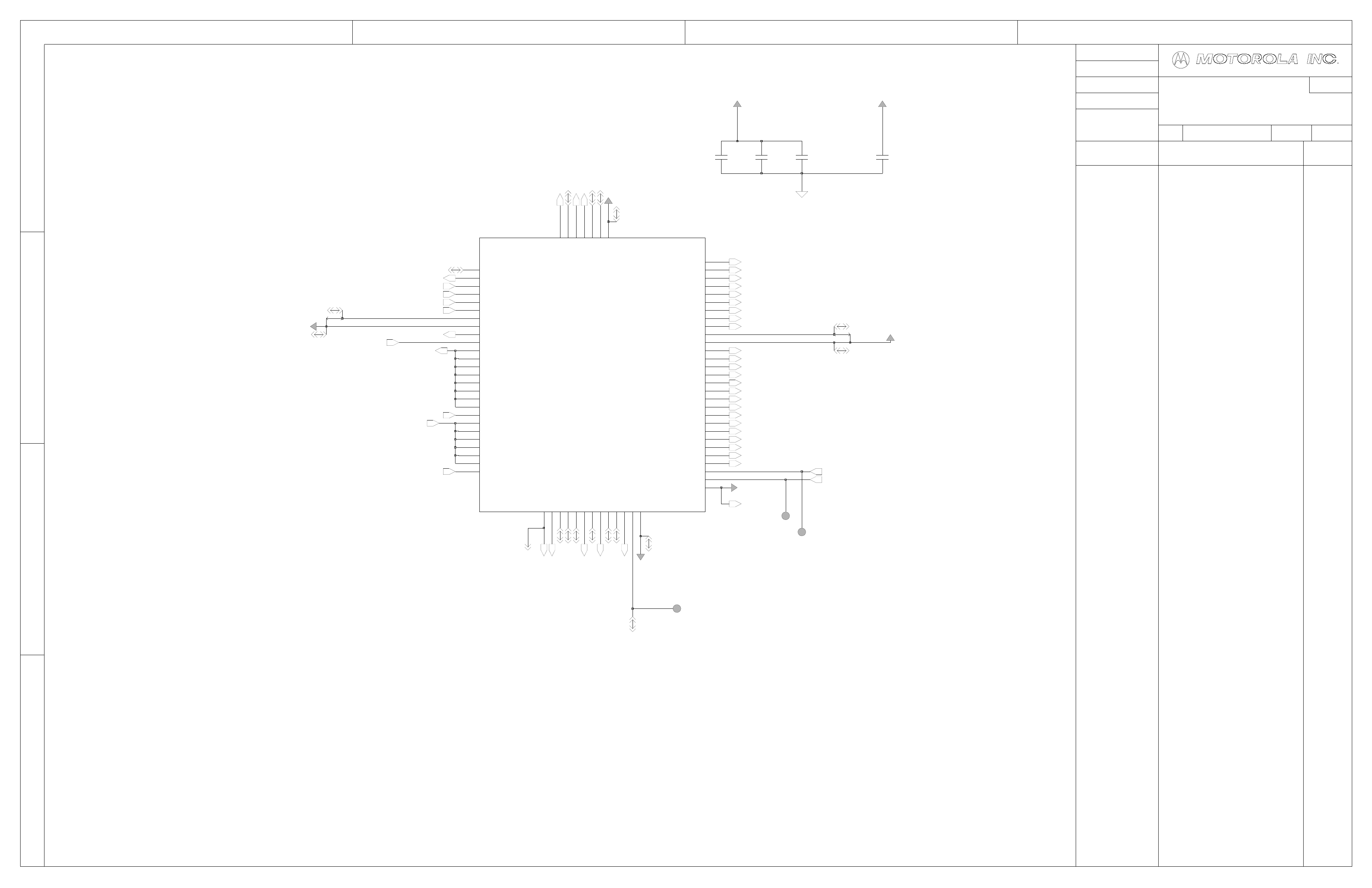

RF

Baseband

MFG CTRL CHK:

QA CHK:

REV:

Drawing Number:

Page:

TITLE:

Size:

Engineer:

Drawn by:

R&D CHK:

DOC CTRL CHK:

Of:

Changed by:

Time:

Date:

D

C

8403671B10

A

MOTOROLA CONFIDENTIAL PROPRIETARY

1

2

B

3

4

SHIELDS

All changes to the schematic are being

recorded and stored in:

X:\Projects_Area\Electrical\Projects\C975\PCB & Schematic Changes

file name:

Implemented_schematic_changes.xls

Note:

GND

GND

GND

GND

11x17

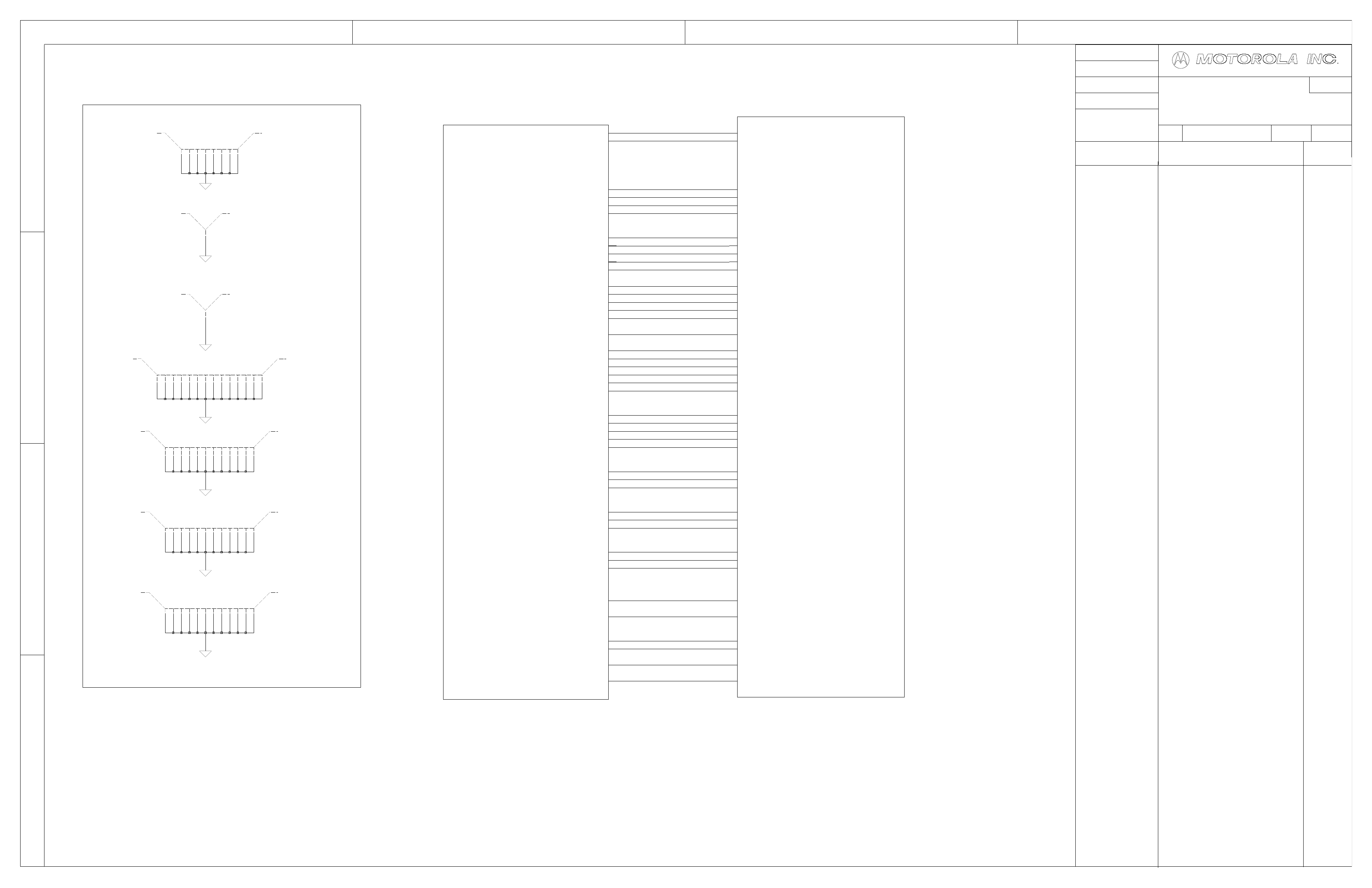

Top Level

September 17, 2003

Ed Naddeo

Ed Naddeo

Ed Naddeo

ELK (E1000)

11

12

3

4

5

6

7

8

9

10

GND

GND

GND

6

7

8

9

10

SHIELD

SH7

1

2

SHIELD

SH6

1

2

11

12

3

4

5

1

2

11

12

3

4

5

6

7

8

9

10

12

13

14

3

4

5

6

7

8

9

10

SHIELD

SH5

1

SH4

SHIELD

1

2

11

SH2

SHIELD

1

SH3

SHIELD

SHIELD

SH1

1

2

3

4

5

6

7

8

MB_SPI_MOSI

PS_CLK

PS_CLK_EN

PS_SPIMB_CE

PS_SPIWB_CE

STBY_MB

STBY_WB

TEMP_SENSE

TX_RAMP

TX_RX_ERROR

WB_SPIWB_CE

WB_SPI_CLK

WB_SPI_MISO

WB_SPI_MOSI

WB_VCO_SF_EN

BFSR

DMCS

HAR_MB_RX_ACQ

HAR_MB_RX_ON

HAR_MB_RX_SLOT

HAR_RESETb

HAR_SPIMB_CE

HAR_SPIWB_CE

HAR_TX_PREKEY

HAR_TX_SLOT

HAR_WB_RX_ACQ

HAR_WB_RX_ON

HAR_WB_RX_SLOT

MB_RX_VCO_EN

MB_SPI_CLK

MB_SPI_MISO

WB_SPI_CLK

WB_SPI_MISO

WB_SPI_MOSI

WB_VCO_SF_EN

AOC_PWR_UP

BBIF_CLK

BBIF_RX[7:2]

BBIF_RX_FRM

BBIF_TX[7:0]

BBIF_TX_FRM

BB_CLK_13M

BB_CLK_15_36M

BCLKR

BCLKX

BDR

BDX

HAR_WB_RX_SLOT

MB_RX_VCO_EN

MB_SPI_CLK

MB_SPI_MISO

MB_SPI_MOSI

PS_CLK

PS_CLK_EN

PS_SPIMB_CE

PS_SPIWB_CE

STBY_MB

STBY_WB

TEMP_SENSE

TX_RAMP

TX_RX_ERROR

WB_SPIWB_CE

BB_CLK_15_36M

BCLKR

BCLKX

BDR

BDX

BFSR

DMCS

HAR_MB_RX_ACQ

HAR_MB_RX_ON

HAR_MB_RX_SLOT

HAR_RESETb

HAR_SPIMB_CE

HAR_SPIWB_CE

HAR_TX_PREKEY

HAR_TX_SLOT

HAR_WB_RX_ACQ

HAR_WB_RX_ON

BDX

BDR

BCLKX

BCLKR

BB_CLK_15_36M

BB_CLK_13M

BBIF_TX_FRM

BBIF_TX[7:0]

BBIF_RX_FRM

BBIF_RX[7:2]

BBIF_CLK

AOC_PWR_UP

TX_RX_ERROR

AOC_PWR_UP

BBIF_CLK

BBIF_RX[7:2]

BBIF_RX_FRM

BBIF_TX[7:0]

BBIF_TX_FRM

BB_CLK_13M

WB_VCO_SF_EN

WB_SPI_MOSI

WB_SPI_MISO

WB_SPI_CLK

WB_SPIWB_CE

TX_RAMP

TEMP_SENSE

STBY_WB

STBY_MB

PS_SPIWB_CE

PS_SPIMB_CE

PS_CLK_EN

PS_CLK

MB_SPI_MOSI

MB_SPI_MISO

MB_SPI_CLK

MB_RX_VCO_EN

HAR_WB_RX_SLOT

HAR_WB_RX_ON

HAR_WB_RX_ACQ

HAR_TX_SLOT

HAR_TX_PREKEY

HAR_SPIWB_CE

HAR_SPIMB_CE

HAR_RESETb

HAR_MB_RX_SLOT

HAR_MB_RX_ON

HAR_MB_RX_ACQ

DMCS

BFSR

FEM_Q_BAND

RX_SYN

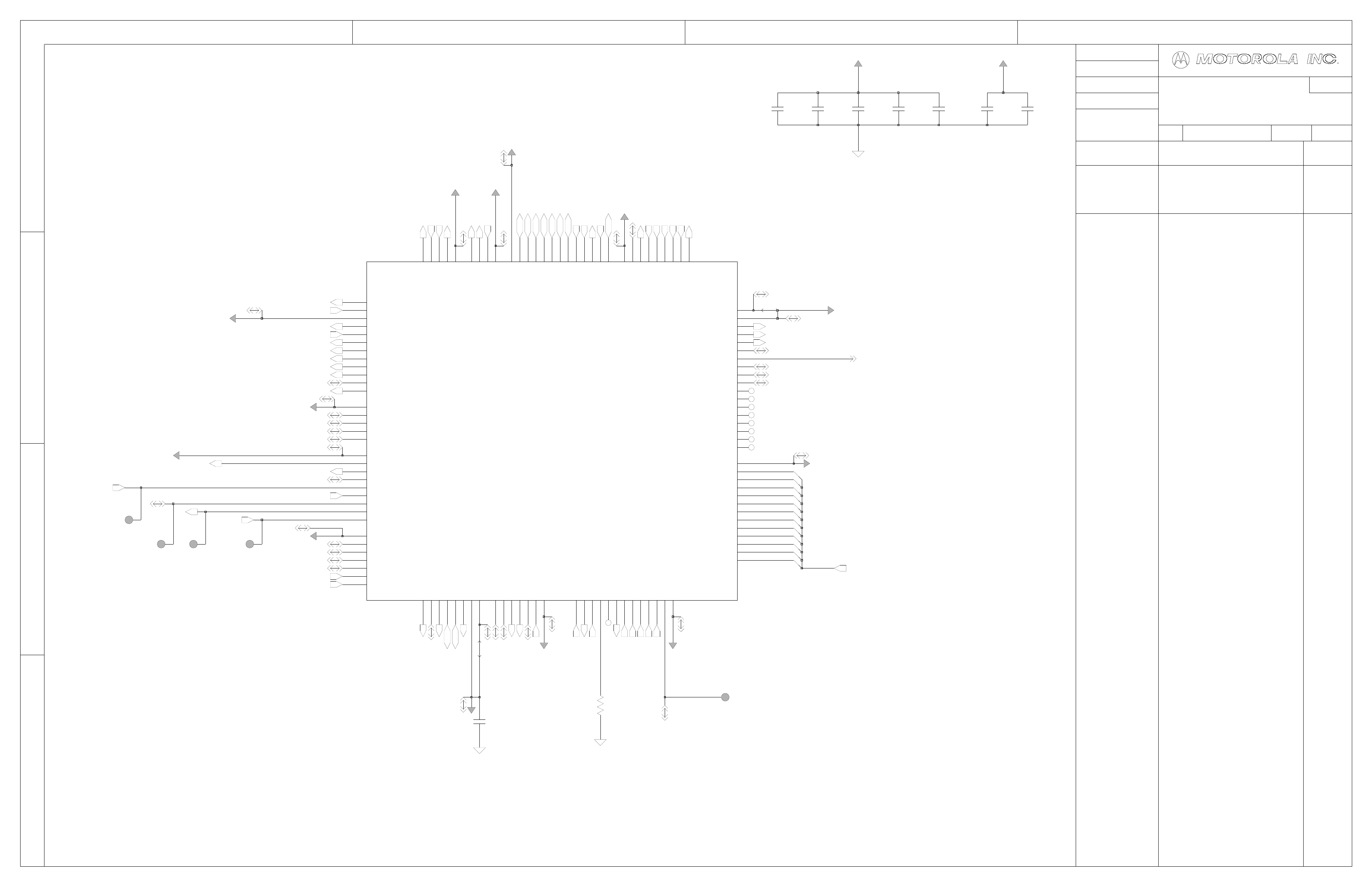

HARMONY

2

Drawing Number

C

D

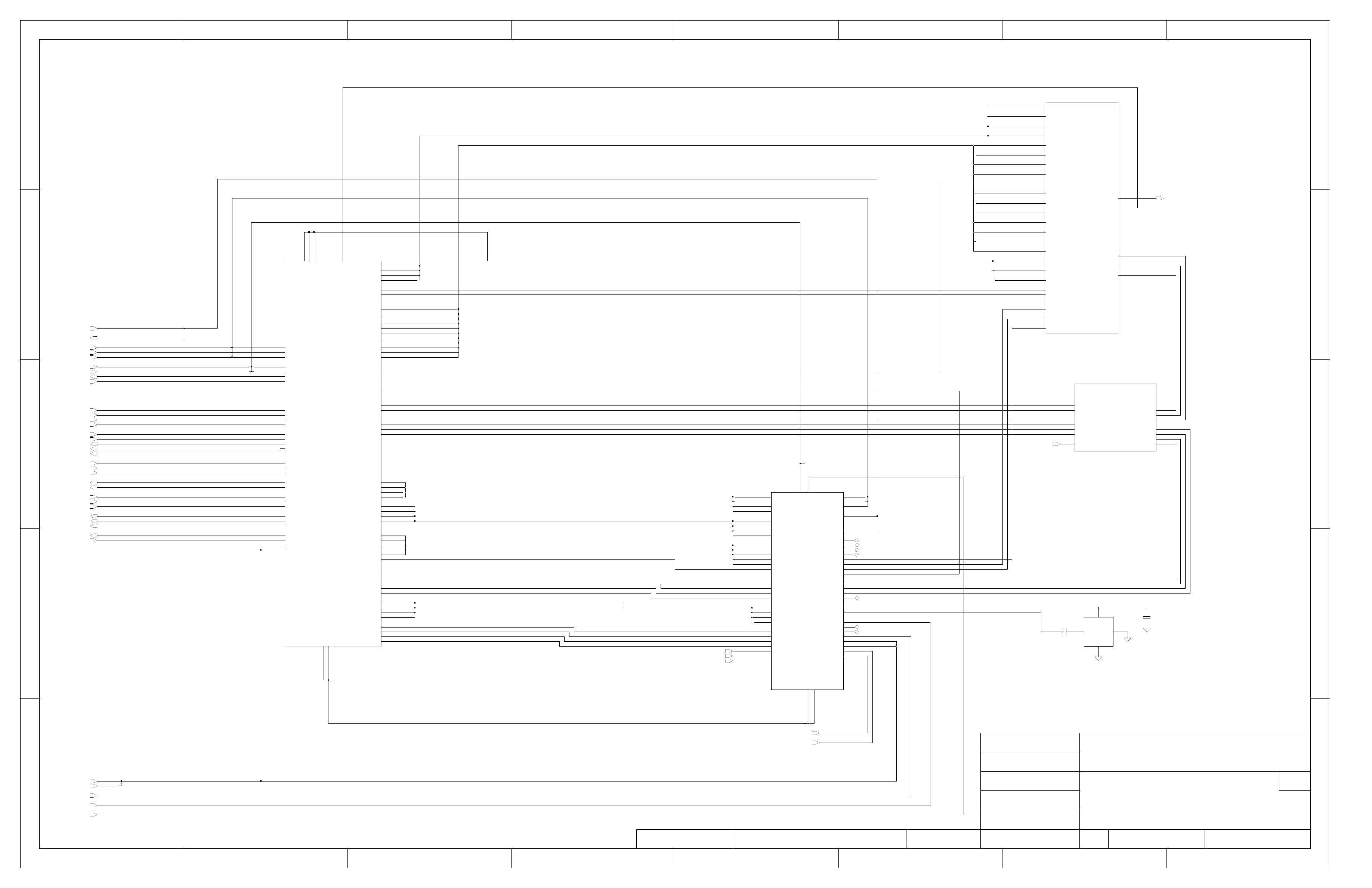

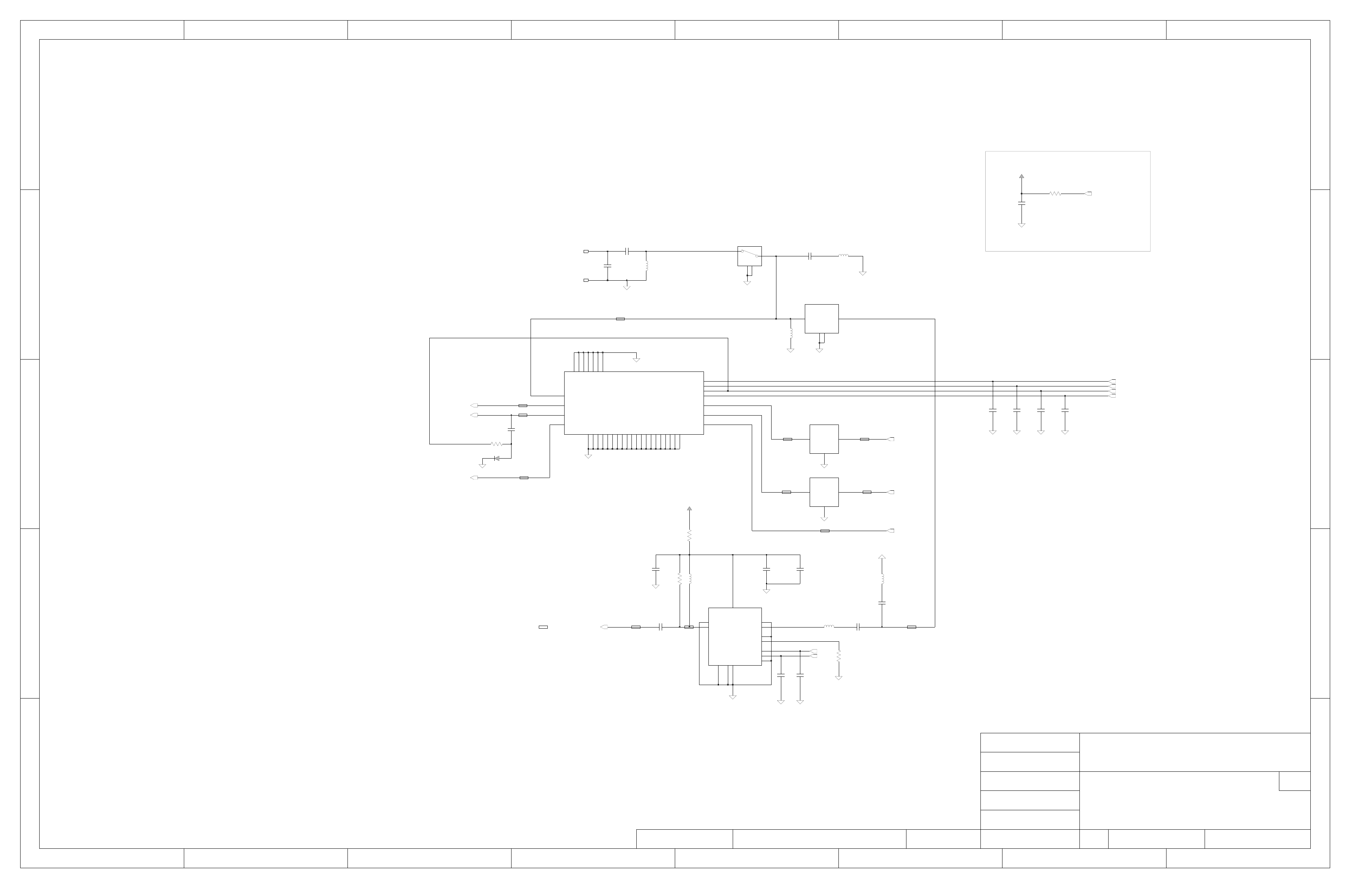

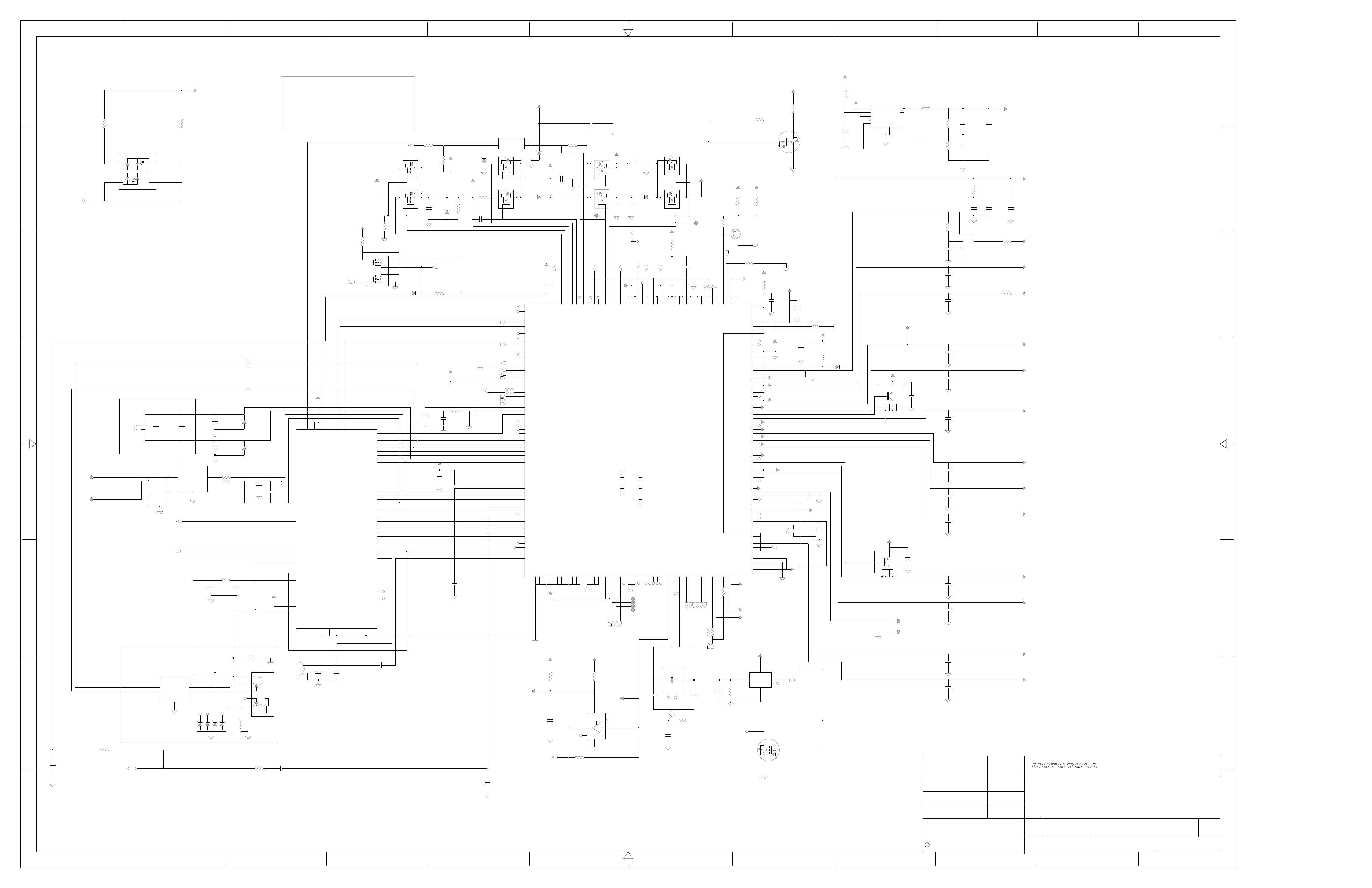

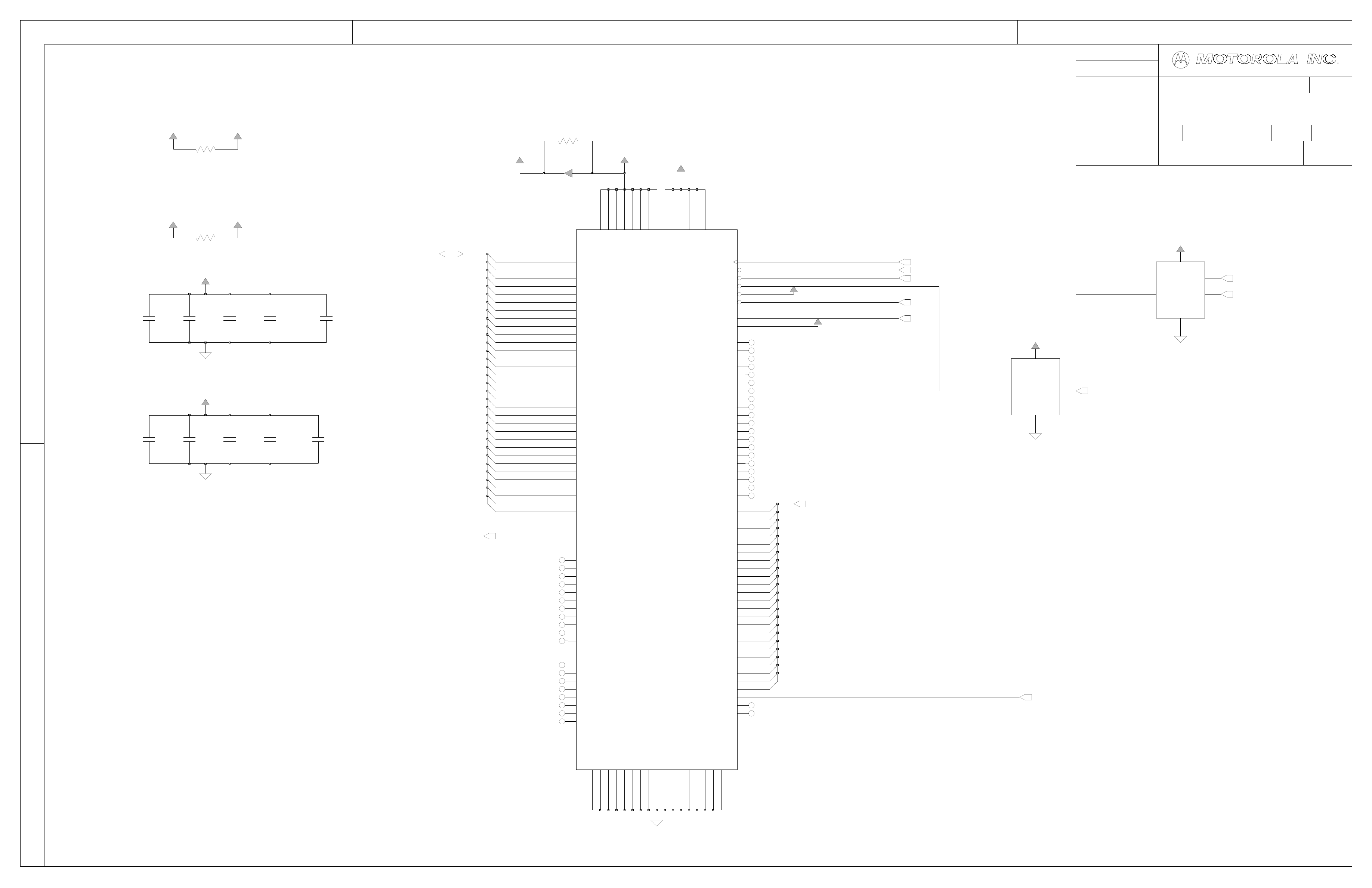

RF TOP LEVEL

3

600 North US Highway 45

Date Changed

A

8

MOTOROLA INC.

C975

B

R&D CHK

DOC CTRL CHK

6

MFG CTRL CHK

of

Libertyville

Drawn by

A

ccl003

3GFUN RF

D

5

E

TITLE

Size

Engineer

D

C

B

Time

Changed by

2

Motorola Confidential Proprietary

1

E

REFERENCE OSCILLATOR

4

5

REV

4

3

7

8

1

Sheet

7

6

QA CHK

Chris Leyh

ccl003

Friday, February 28, 2003

GND

NC

WB_RX_OUT

WB_TX_IN

NC

NC

MBC_EN0

MBC_EN1

MB_DCS_OUT

MB_GSM_OUT

MB_HB_RF_IN

MB_LB_RF_IN

MB_PCS_OUT

SW_POS1

SW_POS2

SW_POS3

SW_POS4

TX_RX_ERROR

Y100

18L24

GND

2

3

OUTPUT

4

VCC

1

V_CONT

NC

NC

26MHz

WB_PA_LOAD_SW

WB_PA_VBA1

WB_PA_VBA2

WB_TX_OUT

REF

RF_IN_DCS_PCS

RF_IN_GSM

SPI_ASPI_CE

SPI_ASPI_CLK

SPI_ASPI_DW

TEMP_SENSE

TEMP_SENSE_EN

TX_EN

VCO_EN

VEND

VENH

VENL

VGC

VMODE

WB_PA_ENABLE

TRANSMITTER

9E_VDET

9E_VREFDET

BB_I

BB_IX

BB_Q

BB_QX

DCS_PCS_TX_OUT

GSM_PA_VBA

GSM_TX_OUT

WB_PCS_IN

WB_Q

WB_QX

WB_RX_EN

WB_SPIWB_CE

WB_TRK_CLK

WB_UMTS_IN

WB_VCO_SF_EN

XTAL_OUT

GND

TCXO_IN

WB_AGC0

WB_AGC1

WB_AGC2

WB_AGC3

WB_AGC4

WB_CMODE

WB_DCOC_I

WB_DCOC_IX

WB_DCOC_Q

WB_DCOC_QX

WB_DCS_IN

WB_I

WB_IX

WB_LNA_BYP

PS_CLK_OUT

PS_SPIMB_CE

PS_SPIWB_CE

RESETB

SER_TX_CLK

SER_TX_DATA

SPIMB_CLK

SPIMB_DW

SPIWB_CLK

SPIWB_DW

STBY_MB

STBY_WB

SW_CP

SW_VCO_FB

SW_VCO_FB_X

TCXO_EN

MB_DCS_IN

MB_EXC_EN

MB_GSM850_IN

MB_GSM900_IN

MB_HB_RF_OUT

MB_I

MB_IX

MB_LB_RF_OUT

MB_PCS_IN

MB_Q

MB_QX

MB_RX_EN

MB_RX_VCO_EN

MB_TRK_CLK

PS_CLK

PS_CLK_ALT

PS_CLK_EN

DMCS

MB_ASPI_CE

MB_ASPI_CLK

MB_ASPI_DATA

MB_CM_IN

NC

.01uF

GND

NC

WB_I

WB_IX

WB_LNA_BYP

WB_Q

WB_QX

WB_RX_EN

WB_TRK_CLK

C9127

SW_VCO_EN

TEMP_SENSE_EN

TX_EN

TX_EN_2V7

TX_WB_EN

WB_AGC0

WB_AGC1

WB_AGC2

WB_AGC3

WB_AGC4

WB_CKIH

WB_CMODE

WB_DCOC_I

WB_DCOC_IX

WB_DCOC_Q

WB_DCOC_QX

SPIWB_DR

SPIWB_DW

STBY_MB

STBY_WB

SW_ASPI_CE

SW_ASPI_CLK

SW_ASPI_DW

SW_I

SW_IX

SW_POS1

SW_POS2

SW_POS3

SW_POS4

SW_Q

SW_QX

SW_VCA_AOC

PAR_RX_DATA(7:2)

PAR_RX_FRAME

PAR_TRX_CLK

PAR_TX_DATA(7:0)

PAR_TX_FRAME

PA_VBA1

PA_VBA2

PS_CLK_OUT

RESETB

SER_RX_CLK

SER_RX_DATA

SER_RX_FRAME

SPIMB_CLK

SPIMB_DR

SPIMB_DW

SPIWB_CLK

HB_EN

LB_EN

MBC_EN0

MBC_EN1

MB_ASPI_CE

MB_ASPI_CLK

MB_ASPI_DATA

MB_CKIH

MB_CM_IN

MB_EXC_EN

MB_I

MB_IX

MB_Q

MB_QX

MB_RX_EN

MB_TRK_CLK

9E_VDET

9E_VMODE

9E_VREFDET

AOC_PWR_UP_DN

GSM_PA_VBA

HAR_MB_RX_ACQ

HAR_MB_RX_ON

HAR_MB_RX_SLOT

HAR_SPIMB_CE

HAR_SPIWB_CE

HAR_TX_PREKEY

HAR_TX_RAMP

HAR_TX_SLOT

HAR_WB_RX_ACQ

HAR_WB_RX_ON

HAR_WB_RX_SLOT

C100

.01uF

5W_VLD

INT{HAR_RESETb,STBY_MB,STBY_WB}

MB_SPI_MOSI

MB_SPI_MOSI

MB_SPI_CLK

MB_SPI_CLK

SPIMB{MB_SPI_CLK,MB_SPI_MOSI}

SPIMB{MB_SPI_CLK,MB_SPI_MOSI}

SPIMB{MB_SPI_CLK,MB_SPI_MOSI}

PS_CLK

PS_CLK_EN

PS_CLK{PS_CLK_EN,BLUETOOTHCLK,GPS_CLK,PS_CLK}

DMCS

BCLKX

MB_RX_VCO_EN

TCXO_EN

TX_RX_ERROR

WB_SPI_MOSI

WB_SPI_CLK

SPI_WB{WB_SPI_CLK,WB_SPI_MOSI}

STBY_WB

HAR_RESETb

BDX

WB_AGC4

WB_AGC3

WB_AGC2

WB_AGC1

WB_AGC0

WB_AGC{WB_AGC0,WB_AGC1,WB_AGC2,WB_AGC3,WB_AGC4}

WB_QX

WB_Q

WB_IX

WB_I

WB_IQ{WB_I,WB_IX,WB_Q,WB_QX}

MB_ASPI_CE

MB_ASPI_DATA

MB_ASPI_CLK

MB_ASPI{MB_ASPI_CLK,MB_ASPI_DATA,MB_ASPI_CE}

WB_DCOC_QX

WB_DCOC_Q

WB_DCOC_IX

WB_DCOC_I

WB_DCOC{WB_DCOC_I,WB_DCOC_IX,WB_DCOC_Q,WB_DCOC_QX}

MB_Q

MB_QX

MB_IX

MB_I

MB_IQ{MB_I,MB_IX,MB_Q,MB_QX}

INT{HAR_RESETb,STBY_MB,STBY_WB}

WB_VCO_SF_EN

WB_RX

WB_TRK_CLK

WB_SPIWB_CE

WB_RX_EN

WB_LNA_BYP

WB_CMODE

TX_RAMP

TCXO_IN

PS_SPIWB_CE

PS_SPIWB_CE

PS_SPIMB_CE

PS_CLK_OUT

MB_RX_EN

MB_PCS

MB_LB_RF

MB_HB_RF

MB_GSM

MB_DCS

STBY_MB

MB_SPI_CLK

MB_SPI_MOSI

SW_ASPI_DW

SW_ASPI_CLK

SW_ASPI_CE

9E_MODE

TX_WB_EN

5W_VLD

TX_EN_2V7

TEMP_SENSE

TEMP_SENSE_EN

TX_EN

SW_VCA_AOC

SW_VCO_EN

PA_VBA1

PA_VBA2

TX_FE{SW_FB_CAL,SW_FB_SEL,SW_VCO_EN,TX_EN,SW_VCA_AOC,SK_VCA_AOC,TX_WB_EN,5W_VLD,PA_VBA1,PA_VBA2,TX_EN_2V7,9E_MODE,HB_EN,LB_EN,RA_BIAS_MIXER}

WB_TX

GSM_TX

MBC_EN2

MBC_EN1

DCS_PCS_TX

SW_POS4

SW_POS3

SW_POS2

SW_POS1

MB_ASPI_CE

LB_EN

HB_EN

HAR_WB_RX_SLOT

HAR_WB_RX_ON

HAR_WB_RX_ACQ

HAR_TX_SLOT

HAR_TX_PREKEY

HAR_SPIWB_CE

HAR_SPIMB_CE

HAR_MB_RX_SLOT

HAR_MB_RX_ON

HAR_MB_RX_ACQ

AOC_PWR_UP

9E_MODE

5W_VLD

SW_ASPI{SW_ASPI_CLK,SW_ASPI_DW,SW_ASPI_CE}

LB_EN

HB_EN

STBY_MB

STBY_MB

STBY_MB

SW_QX

SW_Q

SW_IX

SW_I

SW_QX

SW_Q

SW_IX

SW_I

SW_ASPI_DW

SW_ASPI_CLK

SW_ASPI_CE

STBY_WB

WB_SPI_MOSI

WB_SPI_MISO

WB_SPI_CLK

MB_SPI_MOSI

MB_SPI_MISO

MB_SPI_CLK

BFSR

BDR

BCLKR

HAR_RESETb

PA_VBA2

PA_VBA1

BBIF_TX_FRM

BBIF_TX[7:0]

BBIF_CLK

BBIF_RX_FRM

BBIF_RX[7:2]

MB_QX

MB_Q

MB_IX

MB_I

BB_CLK_13M

MB_ASPI_DATA

MB_ASPI_CLK

SW_IQ{SW_I,SW_IX,SW_Q,SW_QX}

HAR_RESETb

HAR_RESETb

STBY_WB

STBY_WB

WB_SPI_CLK

WB_SPI_CLK

PS_CLK_EN

PS_CLK_EN

PS_CLK

PS_CLK

WB_SPI_MOSI

WB_SPI_MOSI

WB_QX

WB_Q

WB_IX

WB_I

WB_DCOC_QX

WB_DCOC_Q

WB_DCOC_IX

WB_DCOC_I

BB_CLK_15_36M

WB_AGC4

WB_AGC3

WB_AGC2

WB_AGC1

WB_AGC0

TX_WB_EN

TX_EN_2V7

TX_EN

SW_VCO_EN

SW_VCA_AOC

Date Changed

UR_ANCH

Sheet

of

TITLE

Dif.

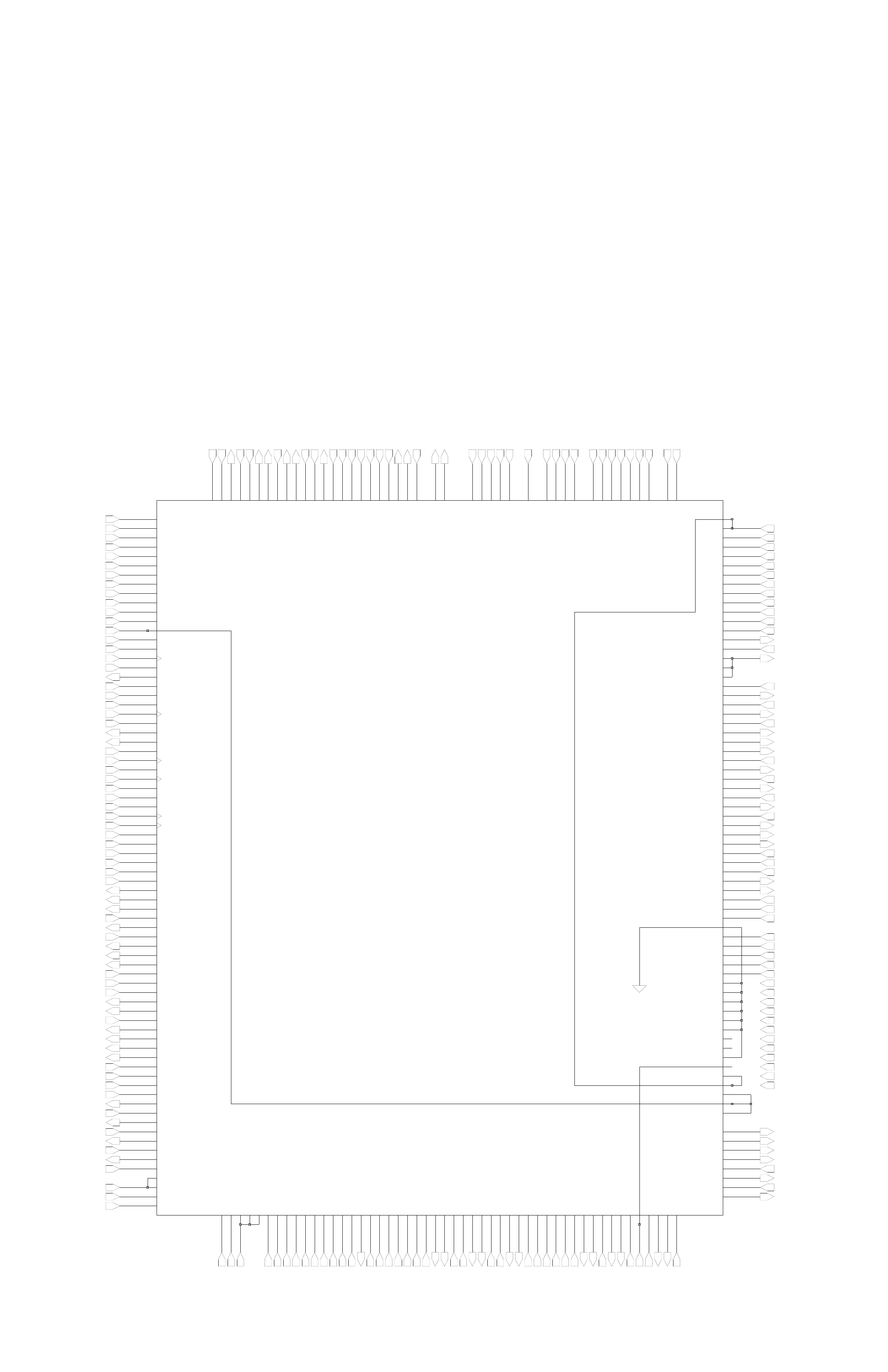

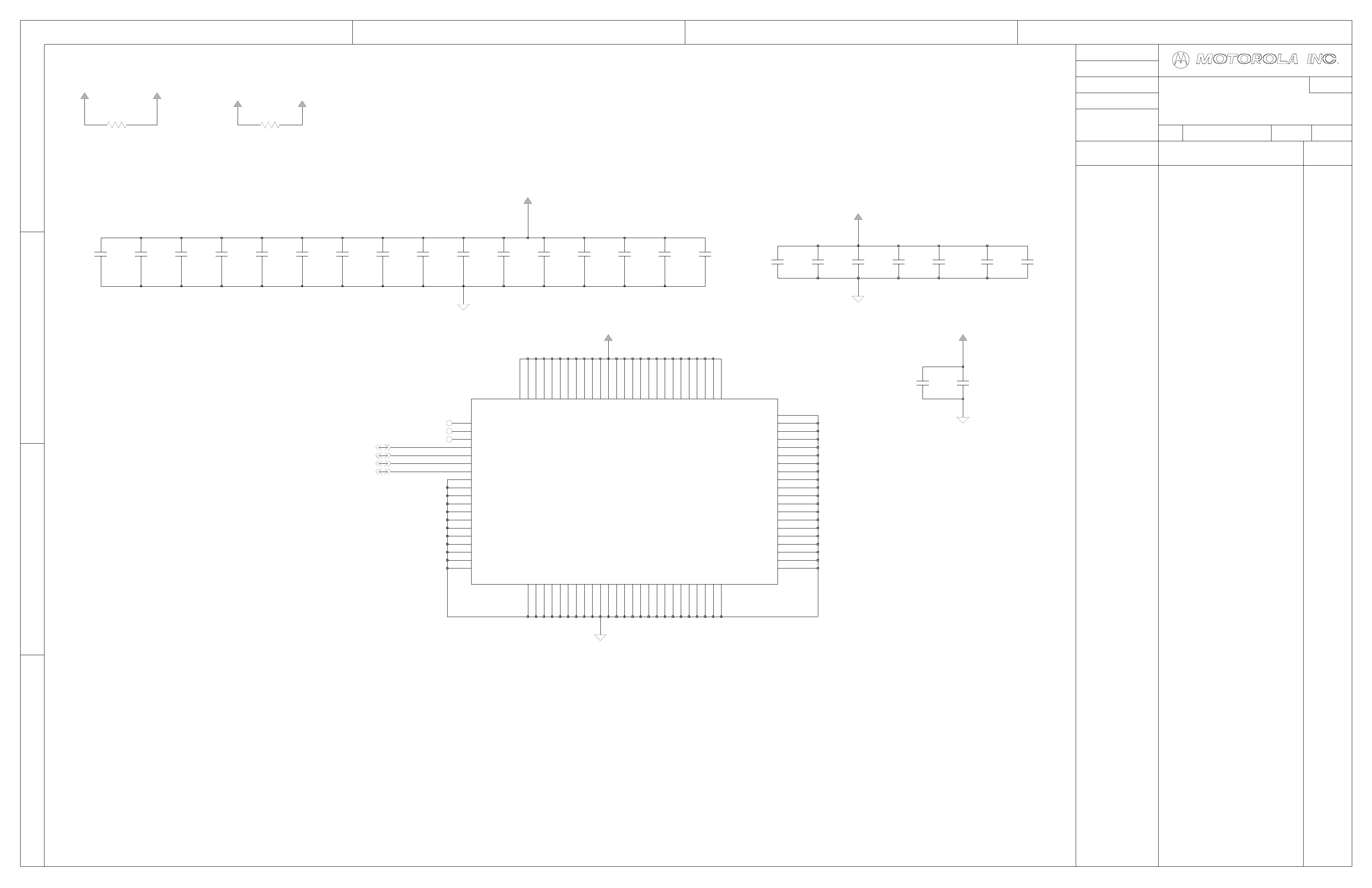

ALL CAPACITORS CLOSE TO HARMONY

BB_GND

1

4

A

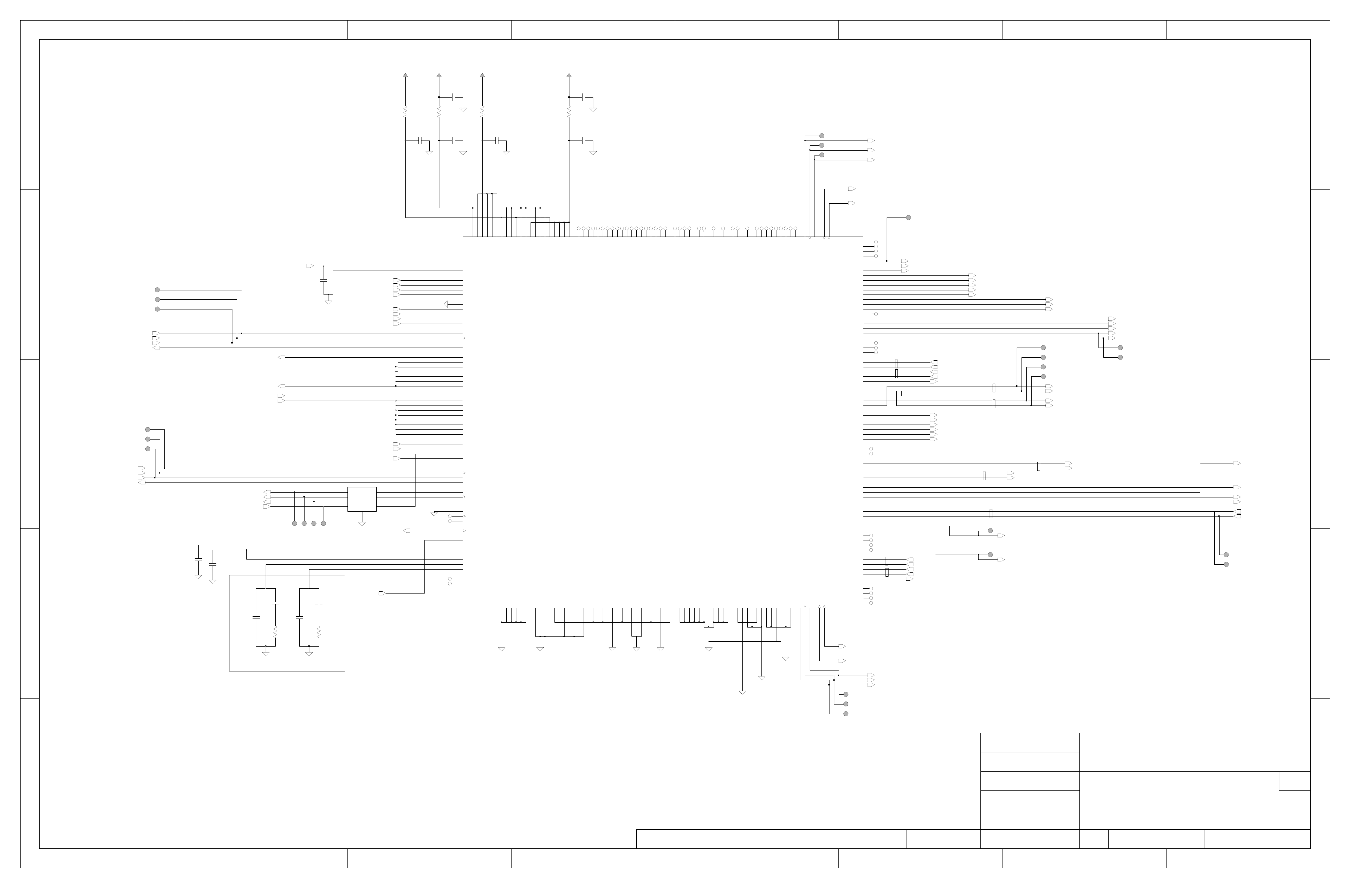

HARMONY

7

7

600 North US Highway 45

Size

Libertyville

Changed by

4

Dif.

C975

2

ALL CAPACITORS CLOSE TO HARMONY

8

UL_ANCH

RX_SD_GND

B

Dif.

A

5

6

6

Dif.

Engineer

Drawn by

Dif.

REV

SYNTHESIS CAPACITORS CLOSE TO HARMONY

B

MOTOROLA INC.

Motorola Confidential Proprietary

TX_SD_GND

SYN_GND

LL_ANCH

C

1

Dif.

Dif.

Drawing Number

TX_RF_GND

D

E

2

C

D

Time

7

1

LR_ANCH

SUPPLIES INTERCONNECTIONS FAR FROM HARMONY

3

Dif.

R&D CHK

8

70 ohm

3

E

TP placeholders for pins with NC

DOC CTRL CHK

MFG CTRL CHK

QA CHK

5

HARMONY

D

ccl003

Chris Leyh

12:06:46 pm

Thursday, April 17, 2003

ccl003

1

70 ohm

4

Dif.

U9129

TEST_POINT

1

TEST_POINT

TP531

1

NC

TP516

TEST_POINT

1

NC

1

R505

0

NC

NC

GND

TP525

TEST_POINT

TP538

1

NC

NC

NC

TEST_POINT

TP508

1

NC

TEST_POINT

NC

NC

NC

NC

4.7uF

C507

1

NC

NC

GND

NC

C506

TEST_POINT

TP510

NC

4.7uF

NC

NC

NC

GND

GND

NC

NC

C514

TP530

TEST_POINT

1

GND

33pF

VRF_TX_2.775V

NC

NC

NC

GND

.01uF

C510

39pF

C520

NC

NC

39pF

C521

GND

NC

NC

TP539

TEST_POINT

1

C511

.01uF

NC

NC

C518

1.0uF

NC

NC

NC

TEST_POINT

TP519

1

R504

0

1

GND

GND

NC

NC

NC

GND

TP507

TEST_POINT

39pF

NC

NC

NC

NC

NC

C516

NC

GND

NC

GND

R502

0

NC

TP532

TEST_POINT

1

NC

1500pF

C512

TEST_POINT

TP526

1

TP518

1

GND

NC

NC

GND

TEST_POINT

1

GND

NC

TEST_POINT

1.0uF

C515

TP509

TP547

TEST_POINT

1

TEST_POINT

TP535

1

NC

NC

NC

NC

GND

GND

NC

GND

TP527

TEST_POINT

1

VHVIO_2.775V

NC

C9128

39pF

TX_VDD

A13

R500

1.5K

TX_SD_Q_P_IN

E4

TX_SD_VCC

D7

TX_SER_CLK_OUT

H13

TX_SER_DATA_IN

J18

G13

TX_SER_FRAME_OUT

TX_SLOT_IN

H17

TX_START_IN

G15

TX_VAG_VCC

E5

TX_SD_GND_1

TX_SD_GND_2

A5

TX_SD_GND_3

A6

TX_SD_GND_4

A7

TX_SD_GND_5

A8

TX_SD_GND_6

A9

TX_SD_I_M_IN

F3

TX_SD_I_P_IN

F4

TX_SD_Q_M_IN

E3

TX_PAR_DATA_IN_6

J16

TX_PAR_DATA_IN_7

K17

TX_PAR_FRAME_IN

H16

TX_PREKEY_IN

H18

TX_Q_M_OUT

G3

TX_Q_P_OUT

G4

TX_RAMP_IN

G14

A4

TX_I_M_OUT

H4

TX_I_P_OUT

H3

TX_PAR_DATA_IN_0

K16

TX_PAR_DATA_IN_1

L18

L17

TX_PAR_DATA_IN_2

TX_PAR_DATA_IN_3

H14

TX_PAR_DATA_IN_4

H15

TX_PAR_DATA_IN_5

K18

E13

TX_AOC_OUT_2

D12

TX_AOC_OUT_3

F12

TX_AOC_REF_IN

B11

TX_AOC_UPDWN_IN

J17

TX_AOC_VCC

F11

TX_DAC_GND

D8

TX_DAC_VCC

D9

TX_GND

A14

TX_AMP_GND_2

D1

TX_AMP_GND_3

E1

TX_AMP_VCC

J1

TX_AOC_DET_IN

B10

TX_AOC_DRVR_GND

D13

TX_AOC_GND

D10

TX_AOC_OUT_0

E12

TX_AOC_OUT_1

J9

SYN_STANDBY_IN_0

SYN_STANDBY_IN_1

J8

J7

SYN_TIMER_OUT_0

SYN_TIMER_OUT_1

J6

SYN_VDD

L4

SYN_WB_CLK_OUT

L13

J4

TEST_MODE_IN

TX_AMP_GND_1

C1

K12

SYN_MB_CLK_OUT

L12

SYN_PAR_CLK_OUT

L5

SYN_REF_IN

SYN_SF_GND

L2

L8

SYN_SF_OUT

L6

SYN_SF_REF

L7

SYN_SF_SENS

SYN_SF_VCC

L3

SPI_DATA_IN_0

L16

SPI_DATA_IN_1

K13

SPI_DATA_OUT_0

J14

SPI_DATA_OUT_1

SYN_CP_GND

P1

N4

SYN_CP_OUT_0

SYN_CP_OUT_1

P3

SYN_CP_VCC

P2

SYN_GND

J2

D15

SM_OUT_7

C16

SM_OUT_8

B18

SM_OUT_9

K14

SPI_CE_IN_0

J15

SPI_CE_IN_1

J13

SPI_CLK_IN_0

K15

SPI_CLK_IN_1

N19

SM_OUT_20

F15

SM_OUT_21

F14

F13

SM_OUT_22

G16

SM_OUT_23

A17

SM_OUT_3

F17

SM_OUT_4

SM_OUT_5

D14

SM_OUT_6

E14

SM_OUT_12

SM_OUT_13

C19

D17

SM_OUT_14

SM_OUT_15

D16

E17

SM_OUT_16

D19

SM_OUT_17

E16

SM_OUT_18

E19

SM_OUT_19

B17

SM_OUT_2

U19

RX_WB_ON_IN

R13

RX_WB_SLOT_IN

RX_WB_TRK_CLK_OUT

M11

B16

SM_OUT_0

A16

SM_OUT_1

C17

SM_OUT_10

C18

SM_OUT_11

D18

M10

RX_SD_VAGI_2

RX_SD_VCC_1

N8

RX_SD_VCC_2

N10

R17

RX_SER_CLK_OUT

T16

RX_SER_DATA_OUT

P15

RX_SER_FRAME_OUT

RX_VDD

W16

P14

RX_WB_ACQ_IN

RX_SD_I_M_IN_1

T10

RX_SD_I_M_IN_2

R7

RX_SD_I_P_IN_1

R10

RX_SD_I_P_IN_2

R8

RX_SD_Q_M_IN_1

T9

RX_SD_Q_M_IN_2

T8

RX_SD_Q_P_IN_1

R9

RX_SD_Q_P_IN_2

RX_SD_VAGI_1

N9

RX_SD_GND_1_4

W6

RX_SD_GND_1_5

W7

RX_SD_GND_1_6

W8

RX_SD_GND_2_1

W12

RX_SD_GND_2_2

W13

RX_SD_GND_2_3

W14

RX_SD_GND_2_4

W15

T7

RX_PAR_DATA_OUT_3

N15

RX_PAR_DATA_OUT_4

T19

RX_PAR_DATA_OUT_5

N14

RX_PAR_DATA_OUT_6

P19

RX_PAR_DATA_OUT_7

RX_PAR_FRAME_OUT

N16

RX_SD_GND_1_1

W3

RX_SD_GND_1_2

W4

RX_SD_GND_1_3

W5

RX_IO_VCC

M9

RX_IO_VDD

L9

RX_MB_ACQ_IN

N12

T18

RX_MB_ON_IN

U18

RX_MB_SLOT_IN

P6

RX_MB_TRK_CLK_OUT

T17

RX_PAR_DATA_OUT_2

N13

RX_DCOC_GND

U1

T2

RX_DCOC_I_M_OUT

R2

RX_DCOC_I_P_OUT

T3

RX_DCOC_Q_M_OUT

R3

RX_DCOC_Q_P_OUT

RX_DCOC_VCC

P4

RX_GND

U17

RX_IO_GND

R5

RX_AGC_STEPA_OUT_1

V2

RX_AGC_STEPB_OUT_0

P5

RX_AGC_STEPB_OUT_1

V1

RX_AGC_STEPC_OUT_0

N5

RX_AGC_STEPC_OUT_1

R12

RX_AGC_STEP_OUT

RX_ASPI_CE_OUT

N6

RX_ASPI_CLK_OUT

N7

RX_ASPI_DATA_OUT

M7

J11

K11

RX_AGC_OUT_1

L11

RX_AGC_OUT_2

K9

RX_AGC_OUT_3

L10

RX_AGC_OUT_4

N11

RX_AGC_SOS_IN_0

P11

RX_AGC_SOS_IN_1

U4

RX_AGC_STEPA_OUT_0

T5

OPEN_4

A19

OPEN_5

B1

OPEN_6

B19

OPEN_7

V18

OPEN_8

V19

OPEN_9

W1

J5

RST_B_IN

RX_AGC_OUT_0

NC_8

F5

NC_9

F6

OPEN_1

A1

OPEN_10

W2

OPEN_11

W18

OPEN_12

W19

OPEN_2

A2

OPEN_3

A18

U14

NC_36

U15

NC_37

U16

NC_38

W11

E18

NC_39

NC_4

C14

NC_5

C15

NC_6

E7

NC_7

E9

N18

NC_29

T13

NC_3

C8

NC_30

T14

NC_31

T15

NC_32

U5

NC_33

U6

NC_34

U13

NC_35

G18

NC_21

H5

NC_22

H6

NC_23

H7

NC_24

H8

NC_25

H9

H11

NC_26

NC_27

H12

NC_28

NC_14

G7

NC_15

G8

NC_16

G9

NC_17

G11

G12

NC_18

NC_19

G17

NC_2

C7

NC_20

F19

INF_IO_VDD_B

INF_SM_VCC

A15

INF_VDD

B14

C6

NC_1

NC_10

F7

NC_11

F8

NC_12

F9

NC_13

G6

INF_ASPI_CLK_OUT

C3

INF_ASPI_DATA_OUT

E6

INF_ASPI_IO_GND

D3

INF_ASPI_IO_OVDD

D6

INF_ASPI_IO_VDD

D5

INF_IO_GND_A

J12

INF_IO_GND_B

F16

INF_IO_VDD_A

N17

U500

50M23

INF_ASPI_CE_OUT

D4

1

100pF

C513

B3GND

B4

B4

B5

B5

NC

TEST_POINT

TP533

A1

A1

A2

A2

A4

A4

A5

A5

B1

B1

B2

B2

B3

NC

GND

GND

CSPRC032AG

FL500

1

VLVIO_1.875V

TP534

TEST_POINT

1

VRF_RX_2.775V

NC

TEST_POINT

TP517

TP523

TEST_POINT

1

TP537

TEST_POINT

1

TEST_POINT

TP524

1

TEST_POINT

TP522

1

1.5K

NC

R501

0

R503

NC

TEST_POINT

TP536

1

NC

GND

NC

TEST_POINT

TP548

1

GND

SW_I

SW_IX

TX_EN

MBC_EN1

MBC_EN0

PS_CLK_OUT

WB_AGC0

WB_AGC2

WB_AGC4

GND

PAR_TX_DATA(6)

PAR_TX_DATA(5)

PAR_TX_DATA(4)

PAR_TX_DATA(3)

PAR_TX_DATA(2)

PAR_TX_DATA(1)

PAR_TX_DATA(7:0)

5W_VLD

TX_WB_EN

PA_VBA1

PA_VBA2

SW_VCO_EN

SW_VCA_AOC

LB_EN

HB_EN

TX_EN_2V7

9E_VMODE

TEMP_SENSE_EN

SW_POS1

SW_POS2

SW_POS3

SW_POS4

HAR_MB_RX_SLOT

SER_RX_FRAME

SER_RX_CLK

SER_RX_DATA

HAR_MB_RX_ACQ

SW_Q

SW_QX

GSM_PA_VBA

9E_VREFDET

MB_RX_EN

WB_RX_EN

MB_TRK_CLK

WB_DCOC_QX

WB_DCOC_Q

WB_DCOC_I

WB_DCOC_IX

WB_Q

WB_QX

WB_I

WB_IX

MB_I

MB_QX

MB_Q

MB_IX

WB_CMODE

WB_AGC3

WB_AGC1

PAR_TX_FRAME

PAR_TX_DATA(0)

PAR_TX_DATA(7)

RESETB

MB_ASPI_DATA

PAR_RX_DATA(2)

PAR_RX_DATA(3)

PAR_RX_DATA(4)

PAR_RX_DATA(5)

PAR_RX_DATA(6)

PAR_RX_DATA(7)

PAR_RX_FRAME

MB_EXC_EN

HAR_SPIMB_CE

HAR_SPIWB_CE

SPIMB_CLK

SPIWB_CLK

SPIMB_DW

SPIWB_DW

SPIMB_DR

SPIWB_DR

MB_CKIH

PAR_TRX_CLK

STBY_MB

STBY_WB

9E_VDET

PAR_RX_DATA(7:2)

HAR_WB_RX_SLOT

HAR_MB_RX_ON

HAR_WB_RX_ACQ

HAR_WB_RX_ON

AOC_PWR_UP_DN

HAR_TX_PREKEY

HAR_TX_RAMP

HAR_TX_SLOT

WB_LNA_BYP

WB_TRK_CLK

MB_CM_IN

MB_ASPI_CLK

MB_ASPI_CE

WB_CKIH

SW_ASPI_DW

SW_ASPI_CLK

SW_ASPI_CE

8

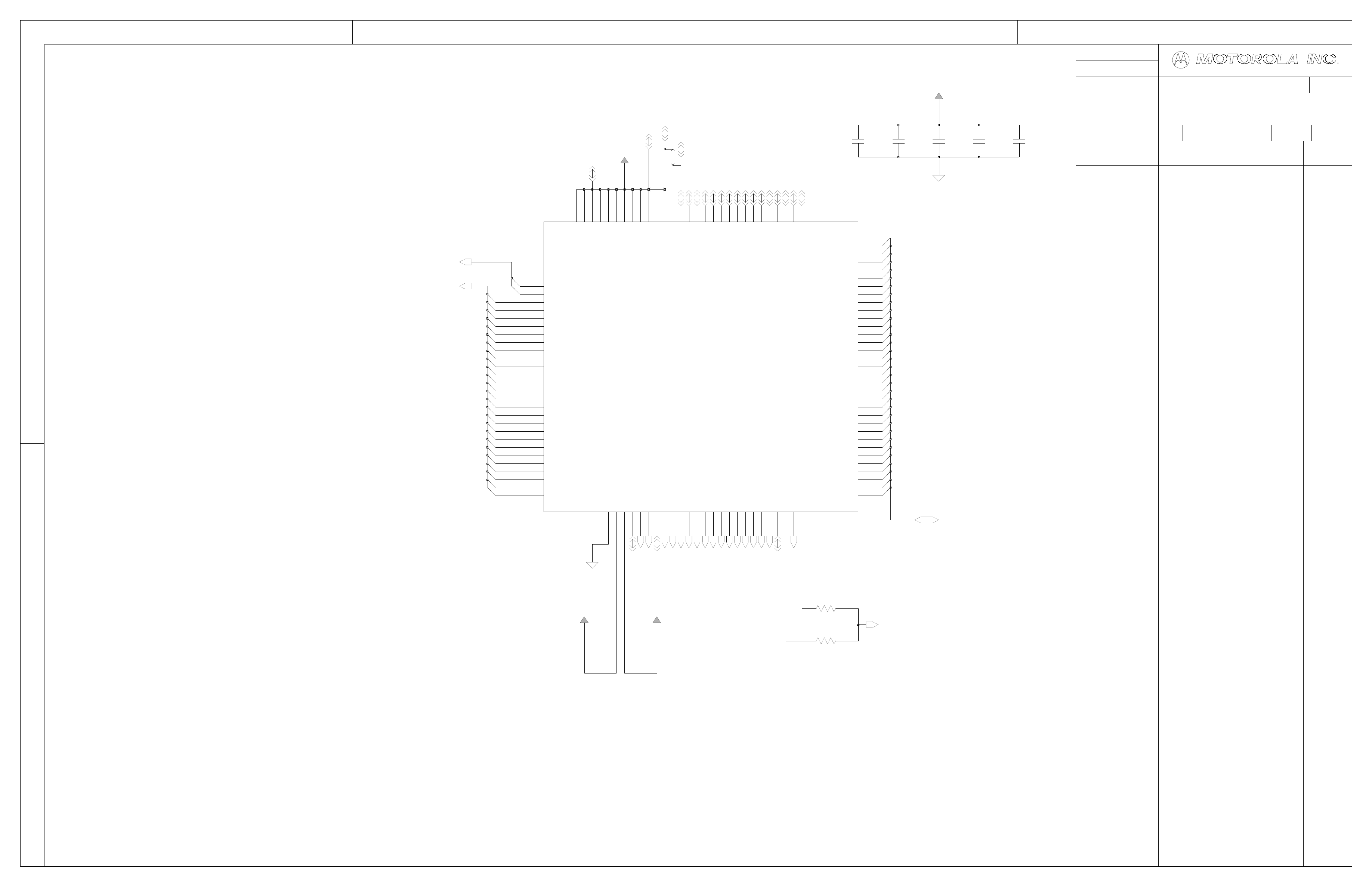

PRIM SYNC_CP_SUPPLY

ONE LIFE WB_RF_SUPPLY

PRIM SYNC 1.8 SUPPLY

6

TITLE

C975

7

DIFF 200 OHMS

Engineer

50 Ohms

50 Ohms

3

MFG CTRL CHK

1

Drawing Number

Size

Date Changed

B

E

8

2

TCXO SUPPLY

DOC CTRL CHK

C

2

Drawn by

C

R&D CHK

REV

DIFF 100 OHMS

Address

Time

DO NOT DELETE

D

3

BLUE MODULE

D

4

5

COMPANY NAME

5

QA CHK

DIFF 100 OHMS

Dif. 200 Ohms

City

TPs for test_1 & test_2

Changed by

A

E

4

1

B

Sheet

of

50 Ohms

ccl003

Thursday, April 10, 2003

9:50:27 am

Chris Leyh

Chris Leyh

1.0

Rx/Syn

D

6

7

A

ORG. Blue Module

ONE LIFE 1.8 SUPPLY

C9135

VRF_HV_5V

0

.01uF

C9126

R912

GND

.01uF

E9

WB_VCC_RF

B7

WB_VCC_VCO

G9

WB_VCO_EN

F8

C9134

.01uF

WB_SF_OUT

WB_SF_REF

G8

WB_SPI_CE

F9

WB_SPI_CLK

J10

WB_SPI_DATA_IN

J9

D11

WB_TEST_1

WB_TEST_2

C11

WB_TRK_CLK

L10

WB_VCC_BB

F10

WB_DCOC_I_NEG

G12

H12

WB_DCOC_I_POS

WB_DCOC_Q_NEG

F11

WB_DCOC_Q_POS

F12

B9

WB_LNA_BYP

WB_RX_EN

D6

WB_SF_EN

F7

G7

WB_AGC_1

C10

WB_AGC_2

C9

WB_AGC_3

B10

WB_AGC_4

B11

WB_BB_I_NEG

K11

WB_BB_I_POS

K10

WB_BB_Q_NEG

J12

WB_BB_Q_POS

J11

WB_CM_IN

K8

UMTS_WB_RX_NEG_IN

D12

C12

UMTS_WB_RX_POS_IN

VCC_MB_EXC

F4

VCC_MB_VCO

E6

VCC_SPI_TRK

G10

VCC_SYN

H5

WB_AGC_0

D10

SYN_SPI_MB_CE

L6

SYN_SPI_MB_CLK

K4

SYN_SPI_MB_DATA

K5

SYN_SPI_WB_CE

J1

SYN_VCC_CP

J7

SYN_VCC_LOGIC

J5

SYN_VCC_REF_BUF

K7

SYN_WB_STBY

L7

TCXO_VCC_OUT

B6

MB_VCO_EN

H3

A10

PCS_MB_RX_NEG_IN

PCS_MB_RX_POS_IN

A9

SPI_TRK_VDD

D3

SYN_MB_STBY

J6

SYN_REF_OSC_IN

L8

SYN_RESET

K6

MB_SD_TX

J4

MB_SF_OUT

F5

MB_SF_REF

E5

MB_TEST_1

C5

MB_TEST_2

C2

MB_TRK_CLK

E2

MB_TX_CLK

K2

MB_TX_RAMP

J3

MB_VCC_RF

B3

MB_BB_Q_NEG

C4

C3

MB_BB_Q_POS

MB_CM_IN

B2

MB_EXC_EN

E1

MB_HB_OUT

F1

MB_LB_OUT

D1

MB_RX_EN

C6

GND6

A12

GND7

B1

GND8

B5

GND9

B8

MB_ASPI_CE

D4

MB_ASPI_CLK

E3

MB_ASPI_DATA

D2

MB_BB_I_NEG

B4

MB_BB_I_POS

K9

GND46

K12

L1

GND47

GND48

L2

GND49

L9

GND5

A11

GND50

L11

GND51

L12

GND38

H7

GND39

H8

GND4

A8

GND40

H9

GND41

H10

GND42

H11

GND43

J8

GND44

K1

GND45

G4

GND31

G5

G6

GND32

GND33

G11

GND34

H1

GND35

H2

GND36

H4

GND37

H6

GND23

E12

GND24

F2

GND25

F3

GND26

F6

GND27

G1

GND28

G2

GND29

G3

GND3

A5

GND30

D8

GND17

D9

E4

GND18

GND19

E7

GND2

A2

GND20

E8

GND21

E10

GND22

E11

EGSM_MB_RX_POS_IN

A3

GND1

A1

GND10

B12

GND11

C1

GND12

C7

GND13

C8

GND14

D5

GND15

D7

GND16

L3

CLK_EN

J2

L4

CLK_GPS_OUT

CLK_NC_OUT

K3

CLK_OUT

L5

DCS_MB_RX_NEG_IN

A7

DCS_MB_RX_POS_IN

A6

EGSM_MB_RX_NEG_IN

A4

GND

17N03

U900

CLK_BT_OUT

3

GND3

5

2

INPUT

OUTPUT1

4

6

OUTPUT2

GND

GND

GND

FL005

SAFSD2G14

GND1

1

GND2

1

GND

.01uF

C9133DNP

SHORT

E901

2

GND

1.2pF

C012DNP

1.5pF

C013DNP

GND

GND

GND

GND

GND

.01uF

C9132

GND

VRF_RX_2.775V

R906

3

PORT2

4

PORT3

0

HHM1526

T2

2 CT

5

GND1

6 NC

1 PORT1

HHM1526

2 CT

5

GND1

6 NC

1 PORT1

3

PORT2

4

PORT3

T3

0

R008

0

0

R006

R007

NC

VLVIO_1.875V

GND

E900

SHORT

2

1

TP915

TEST_POINT

1

C011DNP

C901

1.5pF

R901

4.7uF

TP914

TEST_POINT

1

0

TEST_POINT

TP908

1

R7925

0

C902

4.7uF

TP907

1

GND

GND

TEST_POINT

1

C9138

10uF

TP909

TEST_POINT

1

VRF_RX_2.775V

TEST_POINT

TP913

0

R909DNP

R904

R910

GND

0

.01uF

0

GND

V1

C9125

NC

VRF_REF_2.775V

GND

2 CT

GND1 5

6 NC

1 PORT1

3

PORT2

4

PORT3

T1

HHM1515

TEST_POINT

1

0.1uF

C903

TP912

GND

0

R907

NC

GND

1

R903

0

C904

NC

TP910

TEST_POINT

TP911

1

2.2uF

0

R911DNP

GND

TEST_POINT

0

R908

MB_ASPI_CLK

39pF

C9139

MB_GSM900_IN

MB_DCS_IN

WB_UMTS_IN

SPI_TRK_VDD

SPI_TRK_VDD

SPIWB_DW

MB_PCS_IN

MB_TRK_CLK

MB_IX

MB_I

MB_Q

MB_QX

UMTS_RX_POS

MB_GSM900_IN_POS

MB_GSM900_IN_NEG

MB_DCS_IN_POS

MB_DCS_IN_NEG

MB_PCS_IN_NEG

MB_PCS_IN_POS

MB_RX_EN

SPIMB_DW

PS_SPIWB_CE

PS_SPIMB_CE

SPIMB_CLK

RESETB

STBY_WB

STBY_MB

TCXO_EN

TCXO_IN

PS_CLK_EN

PS_CLK_OUT

PS_CLK_ALT

MB_RX_VCO_EN

MB_CM_IN

SW_VCO_FB

SW_VCO_FB_X

SW_CP

UMTS_RX_NEG

SER_TX_CLK

SER_TX_DATA

MB_LB_RF_OUT

MB_HB_RF_OUT

MB_EXC_EN

MB_ASPI_DATA

MB_ASPI_CE

MB_GSM900_IN_POS

MB_GSM900_IN_NEG

MB_DCS_IN_POS

MB_DCS_IN_NEG

UMTS_RX_NEG

WB_AGC4

WB_DCOC_I

WB_DCOC_IX

WB_DCOC_Q

WB_DCOC_QX

WB_CMODE

WB_Q

WB_I

WB_IX

WB_TRK_CLK

WB_SPIWB_CE

WB_SOS1

WB_SOS2

WB_DCS_IN

XTAL_OUT

WB_PCS_IN

MB_GSM850_IN

PS_CLK

SPIWB_CLK

WB_LNA_BYP

WB_VCO_SF_EN

WB_RX_EN

WB_QX

WB_AGC3

WB_AGC2

WB_AGC1

WB_AGC0

UMTS_RX_POS

MB_PCS_IN_POS

MB_PCS_IN_NEG

DMCS

7

R&D CHK

A

50 Ohms

50 Ohms

4

REV

Drawing Number

2

Size

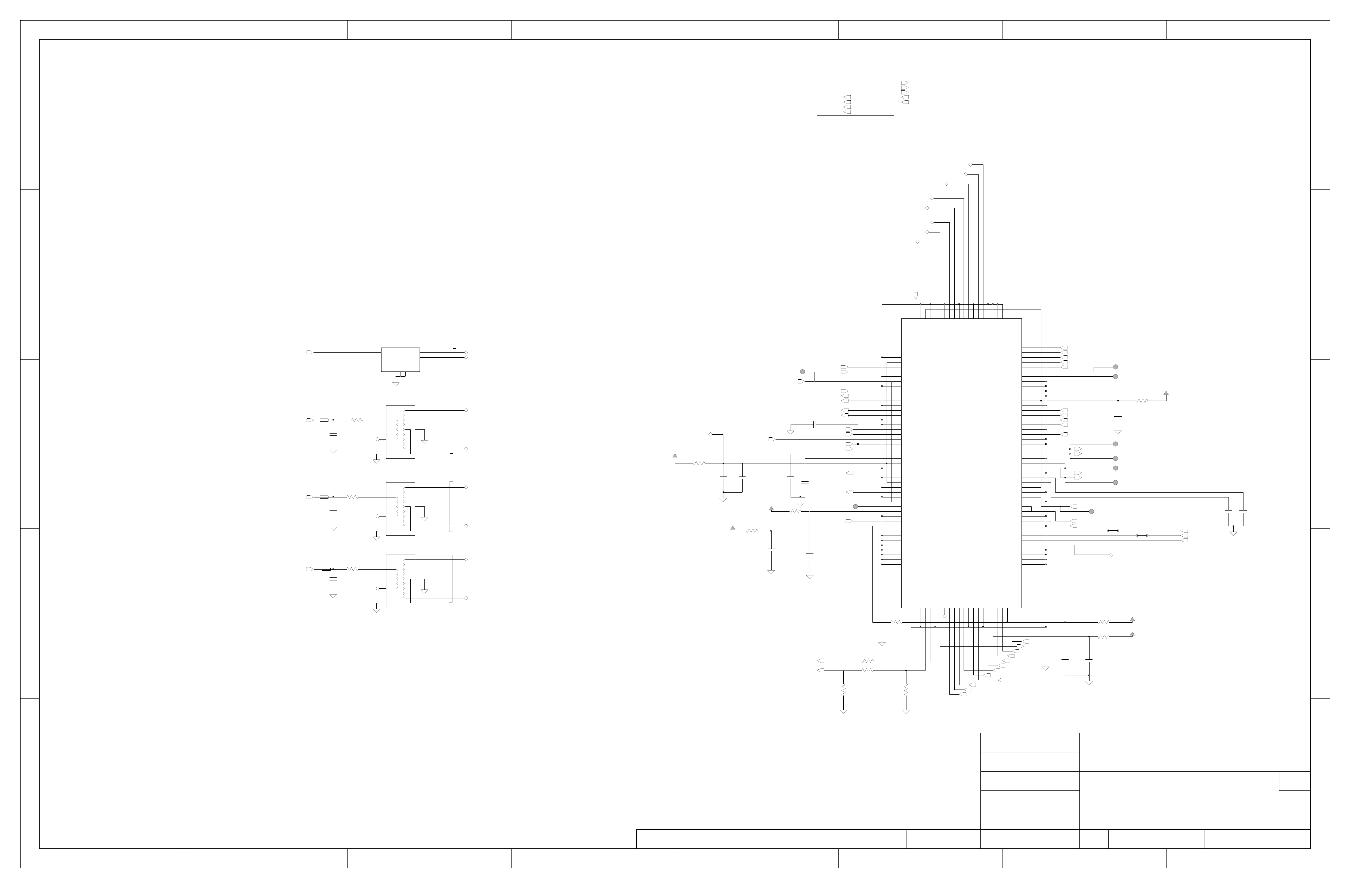

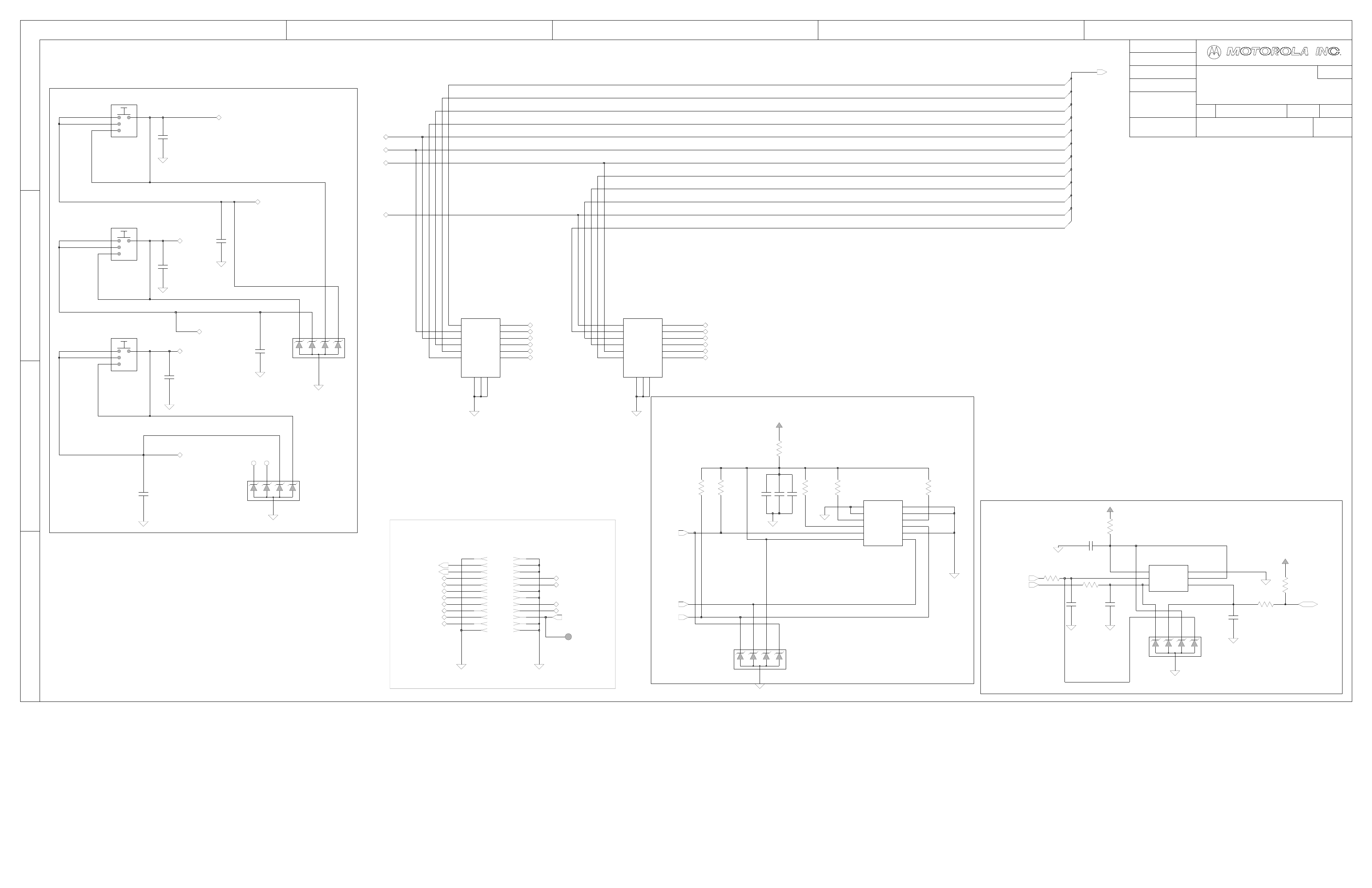

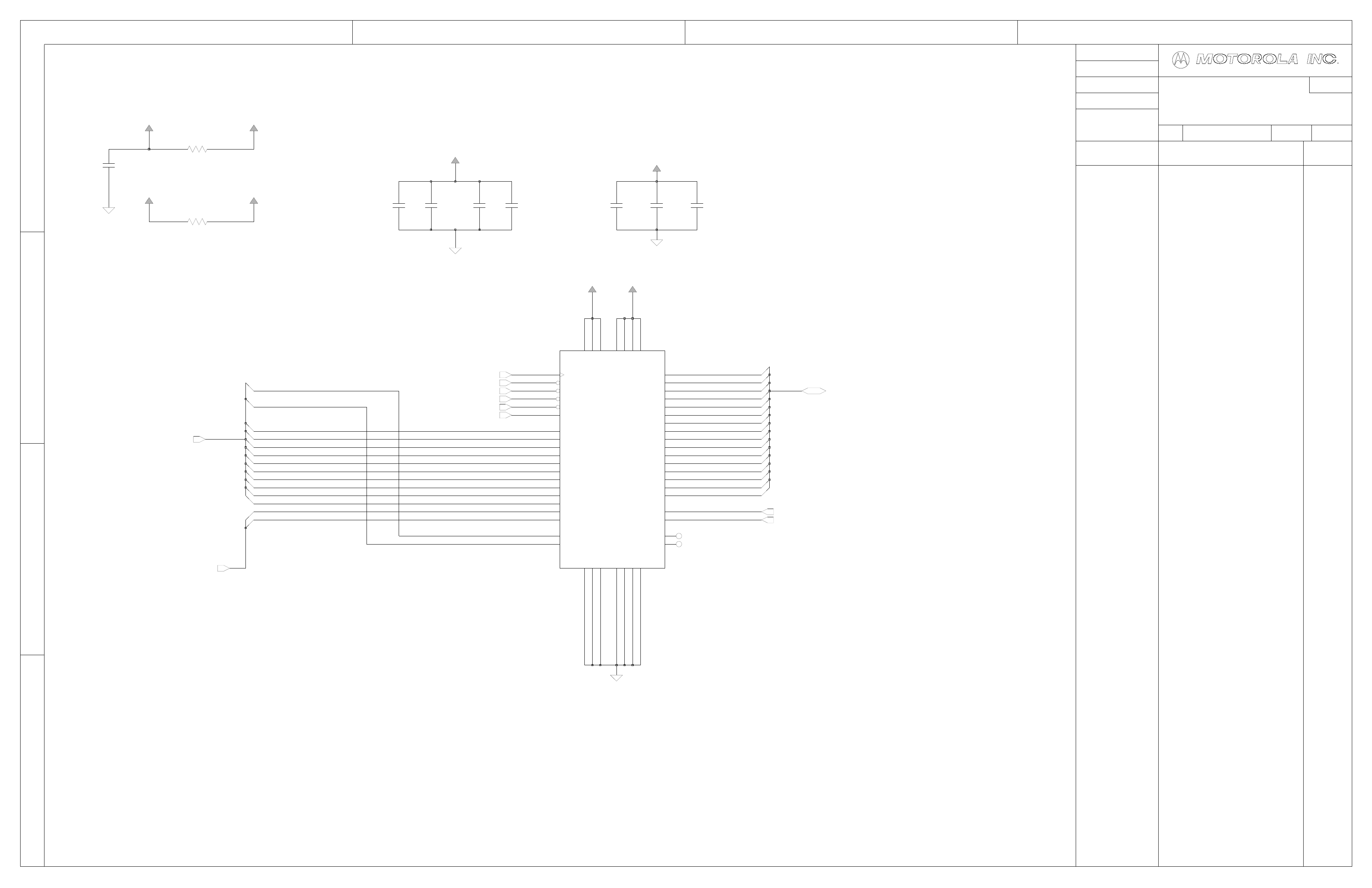

GSM/DCS/PCS and WCDMA Transmitters

Date Changed

50 Ohms

B

5

50 Ohms

Time

WCDMA PA REF # (850 - 879)

B

50 Ohms

4

50 Ohms

7

50 Ohms

Sheet

GSM/DCS/PCS PA REF# ( 800 - 829)

8

8

TX_RATTLER _MODULE

2

6

Motorola Confidential Proprietary

DCS/PCS TX

TITLE

6

D

Engineer

1

Temp Sensor REF # (880 - 889)

MFG CTRL CHK

Libertyville

GSM TX

of

E

5

DOC CTRL CHK

CLOSE TO MMM5092

3

C975

1

C

RATTLER

C

Drawn by

E

D

A

50 Ohms

QA CHK

MOTOROLA INC.

50 Ohms

600 North US Highway 45

3

50 Ohms

TRANSMITTER

D

wlpm11

Thursday, April 24, 2003

1:46:09 pm

wlpm11

wlpm11

Changed by

1pF

C818DNP

GND

R818DNP

0

18

VREF

1

R403

0

8

NC3

12

RFIN

20

RFOUT

10

VBA1

3

VBA2

4

VCC1

17

VCC2

15

VIB

7

GND4

9

GND5

11

GND6

13

GND7

16

GND_FLAG

22

LOADSW

6

NC1

5

NC2

U850

MMM5092

5189552N01

CP_OUT

14

ENABLE

2

GND1

19

GND2

21

GND3

1000pF

C7916

E405

SHORT

2

1

GND

R859DNP

GND

BATT+

0

R858DNP

0

10pF

C857

C401

4.7uF

SHORT

E400

2

1

LM20

5109768D08

2

GND0

5

GND1

1

NC

3

VOUT

VPOS

4

GND

R821DNP

GND

GND

U880

GND

120

R402

0

0

R805

B+

C815DNP

10pF

C7906DNP

10pF

BATT+

1.0uF

C805

39pF

C806

C9136

.01uF

GND

R820DNP

0

GND

12pF

VRF_PA_2.775V

.01uF

C882

C858

R812

4.7uF

0

1pF

C800

100

R810

C817DNP

120

R819DNP

E409

NC

39pF

C854

GND

C807DNP

10pF

VRF_PA_2.775V

C801

E408

39pF

E403

IDCTR

2

1

BATT+

NC

GND

82.0nH

GND

GND

GND

VRF_TX_2.775V

GND

NC

GND

4.7uF

C802

10pF

C859DNP

10pF

C7907DNP

10pF

C814

VRF_TX_2.775V

R882

470

C856

.01uF

39

BATT+

GND

GND

GND

GND

R404

1.0uF

C803

E412

GND

0

R851

R802

0

GND

GND

0

R801

C881

.01uF

GND

C804

L811

GND

GND

GND

39pF

33nH

2

1

1.0nH

0

R830DNP

IDCTR

L7925

C808DNP

10pF

GND

GND

GND

GND

GND

0.5pF

C855

RES

R411

GND

GND

SHORT

E402

2

1

0

GND

E801

SHORT

2

1

GND

8.2pF

C860

C9137

.01uF

GND

C852

1.0uF

10pF

C816DNP

4.7uF

GND

GND

10pF

C850

E406

C810

E407

31

VREF

C809

10pF

22

VCC3_4

27

VCCBIAS

VDET

14

13

VDETREF

15

VEND

28

VENH

34

VENL

3

VMODE

36

SIG_GND2

VBA1

1

VBA2

2

5

VCC1_2_1

24

VCC1_2_2

7

VCC3_1

8

VCC3_2

21

VCC3_3

19

GND7

20

GND8

GND9

23

RFIN1

33

29

RFIN2

11

RFOUT1

17

RFOUT2

35

SIG_GND1

26

GND11

30

GND12

32

GND13

6

GND2

9

GND3

12

GND4

16

GND5

18

GND6

5188220Y02

20Y02

U800

10

CPIN

4

GND1

25

GND10

GND

E401

SDI

2

TX_EN

15

VCC_DIG

26

VCC_MAIN

4

VCC_VCO

32

VCO_EN

23

VGC

16

BATT+

GND9

14

I_M_NEG

20

I_P_POS

21

Q_M_NEG

18

Q_P_POS

19

REF

24

RF_OUT

6

SCK

1

GND16

31

GND2

7

GND3

8

GND4

9

GND5

10

GND6

11

GND7

12

GND8

13

CTGND

33

GND1

5

GND10

17

GND11

22

GND12

27

GND13

28

GND14

29

GND15

30

U401

50M21

5188450M21

BIAS_STATE

25

CEB

3

2

1

10pF

C402DNP

C851

SHORT

E9128

GND

BATT+

1.0uF

6800pF

C7917DNP

GND

GND

82.0nH

L401

10uF

C813

VRF_PA_2.775V

GND

10uF

C812

GND

GND

GND

C853

R803DNP

0

1.0uF

NC

.01uF

C101

WB_TX_OUT

VENL

VENH

VEND

DCS_PCS_TX_OUT

GSM_TX_OUT

REF

TX_EN

VCO_EN

BB_QX

BB_Q

BB_IX

BB_I

VMODE

9E_VDET

9E_VREFDET

GSM_PA_VBA

WB_PA_VBA1

TEMP_SENSE_EN

VGC

SPI_ASPI_CE

SPI_ASPI_CLK

SPI_ASPI_DW

RF_IN_DCS_PCS

RF_IN_GSM

WB_PA_ENABLE

WB_PA_LOAD_SW

TEMP_SENSE

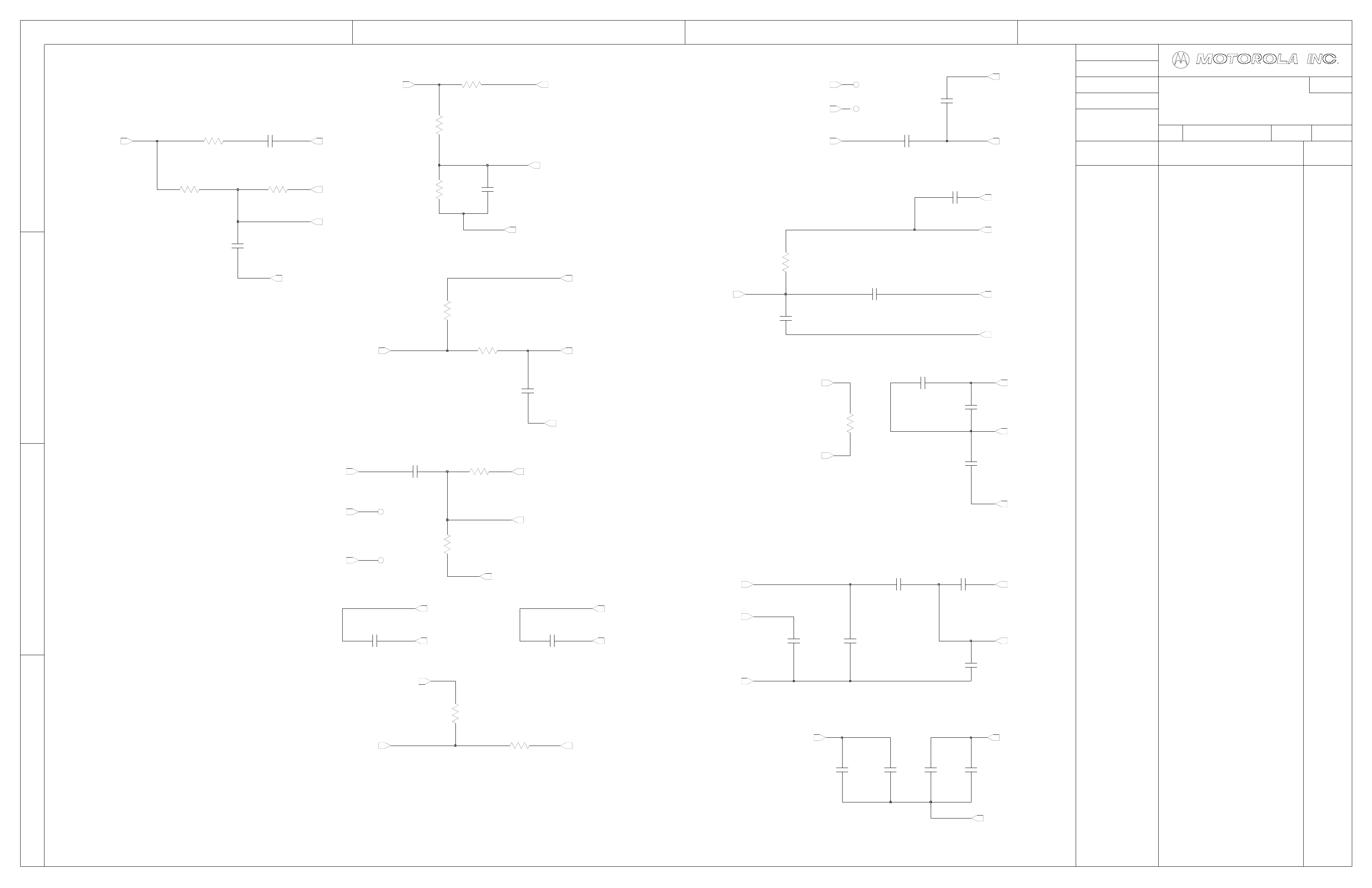

A

case 0603

50 Ohms

DOC CTRL CHK

QA CHK

Motorola Confidential Proprietary

Drawing Number

MFG CTRL CHK

R&D CHK

2

MOTOROLA INC.

Sheet

C

C975

50 Ohms

50 Ohms

4

5

B

8

REV 1

6

50 Ohms

50 Ohms

50 Ohms

D

50 Ohms

7

4

NEAR FL001

7

1

Date Changed

Time

50 Ohms

50 Ohms

600 North US Highway 45

LO02 NEAR FL002

Engineer

Drawn by

NEAR FL001

Changed by

C

50 Ohms

1

50 Ohms

50 Ohms

of

Front End Module REF # (000 - 099)

50 Ohms

6

E

E

5

8

A

TITLE

Size

3

ccl003

Thursday, April 17, 2003

8:25:56 am

Chris Leyh

ccl003

Rev. 1

Quad Band Front End Module

D

FRONT END MODULE

B

D

3

Libertyville

2

To be placed closed to POG

3.6pF

VRF_RX_2.775V

2.7nH

L005

C7934

680nH

L001DNP

0

R004

GND

C9131

10pF

19

PCS_RX

20

V1

5

V2

4

V3

3

2

V4

11

WCDMA_TX

GND

GND_26

GND_27

38

GND_3

7

GND_4

9

GND_5

10

GND_6

12

GND_7

14

GND_8

17

GND_9

GND_19

GND_2

6

GND_20

31

32

GND_21

GND_22

33

34

GND_23

35

GND_24

GND_25

36

37

22

GND_12

23

24

GND_13

GND_14

25

GND_15

26

27

GND_16

GND_17

28

29

GND_18

30

4889729N03

8

ANTENNA

DCS_PCS_TX

13

DCS_RX

18

EGSM_RX

16

EGSM_TX

15

GND_1

1

GND_10

21

GND_11

GND1

GND2

IN

OUT

U002

FEM3203_ES6D

0987378K01

SWITCH

N001

IN

1

OUT

2

R002

3.3K

GND

9109674L20

S0351

FL002

GND1

G1

GND2

G2

L003

4.7nH

GND

74L17

FL004

3

GND

IN

1

OUT

2

4.7nH

L002

C001

10pF

GND

GND

33pF

C005

C010

1pF

GND

9109674L21

CF61A5601

FL003

GND

1

IN

2

OUT

3

C008

GND

J403

10pF

C019

GND

GND

GND

GND

39pF

C018

39pF

39pF

C017

39pF

C016

D7905

GND

10pF

C9130

C015

39pF

GND

C002DNP

0.75pF

GND

1nH

L009DNP

10K

R015

J402

0.8pF

C009DNP

GND

C006DNP

10uF

GND

GND

1.0nH

L014

3

HB_LNA_OUT

4

HB_RBIAS

11

LB_LNA_E_GND

10

LB_LNA_IN

1

LB_LNA_OUT

12

LB_RBIAS

VCC

2

GND

U001

MC13820

9

BAND

13

CTGND

7

ENABLE

8

GAIN

5

HB_LNA_E_GND

6

HB_LNA_IN

10K

GND

R7923

R003

C007

.01uF

VLVIO_1.875V

GND

2K

0.3pF

C014

GND

SW_POS4

SW_POS3

SW_POS2

SW_POS1

TX_RX_ERROR

ANT_SW_RX

MBC_EN0

WB_RX_OUT

MB_DCS_OUT

MB_GSM_OUT

MB_LB_RF_IN

MB_PCS_OUT

MB_HB_RF_IN

WB_TX_IN

MBC_EN1

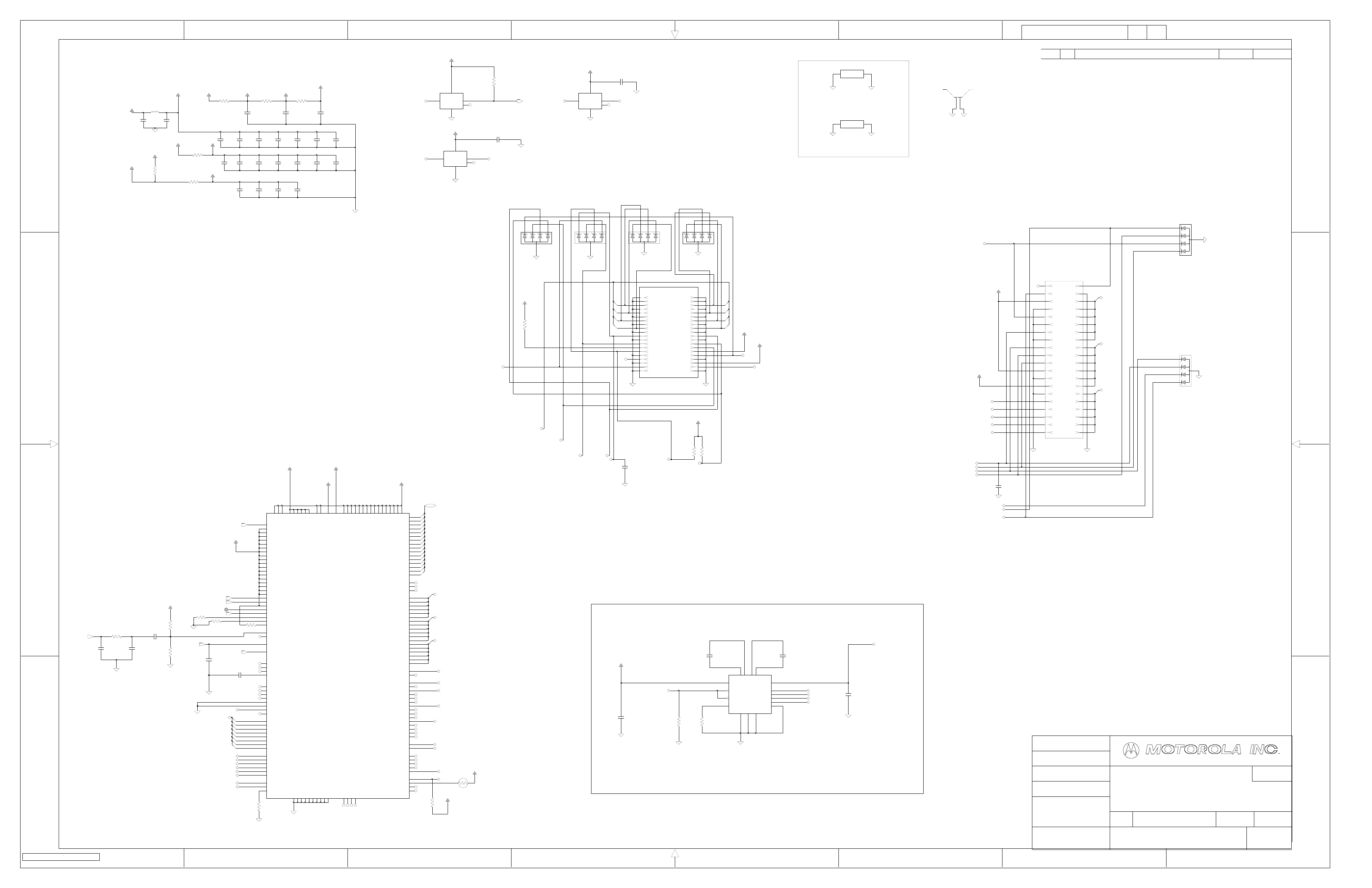

CORE LOGIC BLOCK

POG

Memories

Display & Imager Interfaces

Triflash-R

USIM

LED Lighting

Keypad Connector

Misc Connectors

CE Bus Connector

PCAP2 (Power/Audio)

MFG CTRL CHK:

QA CHK:

REV:

Drawing Number:

Page:

TITLE:

Size:

Engineer:

Drawn by:

R&D CHK:

DOC CTRL CHK:

Of:

Changed by:

Time:

Date:

Fabrizio Filizzola

Fabrizio Filizzola

January 26, 2004

C975

11x17

MOTOROLA CONFIDENTIAL PROPRIETARY

1

2

3

4

D

C

B

Baseband Top Level

A

NC

NC

NC

GPU_IND_ADDR

GPU_INTb

GPU_OEb

GPU_RESETb

PS_CLK

0.10uF

C1161DNP

USIM_IO

USIM_RST

VUSIMC_EN

WATCHDOG

WB_SPIWB_CE

WB_SPI_CLK

WB_SPI_MISO

WB_SPI_MOSI

WB_VCO_SF_EN

DATA[15:0]

GPU_CSb

GPU_EBHb

GPU_EBLb

RXD.VMIN

STBY_MB

STBY_WB

STEREO_CLK

STEREO_FS

STEREO_TX

SWB+_EN

TXD.VPOUT

TX_RAMP

TX_RX_ERROR

USB_DETECT

USB_TXENb

USB_VMOUT

USB_VPIN

USER_OFF

USIM_CLK

MMC_CLK

MMC_CMD

MMC_DAT

MUTEb

MUXCTL

OPT1

OPT2

PCAP_CLK_IN

PCAP_CS

PCAP_INT

PCAP_RESETb

PS_CLK_ENb

PS_SPIMB_CE

PS_SPIWB_CE

RTSb.XRXD

HAR_MB_RX_SLOT

HAR_RESETb

HAR_SPIMB_CE

HAR_SPIWB_CE

HAR_TX_PREKEY

HAR_TX_SLOT

HAR_WB_RX_ACQ

HAR_WB_RX_ON

HAR_WB_RX_SLOT

HKSW

KEY[0:15]

LOGIC_SENSE

MB_RX_VCO_EN

MB_SPI_CLK

MB_SPI_MISO

MB_SPI_MOSI

DMCS

DSEL0

DSEL1

DSEL2

FLASH_GPU_OEb

FLASH_RWb_GPU_EBHb

GPS_CTSb

GPS_RX

GPS_TX

GPU_CSb

GPU_EBLb

GPU_IND_ADDR

GPU_INTb

GPU_RESETb

GPU_RWb

HAR_MB_RX_ACQ

HAR_MB_RX_ON

BB_SPI_CLK

BB_SPI_MISO

BB_SPI_MOSI

BCLKR

BCLKX

BDR

BDX

BFSR

BLUETOOTH_INTb

BLUE_CTSb

BLUE_RTSb

BLUE_RX

BLUE_TX

BLUE_WAKEb

CLK_32_768K

DATA[15:0]

AOC_PWR_UP

ASAP_CLK

ASAP_FS

ASAP_RX

ASAP_TX

BATT_DETB

BATT_FDBK

BATT_FDBK_SW

BATT_IO

BBIF_CLK

BBIF_RX[7:2]

BBIF_RX_FRAME

BBIF_TX[7:0]

BBIF_TX_FRAME

BB_CLK_13M

BB_CLK_15_36M

R1160

0

VLVIO_1.875V

NC

GND

0

R1167

NC

NC

NC

NC

NC

PS_CLK

RTSb.XRXD

RXD.VMIN

STEREO_CLK

STEREO_FS

STEREO_TX

TEMP_SENSE

TXD.VPOUT

USB_DETECT

USB_TXENb

USB_VMOUT

USB_VPIN

USER_OFF

VSIMC_EN

WATCHDOG

BATT_IO

BB_SPI_CLK

BB_SPI_MISO

BB_SPI_MOSI

BL_FB

BL_KPD_ON

CLK_32_768K

D+

D-

LOGIC_SENSE

MUXCTL

ON_OFF_ENDb

PCAP_CLK_IN

PCAP_CS

PCAP_INT

PCAP_RESETb

AD_TRIG

ASAP_CLK

ASAP_FS

ASAP_RX

ASAP_TX

AUDIO_IN

AUDIO_OUT

BATT_DETb

BATT_FDBK

BATT_FDBK_SW

NC

AUDIO_IN

AUDIO_OUT

BATT_FDBK

D+

D-

DSEL0

DSEL1

DSEL2

HKSW

MUTEb

OPT1

OPT2

SWB+_EN

U1161DNP

NL17SZ00

2

A

1

B

3

GND

5

VCC

4

Y

BL_KPD_ON

KEY[0:15]

MMC_CLK

MMC_CMD

MMC_DAT

ON_OFF_ENDb

USIM_CLK

USIM_IO

USIM_RST

GND

STBY_MB

STBY_MB

STBY_WB

STBY_WB

STEREO_CLK

STEREO_FS

STEREO_TX

SWB+_EN

TXD.VPOUT

USB_DETECT

USB_TXENb

USB_VMOUT

USB_VPIN

USER_OFF

VSIMC_EN

WATCHDOG

GPS_CTSb

PS_CLK_EN

PS_CLK_EN

HAR_TX_PREKEY

TX_RX_ERROR

BL_FB

BLUETOOTH_WAKEb

CLK_32_768K

DSEL0

DSEL1

DSEL2

GPS_RX

GPS_TX

HKSW

LOGIC_SENSE

MUTEb

MUXCTL

OPT1

OPT2

PCAP_CLK_IN

PCAP_CS

PCAP_INT

PCAP_RESETb

RTSb_XRXD

RXD.VMIN

GPU_IND_ADDR

DATA[15:0]

BL_FB

BB_CLK_13M

BB_CLK_15_36M

PS_CLK

PS_CLK

BATT_DETb

BATT_FDBK

BATT_FDBK

BATT_FDBK_SW

BATT_IO

BB_SPI_CLK

BB_SPI_MISO

BB_SPI_MOSI

BLUETOOTH_INTb

BLUE_CTSb

BLUE_RTSb

BLUE_RX

BLUE_TX

BBIF_RX_FRM

KEY[0:15]

HAR_SPIWB_CE

TX_RAMP

PS_SPIWB_CE

HAR_MB_RX_ACQ

HAR_MB_RX_ON

HAR_MB_RX_SLOT

PS_SPIMB_CE

HAR_SPIMB_CE

WB_VCO_SF_EN

MB_RX_VCO_EN

BDR

MB_SPI_CLK

MB_SPI_MISO

MB_SPI_MOSI

WB_SPI_CLK

WB_SPI_MISO

WB_SPI_MOSI

MMC_DAT

MMC_CMD

MMC_CLK

ON_OFF_ENDb

DMCS

HAR_RESETb

GPU_CSb

GPU_EBLb

GPU_RESETb

GPU_INTb

GPU_OEb

GPU_EBHb

HAR_WB_RX_SLOT

BCLKR

BBIF_TX[7:0]

BBIF_CLK

AOC_PWR_UP

BBIF_TX_FRM

BCLKX

BDX

BFSR

WB_SPIWB_CE

HAR_WB_RX_ON

HAR_TX_SLOT

HAR_WB_RX_ACQ

BBIF_RX[7:2]

USIM_RST

USIM_IO

USIM_CLK

BL_KPD_ON

AUDIO_IN

TEMP_SENSE

AUDIO_OUT

D+

D-

MFG CTRL CHK:

QA CHK:

REV:

Drawing Number:

Page:

TITLE:

Size:

Engineer:

Drawn by:

R&D CHK:

DOC CTRL CHK:

Of:

Changed by:

Time:

Date:

3

Camera

SIM Card Board Connector

Keypad

B

Triflash-R Connector

Connector

5

4

MOTOROLA CONFIDENTIAL PROPRIETARY

2

D

1

A

Side Keys

C

Vol Down

3

Fabrizio filizzola

Fabrizio filizzola

Fabrizio filizzola

January 27, 2004

1

1

1

4 1 3 A

C975

Misc Connectors

11x21

Vol Up

SWITCH

S2

4

1

2

1

R3901

75K

CR3900

2

5

4

3

10K

GND

GND

VOLTAGE

R3904

10K

R3905

GND

18

1

PIN1

2

PIN2

3

PIN3

4

PIN4

PIN5

5

6

PIN6

21

J5500

2

3

C9119

33pF

6

SWITCH

SW5130

4

1

0.10uF

C3910

GND

0

VSIM_CARD

NC

R5503

GND

C5501DNP

10pF

S1

SWITCH

4

1

2

3

3

5

2

A1

C1

A3

C3

GND

7

15KV

VR5001

C9119

4

1

33pF

GND

0

R5505

C5503

10pF

R5502

0

16

6

PIN5

5

PIN6

6

7

PIN7

PIN8

8

PIN9

9

GND

PIN1

1

10

PIN10

11

PIN11

PIN12

12

2

PIN2

3

PIN3

PIN4

4

33pF

3989655N02

J3901

33pF

C9121

C9121

9

GND

1.0uF

C3911DNP

GND2

GND3

B3

10pF

C5505DNP

FLTR6

A6

FLTR1

C1

FLTR2

C2

FLTR3

C3

FLTR4

C4

FLTR5

C5

FLTR6

C6

GND1

B1

B2

FL4302

CSPEMI306AG

FLTR1

A1

FLTR2

A2

FLTR3

A3

FLTR4

A4

FLTR5

A5

10K

10K

R3900

GND1

B1

GND2

B2

GND3

B3

7

11

R3903

FLTR5

A5

FLTR6

A6

FLTR1

C1

C2

FLTR2

FLTR3

C3

FLTR4

C4

FLTR5

C5

FLTR6

C6

FL4301

CSPEMI306AG

FLTR1

A1

FLTR2

A2

FLTR3

A3

FLTR4

A4

22

20

GND

GND

23

GND

5

GND

24

19

2

5

4

3

1

GND

GND

GND

VOLTAGE

CR5500

GND

GND

2

NC

3

17

0

C9120

33pF

14

J5100

13

VMMC_2.775V

10

C9120

8

1

GND

GND

33pF

12

TP5251

TEST_POINT

VR5002

15KV

11

10

8

1

9

C3906

33pF

GND

GND

R5504

0

R5501

5.6K

15

VSIM_CARD

C5502DNP

4

0

R3902

VSIM_CARD_1

VSIM_CARD_1

KEY3

KEY0

KEY[3]

KEY[0]

VMMC_2.775V_1

10pF

KEY5

KEY[4]

KEY[4]

KEY[5]

KEY[5]

KEY6

KEY7

KEY8

KEY9

KEY10

KEY11

KEY[6]

KEY[6]

KEY[9]

KEY[10]

KEY[10]

KEY[11]

KEY[10]

KEY[6]

KEY[10]

KEY[5]

MMC_DAT

MMC_CLK

MMC_CMD

USIM_RST_1

USIM_CLK_1

USIM_IO_1

USIM_RST

USIM_CLK

USIM_IO

KEY[10]

KEY7

KEY8

KEY9

KEY11

KEY10

KEY0

KEY5

KEY6

KEY4

KEY2

KEY1

KEY3

ON_OFF_ENDb

BL_FB

BL_KPD_ON

KEY[0:15]

KEY[8]

KEY[7]

KEY[2]

KEY[1]

KEY[4]

KEY1

KEY2

KEY4

MFG CTRL CHK:

QA CHK:

REV:

Drawing Number:

Page:

TITLE:

Size:

Engineer:

Drawn by:

R&D CHK:

DOC CTRL CHK:

Of:

Changed by:

Time:

Date:

MUTEb / FS / DCD

CE Connector (0987636K06)

OPTION2

C

SWB+

Accessory Connector

1

D- / RXD / TDI

DSEL1 / FM_CLOCK / SRDA / DTR / TMS

DSEL0 / FM_EN / STDA / DSR / TRST_B

2

B3

GND3

NC

AUDIO_IN

3

AUDIO_OUT / 12V Flash / 8V JTAG

4

EXT_B+

F.Filizzola

D

BATT_FDBK

CE Accessory Connector

January 30th, 2004

OPTION1

Mark Melone

D+ / TXD / TDO

DSEL2 / SCK / RI / TCK

USB_PWR / IGN / SEND_END / RTS / RESET_IN

B

C975

MOTOROLA CONFIDENTIAL PROPRIETARY

A

HKSW / FM_DATA / CTS / DE_B

FLTR1

C1

C2

FLTR2

C3

FLTR3

C4

FLTR4

C5

FLTR5

FLTR6

C6

B1

GND1

B2

GND2

FLTR1

A1

A2

FLTR2

A3

FLTR3

A4

FLTR4

A5

FLTR5

FLTR6

A6

GND

CSPEMI306AG

U5000

C5002

2

1

GND

C5000

0.10uF

33pF

6

C5204

1.0uF

11

GND

12

17

3

14

GND2

5

NC

4

VIN

1

VOUT

6

NC

9

Q5001

17F58

ENABLE

3

GND1

2

20

NC

47K

GND

GND

NC

GND

R5001

19

RAW_EXT_B+

GND

16V

VR5003

B3

GND3

13

A4

FLTR3

A5

FLTR4

C2

FLTR1

C3

FLTR2

C4

FLTR3

C5

FLTR4

B1

GND1

B2

GND2

A1

ESD1

A6

ESD2

C1

ESD3

C6

ESD4

A2

FLTR1

A3

FLTR2

18

CSPEMI307AG

U5001

15

B+

R5000

100K

5

2409646M13

L4400

39nH

10

NC

NC

GND

J5000

1

16

8

GND

7

GND

GND

16V

VS5001

GND

2

4886193U03

USB_PWR

VS5002

5V

4813832M84

GND

GND

NC

4

VR5000

2

5

4

3

1

33pF

C5002

4

3

VOLTAGE

D-

D-

RAW_BATT_FDBK

BATT_FDBK

RAW_DSEL0

OPT2

DSEL1

DSEL0

AUDIO_OUT

BL_KPD_ON

BL_FB

RAW_OPT1

RAW_OPT2

RAW_DSEL1

SWB+_EN

OPT1

RAW_DSEL2

DSEL2

RAW_HKSW

SWB+

HKSW

AUDIO_IN

D+

D+

RAW_MUTEb

MUTEb

PCAP2

SYMBOL

Corner Balls

THE DRAWING ON THIS PRINT AND INFORMATION

MOTOROLA CONFIDENTTIAL PROPRIETARY

A1

SHALL NOT BE USED OR DISCUSSED IN WHOLE

ELECTRICAL ENGINEER

OR IN PART WITHOUT MOTOROLA’S CONSENT.

OF

C COPYRIGHT, MOTOROLA,

THIS DOES NOT IMPLY PUBLICATION

SIZE

CHANGED BY:

THEREWITH ARE PROPRIETARY TO MOTOROLA AND

MOTOROLA CONFIDENTTIAL PROPRIETARY

DWG NO

THE DRAWING ON THIS PRINT AND INFORMATION

SHALL NOT BE USED OR DISCUSSED IN WHOLE

SHEET

ORIGINALLY DESIGNED BY:

OR IN PART WITHOUT MOTOROLA’S CONSENT.

THEREWITH ARE PROPRIETARY TO MOTOROLA AND

CAGE CODE

TITLE

CAD FILE NAME

APPROVALS

DATE

REV

can be replaced by Q3970 Q3971 Q3973 Q3874

7

B

LI_CELL Socket

1

12

6

(SDRAM , Flash)

C

(PrimSyn PLL)

5

Descretes

D

A

(Harmony TX, SW2 TX, Sidekick, AlgaeMB TX)

(PrimSyn xtal+TCXO)

PCAP2

HEADSET JACK

(Harmony I/O )

Alert Speaker

F.Filizzola

G

3

4

10

B

Motorola Confidential Proprietary

(POG I/O, AlgaeMB SPI I/O, ATI LCD )

D

2

8

4

E

U3000

H

(Harmony RX, OneLifeWB RX, AlgaeMB RX)

11

Bokchain Koh

11

2

(POG LVIO, Memory I/O)

A

4809939C39 is a place holder for 4813973M75

6

5

F

E

9

Audio

F

1

NOTE: FET Q3960, Q3961,Q3963,Q3964

VHVIO_2.775V

GND

3

Earpiece Speaker

9

C975

H

Placeholder. Not actual value

(OneLifeWB SPI I/O, BT I/O, nVIDIA I/O)

(POG Core, nVIDIA Core)

F.Filizzola

(Imager DSP)

10

which are IRF6100

12

Connection have been changed taking into account the wrong geometry of the associated symbol

8

7

(Harmony Dig, SW2 Dig, PrimSyn Dig)

G

Power and Audio

Q3970

4803558C01

R7921

88.7

NC

NC

88.7

R7920

6.8uH

GND

GND

GND

R5100

10K

2485063F02

L3100

1

NC

EXT_B+

B+

D3100

4809653F07

TEST_POINT

J3000

GND

NC

4862830F01

Q3961DNP

4862830F01

GND

Q3960DNP

39nH

L4399

2409646M13

4862830F01

Q3963DNP

VLVIO_1.875V

NC

J4201

1

Q3964DNP

4862830F01

EXT_B+

TP5255

1

GND

GND

2

1

Q3971

4803558C01

GND

0

R3965

RES

0613952R66

NC2

RX_GND

SPKR+

SPKR-

SPKRIN

SPKR_OUT1

SPKR_OUT2

ST_CMP

ST_REF

THERM

THERM_BIAS

THERM_GND

TX_GND

VAG

GND

CD_CAP

EXT_MIC

HEADSET_DET

HJACK_DET

HJACK_MIC

IO_REG1

IO_REG2

LOGIC_SENSE

MB_CAP1

MB_CAP2

MIC_BIAS1

MIC_BIAS2

MIC_OUT

MIC_SELECT

NC1

GND

A1_INT

AD4

AD6

ALEFT_OUT

ALRT+

ALRT-

ALRTIN

ALRT_GND

AL_IN

ARIGHT_OUT

AR_IN

AUDIO_IN

AUD_REG

AUX_MIC_OUT

BATT_FBDK

R3150

0613952R66

GND

4804616R01

Q3403

0

22uF

C3560

2113928Z11

8.36V

VR4302

R5103DNP

0

B+

C4206

GND

V1

B+

GND

NC

V1

10pF

1.0uF

C3150

2113946D02

NC

4.7K

R5401

0613952Q89

4803558C01

Q3973

NC

4803558C01

Q3974

VR4301

8.36V

GND

10K

R7915

0613952R01

GND

B+

100

R4400

GND

B2

INPUT_1

A1

INPUT_2

A3

OUTPUT_1

C1

OUTPUT_2

C3

GND

NC

FL4300

CSPEMI202AG

4

POS

2

THERMISTOR

0.10uF

C3962

2113946K02

CONTACT

J5400

3

EEPROM

1

NEG

R4551

0

VRF_REF_2.775V

4809788E06

6.8V

VS4200

1.0uF

C3850

2113946D02

1.5K

R3650

GND

VCAM_2.6V

GND

B+

NC

B+

C4300

0

R3100

0613952R66

NC

VSIM_POG

NC

33pF

C4403

NC

GND

GND

GND

1.0uF

B5400

1

GND

R3652

22

OE

1

VCC

6

Y

4

B+

VCC_OUT

GND

NC

U3651DNP

NC7SP125

A 2

GND

3

5

NC

GND

2113946D02

C3600

1.0uF

10uH

L3000

2588079Y03

NC

10uF

2113944A31

C4208

33pF

C3201

10pF

C3984

2113944A25

V4

GND

VHVIO_2.775V

3.9pF

3.9pF

VHVIO_2.775V

C3965

3.9pF

C3964

10uF

C3963

1

3

5

6

4

2

C3205

GND

B+

NC

VRF_TX_2.775V

NC

J4300

270K

R3210

B+

4

GND

6

MODE

9

PGND1

10

PGND2

7

SW1

8

SW2

2

VIN1

3

VIN2

5188128Y01

TPS62021

U3200

11

CTGND

1

EN

5

FB

22uF

GND

NC

R3101

0.1

2113928Z11

C4306

4809995L20

32.768KHz

2

NC

3

NC1

4

OUT

1

IN

VLVIO_1.875V

C4000

2113944A32

NC

Y3982

MC146

NC

39pF

0

1.2

R5101

GND

GND

GND

R3180

GND

J4201

2

GND

39pF

C4392

2

+

1

2113928C04

C5400

4.7uF

NC

GND

J4100DNP

B+

4809924D18

CR3000

Q5100

4813824A17

VBOOST_5.5V

C4003

39pF

V4

GND

2113944A31

C4204

33pF

2113944A32

4809948D42

CR5401

VMAIN_1.55V

BATT+_RAW

GND

TP3001

TEST_POINT

1

0613952R66

R3654

0

Q3200DNP

0.1

R3001

Q3652

NC

GND

100K

R3200DNP

GND

GND

TP5252

1

VRF_HV_5V

D3961

4809653F07

GND

GND

10pF

C4104

2113944A25

200K

R3963

VLVIO_1.875V

GND

C4105

1.0uF

0

R4552

B+

2113946D02

GND

3

IN_A

2

NC

1

OUT_Y

4

VCC

5

VBOOST_5.5V

NC

MC74VHC1GT50

U3650

TP5253

1

1.0uF

2113946D02

C3209

VA_2.775V

BATT+_RAW

15KV

VR4300

0.10uF

C5402

2113946K02

GND

0

R5102

100

R5402

0613952Q49

R3960

GND

GND

NC

VA_2.775V

B+

0.24

B+

Q3560

4804616R01

33pF

2113944A31

C4402

GND

0613952R66

R3205DNP

0

AC1

AC2

AC3

AC4

GND

VHVIO_2.775V

NC

GND

LNJ0F1X7F0MT

D7904

0.10uF

C3102

2113946K02

B+

2113946K02

C3204

0.10uF

2113945D04

C4551

0.1uF

NC

R4008

0

4.7uF

C4210

2113928C04

NC

GND

J3001

TEST_POINT

1

GND

20m

VRF_RX_2.775V

10pF

C4205

0688044N02

R3961

10pF

4809653F07

D3962

2113944A25

C3983

15pF

C4214

D1

D2

G1

G2

S1

S2

VMAIN_1.55V

GND

4809579E58

Q5401DNP

2113928C04

C3350

4.7uF

NC

20K

R4402

GND

0

R4009

NC

120K

R3211

0

NC

GND

R5406

1.0uF

GND

4809788E06

6.8V

VS5400

VBOOST_5.5V

VMMC_2.775V

GND

2113946D02

C4502

1

B+

GND

2113946D02

C3801

1.0uF

VBOOST_5.5V

TEST_POINT

TP3003

NC

GND

VPOG_LVIO_1.875V

R5405DNP

470K

R3201

0

10uH

L3206

BATT+

C3550

2113946D02

GND

NC

V4

C3100

2113928C12

1.0uF

C1

OUTPUT_1

C3

OUTPUT_2

V1

GND

10uF

CSPEMI201AG

FL4000

B2

GND

A1

INPUT_1

A3

INPUT_2

2113946K02

C3002

0.10uF

C4215

NC

NC

RAW_EXT_B+

C4356

2113928Z11

33pF

5.6K

R3962

22uF

TEST_POINT

TP3002

1

4700pF

C4550

GND

GND

GND

GND

GND

TP3000

TEST_POINT

1

10uF

C3960

C3200

NC

NC

56pF

B+

L3207

6.8nH

C3202

C3961

10uF

NC

NC

150pF

4.7uF

2113946D02

C7904DNP

1.0uF

C3400

2113928Z11

2113928C04

C3951

B+

NC

22uF

VSIM_CARD

2113946D02

C3851

1.0uF

C3001

10uF

VA_2.775V

USB_PWR

NC

NC

C3654

2113946D02

C4393

39pF

NC

NC

1.0uF

NC

B+

39pF

C3003DNP

GND

1.0uF

C3050

2113946D02

C3450

1.0uF

GND

0.10uF

C3563DNP

2113946K02

2113946D02

B+

NC

TP5254

1

10uF

2113928C12

C3000

GND

33pF

C4103

2113944A31

GND

VS4201

6.8V

4809788E06

VSIM

VSIM2

VSIM_EN

VSIM_IN_BP

VSW1

VSW2

VUSB

VUSB_IN

WDI

XRXD

XTAL1

XTAL2

NC

VAUX2_DRV

VAUX3

VAUX3_IN

VAUX4

VAUX4_IN

VCC_OUT

VHOLD_EXT_EN

VHOLD_EXT_IN

VHOLD_OUT

VIB

VIB_IN

VOUT+

VOUT-

VPP

VREF+

VREF-

V4

V4_IN

V5

V5_IN

V6

V6_DRV

V7

V7_IN

V8

V8_IN

V9

V9_IN

VAG

VAUX1

VAUX1_DRV

VAUX2

USB_D-

USB_DIG_VCC

USB_PU

USB_V+

USB_V-

USB_VBUS

USR_OFF

UV_SEL

V1

V10

V10_IN

V1_IN

V2

V2_IN

V3

V3_IN

SPKR_GND2

SPKR_OUT1

SPKR_OUT2

STANDBY

STANDBY2

ST_CMP

ST_REF

THERM_BIAS

TSX1

TSX2

TSY1

TSY2

TS_BYP

TX

TX_ENB

USB_D+

RESETB

RESETMCU_B

RTC_GND

RX0

RX1

SE0_IN

SEC_CE

SEC_MISO

SEC_MOSI

SEC_SPI_CLK

SEC_SPI_VCC

SEC_SSI_VCC

SPKR+

SPKR-

SPKRIN

SPKR_GND1

PGM4

PGND1

PGND2

PLL_GND

PLL_LPF

POWER_FAIL

PRI_CE

PRI_MISO

PRI_MOSI

PRI_SPI_CLK

PRI_SPI_VCC

PRI_SSI_VCC

PSRC1

PSRC2

PSRC3

REG_DO_MON

NC_CB5

NC_CB6

NC_CB7

NC_CB8

NC_CB9

ON

ON2

OV_GATE

OV_SENSE

PGA_INL

PGA_INR

PGA_OUTL

PGM0

PGM1

PGM2

PGM3

MOD

MUX_CTRL

NC1

NC14

NC15

NC2

NC3

NC4

NC5

NC6

NC7

NC_CB1

NC_CB10

NC_CB2

NC_CB3

NC_CB4

LEDR

LI_CELL

LX1

LX2

LX3

MAIN_FET

MB_CAP1

MB_CAP2

MCLK

MIC2_TX2

MIC_BIAS1

MIC_BIAS2

MIC_IN-

MIC_OUT

MID_RATE2

MOBPORTB

DIN

EOLI

EXTOUT

EXT_MIC

FB1

FB2

FB3

FSYNC0

FSYNC1

HS_OUT_L

HS_OUT_R

INT_PRI

INT_SEC

ISENSE

LCELL_BYP

LEDG

BOB_BOOSTP

BOB_BUCKN

BOB_BUCKP

BOB_VDD1

BOB_VDD2

BOB_VSS1

CD_CAP

CHRGC

CHRGC_2

CLKIN1

CLK_IN

CS_OUT

DGND1

DGND2

DGND3

DGND_TEST

AUX_MIC+

AUX_MIC-

AUX_OUT

B+

BATT+

BATT_DETB

BATT_DET_IN

BATT_FDBK

BATT_I

BG_BYP

BITCLK0

BITCLK1

BL2_SINK

BL_FB

BL_SINK

BOB_BOOSTN

AGND4

AGND5

AGND6

AGND7

AGND_ESD1

AGND_ESD2

ALEFT_OUT

ALRT+

ALRT-

ALRTIN

ALRT_GND

ALRT_REF

ALRT_VCC

AL_IN

ARIGHT_OUT

AR_IN

B+

GND

32KHZ

A1_INT

AD4

AD5

AD6

AD7

AD8

AD9

AD_TRIG

AGND1

AGND2

AGND3

22K

R4000

2113946D02

C3300

1.0uF

1.0uF

C4400

2113946D02

VLVIO_1.875V

1

J4001

TEST_POINT

1

B5400

2

TEST_POINT

J4000

5.6K

R4550

0613952Q91

C3151

33pF

C4203

2113944A31

NC

VCC_OUT

VBOOST_5.5V

R3179DNP

GND

33pF

R3651

0

22

R7904

C3651

0.10uF

0

NC

GND

C3101

10uF

OV_GATE

OV_SENSE

OV_SENSE

0.10uF

C3403DNP

2113946K02

VHOLD_EXT_EN

VHOLD_EXT_EN

PCAP_32K

PCAP_32K

CLK_32_768K

ON2

AUDIO_OUT

EXT_OUT

BATT_I

MORTPORTB

MAIN_FET

EXT_B+

XTAL2

XTAL1

HS_SPKR_R

HS_SPKR_L_FILT

HS_SPKR_L

HS_SPKR_R_FILT

HS_MIC

PCAP_RESETb

V_VIB

BB_SPI_MISO

BB_SPI_MOSI

BB_SPI_CLK

PCAP_CS

USB_D+

USB_D-

D+

D-

MIC_BIAS1

AUX_MIC_OUT

USB_DETECT

VUSB

HJACK_MIC

USB_VPIN

RXD.VMIN

RTSb.XRXD

USB_VMOUT

TXD.VPOUT

USB_TXENb

MIC_BIAS2

MB_CAP2

MIC_OUT

A1_INT

VSIMC_EN

AUDIO_IN

MB_CAP1

VAUX2_DRV

LCELL_BYP

ALRT_REF

SPKR_OUT1

SPKRIN

EAR_SPKR-

EAR_SPKR-

EAR_SPKR+

EAR_SPKR+

VAG

VHOLD_OUT

EXT_MIC

ST_CMP

LOGIC_SENSE

ST_REF

LI_CELL

ALEFT_OUT

SPKR_OUT2

ALRTIN

ALRT-

ALRT-

ALRT-

ALRT+

ALRT+

ALRT+

THERM_BIAS

AD6

AD4

CD_CAP

AR_IN

ARIGHT_OUT

AL_IN

PCAP2_V1_OUT

PCAP2_V2_OUT

STEREO_FS

STEREO_CLK

STEREO_TX

PS_CLK

PCAP_CLK_IN

BG_BYP

PLL_LPF

V6_DRV

PCAP_BATT_FDBK

TEMP_SENSE

LX1

AD_TRIG

ASAP_RX

LX3

ASAP_FS

ASAP_CLK

ASAP_TX

BATT_FDBK_SW

BATT_FDBK

FLASH

BL_FB

BL_SINK

WATCHDOG

ON_OFF_ENDb

PCAP_INT

PCAP_RESETb

PCAP_RESETb

MUXCTL

USER_OFF

BATT+_RAW

BATT_DETb

BATT_IO

FLASH

BL_KPD_ON

U8

XTAL2

U10

GND

E8

H14

VSIM_EN

VUSB

A3

VUSB_IN1

C3

VUSB_IN2

D4

V_VIB

L17

WDI

H12

XRXD

C6

XTAL1

VAUX4_IN

VCC_OUT

R12

VHOLD_EXT_EN

U13

VHOLD_EXT_IN

T12

VHOLD_OUT

U12

VIB_IN

L16

VPP_OUT

U6

VSIM

B7

VSIM2

N1

VAUX1

E7

VAUX1_DRV

F8

VAUX2

C10

VAUX2_DRV

B10

VAUX3

K14

VAUX3_IN

L15

M17

VAUX4

M16

R13

V6_DRV

N12

V7

G17

V7_IN

G15

V8

A7

V8_IN

C7

V9

A6

V9_IN

B6

VAG

T1

V2_IN

U3

V3

F17

V3_IN

F16

V4

H15

V4_IN

H13

V5

M15

V5_IN

L13

V6

J13

UV_SEL

P16

V1

H17

V10

E10

V10_IN

A10

V1_IN

G16

V2_1

U1

V2_2

U2

V2_3

E5

USB_DIG_VCC

E6

USB_DM

A5

USB_DP

B4

USB_PU

C4

USB_VBUS

B3

USB_VM

G8

USB_VP

G7

USR_OFF

N8

TSX1

T3

TSX2

T2

TSY1

R4

TSY2

T4

TS_BYP

R8

TX

H8

TX2

M5

TX_ENB

SPKR_GND2

SPKR_IN

J5

H2

SPKR_OUT1

SPKR_OUT2

H3

STANDBY

M9

STANDBY2

P10

ST_CMP

G3

ST_REF

H6

THERM_BIAS

C12

SEC_SPI_VCC

A13

SEC_SSI_VCC

E3

SEO_IN

F7

SPKRM

J4

SPKRP

K2

SPKR_GND1_1

J2

SPKR_GND1_2

J3

K1

L12

RESET_MCU_B

K12

RTC_GND

T9

RX0

F5

RX1

D2

SEC_CE

H9

SEC_MISO

E11

SEC_MOSI

F11

SEC_SPI_CLK

PRI_SSI_VCC_4

PSRC1_1

F13

PSRC1_2

E15

PSRC1_3

E13

PSRC1_4

F12

PSRC2

B12

PSRC3

A11

REG_DO_MON

M12

RESETB

K9

PRI_MISO

R7

PRI_MOSI

P8

PRI_SPI_CLK

M8

PRI_SPI_VCC

U7

PRI_SSI_VCC

L8

PRI_SSI_VCC_2

L7

PRI_SSI_VCC_3

N5

M6

G5

PLL_LPF

F3

PMG0

P9

PMG1

R9

PMG2

J11

PMG3

K10

G12

PMG4

POWER_FAIL

N9

PRI_CE

J12

OV_GATE

N13

OV_SENSE

T15

PGA_INL

L6

PGA_INR

J7

PGA_OUTL

J6

PGND1

C17

PGND2

C11

PLL_GND

NC3

G10

NC4

C13

NC5

A2

NC6

A1

NC7

B1

NC8

U16

NC9

ON2B

T6

ONB

NC1

U17

NC10

T17

NC11

H11

NC12

G11

NC13

NC14

M10

NC15

N11

C14

NC2

E12

N3

MIC_BIAS2

M2

MIC_INM

R3

MIC_OUT

R2

MID_RATE2

R16

MOBPORTB

T16

MOD

N10

MUX_CTRL

R10

H10

T11

LX1

D16

LX2

A12

LX3

B11

MAIN_FET

N15

MB_CAP1

M3

MB_CAP2

M1

MCLK

G6

MIC_BIAS1

K5

HS_OUT_R

K4

INT_PRI

L10

INT_SEC

D15

ISENSE

M13

LCELL_BYP

T10

LEDG

J16

LEDR

J15

LI_CELL

EOL_INT_B

EXTOUT

F2

EXT_MIC

K7

FB1

F15

FB2

F10

FB3

D10

FSYNC0

H7

FSYNC1

B2

HS_OUT_L

R11

D32KHZ

T7

DGND1

J8

DGND2

J14

DGND3

G9

DGND4

K8

G13

DGND_TEST

DIN

C5

J10

B9

BP1

U15

BP2

A8

CD_CAP

L3

CHRGC

R15

CHRGC_2

R14

CLKIN

C2

CLKIN1

C1

CS_OUT

E9

BOB_VOUTP

C9

BOB_VREFM

C8

BOB_VREFP

B8

BOB_VSS1_1

A16

BOB_VSS1_2

A17

BOB_VSS1_3

B17

BOB_VSW1

D9

BOB_VSW2

K15

BL_SINK

K17

BOB_BOOSTN

B15

BOB_BOOSTP

A15

BOB_BUCKN

B16

BOB_BUCKP

C15

BOB_VDD1

B14

BOB_VDD2

C16

BOB_VOUTM

K13

BATT_DET_IN

K11

BATT_FDBK

L9

BATT_I

M11

BG_BYP

U11

BITCLK0

F6

BITCLK1

D3

BL2_SINK

K16

BL_FB

G1

AL_IN

L5

ARIGHT_OUT

L2

AR_IN

K6

AUX_MICM

P2

AUX_MICP

P3

AUX_OUT

R1

BATTP

R17

BATT_DETB

F9

AGND_ESD2

T14

ALEFT_OUT

K3

ALRTIN

H4

ALRTM

F1

ALRTP

H1

ALRT_GND

E1

ALRT_REF

G2

ALRT_VCC

P15

AGND1

L1

AGND2

L11

AGND3

N17

AGND4

H16

AGND5

E17

AGND6

T8

AGND7

D8

AGND_ESD1

A1_INT

H5

AD4

U5

AD5

R5

AD6

R6

AD7

N6

AD8

N7

AD9

M7

AD_TRIG

U3000

TWL93010DGZGR

NC1

NC2

NC4

NC5

USB_D+

USB_V-

VUSB

EXTOUT

AGND4

NC7

VSIM_IN_BP

PGM4

PGND1

USB_VBUS

USB_V+

USB_D-

USB_DIG_VCC

VUSB_IN

FB3

V4_IN

V5_IN

V2_IN

V1_IN

V3_IN

VSIM

VSIM2

VSIM_EN

XTAL2

MAIN_FET

V2

V3

V4

V5

V6_DRV

PGND2

PSRC3

LX3

VAG

AUX_OUT

ST_CMP

VREF+

VREF-

STANDBY2

EXT_MIC

UV_SEL

AD4

AD5

AD6

AD7

A1_INT

EOLI

ON

ON2

STANDBY

BL_SINK

BL_FB

BL2_SINK

LEDR

LEDG

SEC_CE

SEC_SPI_VCC

SPKRIN

THERM_BIAS

AD_TRIG

VPP

PGA_OUTL

USB_PU

NC_CB3

NC_CB2

AGND3

AGND6

AGND5

BITCLK1

RX1

CHRGC

AGND2

PGM1

PGM2

NC_CB10

PGM0

VIB

V1

NC_CB1

NC_CB4

NC_CB5

NC_CB6

PGM3

BOB_BUCKP

BOB_BOOSTN

BOB_BOOSTP

SPKR_GND2

SPKR_GND1

BOB_VSS1

SPKR_OUT1

MB_CAP1

ALEFT_OUT

ARIGHT_OUT

HS_OUT_R

32KHZ

BATT_I

VSW1

VSW2

VOUT+

VOUT-

TSX2

RTC_GND

TX_ENB

TSY1

TSY2

TS_BYP

PRI_SPI_VCC

PRI_CE

PRI_SPI_CLK

ALRT_VCC

ALRT_REF

HS_OUT_L

MIC2_TX2

V6

V7

V8

V9

V10

VAUX1_DRV

VAUX1

VAUX2_DRV

AGND7

NC3

RX0

PSRC2

VHOLD_EXT_EN

V7_IN

V8_IN

V9_IN

V10_IN

SEC_SSI_VCC

FSYNC1

MOBPORTB

BATT_DET_IN

MUX_CTRL

MOD

POWER_FAIL

BATT_FDBK

B+

BATT+

LI_CELL

VHOLD_OUT

VCC_OUT

CS_OUT

CLKIN1

FB1

VAUX4

DGND2

DGND1

CD_CAP

DGND3