Intersil Corporation Digital Library

Technical White Paper

Digital Multiphase Power for

CPU Cores

written by

Scott Deuty, Tom Duffy, and Philip Chesley (Primarion)

Larry Pearce (Intersil)

Abstract

Technology’s relentless march toward ever increasing CPU speed and

performance is taxing today’s power systems and promises to demand

significantly more in the future.

Digital Multiphase Power (DMP) from Primarion and Intersil is the first

architecture that meets key performance, user accessibility, reusability,

and upgradeability requirements.

Technical White Paper

Contents

The Need for a New Regulator Architecture

Digital Multiphase Power Regulation

Design Optimization and Diagnostics Monitoring

Single Solution for Multiple Platforms

Legal Notice and Trademark Information

The information provided in this document is provided on an "AS IS" basis for informational purposes only. In addition, all warranties

are hereby disclaimed, including the implied warranties of merchantability, fitness for a particular purpose, or non-infringement.

Intersil shall not, under any circumstances, be liable to any person for any special, incidental, indirect or consequential damages

whatsoever (including, without limitation, damages resulting from us of or reliance on the information provided, loss or profits,

business interruption, loss of information), even if Intersil has been advised of the possibility of such damages.

Copyright 2002 Intersil Corporation. All rights reserved. All other companies, products, and service names and brands are the

trademarks or registered trademarks of their respective owners.

Technical White Paper

3

The Need for a New

Regulator Architecture

Technology’s relentless march toward ever increasing CPU speed and performance is

taxing today’s power systems and promises to demand significantly more in the

future. While processor core voltages will drop to 1 V and below, current demand will

rise, likely topping 150 A by 2005. Simultaneously, processor clock frequencies will

push into the multiple-GHz range, yielding transients estimated to be 1000 A/ns at the

processor and 1000 A/us at the socket. At these rates, even the smallest parasitic

inductance creates voltage transients that can overwhelm sub-1V logic gates. Current

technology has been shown to generate 160 mV voltage transients on a 1.5 VDC core

voltage, a variation that threatens data integrity.

To minimize line inductance, OEMs place the core power supply at the processor,

requiring the supply to meet small form factor and high efficiency demands along with

electrical performance. A new power architecture is needed to meet these

requirements while providing fast time-to-market and scalability. Digital Multiphase

Power (DMP) from Primarion and Intersil is the first architecture that meets key

performance, user accessibility, reusability, and upgradeability requirements.

Digital Multiphase

Power Regulation

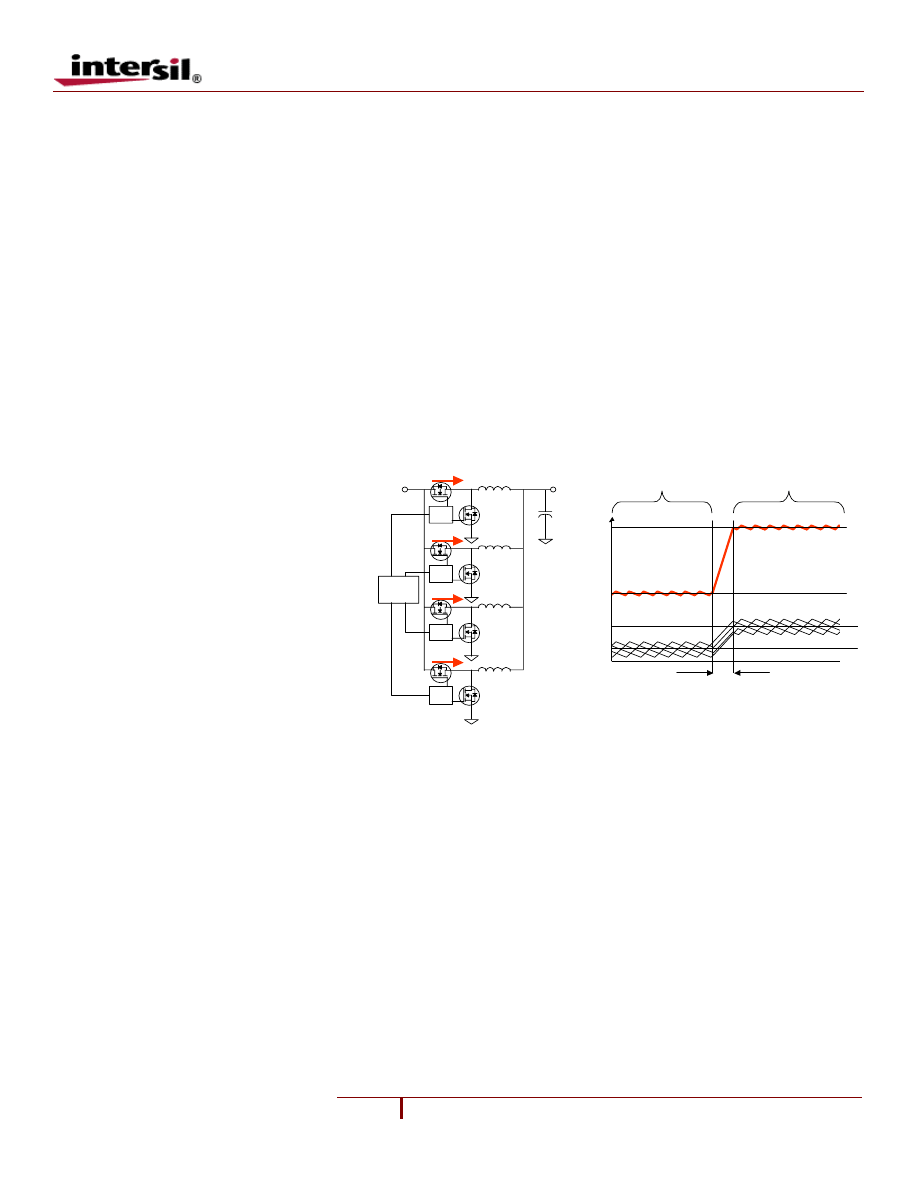

Today’s processors use multiphase, BUCK switching-converters that consist of a

switching controller, gate drivers, and discrete FET power stages as in Figure 1. DMP

from Primarion/Intersil changes the controller architecture from typical analog control

to digital control with associated signal and power partitioning. The DMP architecture

offers greater flexibility, multi-tasking, and noise immunity.

15 amp

60 amp

6 amp

24 amp

Normal Operating Mode

Normal Operating Mode

Active Transient Response Mode

(ATR High Shown)

P W M

Cont rol

IC

Driver

Driver

Driver

Driver

Figure 1:

Typical Multiphase BUCK Regulator Schematic and Current

Waveforms

The Primarion/Intersil signal partitioning isolates analog signals at the Driver/FET and

uses digital signals to communicate with the purely digital controller. Digital control

allows for better optimization and real-time adaptation of the control loop. The

controller also provides a digital link to the outside world allowing the user

unprecedented access to programmable control-loop characteristics and readable

system status data. The programmable DMP architecture is reusable across multiple

voltage and current applications and can accommodate future processor needs.

The Primarion/Intersil power partitioning integrates the high-side FET with the gate

drivers and analog-digital interfacing. This allows control intelligence to be keyed on

the integrated high-side FET, while low-side FET flexibility is maintained for addressing

dissipation challenges of high step-down ratio, low duty-cycle applications.

To meet the transient requirements of 2GHz and greater processors, a multiphase

regulator must operate in two modes, normal and Active Transient Response (ATR) as

shown in Figure 1. DMP optimizes performance in both modes and smoothly manages

mode transitions. In normal mode, phase pulses are evenly distributed across the

switching cycle to minimize the combined ripple as in Figure 1. This allows lower

phase inductance than a single-phase design of the same ripple. During ATR the

phases are time-aligned yielding a current ramp that is the sum of all phase ramps,

Technical White Paper

4

effectively paralleling the inductors. The Primarion/Intersil architecture allows up to

eight phases operating at up to 1 MHz for di/dt rates in excess of 800 A/us at the

inductors and over 1500 A/us at the output capacitor.

Rapid and efficient transition from ATR to normal mode requires adjustment of the

control loop. Digital control provides for such a smooth transition between ATR and

normal operating modes. A patent pending algorithm performs control loop correction

for the transition in DMP. With advanced loop adjustment to manage ATR activity,

output settling-time between modes falls from 50 us to 300 ns.

DMP architecture facilitates the implementation of flexibility and scalability features in

the regulator design. The multitasking that DMP naturally provides allows quick

adaptation of the ATR window to match changes in AVP and VID. DMP automatically

supports one to eight phases per controller allowing designs to scale to meet output

load current requirements. Also, current is evenly distributed among the phases by

the DMP control. Future versions of DMP will detect the loss of a phase and adjust the

system accordingly.

Serial digital signaling allows for point-of-load placement of the power stages

independent of controller placement. Digital signaling to the power stages confines

drive currents to the power stage, along with the analog signals. The integrated

design and use of advanced semiconductor processes enables the DMP solution to

operate up to 1MHz. This increased switching speed reduces filter component size and

maximizes system bandwidth to increase current ramp rates.

The selection of low-side FETs is based on the response time versus efficiency

tradeoff. The DMP architecture allows both the switching frequency and dead-time to

be adjusted for optimal performance with chosen FET and at various system operating

conditions.

Design Optimization

and Diagnostics

Monitoring

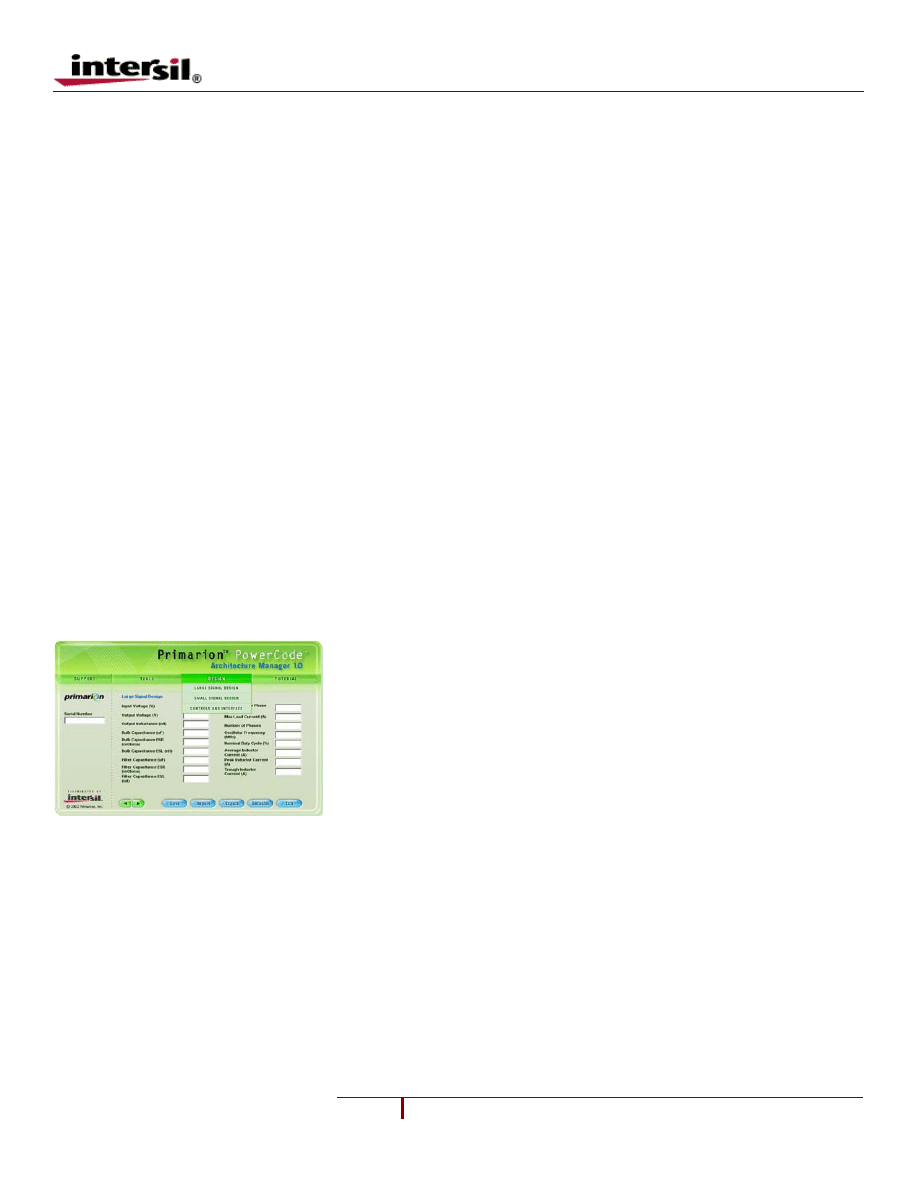

Figure 2:

Users have ultimate control

of the system via Primarion

TM

PowerCode

TM

Architecture Manager

software.

Optimizing the power system for the chosen processor load is critical to today’s

computer system design. The DMP architecture from Primarion /Intersil allows the

power system designer to set key performance parameters through the Primarion

TM

PowerCode

TM

Architecture Manager software. This innovative tool allows designers to

optimize the power system for the processor it powers. Designers can choose low side

FET types, phase inductor values, output capacitor values, non-overlap times, loop

compensation, AVP window, voltage and current, fault monitoring indicators, and

various support component values. Once these values are inserted into the variable

fields, system performance is easily simulated and tested. Data generated by the

Primarion

TM

PowerCode

TM

software can be ported to PSPICE

TM

or Matlab

TM

simulators

for more detailed analysis.

Recent processor designs specify the amount and location of the voltage regulator

output capacitance, which necessarily impacts the regulator’s bandwidth and stability.

Via the Primarion™ PowerCode™ software interface, the control loop is easily adjusted

for optimal performance with the specified capacitance and other system parameters.

These adjustments can be made during system operation. Designers need not shut

down the system to change analog loop components. These in situ adjustments allow

rapid, non-invasive system optimization, a boon to any product development.

The ability to quickly customize designs and optimize system performance also means

a reduction in inventory required to adjust systems to specification. Rather than

storing an inventory of analog components and perhaps controllers, system

customization is reduced to adjusting a set of digital parameters loaded into the

controller.

Single Solution for

Multiple Platforms

The Digital Multiphase architecture is inherently adaptable to various low-voltage,

high-current applications such as DDR memory, memory hub controllers, and DSPs,

as well as other computing platforms. By matching the power stage components to

the application, users can scale the design to optimally meet current and ripple

demands. At 1 MHz switching frequency users can add phases in 15 A increments; of

course other current and frequency phase combinations are possible. The DMP

operating range of 250 KHz to 1 MHz allows system optimization when considering the

tradeoffs of response time versus efficiency.

Switching frequency has a direct effect on overall system efficiency. With DMP

control, the designer is free to set a slower switching frequency for improved

Technical White Paper

5

efficiency, or faster switching frequency for rapid response to load transients. By

simply inputting new values into the software, switching frequency is easily optimized.

Likewise, the DMP architecture allows designers to optimize inductance versus number

of phases, which directly affects output ripple voltage and system response.

Powering the Future

DMP from Primarion/Intersil enables an upgrade path to meet ever-increasing

microprocessor slew rate requirements. The DMP architecture establishes an Active

Voltage Stabilization Interface between the DMP regulator and Primarion point-of-use

transient regulators residing inside the processor package. This system balances

power sourcing between the switching regulator and the transient regulators,

minimizing thermal impact to the processor while maximizing system performance.

The future for digital control of power systems is very bright. Control through

programming expands the functionality of the controller. Future digital controllers

could easily regulate multiple voltage loops, detect loss of phase, and scale to greater

than eight phases. Multiple voltage regulation could include a step down front end for

the 48V market. All of these options are provided through software programming

therefore reducing the amount of added circuitry required to increase functionality.

Conclusion

Digital Multiphase Power from Primarion and Intersil delivers the much-needed

performance, accessibility, reusability and upgradeability that will keep processor

speed and performance on track with Moore’s Law despite significantly tighter

regulation and greater current ramp requirements. Digital Multiphase Power also

provides the benefits of accessibility and reusability, allowing designers to quickly and

easily optimize systems with Primarion

TM

PowerCode

TM

Architecture Manager software.

Not only can Digital Multiphase Power be applied to a range of existing systems, it

allows for upgrade to meet the needs of next-generation processors through its Active

Voltage Stabilization Interface. With Digital Multiphase Power from Primarion and

Intersil, designers can cut design times, enhance system performance, and rely on

clean, efficient, intelligent power to drive advanced processors.

© 2002, Primarion, Inc.,

Primarion and the Primarion logos are trademarks of Primarion, Inc.

Pentium is a registered trademark of Intel Corporation.

Other names and brands are the property of their respective owners.

Document Outline

- The Need for a New Regulator Architecture

- Digital Multiphase Power Regulation

- Design Optimization and Diagnostics Monitoring

- Single Solution for Multiple Platforms

- Powering the Future

- Conclusion

Wyszukiwarka

Podobne podstrony:

300W, 300Khz Current Mode Half Bridge Power Supply With Multiple Outputs Using Coupled Inductors

Digital Control Of Switching Power Supply Power Factor Correction Stage

Convert Computer ATX Power Supply to Lab Power Supply

Jvc Power Supply Description And Trouble Shooting Procedure

Battery Inverter For Modularly Structured Pv Power Supply Systems

0 50V 2A LM10C, 0 50V 2A Bench power supply circuit diagrams, schematics, electronic projects

(Wydruk – ATX Switching Power Supply 13,8 V Proste zmiany w celu zwiększenia napięcia wyjściowego Ja

How to Modify an ATX Computer Power Supply

Adaptive fuzzy control for uninterruptible power supply with three phase PWM inverter

Control and Power Supply for Resistance Spot Welding (RSW)

Performance Improvements in an arc welding power supply based on resonant inverters (1)

Convert Computer ATX Power Supply to Lab Power Supply

(ebook free energy) 50000 vdc power supply

więcej podobnych podstron