Programowanie mikrokontrolerów

ATmega16

Marcin Engel

Marcin Peczarski

Instytut Informatyki Uniwersytetu Warszawskiego

17 września 2009

Poznajemy ATmega16

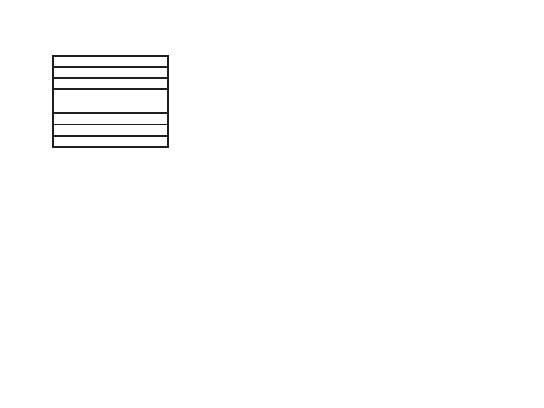

(XCK/T0) PB0

(T1) PB1

(INT2/AIN0) PB2

(OC0/AIN1) PB3

(SS) PB4

(MOSI) PB5

(MISO) PB6

(SCK) PB7

RESET

VCC

GND

XT

AL2

XT

AL1

(RXD) PD0

(TXD) PD1

(INT0) PD2

(INT1) PD3

(OC1B) PD4

(OC1A) PD5

(ICP1) PD6

P

A0 (ADC0)

P

A1 (ADC1)

P

A2 (ADC2)

P

A3 (ADC3)

P

A4 (ADC4)

P

A5 (ADC5)

P

A6 (ADC6)

P

A7 (ADC7)

AREF

GND

A

VCC

PC7 (T

OSC2)

PC6 (T

OSC1)

PC5 (TDI)

PC4 (TDO)

PC3 (TMS)

PC2 (TCK)

PC1 (SDA)

PC0 (SCL)

PD7 (OC2)

Architektura mikrokontrolera ATmega16

I

Procesor o zredukowanym zbiorze rozkazów (RISC)

I

Architektura little-endian

I

Architektura harwardzka (odrębne pamięci i magistrale dla

programu i danych)

I

16 kiB pamięci programu (pamięć flash)

I

1 kiB pamięci danych (SRAM)

I

32 rejestry ogólnego przeznaczenia

I

64 rejestry wejścia-wyjścia, układy peryferyjne

I

512 bajtów pamięci nieulotnej (EEPROM)

I

3 liczniki

I

21 przerwań (o ustalonej kolejności obsługi)

I

Interfejsy szeregowe: USART, I

2

C

I

8-kanałowy, 10-bitowy przetwornik A/C

Architektura, schemat blokowy

Flash

Program

Memory

Instruction

Register

Instruction

Decoder

Program

Counter

Control Lines

32 x 8

General

Purpose

Registrers

ALU

Status

and Control

I/O Lines

EEPROM

Data Bus 8-bit

Data

SRAM

Direct Addressing

Indirect Addressing

Interrupt

Unit

SPI

Unit

Watchdog

Timer

Analog

Comparator

I/O Module 2

I/O Module1

I/O Module n

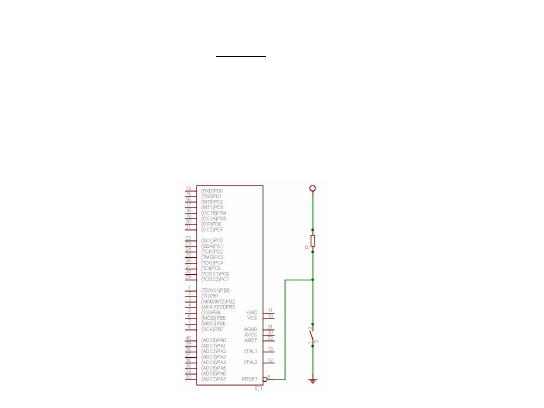

Najprostszy układ

Podłączamy:

I

zasilanie (nóżki VCC, AVCC, GND),

I

układ reset (nóżka RESET),

I

złącze programatora (nóżki MOSI, MISO, SCK, RESET, VCC,

GND).

Wyjaśnienia:

I

VCC na schematach oznacza „+” zasilania (inne oznaczenie

to VDD),

I

AVCC oznacza „+” zasilania części analogowej,

I

GND to „−” zasilania,

I

RESET oznacza odwróconą logikę (tj. reset jest aktywny, jeśli

podamy niski poziom napięcia).

Zasilanie

I

Układ ATmega16 wymaga zasilania napięciem stałym

z zakresu od 4,5 do 5,5 V (wersja 16L od 2,7 V).

I

Nowsza wersja układu ATmega16A może być zasilana

napięciem z zakresu od 2,7 V do 5,5 V.

I

Zwykle stosujemy scalony stabilizator napięcia 5 V typu 7805.

1

Zasilanie, cd.

I

Schemat połączeń znajduje się w nocie katalogowej.

7805

V

in

V

out

1

2

3

I

Na płytce testowej znajduje się mostek prostowniczy

i stabilizator o regulowanym napięciu wyjściowym.

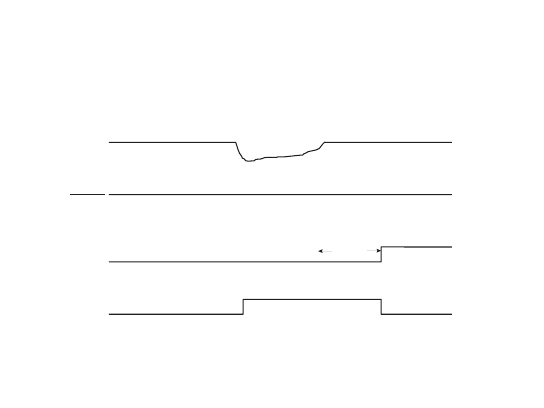

Układ resetu

I

Normalnie na nóżce RESET powinien być stan wysoki.

I

Chcemy móc ręczne zresetować urządzenie (np. przyciskiem).

I

Programator również musi móc zresetować układ.

I

Rezystor podciągający na ogół nie jest potrzebny (jest

wewnętrzny).

Rozwiązanie:

Przestrzeń adresowa

Są trzy rozdzielne przestrzenie adresowe:

I

pamięć danych

I

zorganizowana w bajty

I

rejestry ogólnego przeznaczenia

I

rejestry wejścia-wyjścia

I

SRAM

I

nieulotna pamięć danych

I

zorganizowana w bajty

I

EEPROM

I

dostęp przez rejestry wejścia-wyjścia za pomocą odpowiedniej

sekwencji rozkazów

I

pamięć programu

I

zorganizowana w słowa 16-bitowe

I

przy dostępie do rozkazów adresowana słowami

I

przy dostępie do danych adresowana bajtami

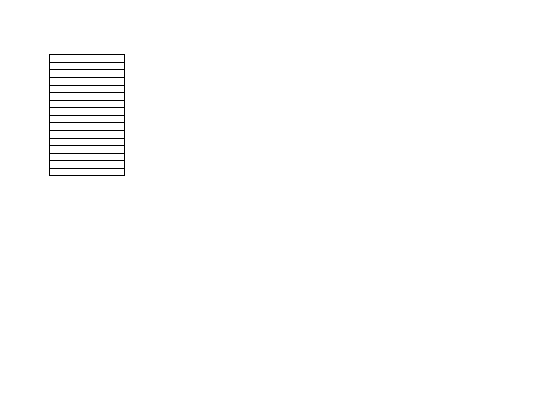

Rejestry

7

0

Addr.

R0 $00

R1

$01

R2

$02

…

R13

$0D

General

R14

$0E

Purpose

R15

$0F

Working

R16

$10

Registers

R17

$11

…

R26

$1A

X-register Low Byte

R27

$1B

X-register High Byte

R28

$1C

Y-register Low Byte

R29

$1D

Y-register High Byte

R30

$1E

Z-register Low Byte

R31

$1F

Z-register High Byte

I

32 rejestry 8-bitowe: R0, . . . , R31

I

W rozkazach z adresowaniem natychmiastowym można

stosować tylko rejestry R16, . . . , R31.

LDI R16, 123

SUBI R18, 5

I

Przesłania wartości są możliwe między każdą parą rejestrów.

MOV R3, R19

I

Operacje arytmetyczno-logiczne można wykonywać na danych

w dowolnych rejestrach.

ADD R9, R17

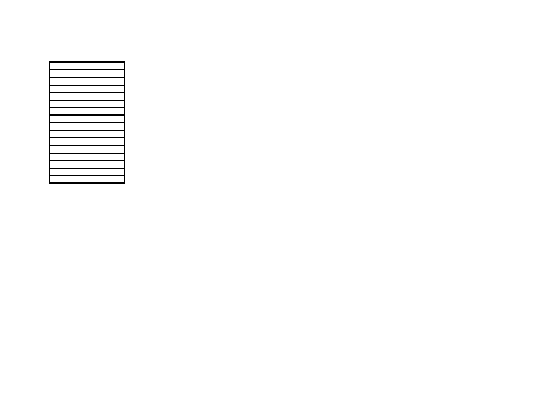

Rejestry

7

0

Addr.

R0 $00

R1

$01

R2

$02

…

R13

$0D

General

R14

$0E

Purpose

R15

$0F

Working

R16

$10

Registers

R17

$11

…

R26

$1A

X-register Low Byte

R27

$1B

X-register High Byte

R28

$1C

Y-register Low Byte

R29

$1D

Y-register High Byte

R30

$1E

Z-register Low Byte

R31

$1F

Z-register High Byte

I

Do adresowania pośredniego pamięci danych używa się par

rejestrów:

I

para rejestrów R27:R26 to rejestr X,

I

para rejestrów R29:R28 to rejestr Y,

I

para rejestrów R31:R30 to rejestr Z.

LD R16, X

ST Y, R17

I

Rejestr Z można stosować do adresowania pośredniego

pamięci programu (rozkazy LPM, SPM).

Rejestry

7

0

Addr.

R0 $00

R1

$01

R2

$02

…

R13

$0D

General

R14

$0E

Purpose

R15

$0F

Working

R16

$10

Registers

R17

$11

…

R26

$1A

X-register Low Byte

R27

$1B

X-register High Byte

R28

$1C

Y-register Low Byte

R29

$1D

Y-register High Byte

R30

$1E

Z-register Low Byte

R31

$1F

Z-register High Byte

I

Rejestry R24, . . . , R31 mogą być używane, do operacji na

danych 16-bitowych.

ADDW R25:R24, 3

I

Para rejestrów R1:R0 jest domyślnym miejscem wyniku

operacji mnożenia.

I

Możliwe są przesłania 16-bitowe między parami rejestrów.

MOVW R13:R12, R17:R16

I

Rejestry są mapowane na adresy od $00 do $1F w przestrzeni

adresowej danych.

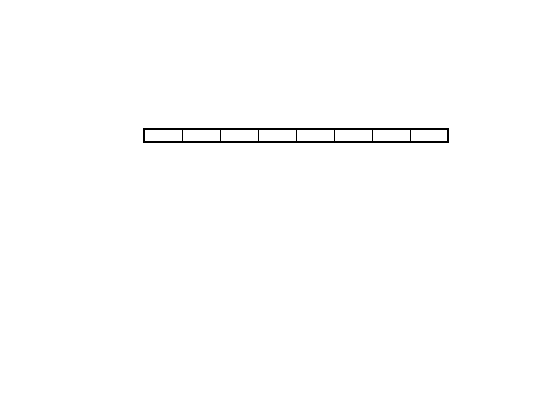

Pamięć wejścia-wyjścia

I/O Registers

$00

$01

$02

$3D

$3E

$3F

...

I

Zawiera 64 rejestry wejścia-wyjścia odpowiedzialne m.in. za

konfigurację poszczególnych układów wejścia-wyjścia (np.

rejestry PORTx, DDRx, SP, SREG).

I

Adresowane od $00 do $3F.

I

Adresy mapowane na adresy od $20 do $5F pamięci danych.

I

Zapis odbywa się za pomocą rozkazu OUT, a odczyt za

pomocą rozkazu IN.

I

Na pierwszych 32 rejestrach we/wy można bezpośrednio

ustawiać bity (rozkazy SBI, CBI) i je sprawdzać (rozkazy

SBIS, SBIC).

Rejestr stanu

I

Znajduje się w pamięci we-wy pod adresem SREG ($3F).

I

Jest uaktualniany po każdej operacji arytmetyczno-logicznej.

Bit

7

6

5

4

3

2

1

0

I

T

H

S

V

N

Z

C

SREG

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

I

bit I – włączone przerwania

I

bit T – do przechowania dowolnego bitu (rozkazy BLD, BST)

I

bit H – przeniesienie z młodszego półbajta do starszego

I

bit V – nadmiar w arytmetyce uzupełnieniowej do dwóch

I

bit N – bit znaku wyniku operacji

I

bit S – bit znaku rzeczywistego wyniku operacji S = V ⊕ N

I

bit Z – wynikiem operacji jest zero

I

bit C – przeniesienie z najstarszego bitu

Pamięć danych – podsumowanie

I

Adresowana od $0000 do $045F (stała RAMEND)

I

1 kiB o adresach od $0060 do $045F to pamięć ulotna SRAM

I

Na adresy od $0000 do $005F są wirtualnie odwzorowane

rejestry ogólnego przeznaczenia i pamięć wejścia-wyjścia, np.:

rozkazy OUT $10, R18 oraz ST $30, R18 mają ten sam

efekt! Ale pierwszy działa szybciej.

R0

R1

R2

R29

R30

R31

I/O Registers

$00

$01

$02

...

$3D

$3E

$3F

...

$0000

$0001

$0002

$001D

$001E

$001F

$0020

$0021

$0022

...

$005D

$005E

$005F

...

$0060

$0061

$045E

$045F

...

Internal SRAM

Stos

I

Znajduje się w pamięci danych.

I

Przed wykonaniem jakiejkolwiek operacji na stosie programista

musi ustawić dwubajtowy wskaźnik stosu SP w pamięci we-wy.

I

Wskaźnik stosu SP składa się z dwóch rejestrów SPH i SPL.

I

Stos rośnie w dół pamięci (od wysokich adresów do niskich).

I

SP pokazuje zawsze na pierwszy wolny bajt pod wierzchołkiem

stosu.

I

Rozkaz PUSH odkłada jeden bajt na stos, a POP zdejmuje

jeden bajt ze stosu.

I

Wywołanie podprogramu (RCALL, CALL) odkłada dwa bajty

(adres powrotu) na stos, a powrót z niego (RET) zdejmuje

dwa bajty.

Typowa inicjacja stosu

LDI R16, HIGH (RAMEND)

OUT SPH, R16

LDI R16, LOW (RAMEND)

OUT SPL, R16

Nieulotna pamięć danych

I

Stanowi odrębną przestrzeń adresową.

I

Dostęp do niej odbywa się za pomocą specjalnych rejestrów

we-wy (EEAR, EEDR, EECR).

I

Protokół dostępu do tej pamięci poznamy w dalszej części

wykładu.

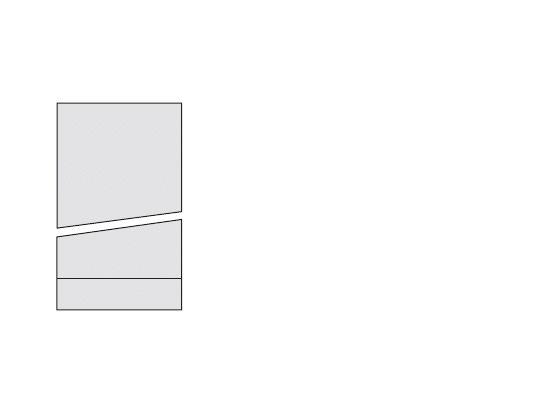

Pamięć programu

$0000

$1FFF

Application Flash Section

Boot Flash Section

I

Ma 16 kiB.

I

Jest podzielona na dwie części

z niezależną ochroną dostępu: boot

loader oraz część aplikacji.

I

Większość kodów rozkazów jest

2-bajtowa (1 słowo), ale są też

rozkazy 4-bajtowe (2 słowa).

I

Program może modyfikować sam

siebie.

Tryby adresowania

I

natychmiastowe: LDI R16, 3

I

bezpośrednie: LDS R1, 100

I

pośrednie: LD R1, X

I

pośrednie z postinkrementacją: LD R1, X+

I

pośrednie z predekrementacją: LD R1, -X

I

pośrednie z przemieszczeniem: LDD R1, Y+2

I

pośrednie pamięci programu: LPM R1, Z

Przerwania

I

Kod programu rozpoczyna się od wektora przerwań.

I

Zgłoszenie przerwania powoduje sprzętowe:

I

odłożenie na stos adresu powrotu (ale nie rejestru stanu!),

I

zablokowanie przerwań poprzez wyzerowanie bitu I w rejestrze

stanu SREG,

I

wykonanie rozkazu spod odpowiedniego adresu w pamięci

programu.

I

Program obsługi przerwania zwykle kończy się rozkazem

RETI, który włącza przerwania.

Wektor przerwań

Vector No.

Program

Address

Source

Interrupt Definition

1

$000

RESET

External Pin, Power-on Reset, Brown-out

Reset, Watchdog Reset, and JTAG AVR

Reset

2

$002

INT0

External Interrupt Request 0

3

$004

INT1

External Interrupt Request 1

4

$006

TIMER2 COMP

Timer/Counter2 Compare Match

5

$008

TIMER2 OVF

Timer/Counter2 Overflow

6

$00A

TIMER1 CAPT

Timer/Counter1 Capture Event

7

$00C

TIMER1 COMPA

Timer/Counter1 Compare Match A

8

$00E

TIMER1 COMPB

Timer/Counter1 Compare Match B

9

$010

TIMER1 OVF

Timer/Counter1 Overflow

10

$012

TIMER0 OVF

Timer/Counter0 Overflow

11

$014

SPI, STC

Serial Transfer Complete

12

$016

USART, RXC

USART, Rx Complete

13

$018

USART, UDRE

USART Data Register Empty

14

$01A

USART, TXC

USART, Tx Complete

15

$01C

ADC

ADC Conversion Complete

16

$01E

EE_RDY

EEPROM Ready

17

$020

ANA_COMP

Analog Comparator

18

$022

TWI

Two-wire Serial Interface

19

$024

INT2

External Interrupt Request 2

20

$026

TIMER0 COMP

Timer/Counter0 Compare Match

21

$028

SPM_RDY

Store Program Memory Ready

Kiedy pojawia się przerwanie RESET

Po włączeniu zasilania (power-on reset)

V

RESET

TIME-OUT

INTERNAL

RESET

t

TOUT

V

POT

V

RST

CC

Kiedy pojawia się przerwanie RESET

Na skutek resetu zewnętrznego

CC

Kiedy pojawia się przerwanie RESET

Przy spadku napięcia (brown-out detection)

V

CC

RESET

TIME-OUT

INTERNAL

RESET

V

BOT-

V

BOT+

t

TOUT

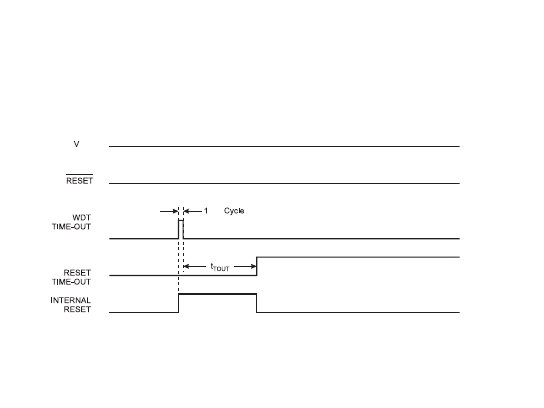

Kiedy pojawia się przerwanie RESET

Przy braku wyzerowania układu watchdog

CK

CC

Co się dzieje po resecie?

I

Ustawienie rejestrów we/wy na wartości początkowe

I

Rozpoczęcie wykonania programu od instrukcji znajdującej się

pod adresem 0 (przerwanie 0)

Pierwszy program

.CSEG

; segment kodu

.ORG 0

; przerwanie o adresie 0 = reset

JMP START

.ORG 42

; pierwszy adres za wektorem przerwań

START:

LDI R16, 0b00001111

OUT DDRA, R16

; nogi PA0..PA3 jako wyjścia

LDI R16, 0b00001011

OUT PORTA, R16

; nogi PA0,PA1,PA3 stan wysoki

; noga PA2 stan niski

PETLA:

RJMP PETLA

; główna pętla programu

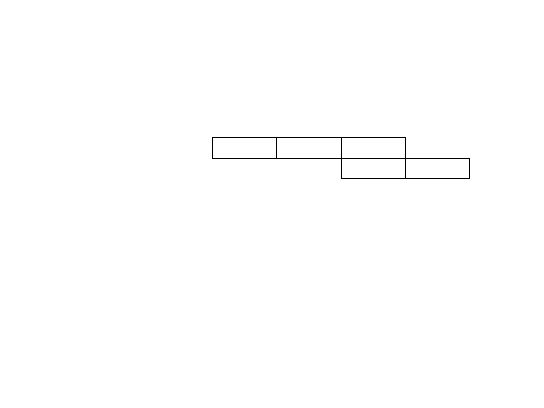

Cykl wykonania instrukcji

I

Gdy nie ma skoków.

takt zegara

T1

T2

T3

T4

instrukcja 1

fetch

execute

instrukcja 2

fetch

execute

instrukcja 3

fetch

execute

I

Gdy instrukcja 1 wykona skok do instrukcji 3.

takt zegara

T1

T2

T3

T4

instrukcja 1

fetch

execute execute

instrukcja 2

fetch

instrukcja 3

fetch

execute

Cykl wykonania instrukcji, cd.

I

Gdy instrukcja 1 potrzebuje więcej taktów do wykonania.

takt zegara

T1

T2

T3

T4

instrukcja 1

fetch

execute execute

instrukcja 2

fetch

execute

I

Dokumentacja podaje liczbę taktów execute.

I

Z wyjątkiem dwóch instrukcji (SPM, BREAK) wszystkie

pozostałe potrzebują maksymalnie cztery takty execute.

I

Większość instrukcji potrzebuje jeden lub dwa takty execute.

I

Czas wykonywania programu jest w pełni przewidywalny –

brak spekulatywnego wykonywania instrukcji.

Jednostka arytmetyczno-logiczna ALU

I

Rozkazy arytmetyczne 8-bitowe wykonuje w jednym cyklu

zegara.

I

Rozkazy arytmetyczne 16-bitowe i rozkazy mnożenia wykonuje

w dwóch cyklach zegara.

I

Wspiera operacje na liczbach bez znaku, ze znakiem (notacja

uzupełnieniowa do dwóch) oraz ułamkowych

(stałoprzecinkowych).

I

Rejestr stanu (SREG) jest uaktualniany po każdej operacji

ALU.

Wyszukiwarka

Podobne podstrony:

Programowanie mikrokontrolerów ATmega16

Programowanie mikrokontrolerów 2 0 pl

ZL5PRG Programator mikrokontrol Nieznany

BIZNESPLAN dla programu promocj Nieznany (16)

AVR i ARM7 Programowanie mikrokontrolerow dla kazdego avrar7

Podstawy Programowania Mikrokontrolera 8051

Programowanie mikrokontrolerow 8051 w jezyku C

Galka Galka Podstawy Programowania Mikrokontrolera 8051

Podstawy programowania mikrokontrolera 8051

Program Konwergencji 2011 dla PL

Podstawy programowania mikrokontrolerów AVR8 w środowisku AVR Studio 4

Podstawy programowania mikrokontrolera 8051(300dpi)

Programowanie mikroprocesora Atmega, ELEKTRONIKA, ATMEGA(1)(1)

programowanie mikrokontrolerów

kurs programowania w języku ms basic, Programowanie mikrokontrolerów

PROGRAM KLUBU WIEWIÓRKA 16 - Kopia, Klub Wiewiórka

Podstawy programowania mikrokontrolera 8051

Programowanie mikrokontrolerów za pomocą programatora USBasp

więcej podobnych podstron