RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

Orderable Part

Non - Orderable Part

U900

U702

U701

G_CAP2

SRAM

EEPROM

J 600

15 PIN EXT CONN.

CON.

SPKR

MIC

DATA BUS

ADDRESS BUS

U980

2

1

H6 H7 K9

H9

SENSE

CNTL.

MAN_TEST_AD

DSC_EN_AD

DOWNLINL_AD

BATT_THERM

ISENSE

A1

B2

A2

B3

D9

REAL TIME

CLOCK

Y

9

0

0

A7 B7

3

2

.7

6

8

K

H

z

S

P

R

-

S

P

R

+

A

L

R

T

O

U

T

ALRT_VCC

REG.

V2

REG.

V3

REG.

VBOOST1

REG.

L901

B+

V_BOOST1

LS_V1

V2

V3

VREF

REG.

VREF

2.775V, for WhiteCap logic outputs, RAM, FLASH, EEPROM

1,8V, for WhiteCap

VSIM

REG.

VSIM1

V1

5.0V, for DSC Bus, Negative Voltage Regulator

Internal GCap use only (VSIM1, LS_V1)

3.0 or 5.0V, for SIM Card Circuit

P

A

_

D

R

V

RESET

2.775V,for GCAP

K5 E10

B10

J5

C6

B5

G9

A6

A10, C10

F7

C7

SENSE

BATT+

EXT_B+

14

1

3

10

VR830

5

RS232_TX

RS232_RX

6

7

DSC_EN

13

12

11

UPLINK

DOWNLINK

GND

GND

GND

RX_ACQ

RX_EN

TX_KEY

DM_CS

TX_EN

CLK_SELCT

RESET

M

A

G

IC

_

1

3

M

H

z

G

C

L

K

A1

C1

E2

E1

E3

E4

BKLT_EN

J700

GND

BKLT+

V2

DP_EN

RESET

DP_EN

HS_INT

KEYBOARD

KBR0, KBR1, KBR2

KBC0, KBC1, KBC2,KBC3

PWR_SW

KBR0, KBR1, KBR2

KBC0, KBC1, KBC2, KBC3

( Keyboard )

CLK

PD

SIM_I/O

VSIM1

2

6

4

1

5

LEVEL

EXT_B+

D10

DEEP SLEEP

P2

( WhiteCap )

( GCAP2 )

PWR_SW

C8

LS1_IN

LS2_IN

LS3_TX

LS3_RX

K7

G6

K10

LS1_IN

LS2_IN

LS3_TX

LS3_RX

H8

J900

SIM

Con.

SHIFT

( SDTX ) BDX

( TX_CLK ) BCLKX

from / to MAGIC

( SCLK_OUT ) BCLKR

( SDFS ) BFSR

( SDRX ) BDR

STDBY

CIRCUIT

LS_V1

V1

U700

WHITE_CAP

D6

A6

J6

SPI

INTERFACE

TIMER

SPI

INTERFACE

K5 G14

K2

L6

E10

H2, H3, H1

K1, J4, J3, J2

UART

INTERF.

M

E

M

O

R

Y

I

N

T

E

R

F

A

C

E

E8

D6

E1

E6

SIM

INTER

FACE

CTM

MODULE

DSC

SERIAL

INTER

FACE

DSP

CHARGE

A / D

CTM

CPU

C6

A2

A3

B4

C4

F3

V2

V3

C14, D4, E12, H4, J10, K6, N12

B5, B9, B10, G12, K14, L11, N8

J650

V2

HEAD_INT

J2

ALRT

Q938

J9

Q939

B

K

L

T

_

E

N

BKLT+

CR901

F6

J8

J7

Logic Control

A

U

D

IO

S

P

I

G

C

A

P

S

P

I

D2

C3

EPROM

FLIP CON.

7, 9, 10, 11, 13,

14, 15, 17

D7 - D0

2, 6 ,24, 26

3, 4, 6, 12, 16

22

21

1

R_W

18

19

A0

RTC_BATT

27

HS_INT

( WhiteCap )

BKLT+

V2

( Q938 )

( GCAP2 )

R

T

C

_

B

A

T

T

D6

VIBRA CON.

J810

J811

U801

VIB_EN

B+

1

5

4

Q805

Q805

LED_RED

LED_GRN

1

2

3

4

5

6

V2

( GCAP2 )

( WhiteCap )

( WhiteCap )

V2

V2

CE0

CE1

CE2

CE3

R_W

( SPI_DATA ) DX1

( SPI_CLK ) MOSPI_CLK1

( CE ) MQSPI_CS1

( MAGIC SPI )

M7

M8

L8

D6, E1

B2

A1

G6

A4, A6, F6

D7

F8

C9

E9

D11

D9

A9

HEADSET

STDBY

G4

C4

M4

RESET

B4

E3

E2

D2

E4

F5

C3

( Flip Con. )

R_W

( Flip Con. )

K4

VIB_EN

KEYPAD

INTERFACE

DISPLAY

LED_RED

LED_GRN

M3

M2

LS_V1

N6

-5V

G

C

A

P

_

C

L

K

1

3

M

H

z

D7

F5

-5V_EN

R932

EXT_B+

ISENSE

Q932

4

CHRGC

3

1, 2, 5, 6

BATT+

EXT_B+

4

J604

BATT_SER_DATA

3

GND

1

U950

V2

2

THERM

BATT CON.

Q942

SELECT

F10

1, 2, 3

B+

4

6-8

CR940

1

2

4

D9

E8

U901

H5

A4

5

2

1

HEAD_INT

N3

H3

Audio

Codec

Interface

SPI

INTERFACE

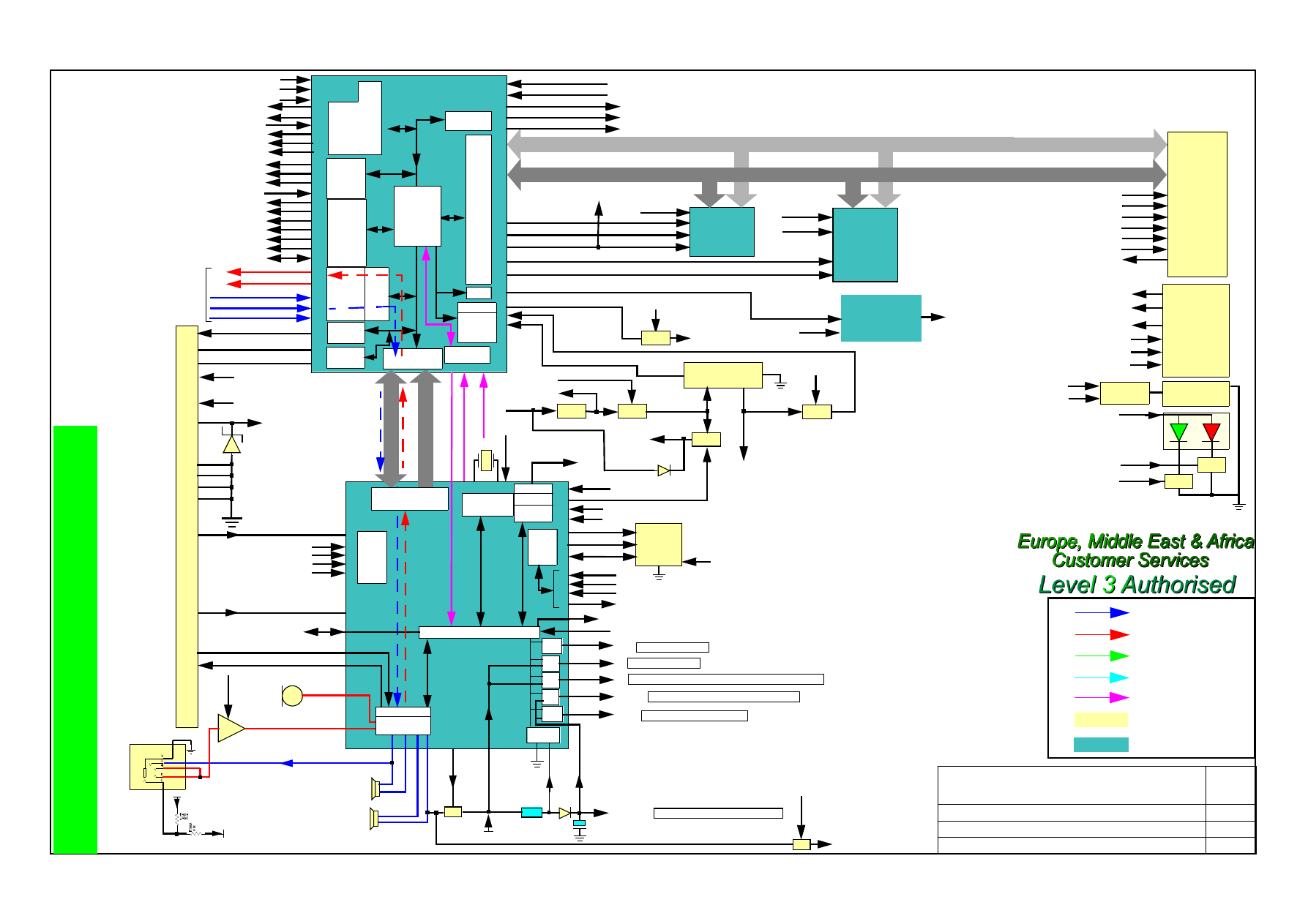

EUROPE MIDDLE EAST & AFRICA

CUSTOMER SERVICES

29.04.99

LEVEL 3 AL Block Diagram

Rev. 1.5

Dualband Kramer

Ralf Lorenzen, Michael Hansen, Colin Jack, Ray Collins Page1

D

U

A

L

B

A

N

D

K

R

A

M

E

R

15

GND

G5

ON / OFF

9

BATT_FDBK

SW_RF

4

2

8

EXT_CHG_EN

ISENSE

CHRGC

B

A

T

T

_

T

H

E

R

M

BATT_PD

B

A

T

T

_

P

D

SW_RF

A1

U401

U101

SWITCH

CONTROL

DET

8

12

11

10

7

1, 3

2

4, 14

SAT.

EXT ANT

FL450

RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

1805-1880MHz

Orderable Part

Non - Orderable Part

FL460

925-960MHz

Q461

Q451

FL465

FL470

Q1254

B

E

C

Q1254

B

E

C

SW_VCC

Q242

B+

E

E

B

B

RF_V1

RF_V2

C

C

to WhiteCap

from WhiteCap

Q240

800MHz

RX

LOCAL

OSCILLATOR

CR259

CR230

VRef

A9

E9

Osc.

circuty

discrete

U913

MAGIC

Q1255

PLL

H7, C8; J1

400 MHz

Q490

B

C

C

FL457

G1

S

W

IT

C

H

S

W

IT

C

H

J8

V1

V1

C8

SF_OUT

CR250

C257

Q253

Q255

Q262

C1

MIX_275

DCS_LNA275

MIX_275

GSM_LNA275

B

B

C

C

P

A

C

_

2

7

5

M

IX

_

2

7

5

TX_KEY_OUT

SAT_DETECT

AOC_DRIVE

DET_SW

PAC_275

RF_IN

U340 PAC

PA

CONTROL

TX_KEY_OUT

SAT_DETECT

AOC_DRIVE

DETECT_SW

B6

C5

A5

B4

SPI

TX

MODULATION

A1

A3

STEP

ATT.

DEMODULATION

SPI

RX

SPI

INTER

FACE

J2

G7

G5

H4

J3

( SDTX ) BDX

( TX_CLK ) BCLKX

( SPI_DATA ) DX1

( SPI_CLK ) MOSPI_CLK1

( CE ) MQSPI_CS1

F7

G9

G8

( SCLK_OUT ) BCLKR

( SDFS ) BFSR

( SDRX ) BDR

RX_ACQ

TX_KEY

DM_CS

CLK_SELCT

26MHz

H9, J9

J7

J6

MAGIC_13MHz

Startup

PHASE

DET

Ref.

1 /2

MUX

LOGIC

CONTROL

H8

J4

H5

CR251

DCS_VCO

RVCO_250

G

P

0

4

F9

GSM LNA

S

U

P

E

R

F

IL

T

E

R

R

E

G

.

GSM_LNA275

DCS_LNA275

GSM / DCS SELECT CIRCUIT

from WhiteCap

to WhiteCap

from WhiteCap

925-960MHz

EGSM: 880-915Mhz

DCS: 1710-1785MHz

1805-1880MHz

RX VCO

EGSM: 1325-1360MHz

DCS: 1405-1480MHz

EGSM: 880-915Mhz

DCS: 1710-1785MHz

CIRCUIT

DCS_SEL

13MHz

A7

C7

F2

F1

H1

H2

C4

Q344

SF_OUT

RVCO_250

LOGIC

CONTROL

Q343

TX_EN

TVCO_250

U250

TX VCO

4

2

6

D

_

T

X

_

V

C

O

G

_

T

X

_

V

C

O

P

A

C

_

2

7

5

12

10

6

Q400

C

B

Q300

C

B

Q455

C

B

U300

U400

DCS

PA

GSM

PA

1

0

-1

5

1

0

-1

5

2

1, 7

7

2, 8

1

3

4

5

FL300

SHIFT LEVEL CIRCUIT

-5V

U341

NPA_MUTE

PA_B+

PAC_275

U341

PA_B+

DM_CS

B+

2

CR306,307

G

S

M

_

P

IN

D

IO

D

E

10

5

6

G

S

M

_

L

N

A

2

7

5

D

C

S

_

L

N

A

2

7

5

4

7

2

9

CR300

CR301

Y230

G6

( RX VCO, GSM/DCS SELECT )

( GSM / DCS SELECT )

1-3

4

5

G_TX_VCO

D_TX_VCO

GSM_PINDIODE

NPA_MUTE

TVCO_250

PAC_275

DCS_VCO

MIX_275

D

U

A

L

B

A

N

D

K

R

A

M

E

R

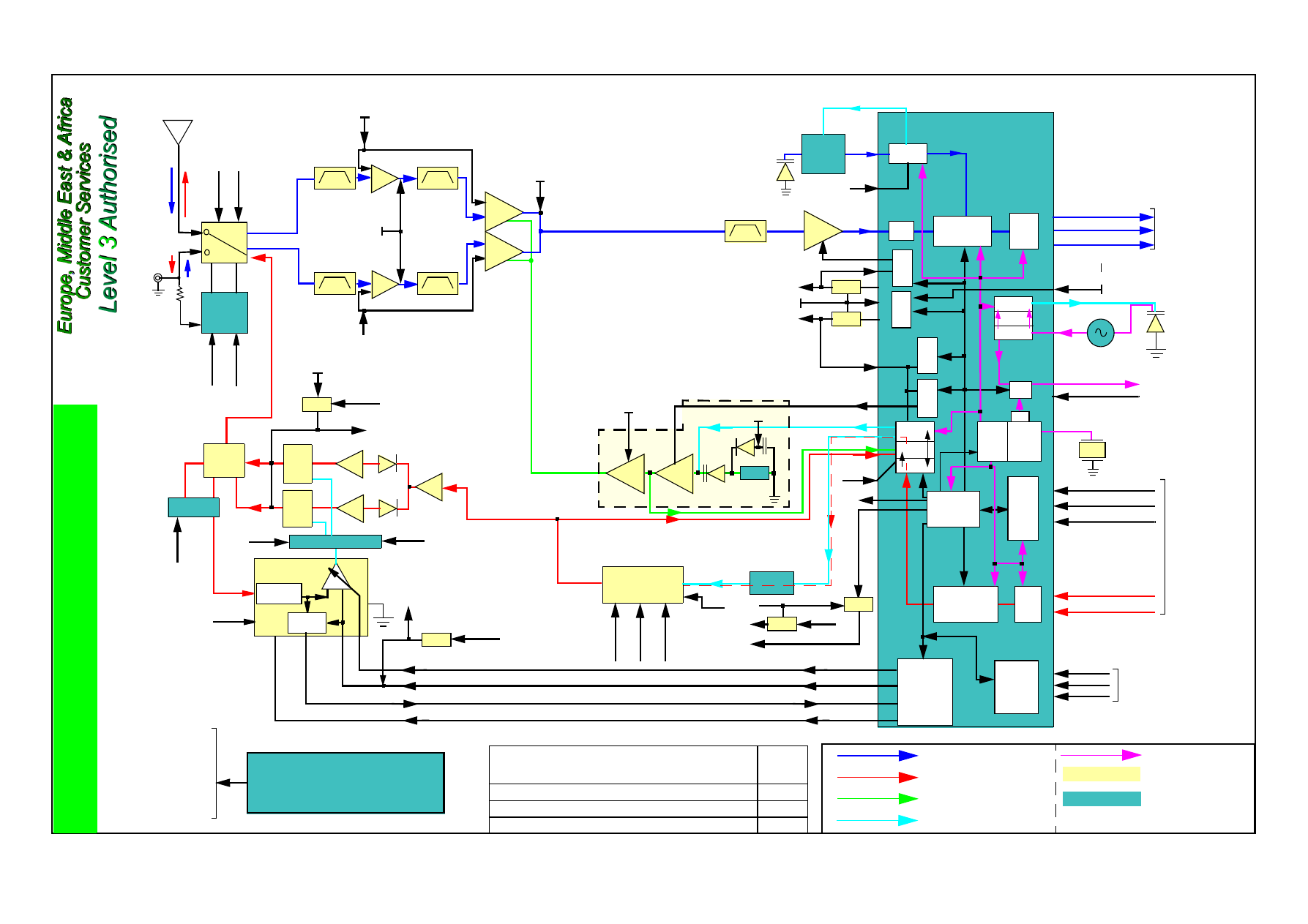

EUROPE MIDDLE EAST & AFRICA

CUSTOMER SERVICES

29.04.99

LEVEL 3 RF Block Diagram

Rev. 1.5

Dualband Kramer

Ralf Lorenzen, Michael Hansen, Colin Jack, Ray Collins Page1

TX LOOP

FILTER

B1

C1

REF. OSC.

26 MHz

Prog.

Divider

200KHz

REF.

Divider

200KHz

AFC

RXI

RXQ

TXI

TXQ

PLL

DET

PHASE

Divider

Wyszukiwarka

Podobne podstrony:

board layouts

W206 W213 board layout

Board Layout H23

Board Layout H13

Board Layout 2

A Practical Guide to High Speed Printed Circuit Board Layout

Board Layout SiFl58 V600 A3 C L3 1 0 040123074622

Board Layout 3

Board Layout V3 06 Razr FLIP 8488650Z01 A3 C L3 O

Board Layout 4

Board Layout 3

Board Layout V3 06 Razr MAIN 8488648Z01 A3 C L3 O

Board Layout Z8 Layout A3 C L3 8403591D06

Board Layout V3 05 A3 C L3 V8471201B01

Board Layout W510 Pemba MAIN Board Layout A3 C L3 rO

C168 Board layout

Board Layout W510 Pemba FLIP A3 C L3 rO

więcej podobnych podstron