Laboratorium układów elektronicznych |

||

|

Temat : Układy logiczne cz.2 |

|

|

|

|

Cel ćwiczenia:

Celem pierwszego ćwiczenia było badanie i realizacja przerzutnika RS, JK, D z wykorzystaniem bramek NAND oraz zapisanie tablicy wzbudzeń. Kolejnym ćwiczeniem było zaprojektowanie i zrealizowanie licznika synchronicznego liczącego do 10

Przerzutnik RS

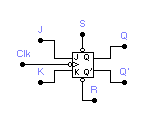

Przerzutnik JK

Przerzutnik D

Licznik synchroniczny

Uwagi i wnioski

Na ostatnich zajęciach laboratoryjnych badaliśmy przerzutniki RS zbudowane z bramek NAND, przerzutnik typu D oraz przerzutnik JK- z wejściami RS I licznik dziesiętny synchroniczny oparty na przerzutnikach JK oraz kilka dodatkowych bramek.

Przerzutniki są to układy których stan na wyjściu zależy od trzech zmiennych - dwóch stanów na wejściu I od poziomu sygnału w poprzednim takcie zegara.

Przerzutnik RS jest wykonany z bramek NAND lub NOR. Posiada wejścia R (reset) i S (set) i dwa wyjścia Q i Q'. W przerzutnika tych niedozwolony jest stan wysoki lub niski na obydwu wejściach (w zależności od typu bramek przerzutnika). Wejście R powoduje zerowanie wyjścia Q niezależnie od poprzedniego stanu na wejściu R, natomiast wejście S jest ustawieniem wyjścia.

Przerzutnik JK podobny jest do działania przerzutnika RS - z tą jednak różnicą, że nie posiada niedozwolonych stanów na wyjściu. Wyposażony jest także w wejścia R i S i Clk. Zmiana stanów na wejściu R lub S powoduje zerowanie lub ustawienie wyjścia przerzutnika niezależnie od poziomu sygnału Clk. Połączenie wejść J I K tworzy przerzutnik typu T.

Utworzenie przerzutnika D (latch) polegało na dołączeniu inwentera wykonanego z bramek NAND do wejścia K przerzutnika JK. Wejście J natomiast było wejściem ustawiającym, a Clk taktującym.

Ostatnim zbudowanym układem był licznik dziesiętny synchroniczny na przerzutniku JK. Licznik ten pozbawiony był wady jakie mają liczniki asynchroniczne, gdzie poszczególne czasy ustalania przerzutników dodają się tworząc opóźnienie, które ogranicza prędkość działania układu. Liczniki tego typu mają wszystkie wejścia taktujące sterowane jednocześnie - równolegle, a nie oddzielnie - szeregowo. Posiadają ten jednak minus, że aby uzyskać sygnał w kodzie BCD, konieczne jest zbudowanie dodatkowego układu logicznego z bramek NAND.

R |

S |

Q n |

Q n+1 |

L |

L |

L |

* |

L |

L |

H |

* |

L |

H |

L |

H |

L |

H |

H |

H |

H |

L |

L |

L |

H |

L |

H |

L |

H |

H |

L |

L |

H |

H |

H |

H |

Wyszukiwarka

Podobne podstrony:

Układy logiczne cz.1, Laboratorium układów elektronicznych

Elektronika- UKŁADY LOGICZNE CZ. II.DOC, LABORATORIUM Z ELEKTRONIKI .

Badanie cyfrowych bramek logicznych2, Laboratorium układów elektronicznych

Elektronika- Układy logiczne cz.1- dekodery, trans-latory.DOC, Wydz. E i A Grupa

Elektronika- Układy logiczne cz.1- dekodery, trans-latory.DOC, Wydz. E i A Grupa

Elektronika - Układy logiczne cz 2, Politechnika Opolska, sprawozdania, zachomikowane, Elektronika i

Elektronika - Układy logiczne cz 1, Politechnika Opolska, sprawozdania, zachomikowane, Elektronika i

Elektronika- Stabilizator napiecia stałego o działaniu nieciągłym, Laboratorium układów elektroniczn

Elektronika- Stabilizator napiecia stałego o działaniu nieciągłym, Laboratorium układów elektroniczn

więcej podobnych podstron