POLITECHNIKA CZĘSTOCHOWSKA

TEMAT :

PAMIĘĆ OPERACYJNA

MSU INFORMATKA ROK II grupa 2

Krzysztof Drozd

Piotr Dyduch

Budowa pamięci

Pamięć operacyjna komputera - zwana pamięcią RAM (Random Accesss Memory) służy do przechowywania danych aktualnie przetwarzanych przez program oraz ciągów rozkazów z których składa się ten program. Pamięć RAM jest pamięcią ulotną, co oznacza, że po wyłączeniu komputera informacja w niej zawarta jest tracona. Pojedyncza komórka pamięci RAM zawiera kondensator, który naładowany do pewnego napięcia, przechowuje jeden bit danych. Kondensator jednak rozładowuje się. Należy więc systematycznie odświeżać zawartość komórki, poprzez zaadresowanie jej i ponowne doładowanie kondensatora. Proces ten nosi nazwę odświeżania i musi być wykonywany cyklicznie.

Pamięć charakteryzowana jest przez dwa istotne parametry: pojemność oraz czas dostępu. Pojemność pamięci jest funkcją liczby linii adresowych i wielkości komórki. Czas jaki upłynie od momentu zaadresowania komórki do uzyskania zapisanej w tej komórce informacji nazywa się czasem dostępu. Czasy dostępu we współczesnych pamięciach są rzędu nanosekund.

Budowa komórki pamięci.

Pamięć operacyjna komputera jest pamięcią dynamiczną. Budowa jej komórki wygląda w sposób przedstawiony na poniższym rysunku:

Dostęp do informacji zawartej w kondensatorze CS staje się możliwy po włączeniu tranzystora T typu NMOS, czyli po doprowadzeniu do linii wiersza napięci o wartości UDD. Gdy tranzystor zostanie włączony nastąpi przemieszczanie ładunku pomiędzy kondensatorem CS i linią bitu. Powstała w ten sposób niewielka zmiana napięcia na linii bitu musi więc zostać wykryta, oraz wzmocniona poprzez wzmacniacz o dużym wzmocnieniu napięciowym. Po każdorazowym odczycie komórki następuje odświeżenie jej zawartości poprzez doładowanie lub rozładowanie kondensatora. Znacznie prostszym jest cykl zapisu informacji. Sprowadza się on wyłącznie do naładowania bądź rozładowania kondensatora CS. Wspomniany wcześniej sposób odświeżania pamięci przy odczycie jej zawartości nie jest jednak wystarczający. Każda pamięć ma określoną częstotliwość odświeżania zapewniającą jej prawidłowe działanie. Częstotliwość ta podawana jest przez producenta jako parametr katalogowy.

Dostęp do pamięci

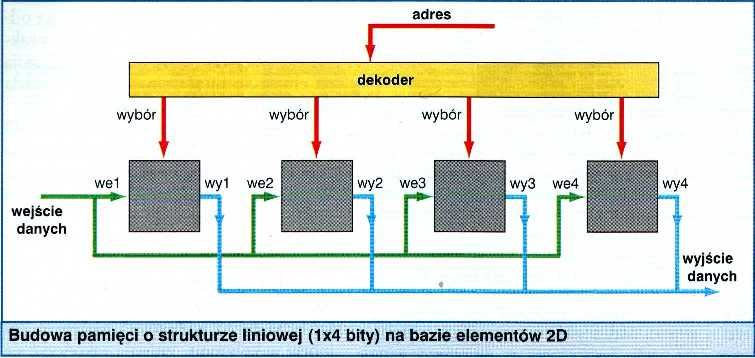

Aby zorganizować komórki pamięci w sprawnie funkcjonujący układ, należy je odpowiednio zaadresować. Najprostszym sposobem jest zorganizowanie pamięci liniowo - jest to tak zwane adresowanie 2D. Do każdej komórki podłączone jest: wejście, sygnał wybierania pochodzący z dekodera oraz wyjście.

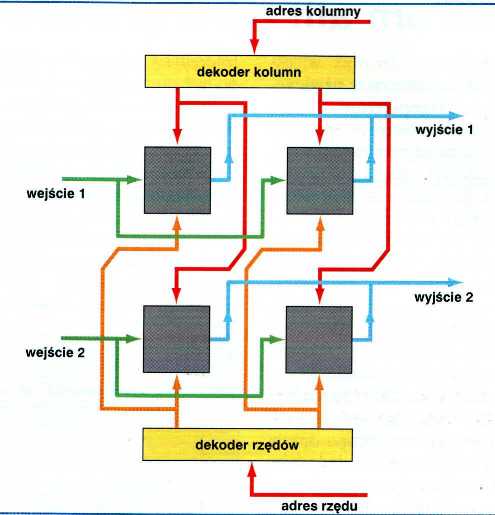

Nieco innym sposobem jest adresowanie przy użyciu tzw. matrycy 3D. Pamięć organizuje się tutaj dzieląc dostępne elementy na wiersze i kolumny. Dostęp do pojedynczego elementu pamiętającego (słowa) można uzyskać po zaadresowaniu odpowiedniego wiersza i kolumny.

Dlatego też komórka RAM obok wejścia i wyjścia musi dysponować jeszcze dwoma sygnałami wybierania, odpowiednio z dekodera kolumn i wierszy. Zaletą pamięci adresowanej liniowo (2D) jest prosty i szybszy dostęp do poszczególnych bitów niż w przypadku pamięci stronicowanej (3D), lecz niestety, przy takiej organizacji budowanie większych modułów RAM jest kłopotliwe. Dlatego też w przemyśle stosuje się zazwyczaj układy pamięci zorganizowanej w matrycę 3D, pozwala to na nieskomplikowane tworzenie większych modułów o jednolitym sposobie adresowania. Możliwe jest również łączenie obu sposobów adresowania stosując np. kilka modułów typu 3D, ale dostęp do każdego z nich jest realizowany jest liniowo.

Pamięci operacyjne RAM wykonywane są w postaci układów scalonych. Wyjścia takiego układu przedstawia poniższy rysunek.

OE# - zezwolenie na odczyt

WE# - zezwolenie na zapis

CE# - sygnał wyboru układu

RAS# i CAS# - wejścia sterujące wprowadzaniem adresu do układu

Schemat blokowy obrazujący sposób adresowania pamięci przedstawia poniższy rysunek.

Adres słowa, które chcemy zaadresować składa się z dwóch części zwanych adresem wiersza i adresem kolumny. Takie podejście zmniejsza ilość potrzebnych wyprowadzeń szyny adresowej i upraszcza konstrukcję dekoderów adresu.

Poprawne zaadresowanie pamięci DRAM wymaga wykonania po kolei następujących czynności:

podanie starszej części adresu na linie adresowe, a następnie wytworzenie aktywnego zbocza sygnału RAS powodującego zapamiętanie tego adresu w rejestrze zatrzaskowym adresu wiersza,

odmierzenie wymaganego opóźnienia czasowego,

podanie młodszej części adresu na linie adresowe i wytworzenie aktywnego zbocza sygnału CAS, powodującego zapamiętanie jego adresu w rejestrze zatrzaskowym adresu kolumny.

Następnie, zgodnie z sygnałami sterującymi OE i WE, wykonywana jest operacja zapisu lub odczytu wybranego słowa, po czym odmierzane jest kolejne wymagane opóźnienie czasowe przed rozpoczęciem następnego cyklu, potrzebne na doładowanie komórek.

Dostęp w trybie stronicowania.

Pamięć pracująca w trybie stronicowania wymaga pewnych dodatkowych układów sterujących. Początek dostępu do pamięci jest prawie identyczny jak w zwykłej pamięci DRAM. Najpierw podawany jest adres wiersza, który jest zatrzaskiwany w rejestrze zatrzaskowym wiersza wewnątrz pamięci. Adres ten jest zapamiętywany. Następnie podawany jest adres kolumny, zatrzaskiwany w rejestrze zatrzaskowym kolumny. Kolejny dostęp różni się od poprzedniego. Po podaniu nowego adresu jego część będąca adresem wiersza jest porównywana z zapamiętaną zawartością adresu wiersza. Jeśli jest ona identyczna, układ sterowania pamięcią DRAM utrzymuje stan niski sygnału RAS do końca bieżącego cyklu odczytu. Dla pamięci DRAM pracującej w trybie stronicowania oznacza to, że kolejny dostęp dotyczy słowa położonego w tym samym wierszu, należy więc wczytać tylko adres kolumny.

Dostęp w trybie seryjnym (Burst)

Dostęp ten wykorzystywany jest przy współpracy pamięci DRAM z pamięcią cache. W trybie tym adres wiersza również pozostaje bez zmian, natomiast adres kolumny przy każdym kolejnym dostępie jest większy o jeden. W zwykły sposób podajemy więc adres pierwszego słowa pamięci, a następnie podajemy wyłącznie aktywne zbocza sygnału CAS. Odpowiedni adres jest generowany wewnątrz układu pamięci.

Z powyższych mechanizmów wynika np. możliwość pracy pamięci SDRAM w sekwencji 5-1-1-1 (rodzaje pamięci zostaną omówione w dalszej części referatu). Podane liczby określają ilość cykli magistrali potrzebnych do wykonania kolejnych operacji na pamięci.

Mechanizm stronicowania

Mechanizm stronicowania pamięci zaimplementowany został dopiero w procesorach 80386 i stanowił przełom w komputerach typu PC. Umożliwił on sklejanie fizycznie rozproszonych obszarów pamięci w ciągłe bloki, oraz implementację pamięci wirtualnej. Mechanizm ten dzieli cały dostępny 4G obszar na strony wielkości 4KB lub 4 MB, które za pomocą tablic stron zmieniają swoje położenie w przestrzeni adresowej widzianej przez programy.

Translacja adresu liniowego na fizyczny w przypadku 4-kilobajtowych stron przebiega w następujących etapach:

10-bitowa część adresu liniowego AL31-AL22 wybiera jedną z 1024 pozycji w katalogu tablic stron.

Zawartość wybranej pozycji w katalogu tablic wskazuje na jedną z 1024 tablic stron. Bity AL21-12 wybierają jedną z 1024 pozycji w wybranej tablicy stron. Wybrana pozycja w tabeli stron podaje adres początkowy 4-kilobajtowej strony, w której znajduje się poszukiwana informacja.

Bity adresu liniowego AL11-AL0 stanowią przesunięcie w wybranej stronie, wskazując na poszukiwaną informację.

Jeśli poszukiwana strona jest nieobecna w pamięci operacyjnej, w rejestrze CR2 procesora umieszczany jest adres liniowy brakującej strony i generowany jest wyjątek 14 - błąd strony. Program obsługi tego wyjątku powinien spowodować wczytanie brakującej strony z dysku i zmodyfikowanie odpowiedniej pozycji w tabeli stron.

Rodzaje pamięci operacyjnych

Moduły SDRAM (Synchronous Dynamic Random Access Memory), które pojawiły się w końcu 1996 roku, obecnie dominują na rynku układów pamięciowych. Ich wydajność jest zadowalająca zasadniczo we wszystkich zastosowaniach. Ten, komu zależy na większych osiągach, powinien zastosować moduły Rambus lub DDR-SDRAM.

Zakres oferty. Każdy producent układów pamięciowych wytwarza moduły SDRAM. Są oferowane praktycznie przez wszystkich producentów komputerów. Układy SDRAM, zwane również DIMM-ami, są dostępne w zakresie pojemności od 32 do 256 MB. Znacznie rzadziej mają pojemność 512 MB. Najlepszy stosunek ceny do pojemności oferują obecnie moduły 128 MB. Istnieje kilka wariantów wydajnościowych pamięci SDRAM. Czynnikiem decydującym podczas doboru jest częstotliwość magistrali. Moduły przeznaczone do szyny 66 MHz (noszą miano PC 66) już zniknęły z rynku. Obecnie popularne są układy do magistral 100 MHz (PC 100) i 133 MHz (PC 133). Różnica w cenie jest niewielka w przypadku układów o pojemności nie przekraczającej 128 M8. Przy większych pojemnościach znacznie tańsze okazują się moduły PC 100.

Wydajność modułów. Przy magistrali o szerokości 64 bitów taktowanej z częstotliwością 66 MHz moduły SDRAM osiągają przepustowość rzędu 500 MB/s. W przypadku częstotliwości 100 MHz transfer danych wzrasta do około 800 MB/s, a przy 133 MHz do około 1,06 GB/s. Jednak szybszy transfer w pamięci nie zawsze przekłada się na zwiększenie łącznej wydajności systemu. Jak wykazują benchmarki, pamięć SDRAM PC 100 jest o około 12 procent szybsza od SDRAM PC 66 (testowano za pomocą programu SysMark 98 w systemie z procesorem Pentium II 300). Przyczyną niewielkiej różnicy są wyjątkowo szybkie pamięci podręczne pierwszego i drugiego poziomu, które przechwytują blisko 90 procent odwołań do pamięci głównej.

Kompatybilność z chipsetami i płytami głównymi. Ze względu na dużą popularność pamięci SDRAM każdy producent chipsetów oferuje przynajmniej jeden aktualny model, który współpracuje z pamięcią tego typu. Również oferta płyt głównych jest bogata. Co najmniej jedna płyta każdego producenta akceptuje układy SDRAM. Podobnie jest w sektorze komputerów.

Zasady działania modułów. Komunikacja między chipsetem i pamięcią odbywa się za pośrednictwem magistrali, która działa zgodnie z częstotliwością systemową. Dzięki temu niepotrzebne stają się czasochłonne procesy uzgadniania (tzw. handshaking), konieczne w starszych typach pamięci DRAM: FPM, EDO i BEDO. Z tego względu w pamięci SDRAM prawie wcale nie występują cykle oczekiwania. Na dodatek układy SDRAM dysponują co najmniej dwoma bankami (czyli grupami bloków) pamięci. Dzięki temu kontroler zintegrowany w układzie SDRAM może przykładowo przygotowywać jeden bank do operacji odczytu/zapisu, podczas gdy drugi bank przeprowadza taką operację. Dlatego czas regeneracji (tzw. precharge time) nie opóźnia transmisji. Aktualne układy SDRAM są wyposażone w maksymalnie cztery wewnętrzne banki pamięci. Operacje odczytu/zapisu w SDRAM są rozdzielane na poszczególne układy scalone. W odróżnieniu od FPMDRAM i EDO-DRAM chipset płyty głównej przekazuje modułowi pamięci SDRAM polecenie (odczyt lub zapis) wraz z adresem komórki (wiersz I kolumna). Elementy logiczne układu SDRAM przejmują sterowanie, a chipset nie bierze udziału w odczycie komórki pamięciowej, jak ma to miejsce w FPM-DRAM i EDO-DRAM. Dzięki temu, wykonując operacje w trybie pakietowym (tzw. burst mode), SDRAM samodzielnie ustala nieodzowne adresy, podobnie jak BEDO-DRAM. Następnie przeprowadza żądaną operację z użyciem kilku banków pamięci. Takie potokowanie operacji umożliwia udostępnianie danych wraz z każdym cyklem. Gdy zamontujesz nowe moduły DIMM, zostaną automatycznie rozpoznane i przygotowane do użytkowania. Nieodzowne do tego informacje BI0S znajduje w tzw. układzie SPD. Są w nim zgromadzone różne parametry, takie jak synchronizacja, długość przesyłanych bloków i rodzaje odświeżania.

Parametry techniczne. Moduły SDRAM stanowią udoskonalenie pamięci DRAM, zatem inicjacja odczytu wymaga pięciu cykli, tak jak w EDORAM. Dopiero w trybie pakietowym transmisja odbywa się cykl po cyklu. SDRAM pracuje z synchronizacją trybu pakietowego 5-1-1-1.

Wygląd modułów pamięciowych. SDRAM to 168-stykowe moduły typu DIMM.

Rozszerzalność. Ponieważ SDRAM jest obecnie najpopularniejszym typem pamięci, nie ma problemów z rozszerzaniem zasobów zainstalowanych na płycie głównej peceta. Moduły DIMM są kompatybilne z poprzednikami. Zatem układy SDRAM PC 100 czy PC 133 działają w komputerze z PC 66.

Perspektywy. Pamięć SDRAM ma zapewnioną przyszłość (średnio długą), mimo że nie należy oczekiwać skoków wydajności w nowych modułach. Zapewne w roku 2002 zostaną zastąpione układami DDR-SDRAM.

Podsumowanie. SDRAM to pamięć dla każdego. ten typ pamięci jest obecnie tani i bardzo popularny. Moduły SDRAM o różnej wydajności znajdziesz w prostych, a takżę profesjonalnych komputerach.

Pamięć Rambus zalecamy tylko tym, którzy stawiają na najwyższą wydajność. Stosowanie modułów tego typu ma sens tylko z bardzo szybkim procesorem.

Zakres oferty. Pamięć Rambus jest oferowana w wielu placówkach handlowych, choć zazwyczaj przed zakupem trzeba złożyć zamówienie. Obecnie w sprzedaży są prawie wyłącznie moduły o pojemności 128 MB. Układy scalone w pamięci tego typu są taktowane z częstotliwością 350 lub 400 MHz. Moduły oznaczono napisem PC 700 (w przypadku częstotliwości 350 MHz) lub PC 800 (przy 400 MHz), ponieważ Rambus wykorzystuje oba zbocza sygnału (0-1 i 1-0).

Wydajność modułów. Wprawdzie Rambus dysponuje wąską, bo 16-bitową, szyną transmisji danych, lecz akceptuje skrajnie wysokie częstotliwości (350 i 400 MHz). Na dodatek korzysta zarówno z natężeń, jak i spadków sygnału. Maksymalna prędkość transmisji danych na szynie wynosi 1,6 GB/s i jest osiągana nawet wtedy, gdy na płycie zainstalowano tylko jeden moduł Rambus. Pamięć Rambus-DRAM jest o około 60 procent szybsza od SDRAM PC 133. Jednak ze względu na pamięć podręczną drugiego poziomu, zintegrowaną w aktualnych procesorach, zwyżka wydajności wynosi w praktyce zaledwie 5 procent.

Kompatybilność z chipsetami i płytami głównymi. Obecnie tylko dwa chipsety (Intel 820 i 840) współpracują z pamięcią Rambus. Jednak każdy znany producent płyt głównych ma w ofercie co najmniej jeden model, który akceptuje moduły RIMM. Jeśli chcesz korzystać z układów Rambus, musisz mieć płytę z procesorem Pentium III lub 4. Obecnie brakuje chipsetu do Athlona, który obsługiwałby pamięć Rambus. Oferta komputerów w tym segmencie jest bardzo skromna.

Zasady działania modułów. Pamięć DRDRAM (Direct Rambus DRAM) stosowana w sektorze pecetów została zaprojektowana przez firmy Rambus i Intel. Rambus składa się z trzech elementów. Należy do nich kontroler pamięciowy na płycie głównej, kanał (który umożliwia komunikowanie się z podzespołami pamięciowymi) oraz układy scalone DRDRAM. Kontroler pamięci Rambus potrafi zarządzać maksymalnie czterema kanałami, co pozwala czterokrotnie zwiększyć przepustowość danych. Wspomniany kanał opiera się na 18-bitowej szynie danych, wyposażonej w korektę błędów ECC (Error Correction Code). Bez tej korekty szerokość szyny wynosi 16 bitów. Kanał dysponuje też szyną kontrolną o szerokości 8 bitów. Szyna odwołuje się do wierszy i kolumn w oddzielnych liniach. Dzięki temu możliwe jest adresowanie następnej komórki, podczas gdy trwa transmisja danych zainicjowana poprzednim poleceniem. Każdy podzespół DRDRAM może transmitować dane na całej szerokości kanału. Dlatego kontroler pamięci Rambus nie rozdziela operacji w trybie pakietowym na kilka układów scalonych, jak w pamięci SDRAM. Właściwa transmisja danych odbywa się w następujący sposób. Korzystając z szyny kontrolnej, kontroler pamięci wybiera układ scalony, w którym ma nastąpić odczyt lub zapis danych. Dane te zostają przesłane poprzez szynę danych. Zanim procesor lub moduł DRDRAM będzie mógł przetwarzać otrzymane dane, chipset płyty głównej musi je skonwertować. Procesor przyjmuje bowiem partie 64 bitów, a Rambus partie po 16 bitów.

Parametry techniczne. Niełatwo tak zaprojektować płytę główną, aby doskonale radziła sobie z wysokimi częstotliwościami taktowania pamięci Rambus. Z tego względu stosuje się specjalny standard o nazwie RSL. Wymaga on stosowania krótkich ścieżek sygnałowych oraz niskiego napięcia rzędu 1,8 V i nakazuje terminować szynę danych i szynę kontrolną, aby wyeliminować odbicia sygnałów.

Wygląd modułów pamięciowych. Pamięć Rambus-DRAM jest dostępna w modułach typu RIMM. Zgodnie ze specyfikacją, muszą być wyposażone w metalową płytkę, która, pełniąc funkcję radiatora, umożliwi odprowadzanie ciepła z układów scalonych. Jeden moduł RIMM może zgromadzić do 16 podzespołów pamięciowych DRDRAM i należy go uważać za element składowy kanału Rambus. Każdy taki kanał może się składać z ) jednego lub dwóch modułów RIMM. Jeśli w którymś z gniazd nie ma modułu RIMM, trzeba umieścić w nim specjalną zaślepkę C-RIMM, aby zapewnić ciągłość linii danych i linii sterowania, zachowując w ten sposób strukturę magistrali.

Rozszerzalność. Maksymalna ilość pamięci Rambus, którą można zainstalować w komputerze, wynosi obecnie 256 MB. Na rynku są bowiem tylko moduły o pojemności 128 MB, a dostępne płyty główne wyposażono w dwa gniazda pamięciowe. W pierwszym kwartale 2001 roku pojawią się moduły 256 MB. Wówczas rozszerzalność pamięci Rambus zostanie podwojona do 512 MB.

Perspektywy. Mimo dużego zaangażowania Intela kariera pamięci Rambus stoi pod znakiem zapytania. Większość producentów podzespołów pamięciowych wybiera bowiem DDRSDRAM. Również konkurencyjny AMD faworyzuje pamięć SDRAM i DDR-SDRAM. Podsumowanie. Jeśli zależy Ci na maksymalnych osiągach a cena nie gra roli, idealnym wyborem jest pamięć Rambus. Dopóki na rynku nie pojawi się DDR-SDRAM, ten typ pamięci będzie górować nad innymi pod względem wydajności. Jednak chwilowo nie zainstalujesz w pececie więcej niż 256 MB. Na dodatek nie jest dostępna dla posiadaczy komputerów z procesorami Athlon.

DDR-SDRAM (Double Data Rate SDRAM) to nowość na rynku pamięci do komputerów klasy PC. Ten typ pamięci jest przeznaczony dla profesjonalnych użytkowników, którzy szukają najwyższej wydajności. SDRAM w wersji PC 266, taktowana z częstotliwością 133 MHz i wykorzystująca oba zbocza (tj. natężenia i spadki) sygnału, ma działać o 31 procent szybciej od Rambus-DRAM.

Zakres oferty. Pamięć DDR-SDRAM była dotychczas stosowana wyłącznie w kartach graficznych. Wiele firm produkuje DDR-SDRAM, m.in. Infineon, Micron i Samsung Electronics.

Wydajność modułów. Przy częstotliwości magistrali 100 lub 133 MHz pamięć DDR-SDRAM oferuje maksymalną przepustowość rzędu 1,6 GB/s (PC 200) lub 2,1 GB/s (PC 266).

Kompatybilność z chipsetami i płytami głównymi. Chipsety obsługujące pamięć DDR-SDRAM wprowadzają firmy ALI (chipset ALI M1647), AMD (AMD 760) i VIA (Apollo Pro 2000 K7-DDR, Apollo Pro 2000 P6-DDR). Z głównych producentów chipsetów tylko Intel zamyka się przed tą technologią.

Zasady działania modułów. DDR-SDRAM polega na stosunkowo prostym ulepszeniu technologii SDRAM, daje jednak znaczny przyrost wydajności. Pamięć ta jest dwukrotnie szybsza od modułów SDRAM z identyczną częstotliwością taktowania. W odróżnieniu od nich DDR-SDRAM transmituje dane nie tylko przy wzroście, lecz również przy spadku sygnału. Krytyczny wpływ na wydajność mają związane z tym opóźnienia czasu przelotu między liniami danych i sygnałem taktującym. Z tego względu do synchronizacji transmisji danych używana jest nie tylko częstotliwość systemowa. DDR-SDRAM udostępnia do tego celu dodatkowy sygnał o nazwie DQS. Pozwala obejść problem pojawiający się wraz z utratą synchronizacji na magistrali między chipsetem i pamięcią. W przypadku polecenia odczytu DDR-SDRAM generuje sygnał DQS. Sterując nim w odpowiedni sposób, informuje chipset, kiedy na magistrali (danych) znajdują, się dane związane z określonym natężeniem lub spadkiem sygnału. Zapis odbywa się w odwrotny sposób. Chipset generuje sygnał DQS, dając znak pamięci DDR-SDRAM, w którym momencie na magistrali znajdują się dane do przejęcia przez pamięć. Zapisywane dane muszą się znajdować przy odpowiednich stykach modułów pamięciowych już w momencie przeskoku sygnału DQS.

Parametry techniczne. Pomijając sygnał DQS oraz modyfikacje w elementach logicznych jednostki sterującej, DDR-SDRAM działa na tych samych zasadach co aktualna pamięć SDRAM. Jednak wymaga stosowania specjalnego chipsetu, przystosowanego do współpracy z tego rodzaju pamięcią. Ponadto producenci płyt głównych muszą, zadbać o nadzwyczaj staranną konstrukcję. Aby zapewnić dokładną synchronizację sygnału DQS z liniami magistrali danych (DQ), ścieżki muszą mieć identyczną długość i pojemność. Dzięki temu odchylenia spowodowane wahaniem napięcia lub temperatury otoczenia w takim samym stopniu wpływają na ścieżki DQ i DQS. Pozwala to uniknąć problemów z synchronizacją podczas transmisji danych między chipsetem i modułem pamięciowym.

Wygląd modułów pamięciowych. Na pierwszy rzut oka moduł DDRSDRAM niewiele różni się od swojego poprzednika SDRAM. Są to układy typu DIMM i mają 184 styki, Zależnie od częstotliwości taktowania nazywa się je PC 200 lub PC 266, aby podkreślić dwukrotnie większą prędkość transmisji.

Rozszerzalność. Przypuszczalnie płyty główne z pamięcią DDR-SDRAM będzie można rozbudowywać tak łatwo jak obecne płyty z układami SDRAM. Jednak nie będzie można instalować w nich modułów SDRAM, ponieważ są krótsze (SDRAM: 168 styków, DDR-SDRAM: 184 styki).

Podsumowanie. Pamięć DDR-SDRAM jest dwukrotnie szybsza od SDRAM. Pokonuje nawet Rambus-DRAM.

Jeśli zależy Ci na stosunkowo niewielkim wzroście wydajności i masz płytę główną, która obsługuje (sprawdź w instrukcji) pamięć VC-SDRAM (Virtual Channel SDRAM), zainstalowanie modułów tego typu może się opłacić. Jednak najpierw się dowiedz, czy nie uzyskasz większej wydajności za mniejsze pieniądze, kupując nową płytę główną z procesorem.

Zakres oferty. Układy VC-SDRAM trafiły już na rynek japoński. Znacznie gorzej jest z podażą w Europie. Jak informuje NEC, twórca pamięci VC-SDRAM, pod względem cenowym nie będzie się bardzo różniła od porównywalnych układów SDRAM. Jednak trzeba wkalkulować różnicę ceny od 5 do 10 procent. NEC deklaruje technologię VC jako otwarty standard, więc pozostali producenci nie muszą uiszczać opłat licencyjnych. Oprócz NEC produkcją układów VCSDRAM zajmują się obecnie Hyundai i Infineon.

Wydajność modułów. Maksymalna przepustowość układów VC-133SDRAM sięga 1,06 GB/s, więc odpowiada wydajności układów SDRAM PC 133. Podobnie do standardowej pamięci SDRAM, nowa VC-SDRAM potrafi dostarczać danych wraz z każdym cyklem. Jednak teoretyczne zalety VC-SDRAM okazują się w praktyce mato znaczące. W zastosowaniach standardowych nie widać wzrostu wydajności. Nawet w grach 3D i specjalnych testach AGP, które w dużym stopniu obciążają pamięć, trudno zauważyć zwiększenie prędkości. W stosunku do pamięci SDRAM różnica jest znikoma (rzędu 1 do 2 procent).

Kompatybilność z chipsetami i płytami głównymi. VCSDRAM może liczyć na asekurację tylko z Dalekiego Wschodu. Obecne chipsety takich producentów jak ALI, SIS i VIA obsługują ten typ pamięci. Dlatego mimo rynkowego niedoboru dostępna jest duża oferta płyt głównych przecież większość pochodzi z Tajwanu.

Zasady działania modułów. VCSDRAM ma oferować większą wydajność względem pamięci SDRAM poprzez jednoczesne odwoływanie się do kilku układów pamięciowych. Jest to rozsądne rozwiązanie, ponieważ w codziennej pracy z komputerem bardzo często aplikacje i podzespoły sprzętowe odwołują się do pamięci roboczej niemal równocześnie. Na dodatek niektóre urządzenia, np. kontroler twardych dysków, może się odwoływać bezpośrednio do pamięci RAM, korzystając z trybu DMA. Również karty graficzne AGP komunikują się za pośrednictwem magistrali AGP bezpośrednio z pamięcią roboczą, aby gromadzić w niej duże tekstury. Jednoczesne odwołania do pamięci RAM pociągają za sobą liczne cykle oczekiwania. VC-SDRAM stara się optymalnie porządkować dane tak, aby nie dopuszczać do zatorów. Dzięki temu zmniejsza średnią liczbę cykli oczekiwania, co podnosi przepustowość danych.

Parametry techniczne. Każdy podzespół w układzie VC-SDRAM składa się z 16 kanałów pamięciowych (tzw. channels). Za ich pośrednictwem tzw. memory master ma szybki i bezpośredni dostęp do poszczególnych segmentów pamięci. Każdy kanał dysponuje własnym buforem o pojemności 1024 bitów, który mieści się w szybkiej pamięci SRAM. Kanały pamięciowe są usytuowane między interfejsem wejścia/wyjścia i macierzą pamięci. Potrafią gromadzić tymczasowo określoną ilość danych. Dzięki temu układ scalony pamięci może przygotowywać kolejne operacje (które mają być dokonane w pamięci), podczas gdy jednocześnie przetwarza aktualny cykl odczytu lub zapisu w komórce pamięciowej. Operacje wewnętrzne są wykonywane równolegle do odczytu i zapisu w pamięci. W przypadku większej liczby zapytań symultanicznych adresy i rodzaje żądanych operacji są buforowane w poszczególnych kanałach modułu VC-SDRAM. Zapytania nie generują więc dodatkowych cykli oczekiwania. Wielokrotne zapytania w dotychczasowych technologiach DRAM łączyły się z niewystarczającym wykorzystaniem pamięci. Każde nieprzyjęte zapytanie musi zostać ponownie zainicjowane, co jest dość czasochłonne. Opisywane zjawisko jest określane mianem page trashing. Wprawdzie wielobankowa organizacja standardowej pamięci SDRAM pozwala jej zminimalizować liczbę cykli oczekiwania, lecz VCM potrafi znacznie skuteczniej przetwarzać zapytania wielokrotne.

Wygląd modułów pamięciowych. Układy pamięciowe wyposażone w technologię Virtual Channel Memory są obecnie dostępne w wersjach taktowanych z częstotliwością 100 i 133 MHz. Wyglądem ani trochę się nie różnią od konwencjonalnych 168-stykowych modułów DIMM.

Rozszerzalność. Teoretycznie możesz użyć układów SDRAM. Każdy pecet, który obsługuje VC-SDRAM, zaakceptuje moduły VC-SDRAM. Na dodatek można zainstalować układy obu typów na jednej płycie głównej.

Perspektywy. VC-SDRAM nie ma rewelacyjnych osiągów w porównaniu do pamięci SDRAM, zatem nie wyznacza standardów na przyszłość.

Podsumowanie. VC-SDRAM ma zoptymalizować przepustowość, samodzielnie ustalając kolejność przetwarzania pojedynczych zapytań w przypadku zapytań wielokrotnych. Jednak w praktyce powoduje marginalną zwyżkę wydajności w stosunku do konwecjonalnej pamięci SDRAM.

DRAM (Dynamic Random Access Memory) to protoplasta nowoczesnych typów pamięci roboczej. Obecnie szansa trafienia na pamięć DRAM w jej pierwotnej postaci jest bardzo nikła. Nawet siedmio- i ośmioletnie pecety klasy 386 są wyposażone w bardziej zaawansowaną wersję o nazwie FPM-DRAM. Jednak zasady działania pamięci DRAM cieszą się jeszcze dziś sporym zainteresowaniem. Na tej technologii opierają przecież wszystkie nowoczesne typy pamięci stosowane w komputerach PC (nawet bardzo wydajne DDR-SDRAM i RambusDRAM).

Zakres oferty. Obecnie pamięć DRAM jest praktycznie nieosiągalna. Przy odrobinie szczęścia uda Ci się kupić używane scalaki na giełdzie. Już przed laty bardziej zaawansowane typy pamięci wyparły DRAM z rynku.

Wydajność modułów. Czasy dostępu w typowych układach scalonych DRAM sięgają 100 nanosekund. Zakładając, że komunikacja odbywa się na magistrali danych o szerokości 32 bitów i częstotliwości taktowania 33 MHz (takie parametry miały ówczesne magistrale danych), 100-nanosekundowy układ scalony DRAM może transmitować dane co cztery cykle. Cykl procesora trwa 30 nanosekund, zatem dopiero w czwartym takcie SDRAM jest gotowy do ponownej operacji. Przy podanej konfiguracji maksymalna wydajność transmisji sięga około 32 MB/s.

Kompatybilność z chipsetami i płytami głównymi. Obecnie nie stosuje się pamięci DRAM w pierwotnej postaci. Nowoczesne chipsety nie obsługują pamięci tego typu.

Zasady działania modułów. Każda komórka pamięci składa się z kondensatora i tranzystora. Poszczególne komórki są w macierzy pamięciowej uporządkowane w rzędach i kolumnach. Pozwała to oszczędzić zewnętrznych ścieżek adresowych, lecz zaadresowanie komórki wymaga dwóch etapów. Chipset przekazuje scalakowi DRAM kolejno adres wiersza i adres kolumny. Poprzez ścieżki RAS i CAS informuje układ scalony, który adres (adres wiersza, tj. RAS, czy adres kolumny, tj. CAS) znajduje się na stykach. Metoda ta nazywa się zwielokrotnianiem, a także multipleksowaniem adresów. Aby można było zaadresować każdą komórkę w układzie DRAM o pojemności 16 megabitów bez użycia multipleksowania, konieczne są aż 24 ścieżki danych (22°=16 777 216). Ponieważ adres jest podawany w dwóch partiach (oddzielnie wiersz i kolumna), wystarczy 12 bitów (2 12= 4096), czyli 12 zewnętrznych styków adresowych. Zawiły sposób adresowania spowalnia operacje zapisu i odczytu. To jeden z zasadniczych powodów stosunkowo niskiej wydajności pamięci DRAM. Dodatkowe opóźnienia są związane z tym, że DRAM gromadzi informacje w mikroskopijnych kondensatorach, które dość szybko tracą zawartość ze względu na tzw. prądy upływowe. Dlatego informacje zapisane w kondensatorach musza być regularnie odświeżane. Cykl odświeżania polega na odczytaniu i ponownym zapisaniu zawartości komórki. Tylko w ten sposób można zapobiec "ulatnianiu" się informacji z pamięci.

Parametry techniczne. Czas, po którym musi nastąpić cykl odświeżania (tzw. refresh), nazywa się okresem odświeżania. Zależnie od typu układu scalonego trwa od kilku do ponad stu milisekund. Odświeżanie komórek odbywa się wiersz po wierszu. Zatem cała zawartość układu DRAM jest zaktualizowana dopiero po odczytaniu i zapisaniu wszystkich wierszy. Potem następuje kolejny przebieg odświeżania. Za sterowanie tą operacją odpowiada kontroler odświeżania. Wczesne DRAM-y nie dysponowały takim kontrolerem. Znajdował się na zewnątrz - w chipsecie płyty głównej. W nowszych DRAM-ach był zaimplementowany wewnątrz scalaków. Kontroler odświeżania kopiuje zawartość komórek do bufora, po czym zapisuje ją w pierwotnym miejscu. Wadą tego rozwiązania jest to, że podczas odświeżania nie ma dostępu do pamięci - czasy oczekiwania są nieco dłuższe.

Wygląd modułów pamięciowych. Pamięć DRAM nie występuje w postaci modułów z kilkoma procesorami, lecz pojedynczych układów scalonych. Są one skonstruowane w formacie DIL (Dual in Line), stosowanym na początku lat dziewięćdziesiątych w układach pamięci. Składają się z właściwej jednostki procesora i nóżek kontaktowych uszeregowanych w dwóch równoległych rzędach.

Podsumowanie. Pamięci DRAM już od lat nie stosuje się w pecetach. Warto jednak dysponować podstawowymi wiadomościami na jej temat, ponieważ wewnętrzna struktura aktualnych układów pamięciowych opiera się na tej samej technologii.

+ duża pojemność na małej powieżchni,

- maksymalna częstotliwość taktowania 33 MHz.

Pamięć FPM-DRAM (FastPage Mode DRAM) jest akceptowana przez większość chipsetów w komputerach klasy 486 i Pentium. Jeżeli masz pecet tego typu, poszukaj pamięci w starych komputerach, a uda Ci się rozszerzyć zasoby pamięciowe.

Zakres oferty. Mimo że kariera FPM-DRAM dobiegła końca tuż przed wprowadzeniem pamięci EDO-DRAM i SDRAM, niektórzy sprzedawcy mają w magazynie drobne zapasy modułów FPM. Jednak słone ceny odstraszają potencjalnych nabywców. Pamięć FPM przestała być produkowana na dużą skalę, ponieważ nie jest stosowana w obecnych pecetach.

Wydajność modułów. Czasy dostępu w pamięci FPM-DRAM wahają się w granicach 60-70 nanosekund, zatem nie jest szybsza od konwencjonalnej pamięci DRAM. Czas cyklu CAS w 60-nanosekundowych modułach DRAM wynosi przy szybkiej transmisji w trybie FPM około 40 nanosekund (ns). Przy magistrali taktowanej z częstotliwością 66 MHz każdy cykl trwa 15 ns. Zatem w trybie FPM procesor może się odwoływać do komórki pamięciowej co trzy cykle. Maksymalną przepustowość pamięci FPM-DRAM w komputerze z magistralą 66 MHz można obliczyć w następujący sposób. Począwszy od modelu Pentium procesory odczytują i zapisują dane poprzez magistralę o szerokości 64 bitów - korzystając z trybu pakietowego (burst mode) przesyłają w jednym cyklu CAS (czyli w przeciągu 40 ns) partię 8 bajtów. Zatem prędkość transmisji między procesorem i pamięcią FPM-DRAM sięga 200 MB/s.

Kompatybilność z chipsetami i płytami głównymi. Wszystkie chipsety współpracujące z procesorami 486 i Pentium (Pro) obsługują moduły FPM. Jednak nie zastosujesz pamięci tego typu w pececie z układem Pentium II, Celeron i Athlon.

Zasady działania modułów. Jako bezpośredni następca konwencjonalnej pamięci DRAM, FPM-DRAM eliminuje jej podstawową wadę. Polega ona na tym, że podczas odczytu i zapisu danych adres komórki pamięciowej jest przekazywany w dwóch etapach. FPM-DRAM unika tego ograniczenia w większości odwołań do pamięci. Bardzo często odwołania dotyczą komórek, które leżą, (jedna za drugą) w tym samym wierszu. W pamięci DRAM operacje są wykonywane wiersz po wierszu, więc jednostka sterująca modułu FPM-DRAM wczytuje zawartość całego wiersza, zanim zanalizuje adresy kolumn. Zatem podczas zapisu lub odczytu kolejnej komórki tego samego wiersza nie trzeba ponownie fatygować macierzy pamięciowej ani podawać numeru kolumny.

Parametry techniczne. Pierwszy odczyt w pamięci FPM-DRAM odbywa się tak samo jak w konwencjonalnej pamięci DRAM. Po pierwszym cyklu odczytywania jednostka sterująca pozostawia sygnał RAS w stanie aktywnym. Sygnalizuje w ten sposób, że kolejne operacje mają być realizowane w trybie Fast Page Mode. Wiersz (określany tu jako "page") pozostaje aktywny. Podczas kolejnych odczytów jednostka sterująca podaje podzespołowi DRAM tylko adres kolumny, Dzięki stosowaniu opisanych cyklów wtórnych można skrócić czasy oczekiwania konieczne w konwencjonalnych modułach DRAM ("RAS Precharge" i "RAS to CAS Delay"). W tym trybie nie trzeba się ponownie odwoływać do macierzy pamięciowej. Odwołania do poszczególnych komórek są realizowane bezpośrednio z poziomu jednostki sterującej, która zna zawartość całego wiersza. Dlatego odczyt trwa średnio dwukrotnie szybciej. Dopiero gdy zapytanie dotyczy innego wiersza pamięci, chipset musi zainicjować zwykły odczyt, który trwa tak długo jak w pamięci DRAM. Zatem w najszybszym trybie odczytu pakietowego z pamięci FPM-DRAM synchronizacja ma postać 5-3-3-3.

Wygląd modułów pamięciowych. Pamięć FPM jest dostępna w postaci modułów SIMM (Single Inline Memory Module). 72-stykowe moduły SIMM (zwane również SIMM-ami PS/2) stanowiły przed dwoma laty standardową pamięć instalowaną w pecetach. Przedtem instalowano zazwyczaj moduły SIMM o 30 stykach.

Rozszerzalność. Mimo że pamięć FPM jest nadal dostępna, nie zaleca się używać jej do rozszerzania posiadanych zasobów. Inwestycja w aktualne typy pamięci (np. SDRAM) okaże się na pewno korzystniejsza, nawet jeśli wymaga wymiany całej płyty głównej.

Perspektywy. Pamięć FPM uchodzi obecnie za przestarzałą i niebawem zniknie z rynku.

Podsumowanie. Modyfikacja jednostki sterującej pamięcią znacznie przyspieszyła odwołania do sąsiadujących komórek. To proste rozwiązanie nie wymaga większych nakładów produkcyjnych.

EDO-DRAM (Extended Data Out) przez długi czas stanowiła pamięciowy standard w komputerach klasy Pentium, dopóki nie została zastąpiona przez SDRAM. Mimo że jest szybsza od poprzednika, obecnie nadaje się tylko do mało wymagających zastosowań, jak edycja tekstu czy zwiedzanie Internetu.

Zakres oferty. Większość sklepów dysponuje resztkami w magazynach, lecz ze względu na niewielką podaż moduły EDO są dość kosztowne.

Wydajność modułów. Czas dostępu w EDO-DRAM wynosi 70, 60 lub 50 nanosekund (ns). Pamięć EDO to "podkręcona" wersja pamięci FPM. Przykładowo w 60-nanosekundowym układzie EDO skrócono cykl CAS z 40 ns (FPM-DRAM) do 25 ns. Zatem przy magistrali taktowanej z częstotliwością 66 MHz odczyt jest możliwy w co drugim cyklu. Inicjacja dostępu w trybie pakietowym zajmuje 5 cykli (tak jak w FPMDRAM). Maksymalnie szybki odczyt pakietowy odbywa się więc przy synchronizacji 5-22-2. Zapis pamięci EDO-DRAM odbywa się z taką samą prędkością jak zapis FPM-DRAM. Maksymalna transmisja odczytu pamięci EDO w pececie z procesorem Pentium i 64-bitową magistralą danych sięga 300 MB/s (czyli około 50 proc. więcej niż FPM). Jednak w praktyce różnica wydajności nie jest tak duża. Pamięć podręczna pierwszego i drugiego poziomu, w którą wyposażono procesor, buforuje około 90 procent operacji zapisu - prędkość pamięci głównej, nie odgrywa w tym przypadku tak wielkiej roli. W sumie zwyżka wydajności wynosi około 5 procent. Dotyczy to jednak tylko pecetów wyposażonych w pamięć podręczną drugiego poziomu (L2). Wielu producentów komputerów wykorzystało ówczesną euforię związaną z dwukrotnie szybszą pamięcią EDO i nie wstawiało kosztownej pamięci podręcznej drugiego poziomu, bardzo ograniczając w ten sposób wydajność pamięci. Zapis w EDO trwa tak samo długo jak w FPM-DRAM. Na dodatek czasy dostępu rzędu 10 ns sprawiają, że pamięć podręczna drugiego poziomu w 90 procentach określa rzeczywistą wydajność pamięci operacyjnej. Komputer wyposażony w pamięć FPM-DRAM i L2 jest zazwyczaj szybszy od peceta z EDO-DRAM, lecz bez L2.

Kompatybilność z chipsetami i płytami głównym. Pamięć EDO akceptują wszystkie chipsety, które współpracują z procesorem Pentium (do wersji III). Jednak większość nowych płyt głównych nie oferuje odpowiednich slotów.

Zasady działania modułów. Moduły EDO stanowią ulepszenie układów FPM, ale dysponują dodatkową pamięcią (latch) na wyjściu danych. W pamięci DRAM i FPM-DRAM bieżące dane muszą zostać w pełni odczytane, zanim chipset poda nowy adres. Zakończenie odczytu jest sygnalizowane natężeniem sygnału CAS. W czasie nieodzownym do dalszego przetworzenia danych, pamięć DRAM pozostaje nieaktywna. EDO-DRAM dysponuje dodatkową komórką (bardzo szybkiej pamięci) na wyjściu danych. Dane dotyczące ostatnio odczytywanej komórki pobrane z macierzy pamięciowej są zapisywane we wspomnianej komórce dodatkowej do kolejnego uaktywnienia sygnału CAS. Procesor może więc odczytywać dane, podczas gdy jednostka sterująca przesyła nowy adres kolumny do podzespołu DRAM.

Parametry techniczne. Metoda przyspieszająca dostęp zastosowana w modułach EDODRAM to tak zwane przetwarzanie potokowe (pipelining). Skraca ono czas oczekiwania między dwoma następującymi po sobie impulsami CAS, co zwiększa przepustowość danych. Stosując analogię do Fast Page Mode DRAM, szybki dostęp w pamięci EDO nazwano Hyper Page Mode. Pamięć EDO-DRAM jest więc czasami nazywana HPM-DRAM. Operacje zapisu są wykonywane z taką samą wydajnością jak w FPMDRAM. Przy częstotliwości taktowania 66 MHz EDO-DRAM dostarcza dane z synchronizacją 52-2-2.

Wygląd modułów pamięciowych. Zdecydowana większość układów EDO występuje w postaci 72-stykowych modułów typu SIMM PS/2. Rzadko spotykane są w formie 168-stykowych modułów DIMM.

Rozszerzalność. Wprawdzie pamięć EDO jest jeszcze dostępna, lecz do rozszerzenia zasobów zaleca się korzystać z modułów SDRAM. Koszt nowej płyty głównej zwraca się nawet przy stosunkowo niewielkim rozbudowaniu pamięci.

Perspektywy. Era modułów EDO-DRAM dobiegła końca. Jeśli inwestować w pamięć, to w nowszą i wydajniejszą.

Podsumowanie. Żaden z innych typów pamięci nie był stosowany tak często w pecetach z procerorami Pentium jak EDO-DRAM. Następca FPM-DRAM jest trochę wydajniejszy, jednak przestał się liczyć wraz z pojawieniem się SDRAM.

Pamięć Burst EDO-DRAM firmy Micron mogła się stać przyszłościowym rozwiązaniem, lecz uległa pamięci SDRAM, którą od początku preferowało wielu producentów płyt głównych.

Zakres oferty. Obecnie pamięć BEDO-DRAM nie jest niedostępna.

Wydajność modułów. Przy 64-bitowej magistrali danych, z którą współpracują takie układy jak Pentium i Pentium Pro, Burst EDO może oferować dane wraz z każdym cyklem. W praktyce daje to przepustowość rzędu 500 MB/s - czyli tyle samo, ile w SDRAM PC 66.

Kompatybilność z chipsetami i płytami głównymi. Pamięć Burst EDO została zignorowana przez producentów chipsetów, którzy postawili na szybszą SDRAM. Tylko Intel opracował chipset 450GX (kryptonim "Orion") współpracujący z procesorem Pentium Pro. Ponieważ na rynku pojawił się tylko jeden chipset, na dodatek nie przeznaczony do popularnego układu Pentium, nie wprowadzano płyt głównych ani komputerów z pamięcią Burst EDO.

Zasady działania modułów. Moduty BEDODRAM mają 2-bitowy generator adresów. Podczas operacji w trybie pakietowym jednostka sterująca podaje pamięci tylko pierwszy adres. Kolejne trzy adresy kolumn są ustalane automatycznie przez wewnętrzny generator adresów bez udziału chipsetu. Jego rola kończy się na zainicjowaniu cyklu odczytu. Oprócz tego BEDO-DRAM dysponuje dwoma wewnętrznymi bankami pamięciowymi, w których gromadzone są następujące po sobie (z logicznego punktu widzenia) dane. Gdy jeden bank jest zajęty podawaniem danych na zewnątrz, w drugim odbywa się adresowanie.

Parametry techniczne. BEDO-DRAM (podobnie jak FPM i EDO) może pokazać swoje mocne strony tylko w trybie pakietowym. Przy częstotliwości magistrali 66 MHz tryb ten jest realizowany z cyklami 5-1-1-1. W odróżnieniu od FPM i EDO pamięć BEDO-DRAM potrafi uaktywnić tryb pakietowy również podczas zapisu.

Wygląd modułów pamięciowych. Pamięć Burst EDO była dostępna w postaci 72-stykowych modułów SIMM PS/2.

Rozszerzalność. Niemożliwa ze względu na brak pamięci Burst EDO na rynku.

Perspektywy. Pamięć Burst EDO nie miała szans w starciu ze SDRAM.

Podsumowanie. Burst-EDO była pierwszą pamięcią DRAM, która przy częstotliwośći 66 MHz nie hamowała procesora cyklami oczekiwania. Jednak producenci chipsetów upodobali sobie szybką pamięć SDRAM i pozostawili BEDO-DRAM na pastwę losu.

Literatura:

Baranowski J., Kalinowski B., Nosal Z.: Układy elektroniczne cz.III. WNT Warszawa 1998

Kolan Z.: Urządzenia techniki komputerowej. CWK SCREEN Warszawa 1999

Wojtuszkiewicz K.: Urządzenia techniki komputerowej - Jak działa komputer ?

MIKOM Warszawa 1999

Materiały z Internetu.

T

Cs

Linia wiersza

Linia bitu

UDD

RAS#

CAS#

WE#

OE#

CE#

dane

adresy

RZW

DW

DK

RZK

Wejście adresowe

RAS#

CAS#

Wyszukiwarka

Podobne podstrony:

06-02 PAM - Połączenie z Waszą Radą Światła, CAŁE MNÓSTWO TEKSTU

07-02 PAM-Dostęp do Waszego Makro-Ducha i do Waszej Świadomości, ezoteryka

b, 1 STUDIA - Informatyka Politechnika Koszalińska, muniol, I rok, pam - egz, 1 koło

08-02 PAM-Podążanie drogą Świętego serca, ezoteryka

BAD OPER 09 10(2)

08 08 PAM Otwarcie Galaktycznej Bramy Nieskończoności

dermatologia pam

wzm oper 05, Inzynieria Materiałowa, I semestr, Elektrotechnika, elektrotechnika, Układy Elektronicz

04-12 PAM-Dostęp do portali i Miast ze Światła, ezoteryka

08-05 PAM-Czy jesteście gotowi, ezoteryka

Wzm oper (2)

Pyt oper (2)

STER 6 3 1 dodat oper?ne kopiujdanestan

STERBHP 5 4 dodat oper opcje konfig

05-11 PAM-Radosne serce w świecie chaosu, ezoteryka

więcej podobnych podstron