LABORATORIUM UKŁADÓW ELEKTRONICZNYCH

Ćwiczenie 6

SUMATORY I KOMPARATORY

Ćwiczenie 6 / wkładki DM 221..,DM 221B

SUMATORY I KOMPAKTORY

6.1. WSTĘP

Tematem ćwiczenia są elementarne układy sumatorów i komparatorów liczb binarnych , przeznaczone do zastosowań w układach i systemach cyfrowych . Pierwsza częśc ćwiczenia polega na badaniu funkcji realizowanych przez układy sumatorów a także metod budowy sumatorów wielobitowych .W tej części ćwiczenia badane są kolejno prosty półsumator dwubitowy ; dwubitowy sumator pełny i czterobitowy sumator ekumulujący.

W drugiej części ćwiczenia prowadzona jest analiza działania 3 układów komparatorów: prostego komparatora wykrywającego równość dwóch słów dwubitowych ; komparatora określającego relację mniejszości ; większości i równości dwóch liczb dwubitowych oraz komparatora opartego na zasadzie zaliczania impulsów zegarowych .

Celem ćwiczenia jest eksperymentalne przedstawianie sposobów sumowania i porównywania liczb binarnych za pomocą układów cyfrowych TTL.

6.2 OPIS TECHNICZNY UKŁADÓW BINARNYCH

6.2.1 Układy sumatorów / wkładka DM221A/

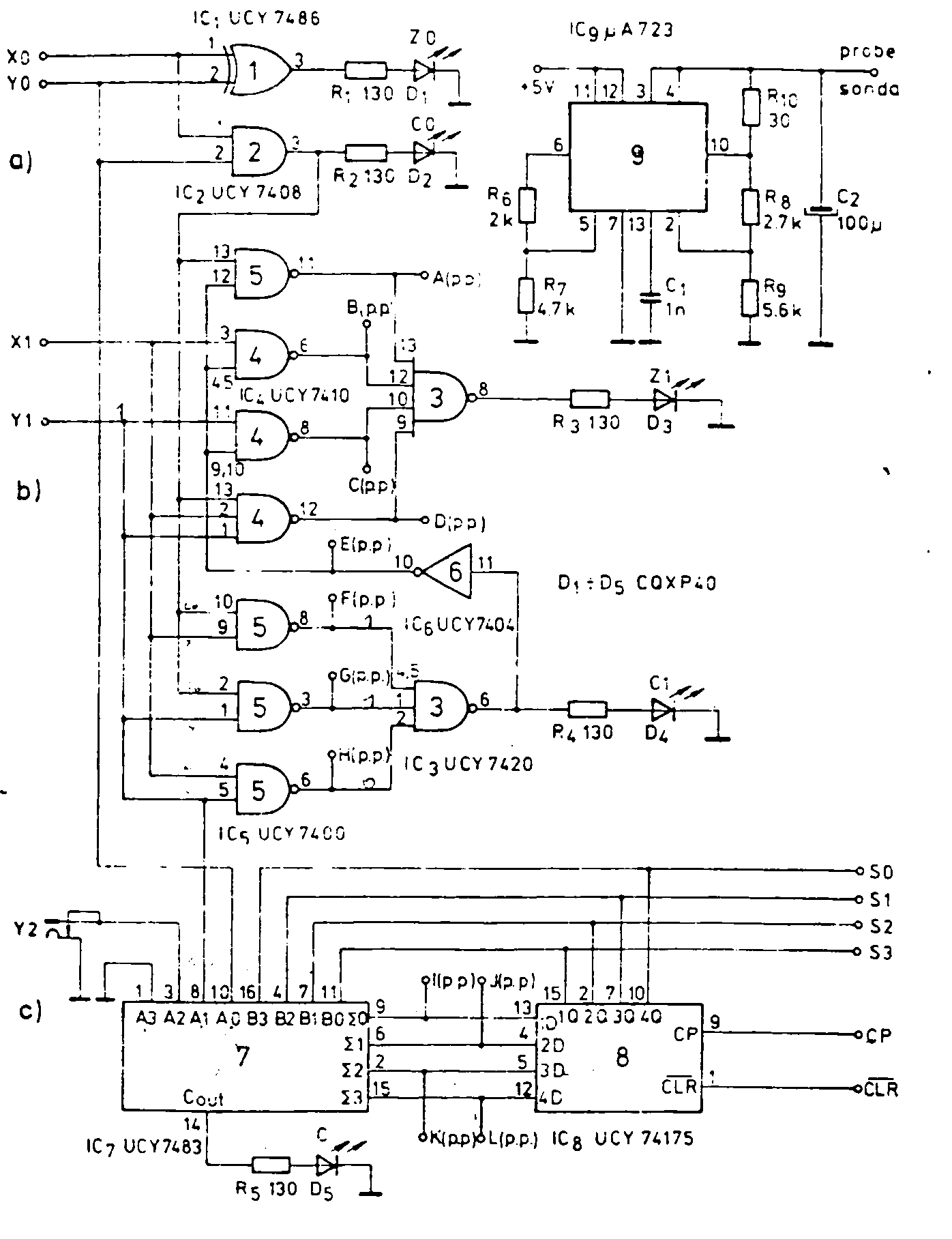

Wkładka DM221A zawiera trzy układy sumatorów przedstawionych na rysunku 6.1:

jednobitowy półsumator zbudowany z elementarnych bramek ;

jednobitowy pełny sumator ,również zbudowany z elementarnych barmek ;

czterobitowy sumatro akumulujący zbudowany z elementów średniej skali integracji .

poziomy wejściowe sumatora „a” wymusza się przez podanie na gniazda XO, YO

napięć z generatora stanów logicznych , natomiast stany wyjść sumy ZO i przeniesienia CO

wskazywane są przez diody elektroluminescencyjne o barwie czerwonej . Świecenie diody oznacza stan wysoki wyjścia .

Poziomy wejść informacyjnych układu „b” wymusza się przez podanie do wejść X1,Y1 napięć generatora SN1222, natomiast wejście przeniesienia podłączone jest do przeniesienia z układu „a” .Stany wyjść sumy Z1 i przeniesienia C1 wskazywane są przez czerwone diody LED, przy czy świecenie diody oznacza stan wysoki odpowiedniego wyjścia

Układ sumatora akumulującego z rys.6.1.c posiada wejścia informacyjne dołączone do gniazd Y0, Y1, Y2 a także wejscie zerujące rejestr dołączone do gniazda CLR.Do wejść tych powinny być doprowadzone napięcia z generatora stanów logicznych SN1222. Ponadto układ posiada wejście wpisuje do rejestru dołączone do gniazda CP, do którego doprowadza się impulsy z generatora SN3311 .Impulsy te powinny być generowane pojedynczo / wyzwalane ręcznie/ .

Wyjścia układu c doprowadzone są do gniazd S0, S1, S2,S3, gdzie mogą być obserwowane za pomocą wskaźnika stanów logicznych SN9111 . Stan wyjścia przeniesienia układu obserwowany jest za pomocą diody LED oznaczonej symbolem C .

Poziomy logiczne w wewnętrznych punktach układów z rys. 6.1.b i c mogą być obserwowane za pomocą sondy logicznej dołączonej do punktów pomiarowych A -L. Przewód zasilający sondy logicznej dołączć należy do gniazda „probe”.

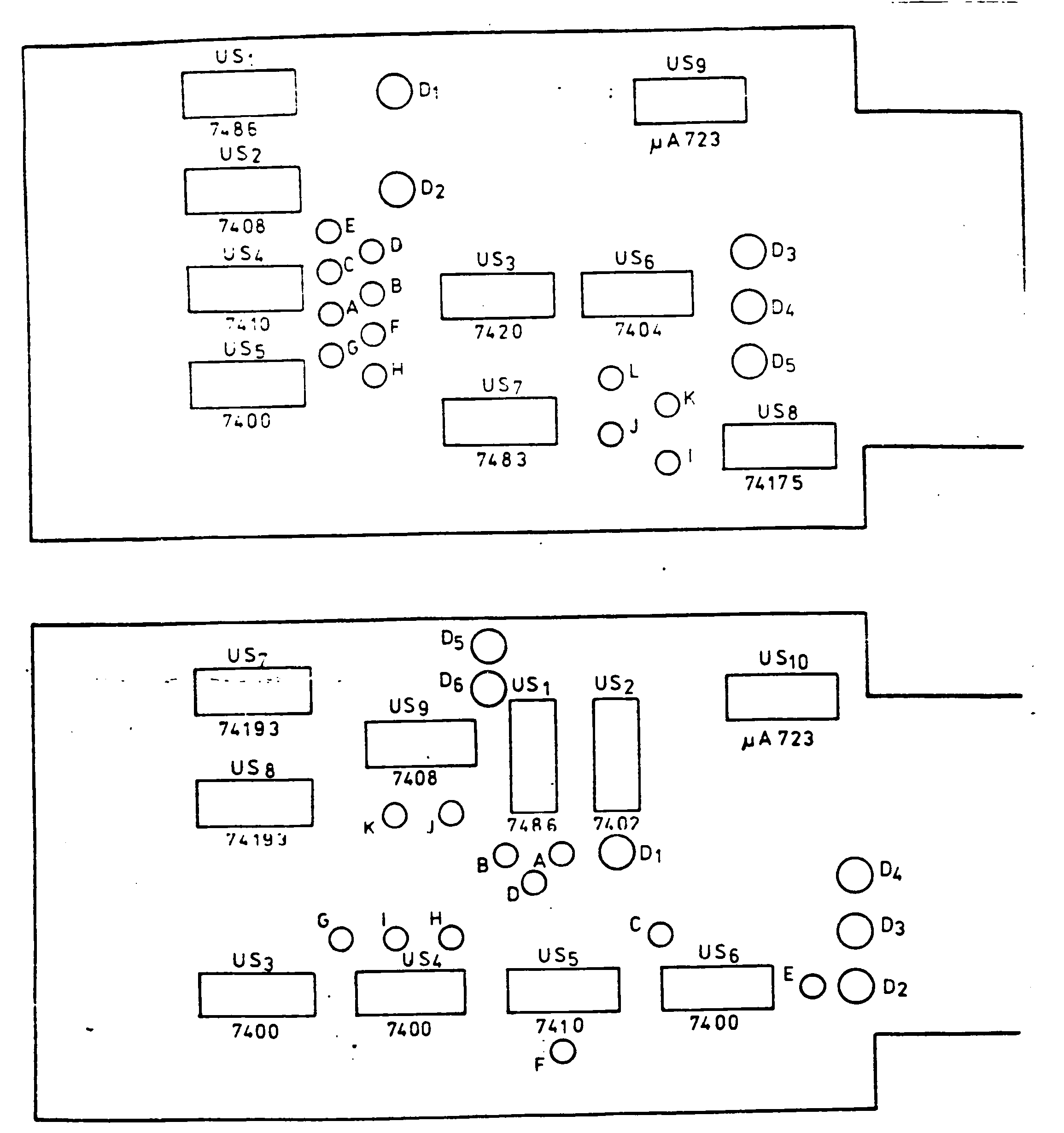

Rozmieszczenie diod wskaźnikowych i punktów pomiarowych zilustrowano na rys. 6.3.

6.2.2. Układy komparatorów / wkładka DM 221B/

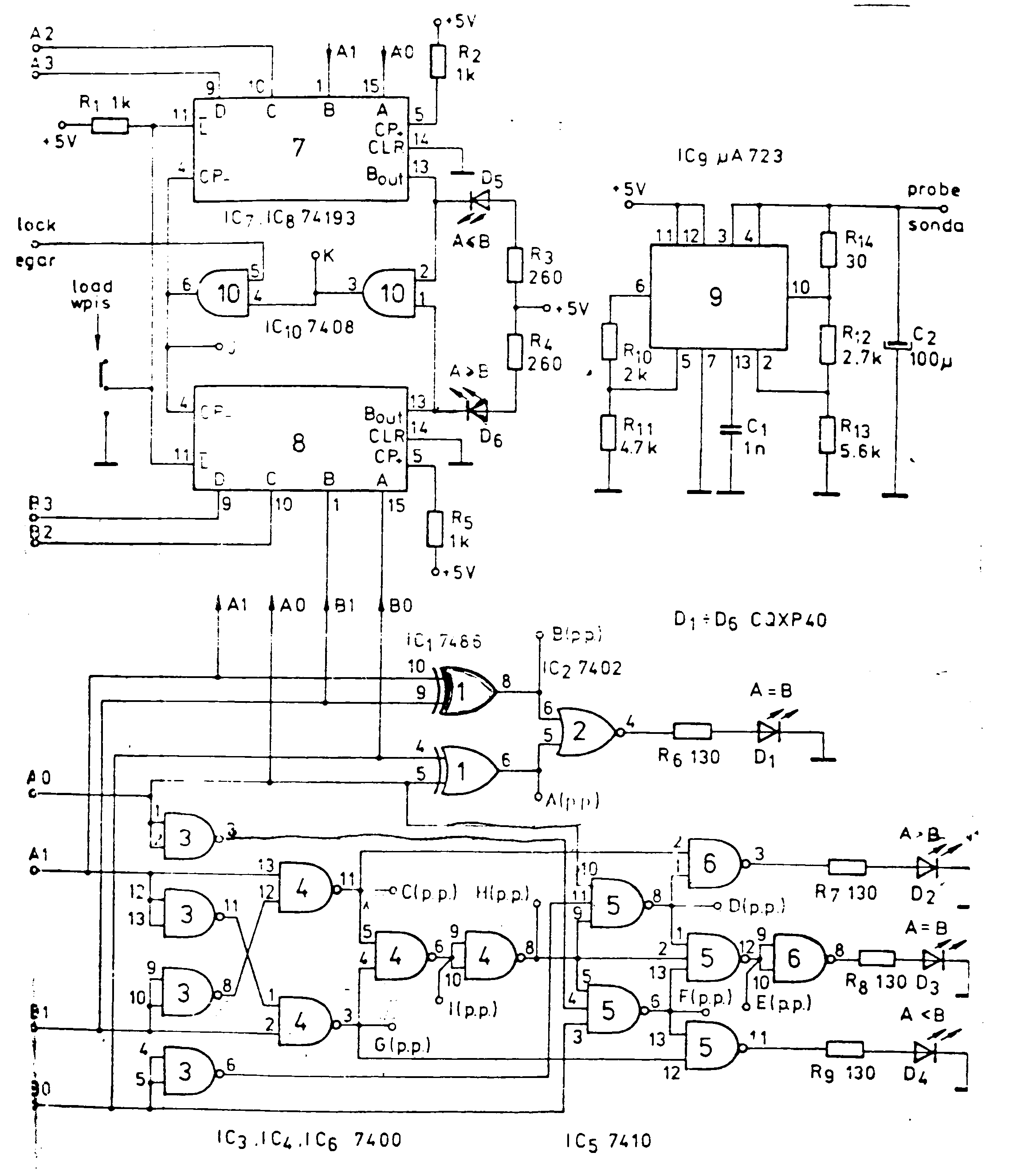

Wkładka DM221B /rys.6.4 / zawiera trzy układy komparatorów :

proste komparator wykrywający równość dwóch słów bitowych ;

komparator umożliwiający określenie relacji większości ,mniejszości i równości dwóch dwubitowych liczb binarnych ;

układ określający nieostre nierówności między dwa czterobitowymi liczbami wykorzystujący odliczenie impulsów zegarowych .

Komparatory z rys.6.4 a i b zbudowane są z bramek małej skali integracji i umozliwiają prześledzenie ich działania za pomocą sondy logicznej dołączonej do punktów pomiarowych A-I . Stany wyjść komparatorów wskazywane są przez czerwone diody LED, przy czym stanowi wysokiemu wyjścia odpowiada świecenie diody .Wejścia obu komparatorów połączone są równolegle do gniazd A0, A1- pierwsza porównywana liczba i B0, B1 - druga . Do wejść tych powinien być dołączony generator stanów logicznych SN1222.

Rys 6.1. Schemat ideowy wkładki LM 221A

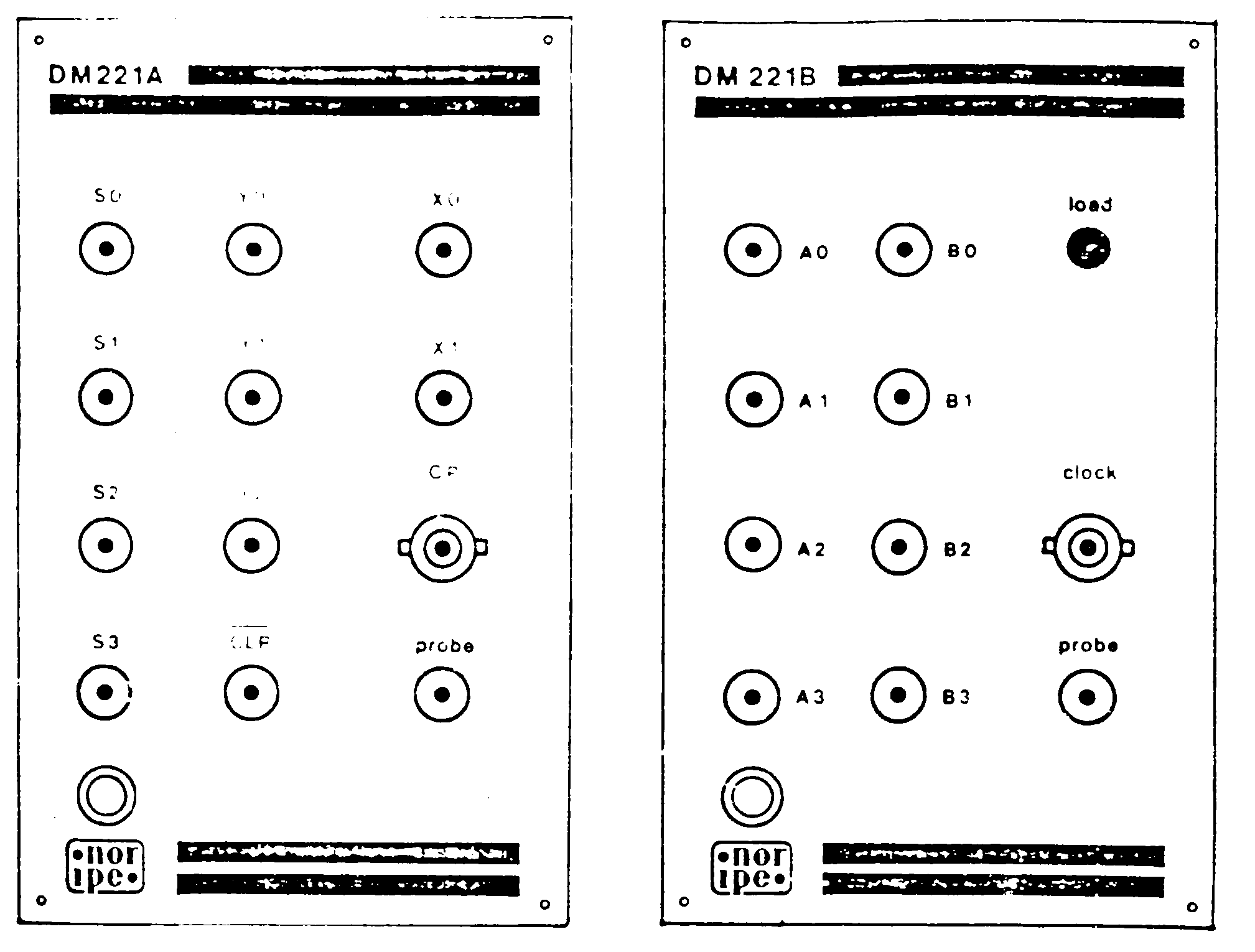

Rys 6.2. Płyty czołowe układów badanych DM221 A i B

Rys 6.3. rozmieszczxenie elementów wskaźnikowych na płytkach DM 221 A i B

Układ przedstawiony na rys.6.4.c składa się z dwóch liczników rewersyjnych z wpisem równoległym oraz bramek blokujących zaliczane w przypadku zerowego stanu jednego z liczników . Wejścia informacyjne obu liczników dołączone są do gniazd odpowiednio A0, A1, A2, A3 i B0,B1, B2, B3 .

Do wejść tych doprowadzone powinny być napięcia z generatorów SN1222. Sygnał zegarowy doprowadzony powinien być z generatora impulsów SN3311 do gniazda „clock” , przy czy impulsy te mogą być generowane pojedynczo /wyzwalanie ręczne /lub w sposób ciągły . Na płycie czołowej znajduje się do ręcznego wpisywania początkowego stanu obu liczników .

Rozmieszczenia diod wskaźnikowych i punktów pomiarowych zilustrowano na rys.6.3

6.3WYKAZ APARATURY POMOCNICZEJ

Do wykonania ćwiczenia potrzebne sa nastepujące przyrządy pomocnicze :

-generator stanów logicznych TTL czterowyjściowy /2 sztuki SN1222/

-generator impulsów zegarowych SN 3311

-wskaźnik stanów logicznych SN9111

-sonda logiczna .

6.4 ZAGADNIENIA WSTĘPNE I PROJEKTOWE

1.Zaprojektować sekwencję stanów podawanych na wejściu kładów binarnych we wszystkich eksperymentach.

2. Opracować i narysować w protokole schematy pomiarów do wszystkich eksperymentów omawianych w p.6.5.

Rys 6.4. schemat ideowy wkładki DM 221 B

6.5 OBSERWACJE I POMIARY

6.5.1 Określanie funkcji wyjść sumatora i półsumatora

Podając różne kombinacje poziomów logicznych na wejścia informacyjne , określić tablice funkcji wyjść Z0, C0, Z1 ,C1, a także tablice funkcji punktów wewnętrznych A,B,H, układów sumatora i półsumatora jednobitowego .Wykorzystując układy z rys.6.1 a i b , tworzące wspólnie sumator dwubitowy ,dodac kilka liczb dwubitowych . Określić tablice funkcji wyjść sumatora dwubitowego. Wejścia X0,X1, Y0,Y1, należy wysterować z generatora stanów logicznych SN1222

Zagadnienia :

sformuować równania opisującego funkcje wyjść sumatora pełnego i półsumatora

zaproponować sposób budowy pełnego sumatora wielobitowego

określić wpływ liczb bitów sumatora na szybkosc jego działania i podac metody zwiększania tej szybkości.

6.5.2 Badanie sumatora akumulującego

Za pomocą układu z rys.6.1c dodać dwie liczby , obserwując stany w punktach I-L wszystkich fazach dodawania .Dodać do siebie cztery liczby tak ,aby spowodować wystąpienie nadmiaru . Zbudować przy użyciu sumatora akumulującego licznik w przód i tył /rewersyjne/ . Wejścia informacyjne i zerujące należy wysterować z generatora SN1222 , natomiast do wejścia wpisującego doprowadzić sygnał z generatora SN3311 wyzwalanego ręcznie .

Zagadnienia :

wyjaśnic różnicę międzu sumatorami badanymi w obu częściach ćwiczenia,

zaproponować sposób budowy układu odejmującego dwie liczby od siebie wykorzystującego zasadę działania sumatora akumulującego .

6.5.3 Określanie tablic funkcji wyjść komparatorów liczb binarnych

Podając wszystkie możliwe kombinacje stanów do wejść układów z rys. 6.4 a i b określić tablice funkcji wyjść obu układów . Obserwując stany w punktach A-I napisać równania opisujące działanie komparatorów . Wejścia układów wysterować z generatora SN1222.

Zagadnienia :

na podstawie układu z rys.6.4 a zaprojektować układ wykrywający równość dwóch liczb czterobitowych ,

zaprojektować układ realizujący funkcję identyczną z funkcją układu przedstawionego na rys.6.4 a zbudowany wyłącznie z bramek NAND,

wyjaśnić działanie układu z rys.6.4 b i podać sposób zwiększenia liczby bitów porównywanych liczb .

Obserwacja działania sekwencyjnego układu porównującego liczby

Opisując różne stany początkowe liczników zaobserwować efekt zliczania impulsów zegarowych .Obserwując sondę logiczną stany w punktach J i K prześledzić blokowanie zegara w momencie osiągnięcia stanu zerowego przez jeden z liczników . Wejścia informacyjne liczników należy wysterować z generatorów SN1222 , wejście impulsów zegarowych należy połączyć z wyjściem generatora SN3311 wyzwalanego ręcznie .

Zagadnienia:

wyjaśnić działanie układu ,

podać sposób zmodyfikowania układu tak ,aby wykazywał on ostre nierówności.

Wyszukiwarka

Podobne podstrony:

TClab5Liczniki, Technika Cyfrowa, Laboratorium

TC7DekoderyMultipleksery, Technika Cyfrowa, Laboratorium

TClab8, Technika Cyfrowa, Laboratorium

Laboratorium 4, Politechnika Koszalińska, III semestr, Laboratorium techniki cyfrowej

Laboratorium 6, Politechnika Koszalińska, III semestr, Laboratorium techniki cyfrowej

TECHNIKA CYFROWA - sprawko lab 1, Studia, PWR, 4 semestr, Podstawy techniki mikroprocesorowej, labor

LABORATORIUM TECHNIKI CYFROWEJ I MIKROPROCESOROWEJ moje

Pytania z laboratorium techniki cyfrowej, pytania

TECHNIKA CYFROWA - sprawko lab 4, Studia, PWR, 4 semestr, Podstawy techniki mikroprocesorowej, labor

TECHNIKA CYFROWA - sprawko lab 5, Studia, PWR, 4 semestr, Podstawy techniki mikroprocesorowej, labor

15 ćwiczeń laboratoryjnych z Podstaw Elektroniki i Techniki Cyfrowej

15 ćwiczeń laboratoryjnych z Podstaw Elektroniki i Techniki Cyfrowej

NOTAKI Z TECHNIKI CYFROWEJ

Lab 2 - Podstawowe techniki mikrobiologiczne, Laboratorium 2

Przekazniki i styczniki, Nauki Ścisłe Politechnika, Elektronika Teoria, Technika Cyfrowa, Technika C

Lab0, ZUT, Technika Cyfrowa, Technika Cyfrowa, sprawozdaniaTC

więcej podobnych podstron