Wyższa Szkoła Techniczno-Ekonomiczna w Warszawie

|

Laboratorium Elektroniki |

Ćwiczenie nr 5

BADANIE PODSTAWOWYCH BRAMEK LOGICZNYCH

Do użytku wewnętrznego

Warszawa 2005

A. Cel ćwiczenia

Celem ćwiczenia jest zapoznanie się z parametrami układów logicznych na podstawie podstawowej bramki NAND.

B. Przebieg ćwiczenia

Charakterystyka przejściowa bramki NAND.

Bramka standardowa

Regulując rezystorem R należy odczytać wartości napięcia wejściowego Uwe i wyjściowego Uwy, odpowiednio na woltomierzach V1 i V2 (patrz rys.3). Następnie z uzyskanych pomiarów wykreślić charakterystykę Uwy = f (Uwe). Liczba pomiarów minimum 10.

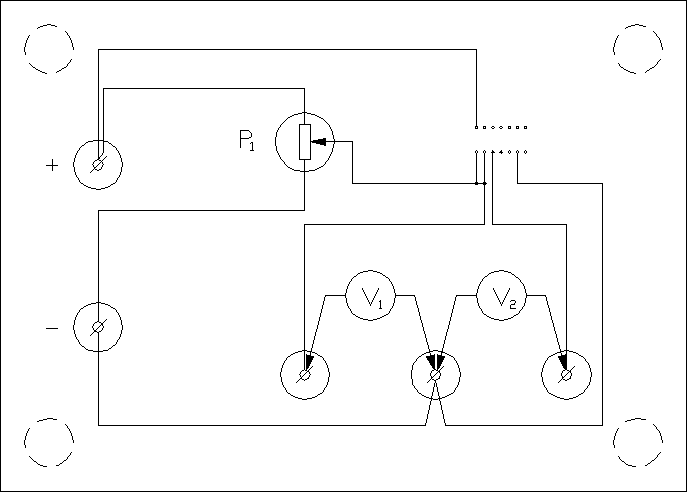

Rys.3. Schemat ideowy układu do zdejmowania charakterystyki przejściowej bramki NAND.

Regulując rezystorem R należy odczytać wartości napięcia wejściowego Uwe i prądu zasilającego bramkę ICC, odpowiednio na woltomierzu V1 i amperomierzu A, (patrz rys.4). Następnie z uzyskanych pomiarów wykreślić charakterystykę ICC = f (Uwe). Liczba pomiarów minimum 10.

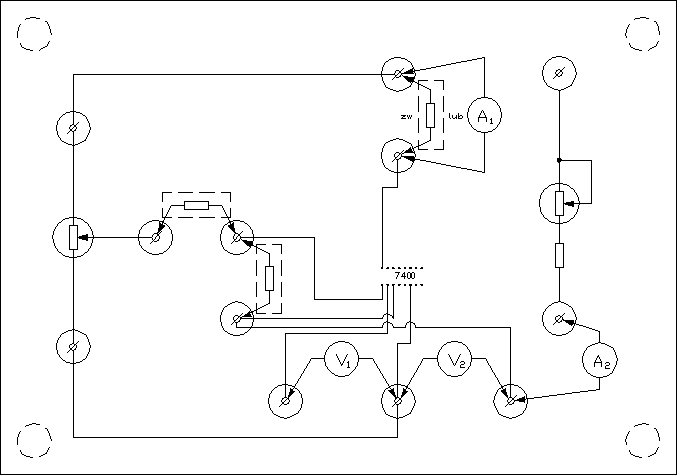

Rys.4. Schemat ideowy układu do zdejmowania charakterystyki ICC = f (UWE) bramki NAND.

Bramka linearyzowana

Regulując rezystorem R1 należy odczytać wartości napięcia wejściowego Uwe i wyjściowego Uwy, odpowiednio na woltomierzach V1 i V2 (patrz rys.5). Następnie z uzyskanych pomiarów wykreślić charakterystykę Uwy = f (Uwe). Powtórzyć pomiary dla różnych wartości rezystancji R2. Liczba pomiarów minimum 10.

Rys.5. Schemat ideowy układu do zdejmowania charakterystyki przejściowej linearyzowanej bramki NAND.

Bramka Schmitt'a.

Regulując rezystorem R1 należy odczytać wartości napięć wejściowego Uwe i wyjściowego Uwy, na woltomierzach odpowiednio V1 i V2 (patrz rys. 6). Pomiary przeprowadzić zmieniając Uwe od 0 do 5V i w odwrotnym kierunku. Następnie z uzyskanych pomiarów wykreślić charakterystykę Uwy = f (Uwe). Liczba pomiarów minimum 10 w każdym kierunku zmian Uwe.

Rys.6. Schemat ideowy układu do zdejmowania charakterystyki przejściowej bramki NAND Schmitt'a.

2) Charakterystyka wejściowa bramki NAND.

Regulując rezystorem R1 należy odczytać wartości napięć Uwe i prądu Iwe wejściowego, na woltomierzu V1 i amperomierzu A (patrz rys. 7). Następnie z uzyskanych pomiarów wykreślić charakterystykę Iwe = f (Uwe). Liczba pomiarów minimum 10.

Rys.7. Schemat ideowy układu do zdejmowania charakterystyki wejściowej bramki NAND

3) Charakterystyki wyjściowe bramki NAND.

W stanie wysokim.

Regulując rezystorem R1 ustawić odpowiedni stan logiczny na wyjściu bramki. Następnie regulując rezystorem R2 należy odczytać wartości napięć Uwy i prądu Iwy wyjściowego, odpowiednio na woltomierzu V2 i amperomierzu A (patrz rys. 8). Następnie z uzyskanych pomiarów wykreślić charakterystykę Uwy = f (Iwy) w stanie wysokim. Liczba pomiarów minimum 10.

Rys.8. Schemat ideowy układu do zdejmowania charakterystyki wyjściowej w stanie wysokim

bramki NAND.

W stanie niskim.

Regulując rezystorem R1 ustawić odpowiedni stan logiczny na wyjściu bramki. Następnie regulując rezystorem R2 należy odczytać wartości napięć Uwy i prądu Iwy wyjściowego, odpowiednio na woltomierzu V2 i amperomierzu A (patrz rys. 9). Następnie z uzyskanych pomiarów wykreślić charakterystykę Uwy = f (Iwy ) w stanie niskim. Liczba pomiarów minimum 10.

Rys.9. Schemat ideowy układu do zdejmowania charakterystyki wyjściowej w stanie niskim

bramki NAND.

C. Zagadnienia do opracowania

Należy przygotować się z zakresu wiedzy obejmującej takie zagadnienia jak: cyfrowe bramki w technice TTL a w szczególności, należy przygotować odpowiedzi na poniższe pytania i polecenia:

Wymień znane Ci techniki realizacji bramek. Wymień ich wady i zalety.

Narysuj schemat budowy bramki NAND zrealizowanej w technice DTL (Diode Transistor Logic). Jaką rolę spełniają tam poszczególne elementy?

Co to jest obciążalność bramki?

Podaj podstawowe parametry elementów logicznych w technice TTL (Transistor Transistor Logic).

Narysuj schemat budowy bramki NAND zrealizowanej w technice TTL (Transistor Transistor Logic). W jakich stanach są poszczególne tranzystory przy wysokim i niskim poziomie na wyjściu bramki?

Narysuj i opisz charakterystykę przejściową bramki NAND TTL.

Narysuj i opisz charakterystykę przejściową linearyzowanej bramki NAND TTL.

Narysuj i opisz charakterystykę przejściową bramki NAND Schmitt'a TTL.

Narysuj symbol bramki AND, OR, NAND, NOR, EX-OR, EX-nor i podaj tabele prawdy.

Widok płyty montażowej do badania układu UCY 74132

Widok płyty montażowej do badania układu UCY 7400

1

4

0V

+5V

R

V2

V1

7

¼ 7400

1

2

3

+5V

14

3

0V

+5V

R1

V2

14

2

1

A

0V

R2

0V

+5V

R

V2

V1

7

¼ 7400

3

V1

7

¼ 7400

3

0V

2

1

R2

14

2

1

A

+5V

R

V2

V1

7

0V

3

14

2

1

R

V2

V1

7

Ľ 7400

3

14

2

1

A

+5V

R1

V2

V1

7

Ľ 7400

3

14

2

1

R3

A

R3

R2

0V

+5V

R1

V2

V1

7

Ľ 7400

3

14

2

1

74132

Wyszukiwarka

Podobne podstrony:

Laboratorium elektroniki - Ćwiczenie 02, Politechnika Lubelska, Studia, sem III, materiały, Teoria O

Laboratorium elektroniki - Ćwiczenie 01, Politechnika Lubelska, Studia, sem III, materiały, Teoria O

Laboratorium elektroniki - Ćwiczenie 04, Politechnika Lubelska, Studia, sem III, materiały, Teoria O

Laboratorium elektroniki - Ćwiczenie 03, Politechnika Lubelska, Studia, sem III, materiały, Teoria O

Metoda prądów oczkowych, Politechnika Lubelska, Studia, sem III, materiały, Teoria Obwodów1, kabelki

stany nieustalone w obwodach RLC zasilanych ze źródła napięcia stałego, Politechnika Lubelska, Studi

BUEE alfabetycznie, Politechnika Lubelska, Studia, sem III, Bezpieczeństwo użytkowania urządzeń elek

bezpieczenstwo calosc 2, Politechnika Lubelska, Studia, sem III, Bezpieczeństwo użytkowania urządzeń

Czwórniki, Politechnika Lubelska, Studia, sem III, pen

Autentyczne dialogi pilotów, Politechnika Lubelska, Studia, sem III

strona piotrka, Politechnika Lubelska, Studia, sem III, pen, METODY NUMERYCZNE, metody numeryczbe st

rozniczki, Politechnika Lubelska, Studia, sem III

metrologiia, Politechnika Lubelska, Studia, sem III

Metro egzam, Politechnika Lubelska, Studia, sem III, Egzamin metrologia

więcej podobnych podstron