Politechnika Warszawska

Wydz. Elektroniki i Technik Informacyjnych

Projekt z ELIU nr 3

Ćwicz. 8 |

Bramki Cyfrowe

|

Rok akad. 1998/99 |

||

Zespół |

Imię i Nazwisko |

Ocena |

Data 11.01.1999 |

|

16 |

Andrzej Maziński |

|

Prowadzący zajęcia |

|

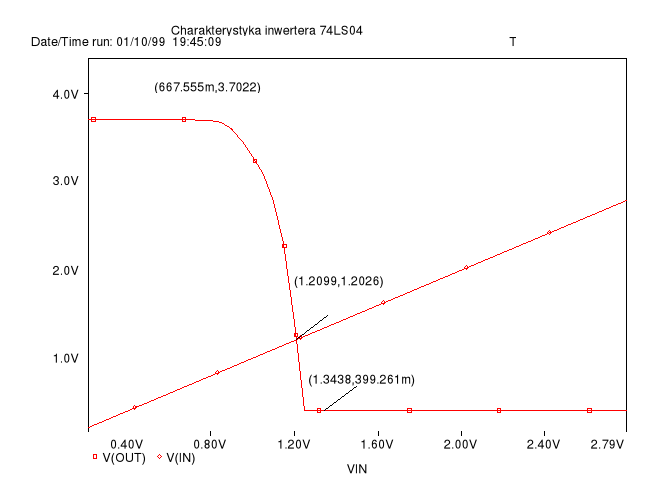

Charakterystyka przejściowa inwertera 74LS04.

Margines szumowy.

Zawartość plik do symulacji programem Pspice:

Charakterystyka inwertera 74LS04 INV_LS.CIR

VCC ZAS 0 5V

VIN IN 0 0V

X1 IN OUT ZAS 74LS04

R1 OUT 0 10K

.DC VIN 0 5 0.05

.PROBE

.LIB INWERTER.LIB

.END

Z wykresu 1 wyznaczam parametry inwertera 74LS04 :

Napięcie wyjściowe stanu wysokiego:

Napięcie wyjściowe stanu niskiego:

Amplituda logiczna:

Napięcie progowe:

Margines zakłóceń dla stanu „1”:

Margines zakłóceń dla stanu „0”:

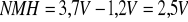

2. Charakterystyka przejsciowa inwertera 74HCU04.

Margines szumowy.

Zawartość plik do symulacji programem Pspice:

Charakterystyka inwertera 74HCU04 INV_MOS.CIR

VCC ZAS 0 5V

VIN IN 0 0V

X1 IN OUT ZAS 74HCU04

.DC VIN 0 5 0.05

.PROBE

.LIB INWERTER.LIB

.END

Z wykresu 2 wyznaczam parametry inwertera 74HCU04 :

Napięcie wyjściowe stanu wysokiego:

Napięcie wyjściowe stanu niskiego:

Amplituda logiczna:

Napięcie progowe:

Margines zakłóceń dla stanu „1”:

Margines zakłóceń dla stanu „0”:

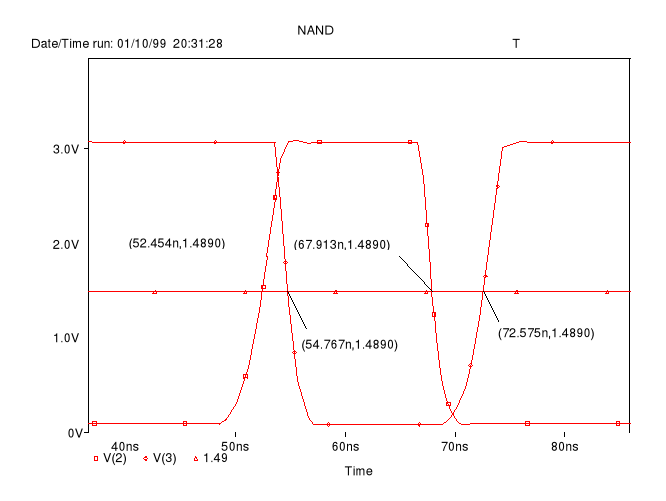

3. Czasy propagacji wyznaczane dla bramki NAND.

MNTYMXDLY = 1

Wykres 3. Przebiegi wejściowe i wyjściowe bramki NAND dla MNTYMXDLY=1

Czasy opóźnień wynoszą :

tdLH = 72,6ns - 67,9ns ≅ 4,7ns

tdHL = 54,8ns - 5,5ns ≅2,3ns

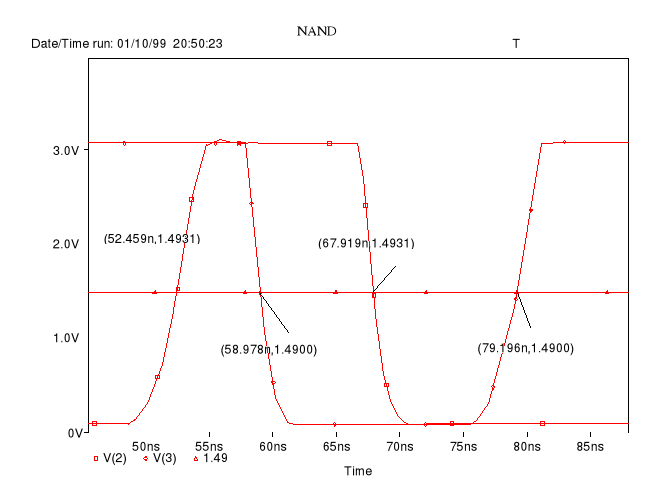

b) MNTYMXDLY = 2

Przebiegi wejściowe i wyjściowy znajdują się na wykresie 4.

Wykres 4. Przebiegi wejściowe i wyjściowe bramki NAND dla MNTYMXDLY=2

Czasy opóźnień wynoszą :

tdLH = 79,2ns - 67,9ns ≅11,3ns

tdHL = 59ns - 52,5ns ≅6,5ns

c) MNTYMXDLY = 3

Przebiegi wejściowe i wyjściowy znajdują się na wykresie 5.

Wykres 5. Przebiegi wejściowe i wyjściowe bramki NAND dla MNTYMXDLY=3

Czasy opóźnień wynoszą:

tdLH = 90,2ns - 67,9ns ≅ 22,3ns

tdHL = 67ns - 52,4ns = 14,6ns

4.Metoda pomiaru uśrednionego czasu propagacji.

Pomiar uśrednionego czasu propagacji sygnału przez pojedynczy inwerter wykonuje się łącząc układ według rys.S3 w protokole. Następnie z oscyloskopu odczytuje się przesunięcie w czasie między impulsami podanymi z wyjść inwerterów oznaczonych odpowiednio na wkładce jako „WY1” i „WY2”.

Metoda I. (przełącznik ustawiony na CI ĄG INV)

Zmierzony czas jest sumą czasów opóźnień czterech ostatnich bramek Δt

Wiadomo, że średni czas propagacji: tpd = 0,5(tdHL + tdLH)

Otrzymujemy więc tpd = 0,25Δt.

Uśredniony czas propagacji tpd inwertera (dla mntymxdly=2) wynosi :

tpd = (tdHL+tdLH)/2 = (11,6+7)/2 = 9,3ns

Okres generatora zbudowanego z pięciu inwerterów (tpd =9,3ns) wynosi:

Tg=2tpdk= 2 * 9,3ns* 5= 93ns

Aby sprawdzić jak ma się to do rzeczywistości zasymulować należy generatora z pliku gen_cyf.cir. Jak widać na poniższym rysunku okres generatora zgadza się z obliczoną wartością Tg.( Uk --> [Author:R.D.Te〄ˠi] ład symulowany dla MNTYMXDLY=2 )

Wykres 6. Przebiegi napięcia w 3 różnych punktach układu z rys S3

Wyniki odczytane z wykresu potwierdzają prawidłowość obliczeń - Tg ok. 95 ns.

Układ użyty do symulacji to 5 inwerterów tworzących pętlę. Gdy do wejścia podłączymy pewien prąd wówczas ustalą się napięcia na inwerterach. Aby zainicjować układ należy podłączyć na 2ns stan niski do 1 inwertera i szybko odłączyć układ powodujący ten stan. Jeśli tego nie zrobimy układ może dać na wyjściu stan nieustalony.

Laboratorium Instytutu Systemów Elektronicznych 99-01-11 13:41

1

Made by Andrzej Maziński

Wyszukiwarka

Podobne podstrony:

6592

06406733id 6592 Nieznany (2)

6592

6592

6592

6592

praca-magisterska-6592, Dokumenty(8)

6592

więcej podobnych podstron