0952

a0 -

CLf ->-

Dekoder 1 2 4

"i/o

//?

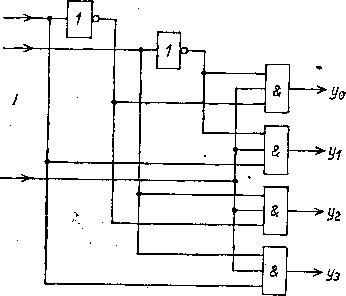

Rys. 9.53. Układ logiczny demultipleksera

a0 oi d% yt — a0 Ol 4, ^2 ** o0 Oi d, y3 = a0 at d

Rys. 9.52. Zasada działania demultipleksera

yo

Tablica 9.4. Scalone demultipleksery

|

Wyjścia |

TTL |

ECL |

CMOS |

|

16 |

74LS154 |

4514 | |

|

8 |

74LS138 |

10162 |

74HC138 |

|

8 |

74ALS5381* |

* 40H138 | |

|

2x4 |

74LS139 |

10172 |

74HC139 |

|

2x4 |

74ALS5390 |

4555 | |

|

0 Przełączana polaryzacja wyjścia. | |||

Wyszukiwarka

Podobne podstrony:

Zo a1 do di dz y Rys. 9.55. Układ logiczny multipleksera y — cio #1 rfi+flo

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

Image314 Rys. 4.360. Układ realizujący dodawanie i odejmowanie a) schemat logiczny układu dla jednej

Image358 Rys. 4.410. Schematy logiczne dekoderów scalonych c

Image448 Rys. 4.541. Układ kombinacyjny współdziałający z licznikiem a) tablice Kamaugha, b) schemat

Image450 "Wij~ f*teek TrNyT Rys. 4.545 Układ realizujący trzy niezależnie nas a) schemat logicz

skanuj0018 (124) Rys, 4,380. Schematy logiczne dekoderów scalonych a) ’42, b) *43, c) *44 co •<3

skanuj0025 (84) Wejścia £9,827 23222l 2° Rys. 4.392. Schemat logiczny dekodera matrycowego 10/1024

Image538 Rys. 4.697 Schemat logiczny fragmentu układu sterującego dynamicznym układem wyświetlani Uk

więcej podobnych podstron