Image132

Zmiana stanu przerzutników następuje przy zmianie sygnału taktującego z 0 na 1. Rejestr jest zerowany sygnałem R — 1.

Rejestr o identycznej strukturze logicznej jak rejestr poprzedni, lecz o dwukrotnie większej długości logicznej (8 bitów) przedstawiono na rys. 4.77a. Działanie układu zilustrowano na rys. 4.77b i c.

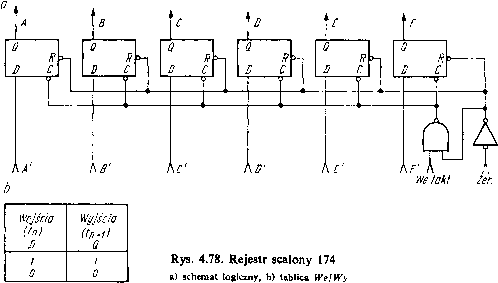

Na rysunku 4.78 przedstawiono schemat logiczny równoległego scalonego rejestru 174. Zawiera on 6 przerzutników typu D z wyprowadzonymi wejścia

mi D i wyjściami Q. Przerzutniki mogą być zerowane. Łącząc wyjście poprzedniego stopnia rejestru z wejściem następnego — można otrzymać rejestr szeregowy. Rejestr jest wykorzystywany głównie jako rejestr buforowy, rejestr przesuwający lub jako element do budowy pamięci podręcznych.

4.3.1.6. Zastosowania rejestrów

Pamięci zbudowane z rejestrów

Rejestry mogą być wykorzystywane do budowy pamięci buforowych, jak również szeregowych i równoległych pamięci różnych typów. Wykorzystywane są zarówno rejestry szeregowe, jak i równoległe (rys. 4.79).

Na rysunku 4.80 przedstawiono schemat ideowy układu wprowadzania informacji ze wspólnej szyny do rejestrów i?, — R10. Jeśli rejestry Rx — Ri0 są zbudowane z przerzutników 75, to w celu dokonania wpisu informacji należy na wejście X podać impuls 0. Informacja wejściowa jest wpisywana do tego rejestru, którego adres jest podany na wejścia dekodera.

Na rysunku 4.81 przedstawiono schemat ideowy układu, służącego do wprowadzenia 4-bitowej informacji ze wspólnej szyny do rejestrów R0 -f- R63 (75). Podanie impulsu 0 na wejście X powoduje wpisanie aktualnej informacji do tego rejestru, którego adres podano na wejścia dekoderów (adresowanie współrzędnościowe). Odczytywanie żądanej informacji z pamięci jest realizowane za pomocą multiplekserów.

142

Wyszukiwarka

Podobne podstrony:

Image132 Zmiana stanu przerzutników następuje przy zmianie sygnału taktującego z 0 na 1. Rejestr jes

DSC04908 (2) MIGRACJA WODY W ZIARNACH Migracja wody w masach ziarnowych następuje przy zmianie tempe

1. Jakie błędy pojawiają się przy zmianie sygnału analogowego na cyfrowy i na

DSC04908 (2) MIGRACJA WODY W ZIARNACH Migracja wody w masach ziarnowych następuje przy zmianie tempe

106 z przyjęciem Symfera 43 minut, która! o strata przy prędkości jazdy 5 km na godzinę jest równa z

Zdjęcie059 (12) Czułość przy zmianie znaku sygnału Jest to zmiana elektrycznego sygnału wejściowego

Image118 lenia informacji na wejściu D (ts) przed zmianą stanu wejścia taktującego z 0 na 1 wynika z

Image512 emiterowego RE. Po przełączeniu na wyjściu układu pojawia się sygnał 1, przy czym sygnał te

skrypt134 137 Przy zmianie stanu skupienia ze stałego w ciekły, obserwuje się dla wszystkich elali s

Image582 Na rysunku 4.777 przedstawiono przebiegi idealne oraz przebiegi z odbiciami występującymi p

skanuj0081 (12) S9 Podobne reperkusje wywoła zmiana stanu podaży, przy założeniu, że stan popytu poz

page0085 81 żna utożsamiać stwarzania ze zmianą (mutatio), gdyż przy zmianie tasama rzecz, fizycznie

powstają w przewodzie przy zmianie kierunku przepływu (tuki, kolana) zmiana przekroju, rozgałęzienia

więcej podobnych podstron