Image137

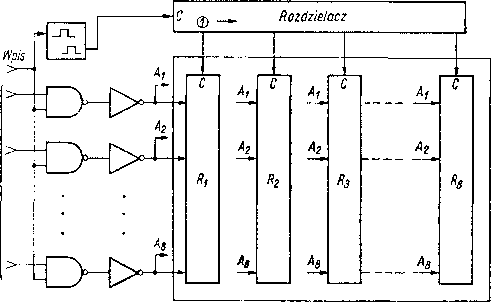

Rys. 4.83

Zespół rejestrów buforowych o pojemności 8 słów 8-bitowych

2 rozdzielacza

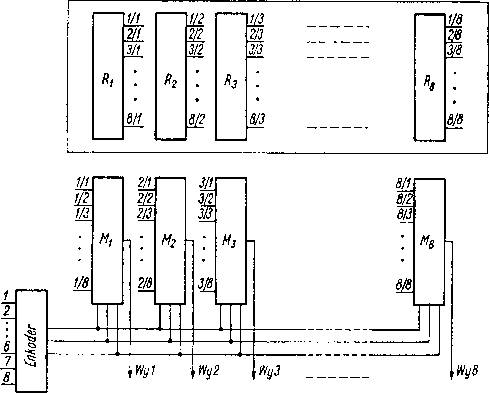

Rys. 4.84

Układ służący do wyprowadzania informacji z rejestrów

Organizację sterowania zapisem i odczytem w buforze przedstawiono na rys. 4.85. Informację z buforu można odczytać wówczas, gdy komparator nie wykazuje równości adresów zapisu i odczytu.

Inny typ pamięci buforowej, a mianowicie pamięć typu FIFO przedstawiono na rys. 4.86. Bufor pamięciowy składa się z rejestrów równoległych oraz układu sterowania. W stanie początkowym wszystkie przerzutniki JK-MS w układzie sterowania powinny być wyzerowane. Jeżeli 5 = 1, to zmiana sygnału 1 na 0 na wejściu „Wpis” powoduje, opadającym zboczem impulsu przebie-

10* 147

Wyszukiwarka

Podobne podstrony:

Image122 a Rys. 4.62 Układ służący do równoległego wprowadzania informacji z czterech źródeł do reje

Image124 Rys. 4.66. Układ służący do równoległego wyprowadzania informacji z rejestru Q

Image173 i©-=E>- WE Aq+A3 CSf CSQ TT Zespół klawiszy do zadawania słów 3?-bitowych U Zespół klawi

Image173 i©-=E>- WE Aq+A3 CSf CSQ TT Zespół klawiszy do zadawania słów 3?-bitowych U Zespół klawi

Image140 Rys. 4.87. Pamięć składająca się z zespołu rejestrów równoległych150

Image134 Adres słowa Rys. 4.80. Układ wprowadzania informacji ze wspólnej szyny do rejestrów równole

Image136 Na rysunku 4.82 przedstawiono przykład rozwiązania pamięci typu RAM, zbudowanej z rejestrów

Image143 rys. 4.91. Impuls „start” powoduje wpisanie informacji do rejestru i odblokowanie bramki B.

Image152 Rys. 4.104. Rejestr generujący ciągi pseudolosowe z samoczynnym likwidowaniem stanów

Image171 Rys. 4.131. Schemat ideowy generatora 8 słów 32 bitowych Rys. 4.132. Schemat ideowy generat

więcej podobnych podstron