Image210

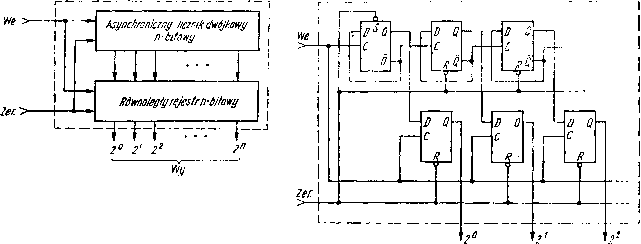

Q Ouasłsymhroniczny licznik dwójkowy n-bitowy b

Rys. 4.202. Quasi-synchroniczny licznik n-bitowy

a) schemat ideowy, b) schemat logiczny

|

A B C D |

A 8 C D |

A B C D | |||

|

We Dekada/ |

We Dekada 2 |

Dekada 3 |

|

D,- |

po1 |

po1 |

nA>~ Dj’ |

bo | ||

|

We |

6

JL ? i. 4 JL 6 7 8 9 to 11 12 13 14 15 16 17

Mfe J5U7LT7UjlJ71J3UJU7Lr5LJ5U3lJ71JilJ3U7lJ7U?L

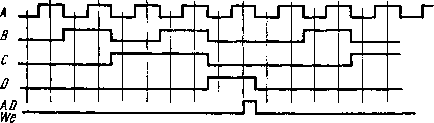

Rys. 4.203. Równolegle łączenie liczników asynchronicznych

a) schemat ideowy, b) przebiegi czasowe

4.4.3. liczniki synchroniczne

4.4.3.1. Liczniki dwójkowe jednokierunkowe

Rozpatrzmy synchroniczny licznik mod. 16, zliczający w przód w naturalnym kodzie dwójkowym.

Na podstawie tablicy wzbudzeń przerzutnika JK-MS (rys. 3.27e), przyjętego do syntezy licznikami tablicy stanów licznika (rys. 4.204a) otrzymuje się tablice Karnaugha (rys. 4.204b, c) umożliwiające wyznaczenie funkcji przełączających dla poszczególnych wejść / i K przerzutników.

Wyszukiwarka

Podobne podstrony:

Image214 ;AA Takt. Rys. 4.207. Zmodyfikowany synchroniczny licznik dwójkowy z przeniesieniami równol

Image235 akt w 2t C Dekada IV Rys. 4.242. Ośmiodekadowy licznik synchroniczny Rys. 4.243.

Image281 Dodawanie liczb dwójkowych można zrealizować szeregowo lub równolegle, jak poglądowo ilustr

Rys. 10.29. Synchroniczny licznik dwójkowy

Image281 Dodawanie liczb dwójkowych można zrealizować szeregowo lub równolegle, jak poglądowo ilustr

Image171 Rys. 4.131. Schemat ideowy generatora 8 słów 32 bitowych Rys. 4.132. Schemat ideowy generat

Image204 4.4.2.3. Scalone liczniki asynchroniczne Wiele przedstawionych typów liczników asynchronicz

Image207 abWg licznikaWe >— aWe >- XA *3 h h Podział

Image258 Stany liczników w kolejnych etapach operacji Tablica 4.16 ma być przedstawiony w postaci li

Image260 jako liczniki dziesiętne. Pojemność licznika składającego się z n dekad liczących wynosi N

Image284 Przykłady rozwiązań dwójkowych sumatorów równoległych Na rysunku 4.324 przedstawiono schema

rys 5 VI Rejestr PIPO z sumatorem dwóch liczb 4 bitowych rys.5.VI. Rejestr PIPO z sumatorem dwóch

więcej podobnych podstron