Image380

Transkoder ten realizuje następujące funkcje przełączające:

A = ae+beg B = af+be+deg C = af+bf+aeg D = abfg

»-n = *fg

Schemat logiczny takiego układu jest przedstawiony na rys. 4.438a.

Ponieważ niektóre z kodów mają właściwości arytmetyczne, dlatego w celu ich konwersji mogą być wykorzystane układy arytmetyczne, głównie sumatory. Przykłady rozwiązań transkoderów zbudowanych z sumatorów scalonych: 82 oraz 83 są przedstawione na rysunkach 4.439 ~ 4.442.

4.6.5. Multipleksery i demultipleksery 4.6.5.1. Wiadomości ogólne

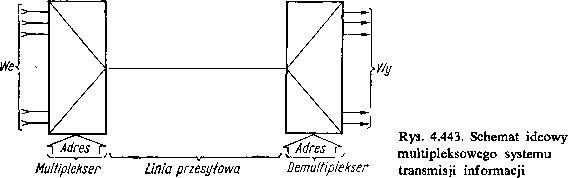

Multipleksery i demultipleksery są układami umożliwiającymi zrealizowanie multipleksowego systemu transmisji informacji (rys. 4.443). Do zrealizowania takiego systemu jest niezbędny po stronie nadawczej przetwornik formatu słów z równoległego na szeregowy (multiplekser), a po stronie odbiorczej przetwornik

formatu słów z szeregowego na równoległy (demultiplekser). Układy tych przetworników funkcjonalnie odpowiadają wielopozycyjnym jednobiegunowym przełącznikom z kodowym wyborem pozycji za pomocą dekodera adresu. W celu zrealizowania transmisji informacji bez zmiany jej postaci, przetworniki powinny być wyposażone w takie same dekodery adresu. Zazwyczaj jest stosowane adresowanie w naturalnym kodzie dwójkowym. Przedstawione poniżej scalone multipleksery i demultipleksery zawierają pełne dekodery adresu.

4.6.S.2. Multipleksery scalone

W technice TTL są wytwarzane multipleksery o 16, 8, 4 i 2 wejściach informacyjnych i odpowiednio o 4, 3, 2 i 1 wejściu adresowym.

Wyszukiwarka

Podobne podstrony:

skanuj0040 (38) Rozpatrywany transkoder realizuje następujące funkcje logiczne: A = ae + beg A — af+

Image370 Schemat logiczny układu realizującego powyższe funkcje przełączające przedstawiono na

Image371 Schemat logiczny układu realizującego powyższe funkcje przełączające przedstawiono na rys.

Image239 z których wyznaczono następujące funkcje przełączające dla poszczególnych przerzutników: Da

Układy kombinacyjne - 1Zadania 1. W językach ST i LD napisz program realizujący następujące funkcje

Image328 Funkcje przełączające (A > B)wy, (A — B)wy oraz (A < B)wy można przekształcać uzyskuj

Image222 Jeżeli poszczególne funkcje przełączające zostaną zrealizowane w następujący sposób: Da = A

Image233 Jeżeli funkcje przełączające dla wejść J i K zostaną przekształcone w następujący sposób: j

Image280 Podobnie jak dla sumatora pełnego, można wyznaczyć funkcje przełączające realizowane przez

Image347 Funkcje przełączające, wyznaczone na podstawie tablicy wartości /-tego stopnia rozpatrywane

Image355 Implementacje układów realizujących funkcje (3) oraz funkcje (4) przedstawiono na rys. 4.40

17047 zad2 treść Narysuj schemat drabinkowy programu realizującego następujące sekwencje: po trzykro

więcej podobnych podstron