Image449

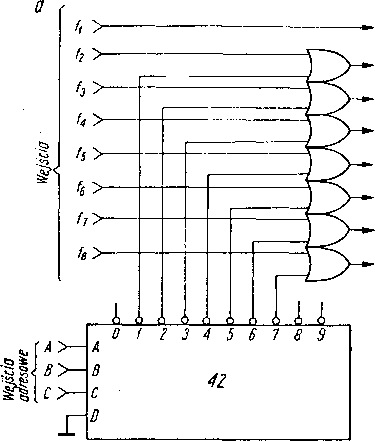

Rys. 4.543. Komutatorowy układ wyjściowy przesuwnika

a) schemat logiczny, b) tablica we iwy ilustrująca działanie układu

|

Wejścia adresowe |

Wyjścia | |||||||||

|

A |

B |

c |

Yi |

y> |

Vj |

* |

ys |

Ys |

Yr |

Ys |

|

0 |

0 |

0 |

u |

f |

i |

/ |

f |

1 |

f |

1 |

|

i |

0 |

0 |

fi |

?2 |

■ ' |

1 |

f |

1 |

1 | |

|

0 |

1 |

0 |

ft |

1 |

h |

/ |

i |

f |

1 |

1 |

|

f |

1 |

0 |

n |

1 |

i |

U |

i |

i |

1 |

1 |

|

0 |

0 |

i |

fi |

f |

i |

i |

fs |

i |

i |

1 |

|

i |

0 |

i |

ft |

1 |

i |

t |

i |

fs |

i |

1 |

|

0 |

i |

i |

t |

1 |

J |

1 |

1 |

f7 |

i | |

|

1 |

1 |

i |

ft |

1 |

1 |

1 |

1 |

i |

1 |

U |

|

nastawnik dziesiętny |

Hastawnik dziesiętny |

tiastawnfk dziesiętny | ||

|

........ . 1 - , .......... | ||||

|

c P L 192 C*- WR |

C~ 132 P~ c-h WR |

- |

C~ 192 P- ■ C+ WR | |

|

-L |

-J- ; | |||

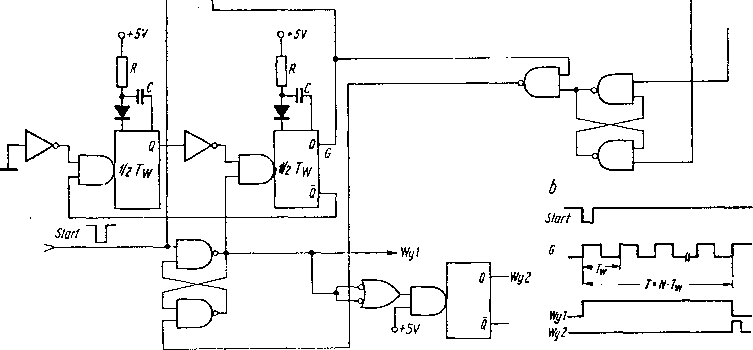

Rys. 4.544. Układ realizujący opóźnienia czasowe w zakresie od Tw do 999 Tu

AS O

Wyszukiwarka

Podobne podstrony:

Image455 a o E Y +27~ Funkcję spełnianą przez układ oraz jego schemat logiczny przedstawiono na rys.

Image444 c Rys. 4.535. Licznikowy układ opóźniający ujemne zbocze impulsu wejściowego o zadany czas

CCF090613�018 4b) Klucz analogowy t t t Rys. 10.17. Układ próbkujący z pamięcią: a) schemat układu;

Image448 Rys. 4.541. Układ kombinacyjny współdziałający z licznikiem a) tablice Kamaugha, b) schemat

Image450 "Wij~ f*teek TrNyT Rys. 4.545 Układ realizujący trzy niezależnie nas a) schemat logicz

Image470 Rys. 4.585. Schemat logiczny rozdzielacza 16-wyjściowego Wyjścia (kod 1 z 64) Wejście >-

Image487 Rys. 4.610. Schemat logiczny generatora impulsów o czasie trwania impulsu wyjściowego progr

Image44 (9) 1 1 Rys. 1 Schemat ideowyMiOMISW ^ Układ powstał w celu poprawienia bezpieczeństwa ruchu

Image450 "Wij~ f*teek TrNyT Rys. 4.545 Układ realizujący trzy niezależnie nas a) schemat logicz

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

Image314 Rys. 4.360. Układ realizujący dodawanie i odejmowanie a) schemat logiczny układu dla jednej

więcej podobnych podstron