86

ROZDZIAŁ 4 M Cyfrowe układy logiczne

ROZDZIAŁ 4 M Cyfrowe układy logiczne

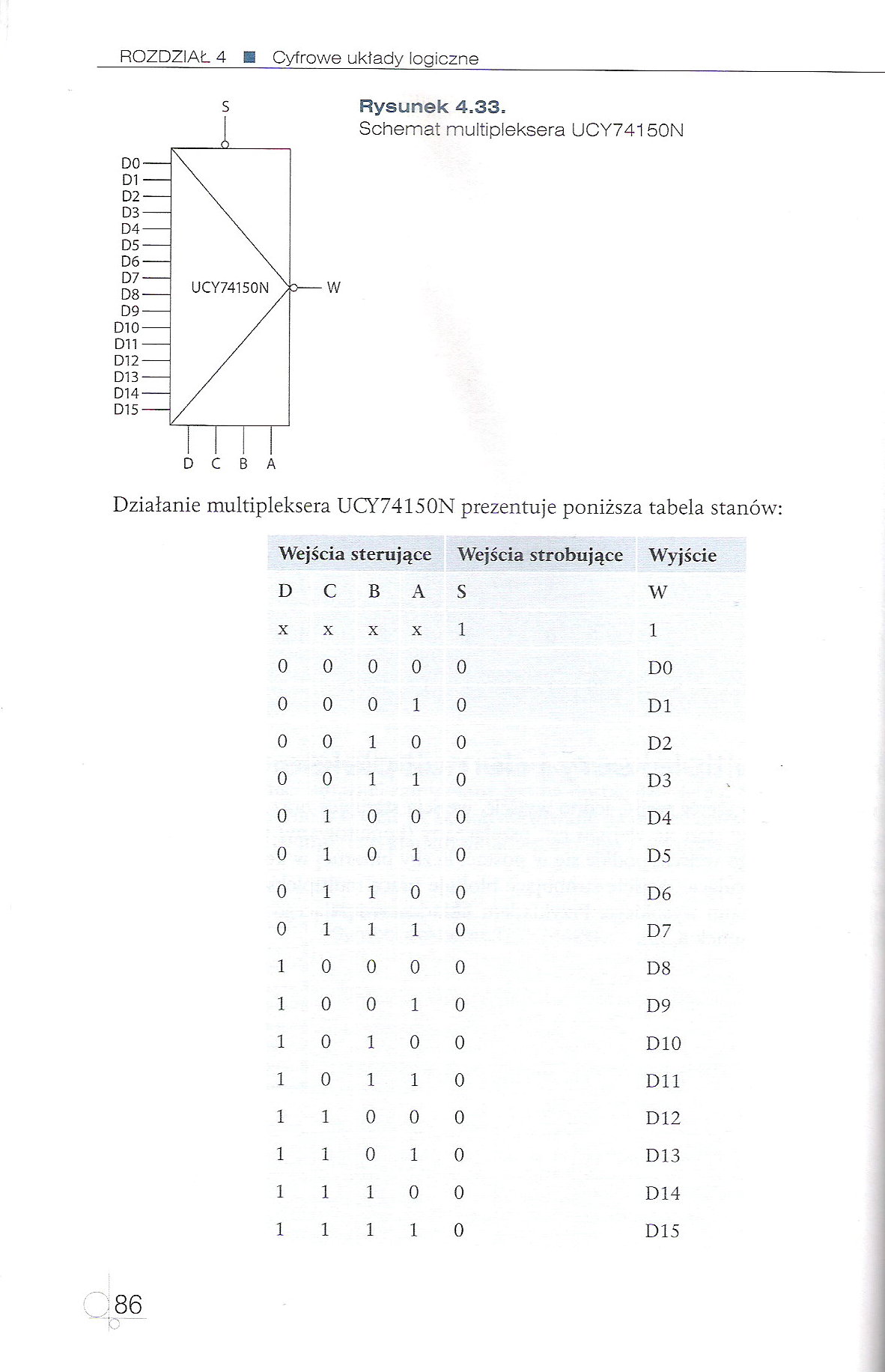

Rysunek 4.33.

Schemat multipleksera UCY74150N

Działanie multipleksera UCY74150N prezentuje poniższa tabela stanów: Wejścia sterujące Wejścia strobujące Wyjście

|

D |

c |

B |

A |

s |

w |

|

X |

X |

X |

X |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

DO |

|

0 |

0 |

0 |

1 |

0 |

Dl |

|

0 |

0 |

1 |

0 |

0 |

D2 |

|

0 |

0 |

1 |

1 |

0 |

D3 |

|

0 |

1 |

0 |

0 |

0 |

D4 |

|

0 |

1 |

0 |

1 |

0 |

D5 |

|

0 |

1 |

1 |

0 |

0 |

D6 |

|

0 |

1 |

1 |

1 |

0 |

D7 |

|

1 |

0 |

0 |

0 |

0 |

D8 |

|

1 |

0 |

0 |

1 |

0 |

D9 |

|

1 |

0 |

1 |

0 |

0 |

D10 |

|

1 |

0 |

1 |

1 |

0 |

Dli |

|

1 |

1 |

0 |

0 |

0 |

D12 |

|

1 |

1 |

0 |

1 |

0 |

D13 |

|

1 |

1 |

1 |

0 |

0 |

D14 |

|

1 |

1 |

1 |

1 |

0 |

D15 |

86

Wyszukiwarka

Podobne podstrony:

IMG 71 (4) 2. UKŁADY POLACZKA STACJI m i i Rys. 2.8. Schemat rozdzielnicy o podwójnym systemie szyn

2.3. UKŁADY Z SZYNAMI ZBIORCZYMI I Rys. 2.5. Schemat rozdzielni dużej stacji z trzema

skanuj0011 (182) 37 Rozdział 3. Żywienie dzieci Tabela 3.3. Aktualny (2007) schemat żywienia niemo

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

skanuj0007 (481) Rozdział 1. ♦ Podstawy 17 Rozdział 1. ♦ Podstawy 17 Rysunek 1.3. Konfiguracja serwe

rys 2 11(1) Rysunek 2.11. Schemat blokowy karty EGA pracującej w trybie graficznym Do cyfrowego wejś

skanuj0144 144 Cyfrowe oświetlenie i rendering Rysunek 5.1. Gradienty kluczowe dla oddawania ks

skanuj0240 240 Cyfrowe oświetlenie i rendering Rysunek 8.7. Przy czerwonym świetle (po lewej)

więcej podobnych podstron