Page19

(20 Q1 Q2

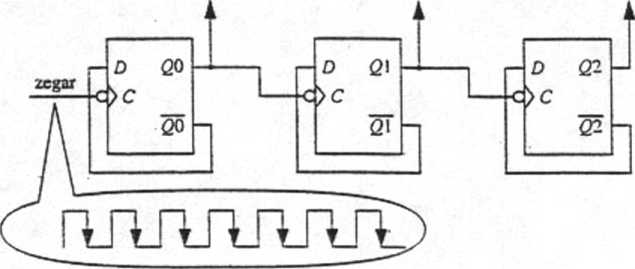

Rys. 2.15. Asynchroniczny licznik binarny

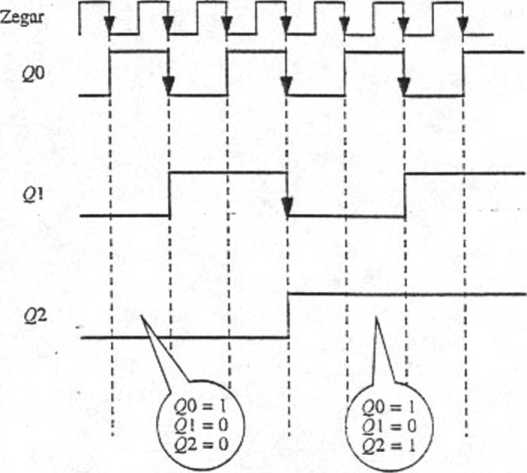

Wyjście z licznika binarnego

|

; Impuls zegara |

02 |

01 |

00 |

|

• ' .......... 0 |

0 |

0 1 0 | |

|

1 |

o |

0 |

1 |

|

2 |

0 |

1 |

0 |

|

3 |

0 |

1 |

1 |

|

4 |

1 |

0 |

0 |

|

5 |

1 |

0 |

1 |

|

6 |

1 |

1 |

0 |

|

I_z_ |

1 |

1 |

1 |

Rys. 2.16. Wykres czasowy dla iicznika asynchronicznego

Li

7c Ti t, tt

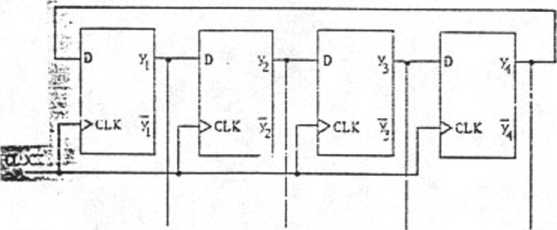

Ring counlcr.

Wyszukiwarka

Podobne podstrony:

ark22 20 Q1 Q2 Rys. 2.15. Asynchroniczny licznik binarny Wy

img045 (15) 120 R.7.11 7 R.7.20. Rozwiązania Zad.7.11 r Zad.7.20 przedstawiono na rys.R.7.2. 120 R.7

5WW10a VFO schem R?ikQ Rys. 15. Schemat VFO Dli - cewka komórkowa 200 pH na rezystorze 20 k£M),5 W

Część 1 15. ZADANIA POWTÓRKA 20 Rys. 15.2S Luk kolony statycznie nie wyznać żalny Układ jest

295 (11) Ryś / 15 20. Uproszczony sposób przesuwania linii pozycyjnej przy określaniu pozycji nicjcd

Rys. 10.28. Asynchroniczny licznik dwójkowy CLK (ans. clock) — zegar RCO (ang. rlpple carry output)

3600 Rys. 4.15. Rozdzielnica WSR 20 - pole odpływowe kablowe 1 szyny zbiorcze, 2 odłącznik, 3 —

ScanImage65 Rys. 15.20 Tablica 15.14 Konstrukcja przejmująca siły poziome Współczynnik j3 przy udź

566 2 15. NOWE ŹRÓDŁA I TECHNOLOGIE WYTWARZANIA ENERGII ELEKTRYCZNEJ Rys. 15.20. Porównanie regulacj

Rys. 10.41. Licznik modulo(M-fl) z równo ległym wpisem P = Zm—M przy Z — 15 LOAD L CLK MZ CT=0 >

81615 img045 (15) 120 R.7.11 7 R.7.20. Rozwiązania Zad.7.11 r Zad.7.20 przedstawiono na rys.R.7.2. 1

Untitled Scanned 62 - 126 Rys.4.2b. Szeregowy licznik dwójkowy z wpisywaniem równoległym asynchronic

więcej podobnych podstron